数字集成电路复习

- 格式:ppt

- 大小:2.00 MB

- 文档页数:49

数字集成电路考试知识点一、数字逻辑基础。

1. 数制与编码。

- 二进制、十进制、十六进制的相互转换。

例如,将十进制数转换为二进制数可以使用除2取余法;将二进制数转换为十六进制数,可以每4位二进制数转换为1位十六进制数。

- 常用编码,如BCD码(8421码、余3码等)。

BCD码是用4位二进制数来表示1位十进制数,8421码是一种有权码,各位的权值分别为8、4、2、1。

2. 逻辑代数基础。

- 基本逻辑运算(与、或、非)及其符号表示、真值表和逻辑表达式。

例如,与运算只有当所有输入为1时,输出才为1;或运算只要有一个输入为1,输出就为1;非运算则是输入和输出相反。

- 复合逻辑运算(与非、或非、异或、同或)。

异或运算的特点是当两个输入不同时输出为1,相同时输出为0;同或则相反。

- 逻辑代数的基本定理和规则,如代入规则、反演规则、对偶规则。

利用这些规则可以对逻辑表达式进行化简和变换。

- 逻辑函数的化简,包括公式化简法和卡诺图化简法。

卡诺图化简法是将逻辑函数以最小项的形式表示在卡诺图上,通过合并相邻的最小项来化简逻辑函数。

二、门电路。

1. 基本门电路。

- 与门、或门、非门的电路结构(以CMOS和TTL电路为例)、电气特性(如输入输出电平、噪声容限等)。

CMOS门电路具有功耗低、集成度高的优点;TTL门电路速度较快。

- 门电路的传输延迟时间,它反映了门电路的工作速度,从输入信号变化到输出信号稳定所需要的时间。

2. 复合门电路。

- 与非门、或非门、异或门等复合门电路的逻辑功能和实现方式。

这些复合门电路可以由基本门电路组合而成,也有专门的集成电路芯片实现其功能。

三、组合逻辑电路。

1. 组合逻辑电路的分析与设计。

- 组合逻辑电路的分析方法:根据给定的逻辑电路写出逻辑表达式,化简表达式,列出真值表,分析逻辑功能。

- 组合逻辑电路的设计方法:根据逻辑功能要求列出真值表,写出逻辑表达式,化简表达式,画出逻辑电路图。

2. 常用组合逻辑电路。

1. 集成电路是指通过一系列特定的加工工艺,将晶体管、二极管、MOS管等有源器件和阻、电容、电感等无源器件,按一定电路互连,“集成”在一块半导体晶片(硅或砷化镓)上,封装在一个外壳内,执行特定电路或系统功能的一种器件。

2.集成电路的规模大小是以它所包含的晶体管数目或等效的逻辑门数目来衡量。

等效逻辑门通常是指两输入与非门,对于CMOS集成电路来说,一个两输入与非门由四个晶体管组成,因此一个CMOS电路的晶体管数除以四,就可以得到该电路的等效逻辑门的数目,以此确定一个集成电路的集成度。

3.摩尔定律”其主要内容如下:集成电路的集成度每18个月翻一番/每三年翻两番。

摩尔分析了集成电路迅速发展的原因,他指出集成度的提高主要是三方面的贡献:(1)特征尺寸不断缩小,大约每3年缩小 1.41倍;(2)芯片面积不断增大,大约每3年增大 1.5倍;(3)器件和电路结构的改进。

4.反标注是指将版图参数提取得到的分布电阻和分布电容迭加到相对应节点的参数上去,实际上是修改了对应节点的参数值。

5.CMOS反相器的直流噪声容限:为了反映逻辑电路的抗干扰能力,引入了直流噪声容限作为电路性能参数。

直流噪声容限反映了电流能承受的实际输入电平与理想逻辑电平的偏离范围。

6. 根据实际工作确定所允许的最低输出高电平,它所对应的输入电平定义为关门电平;给定允许的最高输出低电平,它所对应的输入电平为开门电平7. 单位增益点.在增益为0和增益很大的输入电平的区域之间必然存在单位增益点,即dVout/dVin=1的点8. “闩锁”现象在正常工作状态下,PNPN四层结构之间的电压不会超过Vtg,因此它处于截止状态。

但在一定的外界因素触发下,例如由电源或输出端引入一个大的脉冲干扰,或受r射线的瞬态辐照,使PNPN四层结构之间的电压瞬间超过Vtg,这时,该寄生结构中就会出现很大的导通电流。

只要外部信号源或者Vdd和Vss能够提供大于维持电流Ih的输出,即使外界干扰信号已经消失,在PNPN四层结构之间的导通电流仍然会维持,这就是所谓的“闩锁”现象9. 延迟时间:T pdo ——晶体管本征延迟时间;UL ——最大逻辑摆幅,即最大电源电压;Cg ——扇出栅电容(负载电容);Cw ——内连线电容;Ip ——晶体管峰值电流。

数字集成电路复习要点⼀、简答题1.集成电路发展的特点:速度变快,I/O增多,⼯作电压下降……A,特征尺⼨越来越⼩,B,单个芯⽚晶体管数⽬越来越多,速度越来越快,电压越来越⼩,层数越来越多,端⼝越来越多,功耗越来越低2.P181⼤扇⼊的“设计技术”。

A,调整晶体管尺⼨B,逐级加⼤晶体管尺⼨C,重新安排输⼊D,重组逻辑结构(把光键路径上的晶体管靠近门的输出端)3.简述集成电路⼯艺中典型的光刻步骤及其相互关系。

(P28)氧化层,涂光刻胶,光刻机曝光,光刻胶的显影和烘⼲,酸刻蚀,旋转清洗和⼲燥,各种⼯艺加⼯步骤,去除光刻胶4.什么是多晶⾃对准⼯艺,有哪些优点?(P32)在掺杂之前形成图形的多晶硅栅实际确定了沟道区的确切位置,从⽽也确定了源区和漏区的位置。

它使源和漏这两个区域相对于栅具有⾮常精确的位置,有助于减⼩晶体管中的寄⽣电容。

5.CMOS逻辑门特性:(全摆幅,⽆⽐性,低输出阻抗,⾼输⼊阻抗,⽆静态功耗。

)A,电压摆幅等于电源电压,噪声容很⼤,B,逻辑电平与器件的相对尺⼨⽆关,⽆⽐逻辑,C,具有低输出阻抗,⾼输⼊阻抗,D,不消耗任何静态功率6.伪NCMOS门逻辑的特点A,减少晶体管的数⽬,由2N减到N+1,B,速度快缺点:⼩的噪声容限和⼤的静态功耗6.传输管逻辑的优点是什么?有哪些缺点,解决的办法是什么?优点:结构简单,阀值损失⼩,硬件开销⼩缺点:延时⾼,仅含NMOS的传输管将引起静态功耗并减⼩噪声容限解决办法:避免开关长串联以减⼩延时,增加电平恢复晶体管以消除静态功耗7.什么是时钟馈通,有何危害?(P215)原理:电容耦合的特殊情况,由在预充电器件的时钟输⼊和动态输出节点之间电容耦合引起的效应,当下拉⽹络不导通时,这⼀电容耦合会在时钟由低⾄⾼翻转时,引起的动态节点输出上升到VDD以上;⽽快速上升和下降时时钟边沿会耦合到信号节点上。

特点:a)可能使预充电管正常情况下反偏结⼆极管变为正向偏置,使电⼦注⼊到衬底中,被附近处于⾼电平的⾼阻节点收集,导致出错。

第一章 数字集成电路介绍第一个晶体管,Bell 实验室,1947第一个集成电路,Jack Kilby ,德州仪器,1958 摩尔定律:1965年,Gordon Moore 预言单个芯片上晶体管的数目每18到24个月翻一番。

(随时间呈指数增长)抽象层次:器件、电路、门、功能模块和系统 抽象即在每一个设计层次上,一个复杂模块的内部细节可以被抽象化并用一个黑匣子或模型来代替。

这一模型含有用来在下一层次上处理这一模块所需要的所有信息。

固定成本(非重复性费用)与销售量无关;设计所花费的时间和人工;受设计复杂性、设计技术难度以及设计人员产出率的影响;对于小批量产品,起主导作用。

可变成本 (重复性费用)与产品的产量成正比;直接用于制造产品的费用;包括产品所用部件的成本、组装费用以及测试费用。

每个集成电路的成本=每个集成电路的可变成本+固定成本/产量。

可变成本=(芯片成本+芯片测试成本+封装成本)/最终测试的成品率。

一个门对噪声的灵敏度是由噪声容限NM L (低电平噪声容限)和NM H (高电平噪声容限)来度量的。

为使一个数字电路能工作,噪声容限应当大于零,并且越大越好。

NM H = V OH - V IH NM L = V IL - V OL 再生性保证一个受干扰的信号在通过若干逻辑级后逐渐收敛回到额定电平中的一个。

一个门的VTC 应当具有一个增益绝对值大于1的过渡区(即不确定区),该过渡区以两个有效的区域为界,合法区域的增益应当小于1。

理想数字门 特性:在过渡区有无限大的增益;门的阈值位于逻辑摆幅的中点;高电平和低电平噪声容限均等于这一摆幅的一半;输入和输出阻抗分别为无穷大和零。

传播延时、上升和下降时间的定义传播延时tp 定义了它对输入端信号变化的响应有多快。

它表示一个信号通过一个门时所经历的延时,定义为输入和输出波形的50%翻转点之间的时间。

上升和下降时间定义为在波形的10%和90%之间。

对于给定的工艺和门的拓扑结构,功耗和延时的乘积一般为一常数。

数字集成电路考试重点集成电路设计测试站点1。

填空1。

NML和NMH的概念,热电势,D触发器,D锁存器,施密特触发器低电平噪声容限:VIL-VOL高电平噪声容限:VOH-VIH该容限应大于零热电势:当两种不同的金属相互接触时,如果接触端和非接触端的温度不相等,两种金属之间产生的电势差称为热电势2.金属氧化物半导体晶体管的动态响应之间有什么关系?(本征电容P77)金属氧化物半导体晶体管的动态响应值取决于其充放电期间的本征寄生电容以及由互连线和负载引起的额外电容所需的时间本征电容的源极:基本金属氧化物半导体结构、沟道电荷和漏极以及源极反向偏置PN结耗尽区 3.设计技术(其他测试点与此知识点相似)P147如何降低栅极的传播延迟:降低CL:负载电容主要由以下三个主要部分组成:栅极本身的内部扩散电容、互连电容和扇出电容增加晶体管的纵横比并增加VDD 4。

具有比率逻辑和无与伦比的逻辑具有特定的逻辑:特定的逻辑试图减少实现给定逻辑功能所需的晶体管数量,但通常以降低稳定性和额外功耗为代价。

诸如之类的门不使用有源下拉和上拉网络的组合,而是由实现逻辑功能的NMOS下拉网络和简单的加载设备组成。

无与伦比的逻辑:逻辑电平独立于器件相对大小的门称为无与伦比的逻辑特定逻辑:逻辑电平由构成逻辑的晶体管的相对大小决定。

5. 时序电路的特点:记忆功能原理:(1)基本反馈;(b)电容储存电荷6。

信号完整性(电荷共享,泄漏)信号完整性问题:电荷泄漏电荷共享容性耦合时钟馈通7。

存储器和存储分类按存储模式分为随机存储器:任何存储单元的内容都可以随机访问,访问时间与存储单元的物理位置无关顺序存储器:只能按一定顺序访问,访问时间与存储单元的物理位置有关根据存储器的读写功能,它分为只读存储器:半导体存储器,其内容是固定的,只能读不能写。

随机存取存储器:可读写的半导体存储器根据信息的可存储性,可分为个非永久性存储器:断电后信息消失的存储器。

永久存储器:断电后仍能存储信息的存储器根据内存使用情况分为。

第一章 数字集成电路介绍第一个晶体管,Bell 实验室,1947第一个集成电路,Jack Kilby ,德州仪器,1958 摩尔定律:1965年,Gordon Moore 预言单个芯片上晶体管的数目每18到24个月翻一番。

(随时间呈指数增长)抽象层次:器件、电路、门、功能模块和系统 抽象即在每一个设计层次上,一个复杂模块的内部细节可以被抽象化并用一个黑匣子或模型来代替。

这一模型含有用来在下一层次上处理这一模块所需要的所有信息。

固定成本(非重复性费用)与销售量无关;设计所花费的时间和人工;受设计复杂性、设计技术难度以及设计人员产出率的影响;对于小批量产品,起主导作用。

可变成本 (重复性费用)与产品的产量成正比;直接用于制造产品的费用;包括产品所用部件的成本、组装费用以及测试费用。

每个集成电路的成本=每个集成电路的可变成本+固定成本/产量。

可变成本=(芯片成本+芯片测试成本+封装成本)/最终测试的成品率。

一个门对噪声的灵敏度是由噪声容限NM L (低电平噪声容限)和NM H (高电平噪声容限)来度量的。

为使一个数字电路能工作,噪声容限应当大于零,并且越大越好。

NM H = V OH - V IH NM L = V IL - V OL 再生性保证一个受干扰的信号在通过若干逻辑级后逐渐收敛回到额定电平中的一个。

一个门的VTC 应当具有一个增益绝对值大于1的过渡区(即不确定区),该过渡区以两个有效的区域为界,合法区域的增益应当小于1。

理想数字门 特性:在过渡区有无限大的增益;门的阈值位于逻辑摆幅的中点;高电平和低电平噪声容限均等于这一摆幅的一半;输入和输出阻抗分别为无穷大和零。

传播延时、上升和下降时间的定义传播延时tp 定义了它对输入端信号变化的响应有多快。

它表示一个信号通过一个门时所经历的延时,定义为输入和输出波形的50%翻转点之间的时间。

上升和下降时间定义为在波形的10%和90%之间。

对于给定的工艺和门的拓扑结构,功耗和延时的乘积一般为一常数。

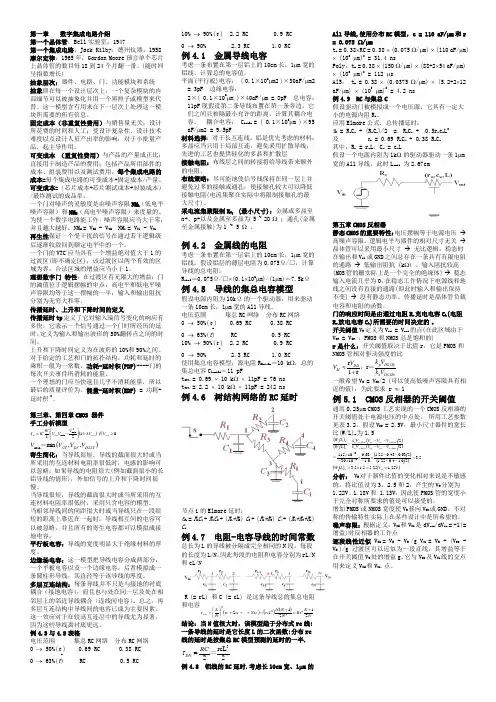

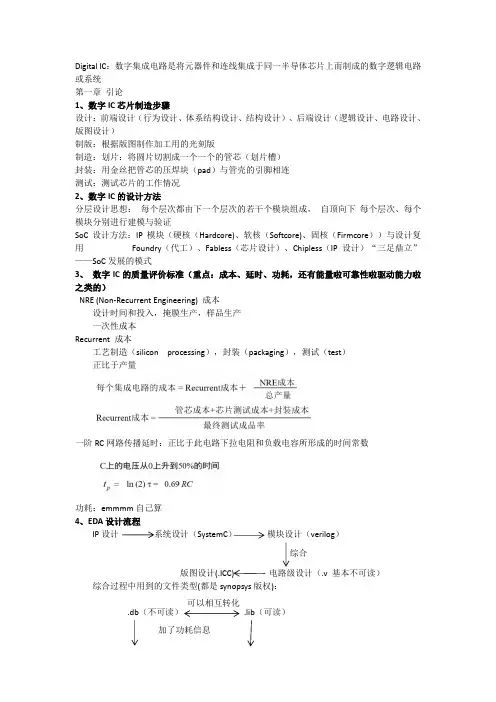

Digital IC:数字集成电路是将元器件和连线集成于同一半导体芯片上而制成的数字逻辑电路或系统第一章引论1、数字IC芯片制造步骤设计:前端设计(行为设计、体系结构设计、结构设计)、后端设计(逻辑设计、电路设计、版图设计)制版:根据版图制作加工用的光刻版制造:划片:将圆片切割成一个一个的管芯(划片槽)封装:用金丝把管芯的压焊块(pad)与管壳的引脚相连测试:测试芯片的工作情况2、数字IC的设计方法分层设计思想:每个层次都由下一个层次的若干个模块组成,自顶向下每个层次、每个模块分别进行建模与验证SoC设计方法:IP模块(硬核(Hardcore)、软核(Softcore)、固核(Firmcore))与设计复用Foundry(代工)、Fabless(芯片设计)、Chipless(IP设计)“三足鼎立”——SoC发展的模式3、数字IC的质量评价标准(重点:成本、延时、功耗,还有能量啦可靠性啦驱动能力啦之类的)NRE (Non-Recurrent Engineering) 成本设计时间和投入,掩膜生产,样品生产一次性成本Recurrent 成本工艺制造(silicon processing),封装(packaging),测试(test)正比于产量一阶RC网路传播延时:正比于此电路下拉电阻和负载电容所形成的时间常数功耗:emmmm自己算4、EDA设计流程IP设计系统设计(SystemC)模块设计(verilog)综合版图设计(.ICC) 电路级设计(.v 基本不可读)综合过程中用到的文件类型(都是synopsys版权):可以相互转化.db(不可读).lib(可读)加了功耗信息.sdb .slib第二章器件基础1、保护IC的输入器件以抗静电荷(ESD保护)2、长沟道器件电压和电流的关系:3、短沟道器件电压和电流关系速度饱和:当沿着沟道的电场达到临界值ξC时,载流子的速度由于散射效应(载流子之间的碰撞)而趋于饱和。

数集复习笔记By 潇然2018.6.29名词解释专项摩尔定律:一个芯片上的晶体管数目大约每十八个月增长一倍。

传播延时:一个门的传播延时t p定义了它对输入端信号变化的响应有多快。

它表示一个信号通过一个门时所经历的延时,定义为输入和输出波形的50%翻转点之间的时间。

由于一个门对上升和下降输入波形的响应时间不同,所以需定义两个传播延时。

t pLH定义为这个门的输出由低至高翻转的响应时间,而t pHL则为输出由高至低翻转的响应时间。

传播延时t p定义为这两个时间的平均值:t p=(t pLH+t pHL)/2。

设计规则:设计规则是指导版图掩膜设计的对几何尺寸的一组规定。

它们包括图形允许的最小宽度以及在同一层和不同层上图形之间最小间距的限制与要求。

定义设计规则的目的是为了能够很容易地把一个电路概念转换成硅上的几何图形。

设计规则的作用就是电路设计者和工艺工程师之间的接口,或者说是他们之间的协议。

速度饱和效应:对于长沟MOS管,载流子满足公式:υ = -μξ(x)。

公式表明载流子的速度正比于电场,且这一关系与电场强度值的大小无关。

换言之,载流子的迁移率是一个常数。

然而在(水平方向)电场强度很高的情况下,载流子不再符合这一线性模型。

当沿沟道的电场达到某一临界值ξc时,载流子的速度将由于散射效应(即载流子间的碰撞)而趋于饱和。

时钟抖动:在芯片的某一个给定点上时钟周期发生暂时的变化,即时钟周期在每个不同的周期上可以缩短或加长。

逻辑综合:逻辑综合的任务是产生一个逻辑级模型的结构描述。

这一模型可以用许多不同的方式来说明,如状态转移图、状态图、电路图、布尔表达式、真值表或HDL 描述。

噪声容限:为了使一个门的稳定性较好并且对噪声干扰不敏感,应当使“0”和“1”的区间越大越好。

一个门对噪声的灵敏度是由低电平噪声容限NM L 和高电平噪声容限NM H来度量的,它们分别量化了合法的“0”和“1”的范围,并确定了噪声的最大固定阈值:NM L =V IL - V OLNM H =V OH - V IH沟道长度调制:在理想情况下,处于饱和区的晶体管的漏端与源端的电流是恒定的,并且独立于在这两个端口上外加的电压。

Digital IC:数字集成电路是将元器件和连线集成于同一半导体芯片上而制成的数字逻辑电路或系统第一章引论1、数字IC芯片制造步骤设计:前端设计(行为设计、体系结构设计、结构设计)、后端设计(逻辑设计、电路设计、版图设计)制版:根据版图制作加工用的光刻版制造:划片:将圆片切割成一个一个的管芯(划片槽)封装:用金丝把管芯的压焊块(pad)与管壳的引脚相连测试:测试芯片的工作情况2、数字IC的设计方法分层设计思想:每个层次都由下一个层次的若干个模块组成,自顶向下每个层次、每个模块分别进行建模与验证SoC设计方法:IP模块(硬核(Hardcore)、软核(Softcore)、固核(Firmcore))与设计复用Foundry(代工)、Fabless(芯片设计)、Chipless(IP设计)“三足鼎立”——SoC发展的模式3、数字IC的质量评价标准(重点:成本、延时、功耗,还有能量啦可靠性啦驱动能力啦之类的)NRE (Non-Recurrent Engineering) 成本设计时间和投入,掩膜生产,样品生产一次性成本Recurrent 成本工艺制造(silicon processing),封装(packaging),测试(test)正比于产量一阶RC网路传播延时:正比于此电路下拉电阻和负载电容所形成的时间常数功耗:emmmm 自己算4、EDA 设计流程IP 设计SystemC 模块设计(verilog )版图设计电路级设计(.v 基本不可读)综合过程中用到的文件类型(都是synopsys 版权):.db .lib (可读).sdb .slib第2章 器件基础1、保护IC 的输入器件以抗静电荷(ESD 保护)2、长沟道器件电压和电流的关系:3、短沟道器件电压和电流关系速度饱和:当沿着沟道的电场达到临界值ξC时,载流子的速度由于散射效应(载流子之间的碰撞)而趋于饱和。

ξC取决于掺杂浓度和外加的垂直电场强度器件在V DS达到V GS --V T 之前就已经进入饱和状态,所以与相应的长沟道器件相比,短沟道器件饱和区范围更大反面整理P63 3.3.2 静态状态下的MOS晶体管相关参数以及公式(尤其是速度饱和)4、MOS管二阶效应阈值变化:随着器件尺寸的缩小,阈值电压变成与L、W、V DS有关短沟效应(漏端感应势垒降低(DIBL)):电压控制耗尽区宽度,V DS提高将会导致势垒降低,甚至过高的V DS将会导致源漏短路,称为源漏穿流窄沟效应:沟道耗尽区并不立即在晶体管边沿终止,而是会向绝缘场氧下面延伸一些,栅电压必须维持这一额外的耗尽电荷才能建立一条导电沟道,在W值较小时将会引起阈值电压升高亚阈值导通:在V GS接近甚至略小于V T时,I D仍然存在热载流子效应:原因:小尺寸器件中的强电场引起高能热电子与晶格碰撞产生电子空穴对,引起衬底电流;电子在强总校电厂的作用下穿过栅氧,引起栅电流。

数字集成电路设计复习提纲(1-7章)2021-121. 数字集成电路的本钱包括哪几局部?●NRE (non-recurrent engineering) costs固定本钱●design time and effort, mask generation●one-time cost factor●Recurrent costs重复性费用或可变本钱●silicon processing, packaging, test●proportional to volume●proportional to chip area2. 数字门的传播延时是如何定义的?一个门的传播延时tp定义了它对输入端信号变化的响应有多快。

3. 集成电路的设计规则(design rule)有什么作用?❑Interface between designer and process engineer❑Guidelines for constructing process masks❑Unit dimension: Minimum line width▪scalable design rules: lambda parameter (可伸缩设计规则,其缺乏:只能在有限的尺寸范围内进展。

)▪absolute dimensions (micron rules,用绝对尺寸来表示。

)4. 什么是MOS晶体管的体效应?5. 写出一个NMOS晶体管处于截止区、线性区、饱和区的判断条件,以及各工作区的源漏电流表达式〔考虑短沟效应即沟道长度调制效应,不考虑速度饱和效应〕注:NMOS晶体管的栅、源、漏、衬底分别用G、S、D、B表示。

6. MOS晶体管的本征电容有哪些来源?7. 对于一个CMOS反相器的电压传输特性,请标出A、B、C三点处NMOS管和PMOS管各自处于什么工作区?Out InV DDPMOSNMOS8. 在CMOS 反相器中,NMOS 管的平均导通电阻为R eqn ,PMOS 管的平均导通电阻为R eqp ,请写出该反相器的总传播延时定义。

数字电路复习资料数字电路复习资料1第一部分:基本要求和基本概念第一章半导体器件的基本知识一,基本建议1,了解半导体pn结的形成及特性,了解半导体二极管的开关特性及钳位作用。

2,介绍半导体三极管的输出特性和输出特性,熟识半导体三极管共发射极电路的三个工作区的条件及特点,掌控三极管开关电路分析的基本方法。

3,了解绝缘栅场效应管(mos)的结构、符号、工作原理及特性。

二,基本概念1,按导电率为可以把材料分成导体、绝缘体和半导体。

2,半导体中存有空穴和自由电子两种载流子。

3,清澈半导体称作本征半导体。

4,p型半导体中的多数载流子是空穴;少数载流子是自由电子。

5,n型半导体中的多数载流子是自由电子;少数载流子是空穴。

6,pn结是一个二极管,它具有单项导电性。

7,二极管电容由结电容和扩散电容构成。

8,二极管的截至条件就是vd<0.5v,导通条件就是vd≥0.7v。

9,三极管的截止条件是vbe<0.5v,截止的特点是ib=ic≈0;饱和条件是ib≥(ec-vces)/(βrc),饱和的特点是vbe≈0.7v,vce=vces≤0.3v。

第二章门电路一,基本要求1,熟识分立元件“与”“或”“非”“与非”“或非”门电路的工作原理、逻辑符号和功能。

2,熟悉ttl集成与非门的结构、工作原理及外部特性,熟悉oc门三态门和异或门的功能及主要用途,掌握各种门电路输出波形的画法。

2,熟识pmos门nmos门和cmos门的结构和工作原理,熟识cmos门的外部特性及主要特点,掌控mos门电路的逻辑功能的分析方法。

二,基本概念1,门是实现一些基本逻辑关系的电路。

2,三种基本逻辑就是与、或、非。

3,与门就是同时实现与逻辑关系的电路;或门就是同时实现或逻辑关系的电路;非门就是同时实现非逻辑关系的电路。

4,按集成度可以把集成电路分为小规模(ssi)中规模(msi)大规模(lsi)和超大规模(vlsi)集成电路。

5,仅有一种载流子参予导电的器件叫做单极型器件;存有两种载流子参予导电的器件叫做双极型器件。

集成电路设计考点1.填空题1.NM L和NM H的概念,热电势,D触发器,D锁存器,施密特触发器。

低电平噪声容限:VIL-VOL高电平噪声容限:VOH-VIH这一容限值应该大于零热电势:两种不同的金属相互接触时,其接触端与非接触端的温度假设不相等,那么在两种金属之间产生电位差称为热电势。

2.MOS晶体管动态响应与什么有关?〔本征电容P77〕MOS晶体管的动态响应值取决于它充放电这个期间的本征寄生电容和由互连线及负载引起的额外电容所需要的时间。

本征电容的来源:根本的MOS构造、沟道电荷以及漏和源反向偏置PN结的耗尽区。

3.设计技术〔其他考点与这种知识点类似〕P147怎样减小一个门的传播延时:减小CL:负载电容主要由以下三个主要局部组成:门本身的内部扩散电容、互连线电容和扇出电容。

增加晶体管的宽长比提高VDD4.有比逻辑和无比逻辑。

有比逻辑:有比逻辑试图减少实现有一个给定逻辑功能所需要的晶体管数目,但它经常以降低稳定性和付出额外功耗为代价。

这样的门不是采用有源的下拉和上拉网络的组合,而是由一个实现逻辑功能的NMOS 下拉网络和一个简单的负载器件组成。

无比逻辑:逻辑电平与器件的相对尺寸无关的门叫做无比逻辑。

有比逻辑:逻辑电平是由组成逻辑的晶体管的相对尺寸决定的。

5.时序电路的特点:记忆功能的原理:〔a〕根本反应;〔b〕电容存储电荷。

6.信号完整性。

〔电荷分享,泄露〕信号完整性问题:电荷泄露电荷分享电容耦合时钟馈通7.存储器与存储的分类按存储方式分随机存储器:任何存储单元的内容都能被随机存取,且存取时间和存储单元的物理位置无关。

顺序存储器:只能按某种顺序来存取,存取时间和存储单元的物理位置有关。

按存储器的读写功能分只读存储器(ROM):存储的内容是固定不变的,只能读出而不能写入的半导体存储器。

随机读写存储器(RAM):既能读出又能写入的半导体存储器。

按信息的可保存性分非永久记忆的存储器:断电后信息即消失的存储器。

数字集成电路复习 前言:看完后一定要自己默写一遍一. 确定组合逻辑延时最小时的尺寸?page186反相器:1,三输入与非门:5/3,二输入与非门:5/3输出负载是一个电容,其电容为第一级(最小尺寸的反相器)输入电容的5倍,因此该电路的等效扇出为1/5L g F C C ==二.用图解的方法得到电压传输特性曲线求解图中门的阈值电压V TN?三. 一个PMOS管的阈值电压为-0.4V,计算VSB=2.5V,20.6TV Φ=−时的阈值电压?Page64四. 绘制CMOS反相器的版图?五.一个CMOS反相器,Kr=1,VDD=5V,VTN=0.8V,VTP=-1V,Cox=4F/cm2,un=500cm2/Vs,up=200cm2/Vs.由逻辑阈值点确定的最大噪声容限为多少?六.根据如下的逻辑关系式合成CMOS逻辑门,画出原理图()=+⋅+F D A B C七.看版图,画原理图八.看图4,分别是什么器件,关键尺寸是多少?并写出详细的分析过程?九.补充内容(1).趋肤效应:与频率有关,高频电流倾向于主要在导体的表面流动,其电流密度随进入导体的深度而呈指数下降。

(2).噪声是指在逻辑节点上不希望发生的电压和电流的变化,一个门的稳态参数衡量的该电路对制造过程中发生偏差和噪声干扰的稳定性。

(3).噪声源的类型:与信号摆幅Vsw成正比的噪声。

它对信号节点的影响用gVsw来表示;固定噪声。

它对信号节点的影响等于fVnf,Vnf是噪声源的幅值,而f是从噪声到信号节点的传递函数。

(4).简述CMOS反相器噪声容限的定义:所谓噪声容限,是指电路在噪声干扰下,逻辑关系发生偏离的最大允许值,若输入信号中混入了干扰,当干扰大过反相器输入电压阈值时,则使原本应该是高电平的输出信号转化翻转为低电平,或使原本应该是低电平的输出信号翻转为高电平。

(5).扇入:一个门的扇入定义为该门输入的数目。

扇出:表示连接到驱动门输出端的负载门的数目N,增加一个门的扇出会影响它的逻辑输出电平。

集成电路考题一、填空题1、世界上第一个自动计算器是1832年。

2、Jack Kilby 提出IC 设想-—集成电路,由此获得诺贝尔奖,标志着数字时代的来临。

3、集成电路的发展按摩尔定律发展变化。

4、数字电路噪声进入的途径有电感耦合、电容耦合、电源和地的干扰。

5、N 型半导体的多子是自由电子,少子是空穴.6、P 型半导体的多子是空穴,少子是自由电子.7、二极管电流D I 与电压D V 的关系表达式为)1(/-=ΦT D V S D e I I 。

8、二极管的反向击穿类型有齐纳击穿和雪崩击穿。

9、互连线电容模型可用平行板电容模型等效,导线总电容的公式为10、互连线电容模型可用微带线模型等效,由平面电容和边缘电容构成。

11、导体为均匀的绝缘介质包围,可知一条导线的电容C 与电感L 的关系为u CL ε=。

12、CMOS 反相器噪声容限的定义有L NM 低电平噪声容限和H NM 高电平噪声容限.13、CMOS 反相器电路总功耗分为三部分,分别为dyn P 由充放电电容引起的动态功耗、dp P 直流通路电容引起的功耗、stat P 静态功耗。

14、静态CMOS 门由上拉网络PUN 和下拉网络PDN 构成。

15、CMOS 互补逻辑实现一个N 输入逻辑门所需MOS 管的个数为2N 个。

16、伪NMOS 逻辑实现一个N 输入逻辑门所需MOS 管的个数为N+1个。

17、动态逻辑实现一个N 输入逻辑门所需MOS 管的个数为N+2个。

18、动态逻辑电路工作过程分为预充电和求值两个阶段。

19、时序电路中与寄存器有关的参数分别为建立时间、维持时间、传播时间。

20、对于时钟偏差不敏感的触发器为Clocked CMOS (或为时钟控制CMOS )。

21、2C CMOS 实现一个N 输入逻辑门所需MOS 管的个数为N+2个。

2223、半定制的电路设计方法分别是以单元为基础的设计方法和以阵列为基础的设计方法。

二、简答题1、画出双阱CMOS电路工艺顺序简化图.(P31)2、二极管的电流受工作温度的双重影响。