PADS9.2 中 BGA Fanout(扇出)教程

- 格式:pdf

- 大小:401.96 KB

- 文档页数:5

光映科技官方技術論壇

歡迎您的參與這是一個EDA開發設計的討論園地

Altium Designer:Fanout (扇出) 功能介紹 (PDF檔案下載,6頁)+線上動畫

相關文章相關文章::

Altium Designer :整合式零件庫 (版本:Protel DXP 後才適用)(PDF 檔案下載,6頁)

/forums/post/1637.aspx

Altium Designer Summer 09:改進的零件清單/物料清單(BOM 表)(Bills of Material)

/forums/post/2270.aspx

Altium Designer :提供Supplier Search 功能.讓您輕鬆找到所需的零件資訊

/forums/post/1866.aspx

Altium Designer :零件.自動佈置/擺置功能 (Placement)

/forums/post/1959.aspx

Altium Designer :多邊形鋪銅管理系統Copper Pour (polygon) Management System

/forums/post/1470.aspx

Altium Designer :支援PCB 鋪銅–多邊形/實心鋪銅 (PCB copper plane support - Solid Polygon Pour) /forums/post/1422.aspx

Altium Designer Layout :多邊形物件放置和編輯;去定義多邊形的形狀(Define polygon)

/forums/post/1370.aspx。

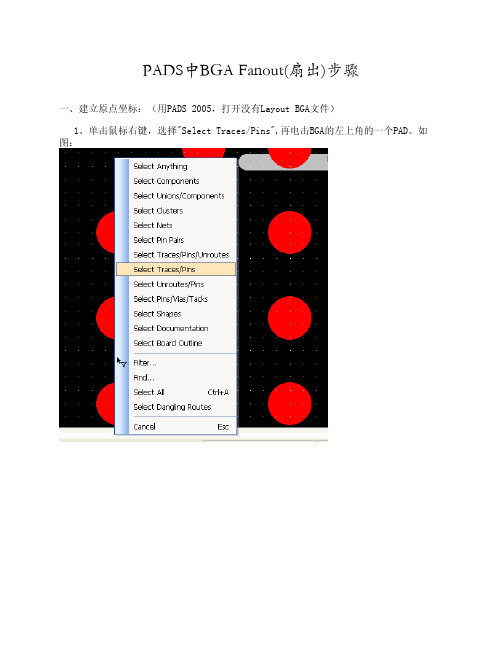

PADS中BGA Fanout(扇出)步骤一、建立原点坐标:(用PADS 2005,打开溡有Layout BGA文件)1、单击鼠标右键,选择"Select Traces/Pins",再电击BGA的左上角的一个PAD。

如图:2、以这个PAD建立原点坐标。

Setup/Set Origin。

如图:选择“是(Y)”。

二、选择BGA Fanout的幂:1、Setup/Layer Definition...。

如图:2、在Layers Serup里选择BGA所在幂(BGA一般放在TOP Component幂)。

Plane Typet选No Plane, Routing选Any,然后点击“OK”。

如图:三、设置Fanout的栅格Grid1、单击Tools/Options...。

如图:2、再弹出的"Options"对话框中选择"Grids"。

(设置成PAD与PAD的二分之一。

这BGA的PAD与PAD的间距是0.7MM。

所以,X与Y设置的是0.35MM。

)设置完后点击"OK"。

如图:2、设置布线宽度及安全间距:1)、Tools/PADS Router...。

如图:2)、在弹出来的"PADS Router Link"。

" Action"里选择"Open PADS Router". "Options"里选择"Routing"。

然后点击"Proceed"。

如图:四、在PADS Router界面1、选择合适的BGA Fanout的VIA。

1)、在PADS Router中,Edit/Properties...。

如图:2)、弹出"Design Properties"对话框,选择"Via Biasing"选项,选择一个Via。

BGA是PCB上常用的组件,通常CPU、NORTH BRIDGE、SOUTH BRIDGE、AGP CHIP、CARD BUS CHIP…等,大多是以bga的型式包装,简言之,80﹪的高频信号及特殊信号将会由这类型的package内拉出。

因此,如何处理BGA package的走线,对重要信号会有很大的影响。

通常环绕在BGA附近的小零件,依重要性为优先级可分为几类:1. by pass。

2. clock终端RC电路。

3. damping(以串接电阻、排组型式出现;例如memory BUS信号)4. EMI RC电路(以dampin、C、pull height型式出现;例如USB信号)。

5. 其它特殊电路(依不同的CHIP所加的特殊电路;例如CPU的感温电路)。

6. 40mil以下小电源电路组(以C、L、R等型式出现;此种电路常出现在AGP CHIP or含AGP功能之CHIP附近,透过R、L分隔出不同的电源组)。

7. pull low R、C。

8. 一般小电路组(以R、C、Q、U等型式出现;无走线要求)。

9. pull height R、RP。

1-6项的电路通常是placement的重点,会排的尽量靠近BGA,是需要特别处理的。

第7项电路的重要性次之,但也会排的比较靠近BGA。

8、9项为一般性的电路,是属于接上既可的信号。

相对于上述BGA附近的小零件重要性的优先级来说,在ROUTING上的需求如下:1.by pass =>与CHIP同一面时,直接由CHIP pin接至by pass,再由by pass拉出打via接plane;与CHIP不同面时,可与BGA的VCC、GND pin共享同一个via,线长请勿超越100mil。

2.clock终端RC电路=>有线宽、线距、线长或包GND等需求;走线尽量短,平顺,尽量不跨越VCC分隔线。

3.damping=>有线宽、线距、线长及分组走线等需求;走线尽量短,平顺,一组一组走线,不可参杂其它信号。

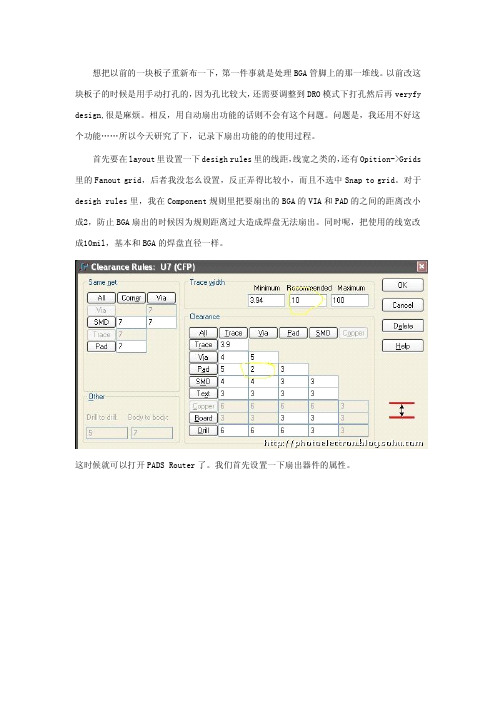

想把以前的一块板子重新布一下,第一件事就是处理BGA 管脚上的那一堆线。

以前改这块板子的时候是用手动打孔的,因为孔比较大,还需要调整到DRO 模式下打孔然后再veryfy design,很是麻烦。

相反,用自动扇出功能的话则不会有这个问题。

问题是,我还用不好这个功能……所以今天研究了下,记录下扇出功能的的使用过程。

首先要在layout 里设置一下desigh rules 里的线距,线宽之类的,还有Opition->Grids 里的Fanout grid,后者我没怎么设置,反正弄得比较小,而且不选中Snap to grid。

对于desigh rules 里,我在Component 规则里把要扇出的BGA 的VIA 和PAD 的之间的距离改小成2,防止BGA 扇出的时候因为规则距离过大造成焊盘无法扇出。

同时呢,把使用的线宽改成10mil,基本和BGA 的焊盘直径一样。

这时候就可以打开PADS Router 了。

我们首先设置一下扇出器件的属性。

中国华录因为之前在layout 里设置的Component 规则和Default 规则有些地方不一样,所以相应的选项卡上会有一个红圈指示。

像我这里,Default 规则推荐的布线宽度是6,Component 规则则是10。

有关扇出的设置还关系到两个选项,一个是Via Biasing,一个是Fanout。

首先看一下Via Biasing。

因为一个PCB 里肯定不止一个过孔,所以我们需要在这里设置一下扇出时需要使用的过孔,中国华录我这里选择的是STANDARDVIA,将其它不使用的过了勾选掉。

对于Fanout 选项中,我们有很多设置,对于For pins on,我们勾选上Plane nets 和Signal nets,确保所有的信号均可以扇出。

而对于Allow multiple connection to,我一开始有些不太懂。

不过无所谓,试试就知道了。

Fanout length 呢,也就是扇出的长度。

Altium Designer BGA扇出,原理图中PCB的类和布线规则设置技巧第一,Altium Designer 认识了这么久,没有用过他的自动扇出功能,今天一试,效果还算不错,不过现在还没有找到不扇出没有网络的引脚的方法,我现在讲我的自动扇出步骤给大家说一下,在BGA 上面点击右键,选择component atcions 然后选择fanout component,这是会弹出一个对话框,你要是不想要BGA的外边焊盘扇出过孔的话就把第二个选项取消掉,然后选择OK就可以了。

要是自动扇出不成功,有两个原因,一个是布线规则设置的问题,要是想试用BGA扇出功能,那么你就讲Clearance规则全部取消,然后照前面的步骤操作就可以看到扇出效果图。

还有一个原因就是你的BGA上面已经有手工的pad扇出,或者连线。

还有一种BGA扇出的方法是在自动布线的选项里面auto route然后选择fanout 这类你可以选择你需要扇出的类型,包括pad、component、net、room等等。

第二,就是原理图class类的设置,directives然后选择blanket,这时鼠标会变成十字状态,这时你可以选择你要设置的class类的网络范围,这个虚线的红色框选中的的类型包括里面的网络标号、元件引脚、tacke等,这时你还可以在这个directives里面放置其他规则,包括class名称,布线规则等内容。

PADS中BGA Fanout扇出教程一、建立原点座标:(用PADS 2005 打开没有layout BGA文件) 1.鼠标右键,点选Select Traces/Pins,再点BGA的左上角的一个PAD 2.以这个PAD建立原点座标,Setup/origin. 二、选择BGA FANOUT 的层: Setup/Layers Setup,BGA 一般放在TOP Component 层,Plane Typet 选No一、建立原点座标:(用PADS 2005 打开没有layout BGA文件)1.鼠标右键,点选"Select Traces/Pins",再点BGA的左上角的一个PAD2.以这个PAD建立原点座标,Setup/origin.二、选择BGA FANOUT 的层:Setup/Layers Setup,BGA一般放在TOP Component 层,Plane Typet 选No Plane ,Routing 选 Any,然后“OK”。

扇入/扇出封装工艺一、Fanout工艺1.数字系统中定义,该模块直接调用的下级模块的个数。

扇出大表示模块的复杂度高,需要控制和协调过多的下级模块。

必须有一个单一的TTL逻辑门来驱动10个以上的其他门或驱动器。

被称为缓冲器的驱动器可以用在TTL逻辑门与它必须驱动的多重驱动器之间,此类型缓冲器有25至30个扇出信号。

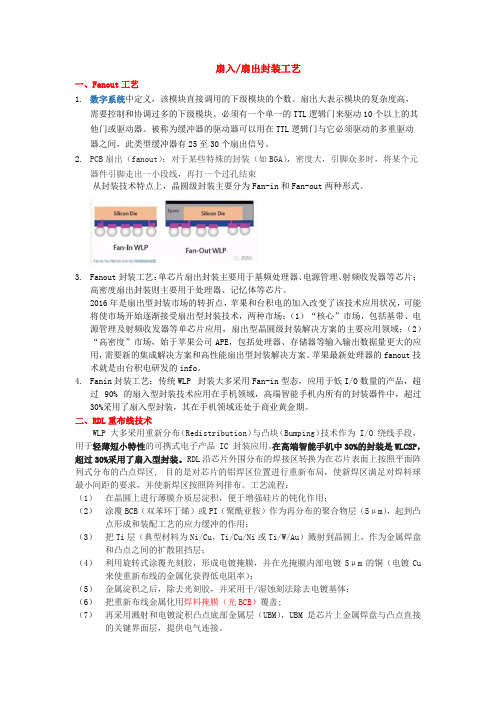

2.PCB扇出(fanout):对于某些特殊的封装(如BGA),密度大,引脚众多时,将某个元器件引脚走出一小段线,再打一个过孔结束从封装技术特点上,晶圆级封装主要分为Fan-in和Fan-out两种形式。

3.Fanout封装工艺:单芯片扇出封装主要用于基频处理器、电源管理、射频收发器等芯片;高密度扇出封装则主要用于处理器、记忆体等芯片。

2016年是扇出型封装市场的转折点,苹果和台积电的加入改变了该技术应用状况,可能将使市场开始逐渐接受扇出型封装技术,两种市场:(1)“核心”市场,包括基带、电源管理及射频收发器等单芯片应用,扇出型晶圆级封装解决方案的主要应用领域;(2)“高密度”市场,始于苹果公司APE,包括处理器、存储器等输入输出数据量更大的应用,需要新的集成解决方案和高性能扇出型封装解决方案。

苹果最新处理器的fanout技术就是由台积电研发的info。

4.Fanin封装工艺:传统WLP 封装大多采用Fan-in型态,应用于低I/O数量的产品,超过90% 的扇入型封装技术应用在手机领域,高端智能手机内所有的封装器件中,超过30%采用了扇入型封装,其在手机领域还处于商业黄金期。

二、RDL重布线技术WLP 大多采用重新分布(Redistribution)与凸块(Bumping)技术作为 I/O 绕线手段,用于轻薄短小特性的可携式电子产品 IC 封装应用。

在高端智能手机中30%的封装是WLCSP,超过30%采用了扇入型封装。

RDL沿芯片外围分布的焊接区转换为在芯片表面上按照平面阵列式分布的凸点焊区, 目的是对芯片的铝焊区位置进行重新布局,使新焊区满足对焊料球最小间距的要求,并使新焊区按照阵列排布。

CadenceAllegroBGA扇出设置1.菜单栏选择 Route -- Create Fanout2.Find栏⽬中选择Symbols3.Options中via Direction选择BGA Quadrant Style。

勾选上override line width。

填上合适的线宽或者不勾选override line width,⽽是选择合适的焊盘即可注意:Allegro⼀开始的时候via是Net default的,并没有焊盘给你选择,如下图这个需要在规则中设置⼀下焊盘,打开约束管理器选择Constraint Manager-->Physical -->Physical Constraint Set-->All layers,找到vias选项,给他对应的焊盘即可。

4.点击需要扇出的BGA器件即可BGA器件扇出如果Pin-Via Space不选择Centered的话,可能是会报错的,⽐如是这样的满满的都是DRC Mark,提⽰你出错了。

(DRC Mark点原本是很⼤的,可以改⼩⼀点,⽅便查看.点击Setup -- Design Parameters)去修改他的DRC Mark Size.要解决这个问题,就需要去修改Allegro BGA区域规则。

将BGA这块区域允许的最⼩间距给他缩⼩⼀些。

建议Pin-via Space选择Centered。

不⽤修改规则不会报错。

————————————————版权声明:本⽂为CSDN博主「⽂鸿开源⼯作室」的原创⽂章,遵循CC 4.0 BY-SA版权协议,转载请附上原⽂出处链接及本声明。

原⽂链接:https:///qq_38376586/java/article/details/86754364。

焊盘连线的扇出方式张明龙1. 焊盘我们在设计PCB时,焊盘的形状一般都是规则的,如BGA的焊盘是圆形的、QFP的焊盘是长圆形的、CHIP件的焊盘是矩形的等。

但实际做出的PCB,焊盘却不规则,可以说是奇形怪状。

以1608电阻封装的焊盘为例,如图1所示的焊盘,是规则的矩形焊盘。

但有0.4mm宽的线走出后,再加上生产工艺偏差,变成图2所示的实际焊盘,是原矩形焊盘的基础上加了一个小矩形焊盘组成的,不规则。

图1中,白色为丝印,红黄色为焊盘,黄色为阻焊开窗,深绿色为阻焊。

图2中,绿色为走线。

图1. 设计的焊盘图2. 实际的焊盘2. 不规则焊盘的不良影响在1608电阻封装的两个焊盘对角分别走0.6mm宽的线,加上PCB生产精度造成的阻焊偏差(阻焊窗单边比焊盘大0.1mm),会形成如图3所示的焊盘。

在这样的情况下,电阻焊接时由于焊锡表面张力的作用,会出现如图4一样的不良旋转。

图3. 连线对角扇的方式3. 如何减小CHIP元件贴装后的不良旋转。

如图4,元件贴装后出现不良旋转的根本原因是焊盘的形状和大小发生了变化。

发生变化的原因在于PCB的加工工艺精度,无法保证阻焊油墨刚好不印在焊盘上,即必须适当放大阻焊开窗,加工精度越高开窗可以越小。

所以要减小CHIP 元件贴装后的不良旋转,PCB设计时就应该尽量缩小阻焊开窗。

一般可以将阻焊开窗设为比焊盘单边大0.05mm。

采用合理的布线方式,如图5所示,焊盘连线采用关于长轴对称的扇出方式,可以比较有效地减小CHIP元件贴装后的不良旋转。

如果焊盘扇出的线也关于短轴对称,还可以减小CHIP元件贴装后的漂移。

从减小CHIP元件贴装后的不良旋转的角度讲,焊盘扇出的线路越细越好。

图5. 焊盘连线的对称扇出方式。

PADS9.2中BGA Fanout(扇出)教程一、建立原点坐标:(用PADS 9.2 打开layout BGA文件)1、选择BGA的左上角的一个PAD;2、以这个PAD建立原点坐标。

Setup/Set Origin。

如图:选择“是(Y)”。

二、选择BGA Fanout的层:1、Setup/Layer Definition...如图:2、在Layers Setup里选择BGA所在层(BGA一般放在TOP Component层)。

Plane Type 选No Plane,Routing选Any,然后点击“OK”。

如图:三、设置Fanout的栅格Grid1、单击Tools/Options...或者快捷组合键Ctrl+Enter,调出Options对话框;2、在弹出的“Options”对话框中选择“Grids”,在Fanout grid里设置成PAD与PAD的二分之一。

如果BGA的PAD与PAD的间距是0.8mm,这时,X与Y设置的是0.4mm。

设置完后点击“ApplyàOK”。

如图:3、同步转到Pads Router中进行设置。

四、在PADS9.2 Router界面1、选择合适的BGA FANOUT的Via过孔类型在PADS ROUTER中,Edit/Properties,调出Design Properties,选择Via Biasing 选项从中选择一个Via(如果没有适合的Via,要在PADS Layout中建立一个比较小的Via)。

2、选择BGA FANOUT的规则选择“Fanout”选项,“Create fanouts”里选择“Plane nets”(Via可以连接到中间平面层)和“Signal nets”(Via可以连接到当前层);“Fanout length”里选Maximum填最大的Fanout长度(如:0.7),默认选择Unlimited;“Placement of via fanout for”里选择“BGA“;“Alignment”里选择Fanout扇出的方向。

1、BGA扇出方法

PADS中BGA扇出有两种方法:手工和自动

一、手工扇出:

1、测量BGA两个焊盘之间的间距;

2、设置扇出栅格,扇出栅格的大小为BGA焊盘间距的1/2;

3、将布线结束方式设置为以孔结束;

4、设置布线结束时孔的类型及大小,通常设置为通孔。

二、自动扇出:

注意:扇出之前必须要给板子添加board outling边框,否则将无法再router中扇出。

过孔太大也无法扇出。

1、进入“router”模式,单击或双击BGA元器件进入“设计特性”设置,如下图

所示:

2、选择“扇出”选项,选择“BGA”,设置如下:

3、选择“扇出”选项,将栅格中的项目全部不选;

4、选择“过孔”选项,将过孔类型选择为BGA布线时的过孔,一般孔径为0.25mm;

5、以上步骤设置完成后,选中要扇出的BGA(可以选多个BGA),单击右键,选择“扇

出”。

6、自动扇出没有完成的焊盘,可以通过手工扇出的方法完成。

PADS9.2中BGA Fanout(扇出)教程

一、建立原点坐标:(用PADS 9.2 打开layout BGA文件)

1、选择BGA的左上角的一个PAD;

2、以这个PAD建立原点坐标。

Setup/Set Origin。

如图:

选择“是(Y)”。

二、选择BGA Fanout的层:

1、Setup/Layer Definition...如图:

2、在Layers Setup里选择BGA所在层(BGA一般放在TOP Component层)。

Plane Type 选No Plane,Routing选Any,然后点击“OK”。

如图:

三、设置Fanout的栅格Grid

1、单击Tools/Options...或者快捷组合键Ctrl+Enter,调出Options对话框;

2、在弹出的“Options”对话框中选择“Grids”,在Fanout grid里设置成PAD与PAD的二分之一。

如果BGA的PAD与PAD的间距是0.8mm,这时,X与Y设置的是0.4mm。

设置完后点击“ApplyàOK”。

如图:

3、同步转到Pads Router中进行设置。

四、在PADS9.2 Router界面

1、选择合适的BGA FANOUT的Via过孔类型

在PADS ROUTER中,Edit/Properties,调出Design Properties,选择Via Biasing 选项从中选择一个Via(如果没有适合的Via,要在PADS Layout中建立一个比较小的Via)。

2、选择BGA FANOUT的规则

选择“Fanout”选项,

“Create fanouts”里选择“Plane nets”(Via可以连接到中间平面层)和“Signal nets”(Via可以连接到当前层);

“Fanout length”里选Maximum填最大的Fanout长度(如:0.7),默认选择Unlimited;

“Placement of via fanout for”里选择“BGA“;

“Alignment”里选择Fanout扇出的方向。

3、选择“Same net”选项。

“Via at SMD placement”中把"Allow vias on surface mount"关掉。

然后“ApplyàOK”。

4、选种BGA封装/右击选择“Fanout”,如图:

也可单独选择BGA的一个PAD,然后右键Fanout,仅对选中的PAD进行扇出,如图:

五、如没扇出请把DRC关掉(尤其是“DRC Filter”里的“Clearance”)再试一次。

如图:

当满足设定的规则(线宽、线距离等)时,却无法实现Fanout操作,一般是因为没有勾选Signal nets选项,或者Fanout length有限制。