实现数据转换器的接地并解开AGND和DGND的谜团(MT-031)

- 格式:doc

- 大小:933.50 KB

- 文档页数:22

Rev.0Circuits from the Lab™ circuits from Analog Devices have been designed and built by Analog Devices engineers. Standard engineering practices have been employed in the design and construction of each circuit, and their function and performance have been tested and verified in a lab environment atroom temperature. However, you are solely responsible for testing the circuit and determining its suitability and applicability for your use and application. Accordingly, in no event shall Analog Devices be liable for direct, indirect, special, incidental, consequential or punitive damages due to any cause One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: /zh电路笔记CN-0213连接/参考器件16位、250 kSPS PulSAR® ADC,采用MSOP/QFN封装AD7685Circuit from the Lab™实验室电路是经过测试的电路设计,用于解决常见的设计挑战,方便设计人员轻松快捷地实现系统集成。

DA转换电路的设计实验十 D / A 、A / D 转换器一、实验目的1、了解D / A 和A / D 转换器的基本工作原理和基本结构2、掌握大规模集成D / A 和A / D 转换器的功能及其典型应用二、实验原理在数字电子技术的很多应用场合往往需要把模拟量转换为数字量,称为模 / 数转换器(A / D转换器,简称ADC );或把数字量转换成模拟量,称为数 / 模转换器(D / A 转换器,简称DAC )。

完成这种转换的线路有多种,特别是单片大规模集成A / D 、D / A 转换器问世,为实现上述的转换提供了极大的方便。

使用者可借助于手册提供的器件性能指标及典型应用电路,即可正确使用这些器件。

本实验将采用大规模集成电路DAC0832实现D / A 转换,ADC0809实现A / D 转换。

1、 D / A 转换器DAC0832DAC0832是采用CMOS 工艺制成的单片电流输出型8位数 / 模转换器。

图10-1是DAC0832的逻辑框图及引脚排列。

图10-1 DAC0832单片D/A 转换器逻辑框图和引脚排列器件的核心部分采用倒T 型电阻网络的8位D / A 转换器,如图10-2所示。

它是由倒T 型R -2R 电阻网络、模拟开关、运算放大器和参考电压V REF 四部分组成。

图10-2 倒T 型电阻网络D / A 转换电路运放的输出电压为 ++=----2n 2n 1n 1n nfREF O 2D 2(D R2R V V ···…0·2D 0+) 由上式可见,输出电压V O 与输入的数字量成正比,这就实现了从数字量到模拟量的转换。

一个8位的D / A 转换器,它有8个输入端,每个输入端是8位二进制数的一位,有一个模拟输出端,输入可有28=256个不同的二进制组态,输出为256个电压之一,即输出电压不是整个电压范围内任意值,而只能是256个可能值。

DAC0832的引脚功能说明如下: D 0-D 7 :数字信号输入端ILE:输入寄存器允许,高电平有效CS:片选信号,低电平有效1WR:写信号1,低电平有效XFER:传送控制信号,低电平有效2WR:写信号2,低电平有效I OUT1,I OUT2:DAC电流输出端R fB:反馈电阻,是集成在片内的外接运放的反馈电阻V REF:基准电压(-10~+10)VV CC:电源电压(+5~+15)VAGND:模拟地>可接在一起使用NGND:数字地DAC083210-3所示。

电路笔记CN-0348Circuits from the Lab™ reference circuits are engineered and tested for quick and easy s ystem integration to help solve today’s analog, mixed-signal, and RF design challenges. For more information and/or support, visit /CN0348.连接/参考器件AD5541A 串行输入、电压输出、无缓冲型16位DAC ADA4500-2 轨到轨输入/输出、零输入交越失真放大器ADR4550超低噪声、高精度5 V 基准电压源16位单电源缓冲电压输出数模转换,积分和微分非线性误差小于±1 LSBRev. 0C i r cu i t s fr o m t h e Lab ™ ci r cu i t s fr o m An al o gD evi ces h ave b een d esi g n ed an d b u i l t b y An al o g D evi ces en g i n eer s. St an d ar d en g i n eer i n g p r act i ces h ave b een emp l o yed i n t h e d esi g n an d co n st r u ct i o n o f each ci r cu i t , an d t h ei r fu n ct i o n an d p er fo r man ce h ave b een t est ed an d ver i ed i n a l ab en vi r o n men t at r o o m t emp er at u r e. H o wever , yo u ar e so l el y r esp o n si b l e fo r t est i n g t h e ci r cu i t an d d et er mi n i n g i t s su i t ab i l i t y an d ap p l i cab i l i t y fo r yo u r u se an d ap p l i cat i o n . Acco r d i n g l y, i n n o even t sh al l An al o g D evi ces b e l i ab l e fo r d i r ect , i n d i r ect , sp eci al , i n ci d en t al , co n seq u en t i al o r p u n i t i ve d amag es d u e t o an y cau se wh at so ever co n n ect ed t o t h e u se o f an y C i r cu i t s fr o m t h e Lab ci r cu i t s. (C o n t i n u ed o n l ast p ag e)One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 www Fax: 781.461.3113 ©2014 Analog Devices, Inc. All rights reserved.ADR4550CS DIN SCLK LDAC3.3VV LOGIC V DDV OUTREF AGNDDGNDSERIAL INTERFACEAD5541AADA4500-26V5V11994-001V INGNDV OUT0.1µF0.1µF1µFVOUT图1. ±1 LSB 线性16位缓冲电压输出DAC(原理示意图,未显示去耦和所有连接)评估和设计支持电路评估板CN-0348电路评估板(EVAL-CN0348-SDPZ)系统演示平台(EVAL-SDP-CB1Z)设计和集成文件原理图、布局文件、物料清单电路功能与优势图1所示电路是一款完整的单电源16位缓冲电压输出DAC ,它利用一个CMOS DAC 和一个无交越失真的创新放大器将积分和微分非线性误差保持在±1 LSB 。

MT-031指南实现数据转换器的接地并解开“AGND”和“DGND”的谜团作者:Walt Kester、James Bryant、Mike Byrne简介目前的信号处理系统一般需要混合信号器件,例如模数转换器(ADC)、数模转换器(DAC)和快速数字信号处理器(DSP)。

由于需要处理宽动态范围的模拟信号,因此拥有高性能ADC和DAC显得更加重要。

在恶劣的数字环境内,能否保持宽动态范围和低噪声与采用良好的高速电路设计技术密切相关,包括适当的信号路由、去耦和接地。

过去,一般认为“高精度、低速”电路与所谓的“高速”电路有所不同。

对于ADC和DAC,采样(或更新)频率一般用作区分速度标准。

不过,以下两个示例显示,实际操作中,目前大多数信号处理IC真正实现了“高速”,因此必须作为此类器件来对待,才能保持高性能。

DSP、ADC和DAC均是如此。

所有适合信号处理应用的采样ADC(内置采样保持电路的ADC)均采用具有快速上升和下降时间(一般为数纳秒)的高速时钟工作,即使吞吐量看似较低也必须视为高速器件。

例如,中速12位逐次逼近型(SAR) ADC可采用10 MHz内部时钟工作,而采样速率仅为500 kSPS。

Σ-Δ型ADC具有高过采样比,因此还需要高速时钟。

即使是高分辨率、所谓的“低频”Σ-Δ工业测量ADC(吞吐速率10 Hz至7.5 kHz)也采用5 MHz或更高时钟工作,并且提供高达24位的分辨率(例如ADI公司的AD77xx系列)。

更复杂的是,混合信号IC具有模拟和数字两种端口,因此如何使用适当的接地技术就更加茫然。

此外,某些混合信号IC具有相对较低的数字电流,而另一些具有高数字电流。

许多情况下,两种类型必须区分对待,才能实现最佳接地。

数字和模拟设计工程师倾向于从不同角度考察混合信号器件,本教程旨在确立适用于大多数混合信号器件的一般接地原则,而不必了解内部电路的具体细节。

接地层和电源层 保持低阻抗大面积接地层对目前所有的模拟和数字电路都很重要。

AD与DA转换实验报告一.实验目的⑴掌握A/D转换与单片机接口的方法;⑵了解A/D芯片0809转换性能及编程方法;⑶通过实验了解单片机如何进行数据采集。

⑷熟悉DAC0832 内部结构及引脚。

⑸掌握D/A转换与接口电路的方法。

⑹通过实验了解单片机如何进行波形输出。

二.实验设备装有proteus的电脑一台三.实验原理及内容1.数据采集_A/D转换(1)原理①ADC0809由一个8路模拟开关、一个地址锁存与译码器、一个A/D转换器和一个三态输出锁存器组成。

多路开关可选通8个模拟通道,允许8路模拟量分时输入,共用A/D转换器进行转换。

三态输出锁器用于锁存A/D转换完的数字量,当OE端为高电平时,才可以从三态输出锁存器取走转换完的数据。

②ADC0809引脚结构:D7 ~ D0:8位数字量输出引脚。

IN0 ~ IN7:8位模拟量输入引脚。

VCC:+5V工作电压。

GND:地。

REF(+):参考电压正端。

REF(-):参考电压负端。

START:A/D转换启动信号输入端。

ALE:地址锁存允许信号输入端。

(以上两种信号用于启动A/D转换).EOC:转换结束信号输出引脚,开始转换时为低电平,当转换结束时为高电平。

OE:输出允许控制端,用以打开三态数据输出锁存器。

CLK:时钟信号输入端(一般为500KHz)。

A、B、C:地址输入线。

(2)内容和步骤1.硬件电路设计:设计基于单片机控制的AD转换应用电路。

AD转换芯片采用ADC0809。

ADC0809的通道IN3输入0-5V之间的模拟量,通过ADC0809转换成数字量在数码管上以十进制形成显示出来。

ADC0809的VREF接+5V电压。

2. 软件设计:程序设计内容(1) 进行A/D转换时,采用查询EOC的标志信号来检测A/D转换是否完毕,经过数据处理之后在数码管上显示。

(2) 进行A/D转换之前,要启动转换的方法:ABC=110选择第三通道。

ST=0,ST=1,ST=0产生启动转换的正脉冲信号2.D/A转换及数字式波形发生器(1)原理典型D/A转换DAC0832芯片V cc 芯片电源电压, +5V ~+15V VREF 参考电压, -10V ~+10VRFB 反馈电阻引出端, 此端可接运算放大器输出端 AGND 模拟信号地 DGND 数字信号地DI7~ DI0数字量输入信号。

单片机原理与接口技术教材习题全部解答第1章绪论1-1解答:第一台计算机的研制目的是为了计算复杂的数学难题。

它的特点是:计算机字长为12位,运算速度为5 000次/s,使用18 800个电子管,1 500个继电器,占地面积为150 m2,重达30 t,其造价为100多万美元。

它的诞生,标志着人类文明进入了一个新的历史阶段。

1-2解答:单片微型计算机简称单片机。

一个完整的单片机芯片至少有中央处理器(CPU)、随机存储器(RAM)、只读存储器(ROM)、定时/计数器与I/O接口等部件。

1-3解答:单片机的发展大致经历了四个阶段:第一阶段(1970—1974年),为4位单片机阶段;第二阶段(1974—1978年),为低中档8位单片机阶段;第三阶段(1978—1983年),为高档8位单片机阶段;第四阶段(1983年至今),为8位单片机巩固发展阶段与16位单片机、32位单片机推出阶段。

1-4解答:Intel公司的MCS-48系列、MCS-51系列、MCS-96系列产品;Motorola公司的6801、6802、6803、6805、68HC11系列产品;Zilog公司的Z8、Super8系列产品;Atmel公司的AT89系列产品;Fairchild公司的F8和3870系列产品;TI公司的TMS7000系列产品;NS公司的NS8070系列产品;NEC公司的μCOM87(μPD7800)系列产品;National公司的MN6800系列产品;Hitachi公司的HD6301、HD63L05、HD6305。

1-5解答:(1)8031/8051/8751三种型号,称为8051子系列。

8031片没有ROM,使用时需在片外接EPROM。

8051片含有4KB的掩模ROM,其中的程序是生产厂家制作芯片时烧制的。

8751片含有4KB的EPROM,用户可以先用紫外线擦除器擦除,然后再利用开发机或编程器写入新的程序。

(2)8032A/8052A/8752A是8031/8051/8751的增强型,称为8052子系列。

第2章 习题参考答案1.什么是接口、接口技术和过程通道? 答:接口是计算机与外设交换信息的桥梁,包括输入接口和输出接口。

接口技术是研究计算机与外部设备之间如何减缓信息的技术。

过程通道是计算机与生产过程之间的信息传送和转换的连接通道。

2.采用74LS244和74LS273与PC/ISA 总线工业控制机接口,设计8路数字量(开关量)输入接口和8路数字量(开关量)输出接口,请画出接口电路原理图,并分别编写数字量输入和数字量输出程序。

答:数字量输入接口设片选端口地址为portMOV DX,port MOV DPTR,PORT MOVX A,@DPTR IN AL,DX74LS244PC 总线*IOR(*RD)_数字量输出接口MOV AL,DATA MOV A,DATA MOV DX ,port MOV DPTR,PORT OUT DX,AL MOVX @DPTR,A3.用8位A/D 转换器ADC0809与8051单片机实现8路模拟量采集。

请画出接口原理图,并设计出8路模拟量的数据采集程序。

输出信号PC 总线(*WR)程序:ORG 0000HMOV R0,#30H ;数据区起始地址存在R0MOV R6,#08H ;通道数送R6MOV IE,#84H ;开中断SETB IT1 ;外中断请求信号为下跳沿触发方式MOV R1,#0F0H ;送端口地址到R1NEXT:MOVX @R1,A ;启动A/D转换LOOP:SJMP LOOPINC R0INC R1DJNZ R6,NEXT ;8路采样未接受,则转NEXTCLR EX1 ;8路采样结束,关中断END中断服务程序:ORG 0003H ;外中断1的入口地址AJMP 1000H ;转中断服务程序入口地址ORG 1000HMOVX A,@R1 ;读入A/D转换数据MOV @R0,A ;将转换的数据存入数据区RETI ;中断返回ORG 0000HMOV R1,#30HMOV R2,#0F0HA1: MOV DPTR, R2MOVX @DPTR, ALOOP: JNB P3.2 , LOOPMOVX A, @DPTRMOV @R1,AINC R2INC R1CJNE R2, 0F7H, A1END4.用12位A/D转换器AD574与PC/ISA总线工业控制机接口,实现模拟量采集。

双积分式A /D 转换器双积分式A /D 转换器(Dual Slope Integrating Converter)以其转换精度高、灵敏度高、抑制干扰能力强、造价低等突出优点而被广泛地应用于各类数字仪表和低速数据采集系统中,它的缺点是转换速度较低,通常低于每秒30次。

这类转换器的输出数据常以BCD 码或数码管七段码格式给出,以便与数字显示器件接口。

一.双积分式A /D 转换原理与特性典型的双积分式A /D 转换电路的基本组成可以用图3-24表示之。

它的一次转换基本工作原理可以分成三个工作阶段来描述。

图3-24 双积分式A /D 转换电路之基本组成第一阶段T 1,模拟开关S 1导通,其余各模拟开关断开,此阶段可称为对输入电压积分采样阶段。

通常,在进入此阶段之前,积分器的输出已被复零。

所以,当输入电压V i 为正时,积分器输出向负渐增;当输入V i 为负时,积分器输出向正渐增,如图3-25所示。

积分器输出电压的变化速率与输入电压成正比:RCV t V i =∆∆INT (3-13)图3-25积分器输出电压波形采样阶段所经历的时间T 1(T 1=t 1-t 0)是一常值。

它常常以计数器对时钟脉冲f cp 计数来确定。

例如,计数器以0累计到N 1所对应的时间N 1×T cp =N 1/f cp 作为T 1,也就是说计数器从0计到N 1所经历的时间作为对输入电压的积分阶段。

T 1阶段结束时刻积分器之输出电压为:i i t t i t t i T V RCdt V RC dt RC V V 111010INT -=-=-=⎰⎰ (3-14) 式中之i V 表示在T 1阶段中V i 之积分平均值,如果输入电压V i 是常值,则i V = V i 。

将T 1=N 1/f cp 代入上式,即可得cpi f N V RC V 1INT 1-= (3-15) 第二阶段T 2(T 2=t 2-t 1),模拟开关S 2或S 3导通,其余开关断开。

电路笔记CN-0155连接/参考器件利用ADI公司产品进行电路设计 4.8 kHz、超低噪声、24位、Σ-Δ型ADC,内置PGA和交流激励AD7195放心运用这些配套产品迅速完成设计。

欲获得更多信息和技术支持,请拨打4006-100-006或访问ADP3303 5 V低压差线性调节器/zh/circuits。

ADP3303 3.3 V低压差线性调节器利用内置PGA和交流激励的24位Σ-Δ型ADC AD7195实现精密电子秤设计电路功能与优势建模块置于芯片内,因此能够简化电子秤设计。

在4.7 Hz至4.8 kHz的完整输出数据速率范围内,AD7195均能保持良好的性能,可用于以较低速度工作的电子秤系统,以及较高速电子秤系统。

AD7195该电路为采用构建的交流激励电子秤系统。

AD7195是一款超低噪声、低漂移24位Σ-Δ ADC,内置PGA和驱动器来实现称重传感器的交流激励。

该器件将大多数系统构图1.采用内置交流激励的AD7195的电子秤系统(简化原理图,未显示所有连接)Rev.0“Circuits from the Lab” from Analog Devices have been designed and built by Analog Devicesengineers. Standard engineering practices have been employed in the design and constructionof each circuit, and their function and performance have been tested and verified in a labenvironment at room temperature. However, you are solely responsible for testing the circuitand determining its suitability and applicability for your use and application. Accordingly, inOne Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.Tel: Rev.0“Circuits from the Lab” from Analog Devices have been designed and built by Analog Devices engineers. Standard engineering practices have been employed in the design and construction of each circuit, and their function and performance have been tested and verified in a labenvironment at room temperature. However, you are solely responsible for testing the circuit and determining its suitability and applicability for your use and application. Accordingly, in One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 电路描述利用交流激励,即可使用外部MOSFET来切换称重传感器的激励电压极性。

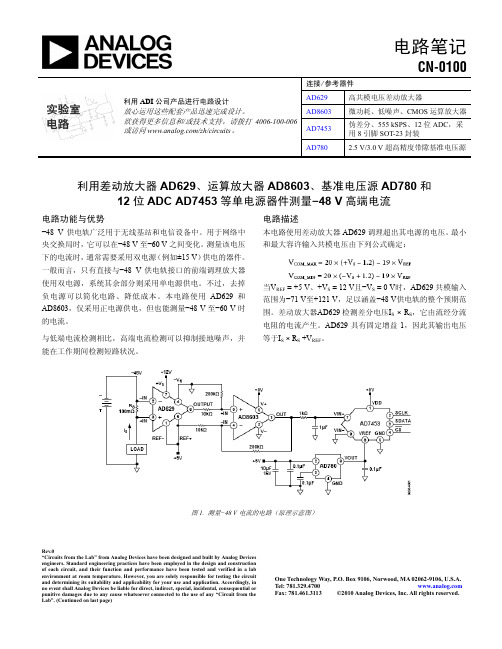

电路笔记CN-0100连接/参考器件AD629 高共模电压差动放大器AD8603 微功耗、低噪声、CMOS运算放大器AD7453伪差分、555 kSPS、12位ADC,采用8引脚SOT-23封装利用ADI公司产品进行电路设计放心运用这些配套产品迅速完成设计。

欲获得更多信息和/或技术支持,请拨打4006-100-006或访问/zh/circuits。

AD780 2.5 V/3.0 V超高精度带隙基准电压源Rev.0“Circuits from the Lab” from Analog Devices have been designed and built by Analog Devicesengineers. Standard engineering practices have been employed in the design and constructionof each circuit, and their function and performance have been tested and verified in a labenvironment at room temperature. However, you are solely responsible for testing the circuitand determining its suitability and applicability for your use and application. Accordingly, inno event shall Analog Devices be liable for direct, indirect, special, incidental, consequential orOne Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.Tel: 利用差动放大器AD629、运算放大器AD8603、基准电压源AD780和12位ADC AD7453等单电源器件测量−48 V高端电流电路功能与优势−48 V供电轨广泛用于无线基站和电信设备中。

数字电子技术实验讲义万用表及实验箱使用一、万用表使用重点讲解:1、电压和电阻测量2、“HOLD”数据保持按钮3、自动关闭功能4、用完后关闭电源二、示波器的使用由学生阅读示波器使用手册完成1、校准和选择探头(P)2、观察输入信号并调出稳定波形3、精确测量输入信号的幅度、周期和频率三、实验箱的构成1、电源开关2、电源输出:要求测量数据3、数据开关:可输出高低电平。

要求测量数据。

4、逻辑开关:可输出单次脉冲。

要求测量数据。

5、元件区:介绍集成块引脚识别、判断集成块是否插好。

6、电平指示:7、数码显示8、拨码开关:9、导线:要求判断通断四、使用注意事项1、导线插拨方法2、接线和更改线路一定要关闭电源3、注意观察电源指示灯,如接通电源时指示灯变暗,说明接线有短路,应关闭电源实验课的目的是培养学生的电子电路实验研究能力,培养学生理论联系实际的能力。

使学生能根据实验结果,利用所学理论,通过分析找出内在联系。

从而对电路参数进行调整,使之符合性能要求。

在实验中培养1.正确使用常用电子仪器。

2.3.4.5.6.7.能独立写出严谨的、有理论分析的、实事求是的、文理通顺、字迹端正的实验报为了顺利完成实验任务,确保人身、设备安全,培养严谨、踏实、实事求是的科学作风和爱护国家财产的优秀品质,特制1.1.1 认真阅读实验指导书,分析、掌握实验电路的工作原理,并进行必要的估算。

1.21.31.42.使用仪器、设备前必须了解其性能、操作方法及注意事项,在使用时应严格遵守。

3.实验时接线要认真,相互仔细检查,确信无误才能接通电源。

初学或没有把握时应经指导教师审查同意后才能接通电源。

4.实验时应注意观察,若发现有破坏性异常现象(例如有元件冒烟、发烫或有异味),应立即关断电源,保持现场,报告指导教师。

找出原因、排除故障并经指导教师同意才能再继续实验。

如果发生事故(例如元件或设备损坏)应主动填写实验事故报告单,服从实验室和指导教师对事故的处理决定(包括经济赔偿)5.6.实验过程中应仔细观察实验现象,认真记录实验结果(数据、波形及其现象)。

电路笔记CN-0155连接/参考器件利用ADI 公司产品进行电路设计4.8 kHz 、超低噪声、24位、Σ-Δ型ADC ,内置PGA 和交流激励 AD7195放心运用这些配套产品迅速完成设计。

欲获得更多信息和/或技术支持,请拨打4006-100-006或访问ADP3303 5 V 低压差线性调节器/zh/circuits 。

ADP33033.3 V 低压差线性调节器利用内置PGA 和交流激励的24位Σ-Δ型ADC AD7195实现精密电子秤设计电路功能与优势建模块置于芯片内,因此能够简化电子秤设计。

在4.7 Hz 至4.8 kHz 的完整输出数据速率范围内,AD7195均能保持良好的性能,可用于以较低速度工作的电子秤系统,以及较高速电子秤系统。

AD7195该电路为采用构建的交流激励电子秤系统。

AD7195是一款超低噪声、低漂移24位Σ-Δ ADC ,内置PGA 和驱动器来实现称重传感器的交流激励。

该器件将大多数系统构图1.采用内置交流激励的AD7195的电子秤系统(简化原理图,未显示所有连接)Rev.0“Circuits from the Lab” from Analog Devices have been designed and built by Analog Devices engineers. Standard engineering practices have been employed in the design and construction of each circuit, and their function and performance have been tested and verified in a lab environment at room temperature. However, you are solely responsible for testing the circuit and determining its suitability and applicability for your use and application. Accordingly, in One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 Rev.0“Circuits from the Lab” from Analog Devices have been designed and built by Analog Devices engineers. Standard engineering practices have been employed in the design and construction of each circuit, and their function and performance have been tested and verified in a labenvironment at room temperature. However, you are solely responsible for testing the circuit and determining its suitability and applicability for your use and application. Accordingly, in One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 电路描述利用交流激励,即可使用外部MOSFET来切换称重传感器的激励电压极性。

MT-031指南实现数据转换器的接地并解开“AGND”和“DGND”的谜团作者:Walt Kester、James Bryant、Mike Byrne简介目前的信号处理系统一般需要混合信号器件,例如模数转换器(ADC)、数模转换器(DAC)和快速数字信号处理器(DSP)。

由于需要处理宽动态范围的模拟信号,因此拥有高性能ADC和DAC显得更加重要。

在恶劣的数字环境内,能否保持宽动态范围和低噪声与采用良好的高速电路设计技术密切相关,包括适当的信号路由、去耦和接地。

过去,一般认为“高精度、低速”电路与所谓的“高速”电路有所不同。

对于ADC和DAC,采样(或更新)频率一般用作区分速度标准。

不过,以下两个示例显示,实际操作中,目前大多数信号处理IC真正实现了“高速”,因此必须作为此类器件来对待,才能保持高性能。

DSP、ADC和DAC均是如此。

所有适合信号处理应用的采样ADC(内置采样保持电路的ADC)均采用具有快速上升和下降时间(一般为数纳秒)的高速时钟工作,即使吞吐量看似较低也必须视为高速器件。

例如,中速12位逐次逼近型(SAR) ADC可采用10 MHz内部时钟工作,而采样速率仅为500 kSPS。

Σ-Δ型ADC具有高过采样比,因此还需要高速时钟。

即使是高分辨率、所谓的“低频”Σ-Δ工业测量ADC(吞吐速率10 Hz至7.5 kHz)也采用5 MHz或更高时钟工作,并且提供高达24位的分辨率(例如ADI公司的AD77xx系列)。

更复杂的是,混合信号IC具有模拟和数字两种端口,因此如何使用适当的接地技术就更加茫然。

此外,某些混合信号IC具有相对较低的数字电流,而另一些具有高数字电流。

许多情况下,两种类型必须区分对待,才能实现最佳接地。

数字和模拟设计工程师倾向于从不同角度考察混合信号器件,本教程旨在确立适用于大多数混合信号器件的一般接地原则,而不必了解内部电路的具体细节。

接地层和电源层保持低阻抗大面积接地层对目前所有的模拟和数字电路都很重要。

模拟器件的PLC/DCS模拟输出模块

电路功能与优势

图1所示电路是一种仅使用两个模拟器件的全功能、灵活、可编程的模拟输出解决方案,它满足可编程逻辑控制器(PLC)和分布式控制系统(DCS)应用的大部分要求。

AD5660-1 是一款低功耗(2.8 mW @ 5 V)、轨到轨输出、16位nanoDAC,AD5750-1是一款工业用电流/电压输出驱动器,二者相结合可提供所有典型的电流和电压输出范围、16位分辨率且无失码、0.05%的线性度以及小于0.1%的输出误差。

该电路还具有一些支持工业应用的重要特性,如片内输出故障检测、用于防止分组错误(PEC)的CRC校验以及灵活的上电选项等,非常适合构建鲁棒的工业控制系统。

在大批量生产中,它无需外部精密电阻或校准程序就能保持一致的性能,因而是PLC或DCS模块的理想选择。

实验二十一 D/A 、A/D转换电路一、实验目的⑴了解DAC0832数模转换器、ADC0804模数转换器的性能及使用方法。

⑵学习测试数模转换器、模数转换器的方法。

⑶了解数模转换器、模数转换器的性能及使用方法。

二、预习要求⑴阅读教材中有关D/A、A/D转换器的内容,理解D/A、A/D转换器的工作原理和参数。

⑵查阅ADC0804、DAC0832引脚定义和控制时序要求,熟悉其工作要求,了解其主要技术指标。

⑶针对实验内容,画出用DAC0832组成的DAC完整实验电路及用ADC0804组成的ADC完整实验电路。

⑷根据实验内容,设计实验方案及实验数据记录表格,写出实验预习报告。

三、实验内容用图21-1所示A/D、D/A转换器实验电路板,完成以下实验内容:1.加入8位数字量,对D/A转换器DAC0832进行D/A转换实验。

2.用模拟开关CD4051控制从备选通道ADC0-ADC7分别加入8路0-5V模拟量,对A/D转换器ADC0804进行A/D转换实验。

3.用2片4位二进制可逆计数器74191和DAC0834设计一个产生阶梯波形的电路。

图21-1 A/D、D/A转换器实验电路板四、实验原理与说明自然界的信息多数是连续变化的模拟量,如温度、压力、速度、声音、光强等,这些物理量在变成电信号之后,仍然是连续的,要送入计算机、数字信号处理器或数字通信系统进行处理和传输,就必须进行模拟量到数字量的转换,即A/D转换。

经过处理和传输之后的数字量往往又要变成模拟量输出,如数字通信系统,最后要转换成声音和图像,这就要进行数字量到模拟量的转换,即D/A转换。

D/A转换器(简称DAC)的电路比A/D转换器(简称ADC)简单,而且在A/D转换器中常包含D/A转换器。

1.D/A转换器这里以DAC0832数模转换器为例,来说明集成DA转换器的电路结构和应用电路。

DAC0832为电压输入、电流输出的R-2R电阻网络型的8位D/A转换器,采用CMOS 和薄膜Si-Cr电阻相容工艺制造,温漂低,逻辑电平输入与TTL电平兼容。

数模转化器工作原理与接口隔离技术和外围电路数模转化器简介数模转化器,又称DIA转换器,简称DAC I 数模转化器是将数字信号转换为模拟信号的系统。

D/A转换器基本上由4个部分组成,即权电阻网络、 运算放大器、 基准电源和一模拟开关。

它是把连续的模拟信号转变为离散的数字信号的器件。

般用低通滤波即可以实现。

数模转换器工作原理就是数字信号先进行解码,即把数字码转换成与之对应的电平,形成阶梯状信号,然后进行低通滤波。

数模转化器构成DAC主要由数字寄存器、 模拟电子开关、 位权网络、 求和运算放大器和基准电压源(或恒流源)组成。

用存千数字寄存器的数字量的各位数码,分别控制对应位的模拟电子开关,使数码为1的位在位权网络上产生与其位权成正比的电流值,再由运算放大器对各电流值求和,并转换成电压值。

根据位权网络的不同,可以构成不同类型的DAC, 如权电阻网络DAC、 R-2R倒T形电阻网络DAC和单值电流型网络DAC等。

©权电阻网络DAC的转换精度取决于基准电压VREF, 以及模拟电子开关、 运算放大 器和各权电阻值的精度。

它的缺点是各权电阻的阻值都不相同,位数多时,其阻值相差甚远,这给保证精度带来很大困难,特别是对于集成电路的制作很不利,因此在集成的DAC中很少单独使用该电路。

@R-2R倒T形电阻网络DAC由若干个相同的R、2R网络节组成,每节对应于一个输入位。

节与节之间串接成倒T形网络。

R-2R倒T形电阻网络DAC是工作速度较快、应用较多的一种。

和权电阻网络比较,由千它只有R、2R两种阻值,从而克服了权电阻阻值多,且阻值差别大的缺点。

@电流型DAC则是将恒流源切换到电阻网络中,恒流源内阻极大,相当于开路,所以连同电子开关在内,对它的转换精度影响都比较小,又因电子开关大多采用非饱和型的ECL开关电路,使这种DAC可以实现高速转换,转换精度较高。

数模转化器工作原理数字量是用代码按数位组合起来表示的,对千有权码,每位代码都有一定的位权。

双积分式A /D 转换器双积分式A /D 转换器(Dual Slope Integrating Converter)以其转换精度高、灵敏度高、抑制干扰能力强、造价低等突出优点而被广泛地应用于各类数字仪表和低速数据采集系统中,它的缺点是转换速度较低,通常低于每秒30次。

这类转换器的输出数据常以BCD 码或数码管七段码格式给出,以便与数字显示器件接口。

一.双积分式A /D 转换原理与特性典型的双积分式A /D 转换电路的基本组成可以用图3-24表示之。

它的一次转换基本工作原理可以分成三个工作阶段来描述。

图3-24 双积分式A /D 转换电路之基本组成第一阶段T 1,模拟开关S 1导通,其余各模拟开关断开,此阶段可称为对输入电压积分采样阶段。

通常,在进入此阶段之前,积分器的输出已被复零。

所以,当输入电压V i 为正时,积分器输出向负渐增;当输入V i 为负时,积分器输出向正渐增,如图3-25所示。

积分器输出电压的变化速率与输入电压成正比:RCV t V i =∆∆INT (3-13)图3-25积分器输出电压波形采样阶段所经历的时间T 1(T 1=t 1-t 0)是一常值。

它常常以计数器对时钟脉冲f cp 计数来确定。

例如,计数器以0累计到N 1所对应的时间N 1×T cp =N 1/f cp 作为T 1,也就是说计数器从0计到N 1所经历的时间作为对输入电压的积分阶段。

T 1阶段结束时刻积分器之输出电压为:i i t t i t t i T V RCdt V RC dt RC V V 111010INT -=-=-=⎰⎰ (3-14) 式中之i V 表示在T 1阶段中V i 之积分平均值,如果输入电压V i 是常值,则i V = V i 。

将T 1=N 1/f cp 代入上式,即可得cpi f N V RC V 1INT 1-= (3-15) 第二阶段T 2(T 2=t 2-t 1),模拟开关S 2或S 3导通,其余开关断开。

实现数据转换器的接地并解开“AGND”和“DGND”

的谜团

目前的信号处理系统一般需要混合信号器件,例如模数转换器(ADC)、数模转换器(DAC)和快速数字信号处理器(DSP)。

由于需要处理宽动态范围的模拟信号,因此拥有高性能ADC和DAC显得更加重要。

在恶劣的数字环境内,能否保持宽动态范围和低噪声与采用良好的高速电路设计技术密切相关,包括适当的信号路由、去耦和接地。

过去,一般认为高精度、低速电路与所谓的高速电路有所不同。

对于ADC和DAC,采样(或更新)频率一般用作区分速度标准。

不过,以下两个示例显示,实际操作中,目前大多数信号处理IC真正实现了高速,因此必须作为此类器件来对待,才能保持高性能。

DSP、ADC和DAC均是如此。

所有适合信号处理应用的采样ADC(内置采样保持电路的ADC)均采用具有快速上升和下降时间(一般为数纳秒)的高速时钟工作,即使吞吐量看似较低也必须视为高速器件。

例如,中速12位逐次逼近型(SAR)ADC可采用10 MHz内部时钟工作,而采样速率仅为500 kSPS。

Σ-Δ型ADC具有高过采样比,因此还需要高速时钟。

即使是。

实现数据转换器的接地并解开AGND和DGND的谜团Grounding Data Converters and Solving the Mystery of"AGND" and "DGND"author:Walt Kester, James Bryant, and Mike Byrne介绍:今天的信号处理系统一般都要求混合信号设备,如模拟到数字转换器(ADC)和数字到模拟转换器(DAC),还有快速数字信号处理器(DSP)。

要求处理模拟信号要有宽的动态范围,来增加高性能ADC 和DAC的价值。

在敌对的数字环境中,要保持有低噪声的宽动态范围取决于好的高速电路设计技术,包括合适的信号布线,去耦,和接地。

在过去,“高精密,低速”电路一般被显为不同于所谓的“高速”电路。

相对于ADC和DAC,采样(更新)频率一般被用来区分速度标准。

当然,下面列举了两个在实际中的例子,在今天的大多数信号处理IC是真正的“高速”,因此必须这样对待它,为了保持它的高性能。

这的确符合于DSP和ADC、DAC。

所有带有快的上升和下降时间(一般几纳秒)的高速时钟采样ADC(ADC带有内部采样保持电路)都适合于信号处理应用,它必须被看作高速设备,即使它的吞吐率较低。

如,一个中速12位逐次逼近型(SAR)ADC可以工作在10MHz的内部时钟,它的采样速率只有500KSPS。

Sigma-delta(Σ-Δ)ADC也要求高速时钟,因为它们要有高的过采样率。

甚至所谓的高分辨率“低频”的Σ-Δ工业测量ADC(吞吐率在10Hz至7.5KHz)工作在5MHz或较高的时钟和提供分辨率达到24位(如,Analog Devices AD77xx-series)。

长远的复杂问题是,混合信号IC有模拟和数字端口,因为这,更多的混淆是对于合适的接地技术。

另外,有些混合IC有相对较低的数字电流,同时其它的有较高的数字电流。

在很多情况下,在最佳接地方面这两种情况必须要不同的对待。

数字和模拟设计工程师趋向于从不同的观点看待混合信号设备,这个向导的目的是去开发普通的接地理念,它将适合于大多数混合信号设备,而不必对它们的内部电路特别了解。

地和电源层:保持大面积地平面的低阻抗是重要的,对于现今的模拟和数字电路是很关键的。

地平面不仅担当着对高频去耦电流(由快速数字逻辑引起)的低阻抗回路,而且还最小化EMI/RFI的辐射。

由于地平面的屏蔽作用,电路对于外界的EMI/RFI的敏感性就会降低。

在要求控制阻抗的地方,在使用传输线技术时(微波传输线或带状引线),平面也可以允许传输高速数字或模拟信号。

“总线”用于“地”是完全不可接受的,因为它的等效阻抗发生在大多数逻辑的过渡频率处。

例如,#22标准线有大约20nH/inch的电感。

如一个逻辑信号创造一个转换速率在10mA/ns的瞬变电流,在这个频率下流过1英寸的这样的线将会对电压造成200mV的下降。

对于2V峰峰值范围的信号,换算成误差为10%(大约3.5位精度)。

即使在全数字电路中,这个误差将造成逻辑噪声边缘的很大下降。

图1显示了数字返回电流混合模拟返回电流的情况的典型图解(顶图)。

地返回线的电感和电阻被模拟和数字电路共用,它会引起互调并造成误差。

可能的解决方案是把数字返回电流直接流到GND REF,如底图显示。

这是“星形”原理,或单点地系统。

对包含多个高频返回路径的系统,实现真正的单点接地是很困难的,因为单个电流返回线的实际长度将引入寄生电阻和电感,这对于获得低阻抗的高频地是困难的。

实际上,对于高频返回电流要有低阻抗,则电流返回必须由大面积的地平面构成。

没有一个低阻抗的地平面,几乎不可能避免共享阻抗,尤其是在高频中。

所有的集成电路地引脚都应该直接焊接到低阻抗的地平面上,以最小化串联电感和电阻。

传统IC插座的使用在高速设备中是不被推荐的。

即使“低剖面”的插座,由于引入有害的共享路径,它的额外电感和电容也可能降低设备的性能。

如果插座必须使用DIP封装,作为模型,单个的“引脚插座”或“cage jack”是可以接受的。

这些有管帽或无管帽引脚插座是可用的(AMP部件号5-330808-3和5-330808-6)。

它们有用弹簧顶住的黄色触点,这保证了与IC引脚有好的电气和机械连接。

多次插入的话,当然,就降低了它们的性能。

低、高频去耦:每个电源都应该通过一个高质量的去耦电解电容连到低阻抗的地平面上。

最小化低频噪声在电源线上。

对于单个的IC电源引脚仅高频滤波是被要求的。

图2显示了这种技术,正确(左边)和不正确(右边)的例子。

在左图中,一个典型的0.1uF的瓷片电容通过过孔直接连到PCB的反面的地平面上,用另一个过孔回到IC的GND上。

作为对比,右图的地回路由于PCB线的电感会降低去耦性能(这句采用了我自己的意思)。

在高频(如大于10MHz)IC应该使用旁路设计,类似图2,为获得最好性能。

磁珠不是100%必要的,但它们对高频噪声将增加额外的隔离和去耦,这常令人满意。

在这可能要检查的是当IC正处理大电流时不能让磁珠饱和。

注意:有些磁珠,即使在全饱和发生之前也可能是非线性的,所以对于功率级要求低失真输出的,就检查。

双层对比多层PCB板:每一个系统的PCB板至少要有一个完整的层用于地平面。

理想地,双层板应该有一层完全地用于地平面,另一层用于互相连接。

实际上,这是不可能的,因为一些地平面将必定被信号和电源走线,过孔,通孔所移除。

不过,应尽可能的保证面积,至少要剩余75%的地平面。

在初步完成布局后,应该仔细检查地平面,以确保没有孤立的地“岛”,因为IC的地引脚在孤立的地“岛”上没有返回地平面的电流回路。

还有,在地平面应该检查“内部”和大的面积的连接,它可能明显的降低地平面的性能。

不用多说,自动布线技术对于混合信号板一般会导致布局灾难,所以手工介入被强烈推荐!对于密集放置表贴IC的系统,会有很多的相互连线,因此多层板是必须的。

这允许至少一个层完全用于地。

简单的四层板应该有内部地和电源层,外面的两层用于和表贴元件相互连接。

放置电源和地平面会为彼此提供内置电容,这对电源的高频去耦是有帮助的。

在大多数的系统,四层板是不够的,附加层用于信号布线,和电源层一样。

多板混合信号系统:在多板系统中,最小化地阻抗的最好方法是使用一个“母板”作为底板,用于其它多板的连接,因此要为底板提供一个连续的地平面。

PCB的连接头至少应有30~40%的引脚用于地,这些引脚应该连接到母板的地平面上。

要完成整个系统的地设计有两种可能:1.低板地层可以在多点连接,从而散开不同地电流返回路径。

这常叫做多点接地系统,如图3显示。

2.地层可以连接到一个单系统“星形”点(一般在电源处)。

第一个方法常用在全数字电路系统中,但如果到数字电路的地电流足够低且分散到大的面积上,这时也可以用在混合信号系统中。

通过PCB板,底板或最终底座的回路的低地阻抗是应该保持的。

当然,地连接到金属薄片底座的电气接触要求是很严格的。

这要求自动攻丝螺丝或“咬”垫圈。

阳极电镀铝就用于底座材料必须仔细,因为它的表面扮演着绝缘体。

第二种方法(“星形地”)常用于有独立的模拟和数字地的高速混合信号系统中,且为长远讨论。

分离模拟和数字地平面:带有大量的数字电路的混合信号系统中,在“物理上”分离模拟元件和嘈杂的数字元件是很令人满意的。

对于模拟和数字电路,这样也有利于去使用分离的地平面。

这样的布置不应该重叠,为了最小化两者之间的电容耦合。

分开的模拟和数字地平面在母板地平面或“地屏幕”(指的是由一系列的线和转接头的地引脚互连)上连接起来。

图4说明了这样的布置,两个地平面保持分离,所有的路径回到系统的公共“星形”地上,一般是供电电源处。

为了最小化电阻和电感,在地平面,电源和“星形”应该组成多总线条或宽的铜带。

在每个PCB 板上都插入背对背的肖特基二极管是为了防止在卡板插入和拨出时在两个地系统之间产生意外的dc电压。

这个电压应该保持在低于300mv,是为防止损坏那些即连接在模拟地又连接在数字地的IC。

肖特基二极管是很好的选择,因为它们有低的电容和低的正向导通压降。

低的电容可以防止在模拟和数字地平面的ac耦合。

它在大约300mv就开始导通,如果可能产生大电流,则应使用若干个相并。

在有些情况下,磁珠可用于代替肖特基二极管,当然它引入的dc地环路在精密系统中是麻烦的。

返回到星形点的回路一定要尽可能的保持低阻抗。

在两个地平面之间的DC或AC电压超过300mv不仅可以损坏IC,而且也会引起逻辑门触发和锁存失败。

带有低数字电流的混合IC的接地和去耦:敏感的模拟元件,如放大器和基准电压,它们总是以模拟地平面为参考和去耦。

ADC和DAC(还有其它混合信号IC),它们带有低的数字电流,一般应看作是模拟元件,接地和去耦应以模拟地平面为参考。

初看,似乎有点矛盾,因为转换器有模拟和数字接口,且常区分模拟地和数字地。

图5将帮助解释这个表面的困惑。

IC的内部有模拟和数字电路,如ADC或DAC,地通常保持分离的,这样是为了避免数字信号耦合到模拟电路中。

图5显示了一个转换器的简单模型。

There is nothing the IC designer can do about the wire bond inductance and resistance associated with connecting the bond pads on the chip to the package pins except to realize it's there.(不明白这句意思)。

快速改变的数字电流在B点产生一个电压,这将不可避免的通过寄生电容C STRAY耦合到模拟电路的A点。

另外,在IC封装的每个引脚都不可避免的存在大约0.2pF的寄生电容!尽管如此,使芯片工作这是IC设计者的工作。

当然,为了防止进一步的耦合,AGND 和DGND引脚应该在外部用一个尽可能短的线一起连接到模拟地平面。

在DGND连接处的任何额外阻抗将会在B点引起更多的数字噪声;通过寄生电容,继而耦合更多的数字噪声到模拟电路。

注意:连接DGND到数字地平面产生的VNOISE穿过AGND和DGND引脚会招致灾难。

IC的“DGND”告诉我们这个引脚连接到IC的数字地。

这不意味着这个引脚必须被连接到系统的数字地平面。

实际这样的布置可能引入小数量的数字噪声到模拟地平面。

这个电流是相当小的,它能通过确保转换器不驱动大的扇出(正常是不可能的,通过设计)来最小化它。

在转换器的数字端口最小化扇出,将保证转换器的逻辑过渡,最小化数字开关电流,同时也降低了至模拟端口的任何的潜在耦合。

可以通过一个较小的有损磁珠来隔离逻辑供电引脚(V D)和模拟供电引脚,如图5。