集成电路分析与设计课程实验(一)

- 格式:doc

- 大小:13.16 MB

- 文档页数:18

第一章集成电路的发展1.何谓集成电路(Integrated Circuits)?集成电路:指通过一系列特定的加工工艺, 将晶体管,二极管等有源器件和电阻,电容,电感等无源器件,按照一定的电路互连,”集成”在一块半导体晶片上,封装在一个外壳内,执行特定电路或系统功能的一种器件.2.什么是摩尔定律(Moore’s Law)?它对集成电路的发展有什么作用?集成度:大约每三年翻两番,特征尺寸:每六年缩小近一倍事实上,摩尔定律并不是一个物理定律,而是一种预言,一张时间表。

它鞭策半导体产业界不断进步,并努力去实现它。

从根本上讲,摩尔定律是一种产业自我激励的机制,它让人们无法抗拒,并努力追赶,谁跟不上,谁就可能被残酷地淘汰。

摩尔定律已成为一盏照亮全球半导体产业前进方向的明灯。

3.IC发展水平的指标是什么?随着IC工业的发展,这些指标如何变化?集成规模(Integration scale)和特征尺寸(Feature size) 单个芯片上已经可以制作含有几百万个晶体管的一个完整的数字系统或数模混合的电子系统,集成电路的特征尺寸也已发展到深亚微米水平,0.18μm工艺已经走向规模化生产.4.什么是IDM、Fabless和Foundry?理解他们之间的关系。

IDM:集成电路发展的前三十年中,设计、制造和封装都是集中在半导体生产厂家内进行的,称之为一体化制造(IDM,Integrated Device Manufacturer)的集成电路实现模式。

无生产线(Fabless)集成电路设计提供了条件,为微电子领域发展知识经济提供了条件。

Fabless:1.设计公司拥有设计人才和设计技术,但不拥有生产线2.芯片设计公司不拥有生产线而存在和发展,而芯片制造单位致力于工艺实现(代客户加工,简称代工)3.设计单位与代工单位以信息流和物流的渠道建立联系Foundry:Foundry(代客户加工)第二章PN结的形成1.P型、N型半导体的形成及其能带结构图(EF与掺杂的关系)在纯净的硅晶体中掺入三价元素(如硼),使之取代晶格中硅原子的位置,此时自由电子和空穴浓度远远小于由于掺杂带来的空穴浓度,因此自由电子的导电基本可以忽略,这样的半导体叫做P型半导体。

西安邮电大学集成电路版图设计实验报告学号:XXX姓名:XX班级:微电子XX日期:20XX目录实验一、反相器电路的版图验证1)反相器电路2)反相器电路前仿真3)反相器电路版图说明4)反相器电路版图DRC验证5)反相器电路版图LVS验证6)反相器电路版图提取寄生参数7)反相器电路版图后仿真8)小结实验二、电阻负载共源放大器版图验证9)电阻负载共源放大器电路10)电阻负载共源放大器电路前仿真11)电阻负载共源放大器电路版图说明12)电阻负载共源放大器电路版图DRC验证13)电阻负载共源放大器电路版图LVS验证14)电阻负载共源放大器电路版图提取寄生参数15)电阻负载共源放大器电路版图后仿真16)小结实验一、反相器电路的版图验证1、反相器电路反相器电路由一个PMOS、NPOS管,输入输出端、地、电源端和SUB 端构成,其中VDD接PMOS管源端和衬底,地接NMOS管的漏端,输入端接两MOS管栅极,输出端接两MOS管漏端,SUB端单独引出,搭建好的反相器电路如图1所示。

图1 反相器原理图2、反相器电路前仿真通过工具栏的Design-Create Cellview-From Cellview将反相器电路转化为symbol,和schemetic保存在相同的cell中。

然后重新创建一个cell,插入之前创建好的反相器symbol,插入电感、电容、信号源、地等搭建一个前仿真电路,此处最好在输入输出网络上打上text,以便显示波形时方便观察,如图2所示。

图2 前仿真电路图反相器的输入端设置为方波信号,设置合适的高低电平、脉冲周期、上升时间、下降时间,将频率设置为参数变量F,选择瞬态分析,设置变量值为100KHZ,仿真时间为20u,然后进行仿真,如果仿真结果很密集而不清晰可以右键框选图形放大,如图3所示。

图3 前仿真结果3、反相器电路版图说明打开之前搭建好的反相器电路,通过Tools-Design Synthesis-Laout XL新建一个同cell目录下的Laout文件,在原理图上选中两个MOS管后在Laout中选择Create-Pick From Schematic从原理图中调入两个器件的版图模型。

哈尔滨理工大学数字集成电路设计实验报告学院:应用科学学院专业班级:电科12 - 1班学号:1207010132姓名:周龙指导教师:刘倩2015年5月20日实验一、反相器版图设计1.实验目的1)、熟悉mos晶体管版图结构及绘制步骤;2)、熟悉反相器版图结构及版图仿真;2. 实验内容1)绘制PMOS布局图;2)绘制NMOS布局图;3)绘制反相器布局图并仿真;3. 实验步骤1、绘制PMOS布局图:(1) 绘制N Well图层;(2) 绘制Active图层; (3) 绘制P Select图层;(4) 绘制Poly图层; (5) 绘制Active Contact图层;(6) 绘制Metal1图层;(7) 设计规则检查;(8) 检查错误; (9) 修改错误; (10)截面观察;2、绘制NMOS布局图:(1) 新增NMOS组件;(2) 编辑NMOS组件;(3) 设计导览;3、绘制反相器布局图:(1) 取代设定;(2) 编辑组件;(3) 坐标设定;(4) 复制组件;(5) 引用nmos组件;(6) 引用pmos组件;(7) 设计规则检查;(8) 新增PMOS基板节点组件;(9) 编辑PMOS基板节点组件;(10) 新增NMOS基板接触点; (11) 编辑NMOS基板节点组件;(12) 引用Basecontactp组件;(13) 引用Basecontactn 组件;(14) 连接闸极Poly;(15) 连接汲极;(16) 绘制电源线;(17) 标出Vdd 与GND节点;(18) 连接电源与接触点;(19) 加入输入端口;(20) 加入输出端口;(21) 更改组件名称;(22) 将布局图转化成T-Spice文件;(23) T-Spice 模拟;4. 实验结果4.1 nmos版图4.2 pmos版图4.3反相器的版图4.4反相器的spice文件4.5反相器的仿真曲线5.实验结论通过对仿真曲线的分析,当输入为高电平时,输出为低电平;当输入为低电平时,输出为高电平。

![[精品]数字集成电路分析与设计教学大纲.doc](https://uimg.taocdn.com/14361b0afab069dc5122014d.webp)

数字集成电路分析与设计一、课程基本情况课程编号40260103开课单位微纳电子学系课程名称中文名称数字集成电路分析与设计英文名称Digital Integrated Circuit Analysis and Design教学目的与重点教学目的:1)让学生掌握数字集成电路的工作原理与分析方法2)让学生掌握数字集成电路与系统的设计流程和基本方法3)培养学生实际设计数字集成电路与系统的能力教学重点:1) CMOS反相器的特性,数字集成电路分析与设计的关键问题2)组合逻辑链的性能优化3)互连线的延时模型与分析4)同步时序电路的分析和设计5)数据通路运算单元的分析与设计6)存储器的工作原理的理解与分析课程负责人刘雷波吴行军课程类型□文化素质课□公共基础课□学科基础课□专业基础课■专业课□其它教学方式■讲授为主□实验/实践为主□专题讨论为主□案例教学为主□自学为主□其它授课语言■中文口中文+英文(英文授课>50%)□英文□其他外语学分学时学分 3 总学时48考核方式及成绩评定标准作业:15%,课程设计:15%,期中考试(闭卷):30%,期末考试(闭卷):40%教材及主要参考书中文外文教材数字集成电路一电路、系统与设计(第二版),JanM.Rabaey等著,周润德等译,电子工业出版社。

Jan M. Rabaey etc. “Digital Integrated Circuits , A Design Perspective (Second Edition)", Prentice Hall , 2003.主要参考书CMOS数字集成电路一分析与设计(第3版),Sung-Mo Kang等著,王志功等译,清华大学出版社(影Sung-Mo Kang, Yusuf Leblebici,"CMOS Digital IntegratedCircuits-Analysis and Design(ThirdEdition)".三、课程主要教学内容9.4高级互连技术9. 5综述9.6总结第10章存储器(6学时)(教材第12章)10.1分类10.2结构10.3内核--- 存储单元和阵列10.4外围电路10.5可靠性10.6总结。

CMOS 模拟集成电路设计及HSPICE 使用实验学时:4学时实验一 CMOS 工艺参数测量 一、实验目的:学习和掌握EDA 仿真软件Hspice ;了解CMOS 工艺技术及元器件模型,掌握MOSFET 工作原理及其电压电流特征;通过仿真和计算,获得CMOS 中NMOS 和PMOS 的工艺参数,,,,,p n p n tp tn k k V V λλ,为后续实验作准备。

二、实验内容:1) 通过Hspice 仿真,观察NMOS 和PMOS 管子的I-V 特性曲线;2)对于给定长宽的MOSFET ,通过Hspice 仿真,测得几组栅-源电压、漏-源电压和漏-源电流数据,代入公式21()()(1)2DSn n n GS tn n DS WI K V V V Lλ=-+,求得对应的工艺参数,,,,,p n p n tp tn k k V V λλ 。

三、实验结果:本实验中所测试的NMOS 管、PMOS 管L=1u ,W 由学号确定。

先确定W 。

W 等于学号的最后一位,若学号最后一位=0,则W=10u 。

所以,本实验中所测试的NMOS 管、PMOS 管的尺寸为:L=1u ,W=( 8 )u 。

(1) 测0.5um 下NMOS 和PMOS 管的I-V 特性曲线所用工艺模型是 TSMC 0.50um 。

所测得的Vgs=1V 时,NMOS 管Vds 从0V 到2.5V 变化时的I-V 特性曲线为:所测得的Vds=1.2V时,NMOS管Vgs从0V到2.5V变化时的I-V特性曲线为:所测得的Vsg=1V时,PMOS管Vsd从0V到2.5V变化时的I-V特性曲线为:所测得的Vsd=1.2V时,PMOS管Vsg从0V到2.5V变化时的I-V特性曲线为:(2)计算TSMC 0.50um工艺库下mos管对应的工艺参数测试NMOS管相关参数,Hspice中仿真用源文件(.sp文件)为:NOMS I-V CharacteristicM1 OUT IN 0 0 CMOSn L=1U W=8UVIN IN 0 1VOUT OUT 0 1.2.OPTIONS LIST NODE POST*.DC VOUT 0 2.5 0.1.DC VIN 0 2.5 0.1*.DC VOUT 0 2.5 0.1 VIN 0.8 1.0 0.2.PRINT DC I(M1).LIB "C:\synopsys\project\tsmc_050um_model.lib" CMOS_MODELS .END所测得的NMOS 管电流曲线为:所测的数据如下表:Ids Vds1V 1.5V Vgs 1V65.4uA 66.5 1.2V14.014.4根据公式21()()(1)2DSn n n GS tn n DS I K V V V Lλ=-+,计算,,n n tn k V λ,分别为: -611910,0.028, 1.37n n tn k V λ≈⨯≈≈测试PMOS 管相关参数,Hspice 中仿真用源文件(.sp 文件)为: POMS I-V CharacteristicM1 OUT IN Vdd Vdd CMOSP L=1U W=8UVIN Vdd IN 1 VOUT Vdd OUT 1.2.OPTIONS LIST NODE POST *.DC VOUT 0 2.5 0.1 .DC VIN 0 2.5 0.1*.DC VOUT 0 2.5 0.1 VIN 0.8 1.0 0.2.PRINT DC I(M2).LIB "C:\synopsys\project\tsmc_050um_model.lib" CMOS_MODELS .END所测得的PMOS 管电流曲线为:所测的数据如下表:Isd Vsd1V 1.5VVsg 1V 1.17 1.181.2V 4.87 5.15计算TSMC 0.50um 工艺中 pmos 参数p p tp ,分别为:-654.8910,0.017,0.927p p tp K V λ≈⨯≈≈综上所述,可得:TSMC 0.50um 工艺参数=n λ0.028=p λ0.017=tn V 0.37V=tp V 0.927V2/119V A K n μ=2/89.54V A K p μ=四、思考题2) 不同工艺,,p n λλ不同。

集成电路课程设计通常包括以下几个步骤:

确定设计题目:根据课程要求和实验室条件,选择一个合适的题目,如数字逻辑门电路、计数器、微处理器等。

理论分析:对所选题目进行理论分析,包括电路的基本原理、功能、性能指标等,并确定电路的总体结构。

电路设计:使用专业软件(如Multisim)设计电路,根据理论分析的结果,搭建电路模型,并对其进行仿真测试。

制作电路板:将设计好的电路原理图转化为PCB图,交给实验室制作电路板。

焊接与调试:将电子元件焊接到电路板上,并进行测试和调试,确保电路正常工作。

编写程序:如果设计题目涉及到微处理器,还需要编写程序并进行调试。

撰写报告:整理实验数据、图表、照片等资料,编写设计报告,对整个设计过程进行总结。

答辩与验收:最后进行答辩,向老师和同学展示设计成果,并进行验收。

在设计过程中,需要注意以下几点:

遵守实验室规章制度,注意安全。

严格按照设计步骤进行,不能跳步或省略任何环节。

在设计过程中要及时记录数据和经验,以便后期整理和总结。

在遇到问题时,要善于查阅资料和请教老师或同学。

设计完成后要及时整理和归档资料,以便日后查阅和使用。

模拟集成电路分析与设计教学实践研究摘要:模拟集成电路人才的培养与发展是我国芯片技术发展的核心,为了适应时代发展的趋势,本文对模拟集成电路分析与设计的教学实践进行有效地研究。

在教学目标确认的情况下,设计符合当前半导体、芯片的课程内容和教学大纲,然后制定良好的教学方法,并打造实验和设计环境,从而全面展开人才的培养,并对其的实践、创新能力进行有效地引导。

从而为我国半导体人才的教育与培养提供可靠的支持。

关键词:模拟集成电路;电路分析;分析与设计;教学实践在全球进入信息、数据时代的过程中,集成电路产业的发展创新能力,已经成为我国技术发展、转型的重要核心。

现阶段我国集成电路产业的发展相对比较落后,虽然经过多年的发展,但我国自主集成电路产业的研发、创新能力依然较为落后。

同时集成电路产业具有技术、资金、人才集中的特点,从实际的市场角度来讲,我国集成电路产业,拥有14亿人口的市场,因此在市场与资金方面具有一定的优势。

但在技术和人才方面,却存在大量的缺口,不足以支撑集成电路产业的快速发展与创新。

而根据我国技术发展创新的战略要求,我国在高校教育规划中,进一步要求各高校充分重视集成电路产业相关的专业和技术的研究,但在实际展开的过程中,不少课程依然存在较为落后,与当前市场发展脱节的现象。

因此,需要进一步对集成电路专业的相关课程进行深入的研究,在丰富理论教学内容的同时,采取有效的手段提升相关专业课程的合理性与适用性。

一、教学目标的确定教学目标的确定,需要明确课程具体的教学目标,以及学生在学习的过程中,需要获得的知识、能力和素养。

对于模拟集成电路分析与设计课程来说,学生所学习的基本知识需要具备电路分析、电子器件、模拟电子技术、信号分析等方面的基本概念和原理的充分了解。

并在此基础上,学生应当具备对模拟集成电路进行分析、设计、仿真的能力,能够使用相关的软件展开电路设计,并对其进行有效地优化和验证,还需要从实际的角度出发,对实际中存在的集成电路问题提出有效的解决方案,从而让学生在模拟集成电路领域中进行主动思考,并展开有效的创新。

![L-Edit实验指导书[1]](https://uimg.taocdn.com/3fb4a22d376baf1ffc4fad8b.webp)

MEMS原理实验(L-Edit)指导书电子信息科学与技术前言近年来,集成电路设计的发展非常迅速,许多设计必须借助于计算机辅助设计软件来完成,而大部分软件是在工作站上执行的,虽然其功能强大,但是价格昂贵,不利于初学者学习使用。

目前,在个人电脑上开发的Tanner Pro工具为用户提供了完整电路设计的环境,为初学者进入VLSI设计领域提供了帮助。

Tanner集成电路设计软件是由Tanner Research 公司开发的基于Windows 平台的用于集成电路设计的工具软件。

该软件功能十分强大,易学易用,包括S-Edit,T-Spice,W-Edit,L-Edit与LVS,从电路设计、分析模拟到电路布局一应俱全。

其中的L-Edit版图编辑器在国内应用广泛,具有很高知名度,它不仅可以用于传统的集成电路设计,还可以用于MEMS版图设计,具有强大的集成电路设计、模拟验证、版图编辑和自动布局布线等功能,图形处理速度快、编辑功能强、通俗易学、使用方便,很适用于个人进行集成电路设计或其它微细图形加工的版图设计工作。

将其作为《MEMS原理》课程的实验课程,旨在通过对L-edit学习,掌握版图设计的基本流程。

实验一L-Edit的使用一、实验目的1、了解TANNER Pro软件的构成及其功能;2、熟悉版图设计工具L-Edit的使用环境;3、掌握L-Edit的使用方法;二、基本原理1、版图设计的概念:版图设计是创建器件或者系统的工程制图的物理描述过程,而这一物理描述遵守有制造工艺、设计流程以及通过仿真显示为可行的性能要求所带来的一系列约束。

2、TANNER Pro简介Tanner Tools Pro是一套集成电路设计软件,包含S-Edit, T-Spice, W-Edit, L-Edit 与LVS,各软件的主要功能整理如表1所示。

Tanner Pro 的设计流程如图1所示。

将要设计的电路先以S-Edit编辑出电路图,再将该电路图输出成SPICE文件。

华侨大学电子工程系集成电路设计与分析实验 B(模拟集成电路分析与设计课程实验) 实验(一)ADE5.1.41 设计软件的简单应用(1)华侨大学厦门专用集成电路系统重点实验室 -2012-集成电路设计与分析实验 B(一)2012 年-03 月-06 日 19:00 机电信息实验大楼 A526一、实验目的1.掌握使用 Cadence Virtuoso ADE5.1.41 软件进行原理图的编辑 2.掌握使用 Cadence Virtuoso ADE5.1.41 软件进行电路仿真 3.掌握使用 Cadence Virtuoso ADE5.1.41 软件进行结果的显示 4.熟练掌握低频模拟电路的几种分析方法二、实验软件:Cadence IC Virtuoso ADE 5.1.41三、实验要求:实验前请做好预习工作,实验后请做好练习,较熟练地使用 Virtuoso 软件对原理图进行编 辑并熟练掌握常用的几种低频模拟电路的分析方法。

集成电路分析与设计实验 B(一) 教学任务 Virtuoso ADE5.1.41 软件的使用(1) 专业能力: 教学目标 1.掌握原理图编辑软件的使用 2.掌握 ADE5.1.41 软件进行电路仿真 3.熟练掌握低频模拟电路的几种分析方法 教学内容 重点 难点 1. Cadence Virtuoso 原理图编辑 2. Cadence ADE5.1.41 进行电路性能的仿真验证 Cadence Virtuoso 原理图编辑软件使用 Cadence Virtuoso 原理图编辑软件使用,及常用分析方法 学时 2华侨大学电子工程系(The Department of Electronic Engineering Huaqiao University)1 华侨大学厦门专用集成电路系统重点实验室四、实验要点掌握说明:㈠ 电路原理图部分:1.学会建立仿真使用的库文件、仿真原理图 Cell 2.掌握器件输入、电路原理图连线、电源线标示符、地线标示符、输入/输出 PIN 标示符的使 用。

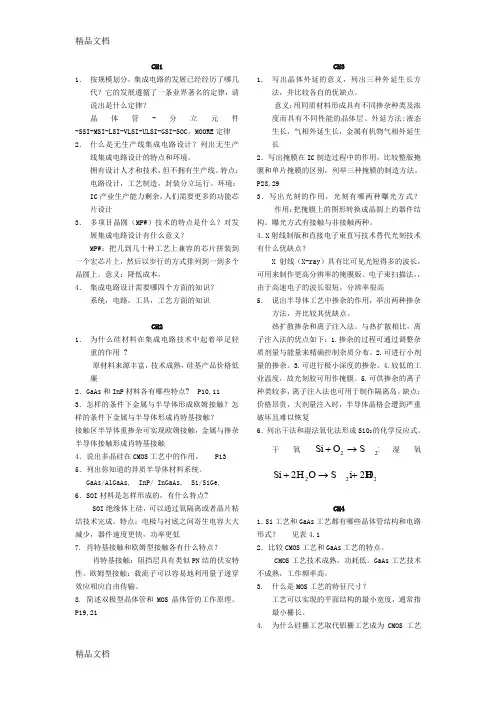

CH11.按规模划分,集成电路的发展已经经历了哪几代?它的发展遵循了一条业界著名的定律,请说出是什么定律?晶体管-分立元件-SSI-MSI-LSI-VLSI-ULSI-GSI-SOC。

MOORE定律2.什么是无生产线集成电路设计?列出无生产线集成电路设计的特点和环境。

拥有设计人才和技术,但不拥有生产线。

特点:电路设计,工艺制造,封装分立运行。

环境:IC产业生产能力剩余,人们需要更多的功能芯片设计3.多项目晶圆(MPW)技术的特点是什么?对发展集成电路设计有什么意义?MPW:把几到几十种工艺上兼容的芯片拼装到一个宏芯片上,然后以步行的方式排列到一到多个晶圆上。

意义:降低成本。

4.集成电路设计需要哪四个方面的知识?系统,电路,工具,工艺方面的知识CH21.为什么硅材料在集成电路技术中起着举足轻重的作用 ?原材料来源丰富,技术成熟,硅基产品价格低廉2.GaAs和InP材料各有哪些特点? P10,11 3.怎样的条件下金属与半导体形成欧姆接触?怎样的条件下金属与半导体形成肖特基接触?接触区半导体重掺杂可实现欧姆接触,金属与掺杂半导体接触形成肖特基接触4.说出多晶硅在CMOS工艺中的作用。

P13 5.列出你知道的异质半导体材料系统。

GaAs/AlGaAs, InP/ InGaAs, Si/SiGe, 6.SOI材料是怎样形成的,有什么特点?SOI绝缘体上硅,可以通过氧隔离或者晶片粘结技术完成。

特点:电极与衬底之间寄生电容大大减少,器件速度更快,功率更低7. 肖特基接触和欧姆型接触各有什么特点?肖特基接触:阻挡层具有类似PN结的伏安特性。

欧姆型接触:载流子可以容易地利用量子遂穿效应相应自由传输。

8. 简述双极型晶体管和MOS晶体管的工作原理。

P19,21CH31.写出晶体外延的意义,列出三种外延生长方法,并比较各自的优缺点。

意义:用同质材料形成具有不同掺杂种类及浓度而具有不同性能的晶体层。

外延方法:液态生长,气相外延生长,金属有机物气相外延生长2.写出掩膜在IC制造过程中的作用,比较整版掩膜和单片掩膜的区别,列举三种掩膜的制造方法。

数字集成电路课程设计一、课程目标知识目标:1. 让学生理解数字集成电路的基本概念,掌握常用数字逻辑电路的组成、工作原理及应用。

2. 使学生了解数字集成电路的设计流程,掌握使用硬件描述语言(如Verilog HDL)进行数字电路设计的基本方法。

3. 帮助学生掌握数字电路的仿真、测试与优化方法。

技能目标:1. 培养学生运用所学知识,独立完成简单的数字集成电路设计任务。

2. 培养学生运用硬件描述语言进行数字电路编程的能力。

3. 培养学生分析问题、解决问题的能力,提高创新意识和团队协作能力。

情感态度价值观目标:1. 激发学生对数字集成电路的兴趣,培养其探索精神。

2. 培养学生严谨、踏实的科学态度,养成良好的学习习惯。

3. 增强学生的环保意识,使其关注数字集成电路对环境的影响。

分析课程性质、学生特点和教学要求,本课程目标旨在使学生在掌握数字集成电路基本知识的基础上,提高实际设计能力,培养创新思维和团队协作能力。

通过课程学习,使学生能够具备以下具体学习成果:1. 能够正确描述常用数字逻辑电路的组成、工作原理及应用。

2. 能够运用硬件描述语言进行简单数字电路设计。

3. 能够分析并解决数字电路设计过程中遇到的问题。

4. 能够参与团队协作,完成具有一定难度的数字集成电路设计项目。

二、教学内容本章节教学内容依据课程目标,紧密围绕数字集成电路的设计原理和实践操作,确保科学性和系统性。

具体教学内容安排如下:1. 数字集成电路基础知识- 数字逻辑电路的基本概念与分类- 常用数字逻辑电路(如与门、或门、非门等)的组成、工作原理及应用2. 硬件描述语言(Verilog HDL)基础- Verilog HDL的基本语法和结构- 常用Verilog HDL语句及其功能描述3. 数字集成电路设计流程- 设计需求分析- 电路设计、编码、仿真与测试- 优化与调试4. 常用数字集成电路设计实例- 简单组合逻辑电路设计- 时序逻辑电路设计- 数字信号处理电路设计5. 数字电路设计工具与平台- 硬件描述语言编译器(如ModelSim)- 电路设计与仿真软件(如Quartus II)教学内容参照教材相关章节进行安排,确保与课程目标紧密结合。

集成电路原理与设计教案教案一:集成电路的概述I. 课程背景A. 教学目标B. 先修知识II. 教学内容A. 集成电路的定义B. 集成电路的分类1. 按集成度分类2. 按制作工艺分类3. 按应用领域分类C. 集成电路的发展历程1. 从离散元件到集成电路2. 集成电路的快速发展3. 集成度与功能的提升III. 教学方法A. 讲授B. 讨论C. 实践操作D. 案例分析IV. 教学步骤A. 引入1. 介绍课程背景和重要性2. 激发学生兴趣B. 讲解集成电路的定义和分类1. 详细解释集成电路的概念2. 分类介绍不同类型的集成电路C. 探讨集成电路的发展历程1. 分析从离散元件到集成电路的进步2. 总结集成电路的发展趋势D. 进行实践操作和案例分析1. 学生通过实验了解集成电路的原理和设计过程2. 分析真实的集成电路案例E. 总结与展望1. 总结所学内容2. 展望未来集成电路的发展V. 教学评价A. 以课堂讨论和实际操作为主要评价方式B. 考核学生对集成电路原理和设计的理解能力C. 督促学生完成相应的实验报告和案例分析报告教案二:逻辑门电路设计I. 课程背景A. 教学目标B. 先修知识II. 教学内容A. 逻辑门的基本原理B. 逻辑门的代数表达式1. 布尔代数基本运算2. 逻辑门的真值表C. 逻辑门的设计方法1. 小规模集成电路的设计2. 大规模集成电路的设计D. 逻辑门的应用场景1. 数字电路中的逻辑门2. 逻辑门在计算机中的应用III. 教学方法A. 讲授B. 实验演示C. 讨论D. 练习IV. 教学步骤A. 引入1. 复习前一教案的内容2. 引出本节课的主题B. 介绍逻辑门的基本原理和代数表达式1. 解释逻辑门的基本功能2. 分析逻辑门的代数运算C. 演示逻辑门的设计方法1. 通过实验演示小规模集成电路设计的过程2. 探讨大规模集成电路设计的要点D. 讨论逻辑门的应用场景1. 分析数字电路中逻辑门的作用2. 探索逻辑门在计算机中的应用E. 知识巩固练习1. 学生进行逻辑门电路的设计练习2. 分析练习中出现的问题并进行讨论V. 教学评价A. 以练习结果和讨论参与度为主要评价方式B. 考核学生对逻辑门设计和应用的掌握程度C. 督促学生完成相应的设计练习报告和讨论记录教案三:集成电路的工艺制造I. 课程背景A. 教学目标B. 先修知识II. 教学内容A. 集成电路的工艺流程1. 层叠式工艺流程2. 半导体工艺制造步骤B. 集成电路的工艺问题与解决方案1. 掺杂控制问题2. 掩膜制备问题3. 金属铝连接问题C. 集成电路的测试与封装1. 功能测试2. 封装技术III. 教学方法A. 讲授B. 实验演示C. 讨论D. 案例分析IV. 教学步骤A. 引入1. 介绍工艺制造的重要性2. 引出本节课的主题B. 讲解集成电路的工艺流程1. 详细介绍层叠式工艺流程和半导体工艺制造步骤2. 分析每个步骤的作用和要点C. 探讨工艺问题与解决方案1. 分析工艺制造中可能出现的问题2. 提出相应的解决方案D. 实验演示集成电路的测试与封装技术1. 演示集成电路的功能测试方法2. 介绍封装技术的原理和方法E. 案例分析1. 分析真实的工艺制造案例2. 总结案例中的经验和教训V. 教学评价A. 以实验结果和案例分析报告为主要评价方式B. 考核学生对集成电路工艺制造的理解能力C. 督促学生完成相应的实验报告和案例分析报告通过以上三个教案,学生将能够全面了解集成电路的原理与设计,掌握逻辑门电路的设计方法,并深入了解集成电路的工艺制造过程。

CMOS射频集成电路分析与设计课程设计一、课程设计背景近年来,随着无线通信技术的日益普及,射频集成电路越来越受到关注。

CMOS 射频集成电路以其低功耗、高集成度等优势成为了当前射频集成电路发展的热点。

因此,对于射频集成电路分析与设计的教学与研究需求也逐渐增加。

本文旨在介绍一种CMOS射频集成电路分析与设计的教学课程设计,旨在帮助学生深入了解CMOS 射频集成电路的原理及设计方法。

二、课程设计内容1. 课程介绍在本课程中,我们将先介绍CMOS射频集成电路的基本原理和设计方法,然后根据实际情况,设计出一款简单的CMOS射频集成电路。

在课程结尾,我们将通过仿真软件进行验证,并进行性能测试。

2. 理论部分在理论部分,我们将介绍以下内容:•CMOS射频集成电路的基本原理•基本分析方法和常用工具•基本设计方法•常见的射频电路和器件3. 实验部分在实验部分,我们主要通过仿真软件进行实验设计,包括:•基于ADS和Cadence的仿真实验•基于实际测试的性能评估4. 报告及论文撰写学生们需要完成一份包含实验设计方法、仿真结果和理论分析的课程报告,并撰写一篇包含理论分析以及实验结果的小论文。

三、课程设计目标本课程设计的主要目标为:1.深入了解CMOS射频集成电路的基本原理和设计方法;2.掌握常见的射频电路和器件设计技能;3.学会运用仿真软件进行射频电路设计的能力;4.学会进行性能测试,评估射频电路设计的质量;5.培养学生的独立思考和解决问题的能力;6.培养学生的实验设计和报告撰写能力。

四、课程设计流程1.理论讲解:介绍CMOS射频集成电路的基本原理和设计方法,让学生了解射频电路的基本知识、分析方法和设计流程;2.实验指导:通过仿真软件对设计的射频电路进行验证,通过性能测试评估电路设计的质量,并给出改进建议;3.报告撰写:学生完成课程报告和小论文,包括理论分析、实验设计和仿真结果等内容;4.答辩:学生进行小组答辩,分享自己的设计思路和实验结果,互相评价、交流。

集成电路工程的课程设计一、教学目标本课程的目标是让学生了解和掌握集成电路工程的基本原理、设计和制造过程。

通过本课程的学习,学生应能理解集成电路的基本结构、工作原理和设计方法,掌握集成电路的制造流程和测试技术,并了解集成电路在现代电子技术中的应用。

具体来说,知识目标包括:1.了解集成电路的基本结构和类型;2.理解集成电路的工作原理和设计方法;3.掌握集成电路的制造流程和测试技术;4.了解集成电路在现代电子技术中的应用。

技能目标包括:1.能够使用集成电路设计软件进行简单的设计;2.能够进行集成电路的制造和测试;3.能够分析集成电路的性能和问题。

情感态度价值观目标包括:1.培养对集成电路工程技术的兴趣和热情;2.培养创新意识和团队合作精神;3.培养学生对科技发展的敏感性和适应性。

二、教学内容本课程的教学内容主要包括四个方面:1.集成电路的基本原理:包括集成电路的定义、分类、结构和功能,以及集成电路的设计原则和流程。

2.集成电路的设计方法:包括数字集成电路、模拟集成电路和混合集成电路的设计方法,以及集成电路设计工具和软件的使用。

3.集成电路的制造流程:包括硅片制造、集成电路版图设计、光刻、蚀刻、离子注入等基本工艺,以及集成电路的封装和测试。

4.集成电路的应用:包括集成电路在电子设备中的应用、集成电路系统的组成和原理,以及集成电路技术的未来发展趋势。

三、教学方法为了激发学生的学习兴趣和主动性,本课程将采用多种教学方法,包括:1.讲授法:通过教师的讲解,让学生了解和掌握集成电路的基本原理和设计方法;2.案例分析法:通过分析实际案例,让学生了解集成电路的应用和制造过程;3.实验法:通过实验操作,让学生掌握集成电路的测试技术和性能分析;4.小组讨论法:通过小组讨论,培养学生的团队合作精神和创新意识。

四、教学资源为了支持教学内容和教学方法的实施,丰富学生的学习体验,我们将选择和准备以下教学资源:1.教材:选用《集成电路工程》作为主教材,为学生提供系统的学习内容;2.参考书:推荐《集成电路设计手册》等参考书籍,为学生提供更多的学习资料;3.多媒体资料:制作PPT、视频等多媒体资料,为学生提供直观的学习体验;4.实验设备:准备集成电路设计软件、实验板等实验设备,为学生提供实践操作的机会。

集成电路分析与设计

课程实验1(2010-03-18)

熟悉Cadence设计软件中的Schematic Editing进行原理图编辑,并使用Spectre工具进行仿真验证。

要求及说明:

1. NMOS和PMOS晶体管的1级模型参数参考教材(拉扎维,P32)中表

2.1,相应的Spectre 模型为hquicmodel_v1.0.scs。

2. 假设VDD=3V,NMOS和PMOS器件的衬底端子(B,除非另有说明)分别接地和VDD (或最正的电压节点),(W/L)=50/2(即W=50u,L=2u)。

3. 采用直流扫描(DC Sweep,改变VX),画出IX和晶体管的跨导关于VX的函数曲线图。

4. 解释分析结果,比较仿真分析结果与你的手工计算结果。

5. 报告截止提交日期为2008年3月25日。

题目:

(参考拉扎维的模拟CMOS集成电路设计P34-35)

2.5 对图2.42的每个电路,画出I

X 和晶体管跨导(g

m

)关于V

X

的函数曲线。

V

X

从0变化到V

DD。

+1.9V

x

V

(b)

1V

x

V 2.42

图

2.6 对图2.43的每个电路,画出I

X 和晶体管跨导(g

m

)关于V

X

的函数曲线。

V

X

从0变化到V

DD。

I 原理图绘制篇

1.右键open Terminal

2.输入icfb&

3.回车启动Cadence

4.Tools – Library Manager…

5.File-Library新建项目

6.输入建立的项目的名称-OK

7.选择Don’t need a Techfile-OK

8. File-Cell View新建项目

9.输入建立的子项目名称-OK

10.输入器件按快捷键I

11.选择Browse – analoglib-nmos4-symbol输入nmos器件

12.在属性框里填写器件的模型和参数:模型名称:nmos、参数W=50u L=2u 点Hide完成

13.修改器件参数如果想修改器件参数,选择该器件后按快捷键q,可以在属性框里修改

14.输入直流电源:快捷键I – analoglib – vdc – symbol

15.放置直流电压源,如果放置位置不满意可以按快捷键m移动位置,移动到指定位置后按ESC 退出

16.修改电压源参数:按q,然后逐一修改

17.输入接地符号GND

18. 按W进行连线

19.Check and Save

请确认保存,不保存仿真无法正常进行

II 仿真验证篇

1.Tools – Analog Environment启动模拟电路仿真环境ADE

2.在ADE中选择Setup-Model Libraries

3.按浏览Browse选择我们需要的模型:hquicmodel_v1.0.scs-OK

4.Add - OK

5.Analyses-Choose…

6.选择DC – Component Parameter

7.通过选择Select Component,选择需要进行参数扫描的电压源,然后在弹出页选DC项,OK

或者自己手动在Choosing Analyses中填写也行

8.填写DC扫描的起止值Start = 0 Stop = 3 OK

9.选择输出节点波形OUTPUTS-To Be Plotted – Select on Schhematic

10.在原理图上选择输出节点波形,电压选连线电流选器件的节点,我们需要器件电流,所以我们选择NMOS的漏端。

11.设置完成后选择netlist and Run运行

12.输出结果。