万年历电子钟设计报告

- 格式:docx

- 大小:1.25 MB

- 文档页数:33

摘要随着社会快速的发展,人们的生活节奏变得越来越快,人们对时间观念也愈来愈重视。

自动化、智能化技术的发展,机电产品的智能度愈来愈高,用到时间提示、定时控制的地方也会愈来愈多,因此,设计开发数字时钟具有良好的应用前景。

由于单片机价格的低成本、高性能,在自动控制产品中得到了广泛的应用。

本文以STC89C52为核心控制芯片,DS1302为时钟芯片,DS18B20为温度传感器,通过液晶显示器AMPIRE128X64实时显示时间及温度,通过按键设置年月日和星期以及定时闹钟,定时闹钟时间到自动发出警报,应用C语言进行软件编程,并用Altium Designer Summer 09软件进行演示、验证。

经过测试,系统可以正常完成预定的功能。

关键词:单片机STC89C52 电子时钟C语言AbstractWith rapid development of society, people's life rhythm becomes faster and faster, people to the concept of time is also more and more attention. Automation, intelligent technology development, the intelligence degree of mechanical and electronic products become more and more high, use time reminder, timing control will be more and more, therefore, design and develop digital clock has a good application prospect.Because of the price of low-cost, high-performance microcontroller, has been widely used in automatic control of the products. With STC89C52 as the core control chip, this paper DS1887 for the clock chip, DS18B20 as temperature sensor, through the LCD display AMPITE128X64 real-time display of time and temperature, through the button and set the date and week timing alarm clock, timer alarm clock time to alert automatically, using C language for software programming, using Altium Designer Summer 09 for demonstration, software validation. Program download by general technology of PZ - ISP software made by the company to complete. After the test, the system can accomplish the functions normally.Key words: single chip microcomputer C language STC89C52 electronic clock第一章绪论1.1电子时钟的研究背景单片机自1976年由Intel公司推出MCS-48开始,迄今已有二十多年了。

基于单片机和DS1302的电子万年历设计报告一、设计意义随着科技的不断进步和发展,单片机的使用已经渗透到我们日常生活当中的各个领域,几乎很难找到有哪个领域没有使用单片机的踪迹。

导弹的导航装置,飞机上各种仪表的控制,计算机的网络通讯与数据传输,工业自动化过程的实时控制和数据处理,广泛使用的各种智能IC卡,以及程控玩具、电子宠物等等,这些都离不开单片机,更不用说自动控制领域的机器人、智能仪表、医疗器械了。

本文设计的电子万年历属于小型智能家用电子产品。

利用单片机进行控制,实时时钟芯片进行记时,外加掉电存储电路和显示电路,可实现时间的调整和显示。

电子万年历既可广泛应用于家庭,也可应用于银行、邮电、宾馆、饭店、企业、商店等相关行业的大厅,以及单位会议室、门卫等场所。

因而,此设计具有相当重要的现实意义和实用价值。

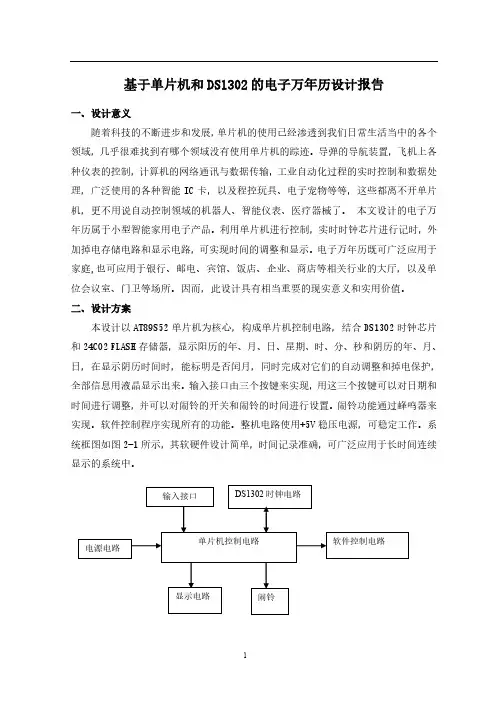

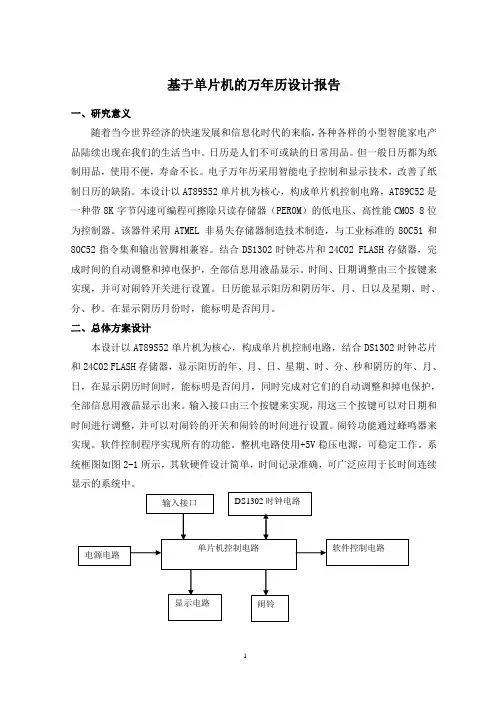

二、设计方案本设计以AT89S52单片机为核心,构成单片机控制电路,结合DS1302时钟芯片和24C02 FLASH存储器,显示阳历的年、月、日、星期、时、分、秒和阴历的年、月、日,在显示阴历时间时,能标明是否闰月,同时完成对它们的自动调整和掉电保护,全部信息用液晶显示出来。

输入接口由三个按键来实现,用这三个按键可以对日期和时间进行调整,并可以对闹铃的开关和闹铃的时间进行设置。

闹铃功能通过蜂鸣器来实现。

软件控制程序实现所有的功能。

整机电路使用+5V稳压电源,可稳定工作。

系统框图如图2-1所示,其软硬件设计简单,时间记录准确,可广泛应用于长时间连续显示的系统中。

三、硬件电路设计按照系统设计功能的要求,初步确定设计系统由主控模块、时钟模块、存储模块、键盘接口模块、显示模块和闹铃模块共6个模块组成,电路系统构成框图如图3-1所示。

主控芯片使用52系列AT89S52单片机,时钟芯片使用美国DALLAS公司推出的一种高性能、低功耗、带RAM的实时时钟芯片DS1302,存储模块采用美国ATMEL公司生产的低功耗CMOS串行EEPROM存储芯片AT24C02。

目录摘要 ........................................................... 错误!未定义书签。

一.设计要求与方案论证............................................ 错误!未定义书签。

1.1设计要求................................................... 错误!未定义书签。

1.1.1基本要求................................................ 错误!未定义书签。

1.1.2创新要求................................................ 错误!未定义书签。

1.2系统基本方案选择和论证...................................... 错误!未定义书签。

1.2.1单片机芯片.............................................. 错误!未定义书签。

1.2.2 显示模块 ............................................... 错误!未定义书签。

1.2.3时钟芯片................................................ 错误!未定义书签。

1.2.4温度传感器.............................................. 错误!未定义书签。

1.3电路设计最终方案决定........................................ 错误!未定义书签。

二.电子万年历硬件设计与实现...................................... 错误!未定义书签。

2.1电子万年历系统设计.......................................... 错误!未定义书签。

阿坝师范学院万年历设计报告姓名:李朝林学号:20156045 班级:电子信息工程02班阿坝师范学院物理与电子科学系目录1•设计任务与要求 (2)2•主要器件讨论与选择 (2)3.设计原理 (3)4•单元电路设计 (3)4.1显示电路 (3)4.2时分秒设计............................................. .44.3星期天数设计 (5)4.4闰年平年判断电路 (6)4.5二月与大小月判断电路 (9)4.6天数置数信号 (10)4.7校正电路 (11)4.8秒脉冲电路 (11)5.完整的电路设计原理图 (12)6.电路调试过程与方法 (13)7.实验心得体会与总结 (13)1. 设计任务与要求用数字集成电路设计万年历电子钟逻辑电路指标如下:1)设计一个能直接显示“年”“月”“日”、“星期”、“时”、“分”、“秒”的十进制万年历时钟显示器。

2)具有校时的功能,可分别对“年”、“月”、“日”、“星期”、“时” “分” “秒”进行单独校时。

2. 主要器件讨论与选择主要器件中显示模块选用74SEG_BCD数码管显示8421bcd码,计数模块统一选用74LS160作为计数芯片;74LS160具有同步置数异步清零功能,同时在有时钟脉冲的情况下进行加计数,无论采用同步置数还是异步清零都可以实现60s、60m、24h置数清零功能。

因此2/ 13[在此处键入]数字电子技术万年历设计报告3/ 1374LS160是一个不错的选择。

本次仿真通过 74LS160作为时分秒年月 日星期置数,通过秒计数的置数信号作为分计时的脉冲 cp ,取反作 为分计时的使能端,依次向高位进位达到显示目的。

通过闰年、平年、大月、小月、二月的判断电路来控制天计数的 多少。

校时电路,校时选用74LS74触发器作为跳变信号;74LS244存储 信号。

起作用的只有一个,当校时有效时计时电路无效。

3. 设计原理原理图如下:万年加时种星示器框采禺P4. 单元电路设计4.1显示电路振荡器呈期廿数楼时电路・译码显示电路疋*千 百 十个阿坝师范学院物理与电子科学系4 13整个显示电路分为年、月、日、时、分、秒、星期几大模块。

.万年历设计报告姓名:李朝林学号:20156045班级:电子信息工程02班阿坝师范学院物理与电子科学系目录1.设计任务与要求 (2)2.主要器件讨论与选择 (2)3.设计原理 (3)4.单元电路设计 (3)4.1显示电路 (3)4.2时分秒设计 (4)4.3星期天数设计 (5)4.4闰年平年判断电路 (6)4.5二月与大小月判断电路 (9)4.6天数置数信号 (10)4.7校正电路 (11)4.8秒脉冲电路 (11)5.完整的电路设计原理图 (12)6.电路调试过程与方法 (13)7.实验心得体会与总结 (13)1.设计任务与要求用数字集成电路设计万年历电子钟逻辑电路指标如下:1)设计一个能直接显示“年”、“月”、“日”、“星期”、“时”、“分”、“秒”的十进制万年历时钟显示器。

2)具有校时的功能,可分别对“年”、“月”、“日”、“星期”、“时”、“分”、“秒”进行单独校时。

2.主要器件讨论与选择主要器件中显示模块选用74SEG_BCD数码管显示8421bcd码,计数模块统一选用74LS160作为计数芯片;74LS160具有同步置数异步清零功能,同时在有时钟脉冲的情况下进行加计数,无论采用同步置数还是异步清零都可以实现60s、60m、24h置数清零功能。

因此[在此处键入]数字电子技术万年历设计报告74LS160是一个不错的选择。

本次仿真通过74LS160作为时分秒年月日星期置数,通过秒计数的置数信号作为分计时的脉冲cp,取反作为分计时的使能端,依次向高位进位达到显示目的。

通过闰年、平年、大月、小月、二月的判断电路来控制天计数的多少。

校时电路,校时选用74LS74触发器作为跳变信号;74LS244存储信号。

起作用的只有一个,当校时有效时计时电路无效。

3.设计原理原理图如下:4.单元电路设计4.1显示电路阿坝师范学院物理与电子科学系整个显示电路分为年、月、日、时、分、秒、星期几大模块。

统一采用7SEG-BCD数码管显示4.2时分秒设计秒分时一致采用74LS160芯片进行加计数,通过与非门截取信号作为置数信号和高位进位信号,取反作为高位使能端;送入BCD数码管显示。

摘要单片机应用技术飞速发展,纵观我们现在生活的各个领域,从导弹的导航装置,到飞机上各种仪表的控制,从计算机的网络通讯与数据传输,到工业自动化过程的实时控制和数据处理,以及我们生活中广泛使用的各种智能IC卡等,这些都离不开单片机。

单片机是集CPU ,RAM ,ROM ,定时,计数和多种接口于一体的微控制器。

它体积小,成本低,功能强,广泛应用于智能产业和工业自动化上。

而51系列单片机是各单片机中最为典型和最有代表性的一种。

这次毕业设计通过对它的学习,应用,从而达到学习、设计、开发软、硬的能力。

本文以单片机为核心,采用串行时钟芯片DS1302。

过去多用并行接口的时钟芯片,如MC146818、DS12887 等。

它们已能完全满足单片机系统对实时时钟的要求,但是这些芯片与单片机接口复杂、占用地址, 数据总线接线多、芯片体积大占用空间多。

显示电路采用LED动态扫描方式,动态扫描方式节省外部接口资源。

本文通过对一个基于单片机的能实现万年历功能电子时钟的设计,从而达到学习、了解单片机相关指令在各方面的应用。

系统由主控制器A T89C52、时钟电路DS1302、显示电路、按键电路、和复位电路等部分构成,能实现时钟日历显示的功能,能进行年、月、日、时、分及星期的显示。

关键词:AT89C52芯片DS1302芯片C语言Keil软件LED动态显示;AbstractSCM rapid development of applied technology, we now live Looking at the various fields, from the missile's navigation devices, to the various instruments on the aircraft control, computer network communications and data transmission, industrial automation to the process of real-time control and data Processing, and we live in the extensive use of the smart IC cards, these are inseparable from the SCM. S CM is set CPU, RAM, ROM, timing, counting on one interface and a variety of microcontrollers. Its small size, low cost, feature strong, smart widely used in industry and industrial automation. And 51 of the SCM SCM is the most typical and most representative one. The graduation project through its study, and thereby to study, design, develop software and hardware capabilities.Based on SCM as the core, a serial clock chip DS1302. Past the use of parallel interface chip's clock, such as the MC146818, DS12887, and so on. They have been able to fully meet the SCM system to the requirements of real-time clock, but these chips and microcontroller interface complex, occupied address, data bus wiring, chip size of the space and more. LED display circuit using dynamic scan mode, dynamic scan mode external interface save resources.Based on a microcontroller based on the calendar function to achieve the design of electronic clock, so as to achieve learning and understanding of SCM related instructions in all aspect s of the application. System by the main controller AT89C52, clock circuit DS1302, show circuit, the circuit keys, and reset circuit, and other components, to achieve the clock showed that the calendar function, capable of year, month, day, hour, minute an d weeks of shows.Key W ords:AT89C52 Chip DS1302 Chip Keil C language software LED dynamic display;目录摘要 (I)Abstract (II)目录........................................................................................................... 错误!未定义书签。

题目:带温度显示的万年历的设计姓名:学院:组别:万年历的设计与实现摘要随着科技的快速发展,时间的流逝,至从观太阳、摆钟到现在电子钟,人类不断研究,不断创新纪录。

美国DALLAS公司推出的具有涓细电流充电能的低功耗实时时钟电路DS1302。

它可以对年、月、日、周日、时、分、秒进行计时,还具有闰年补偿等多种功能,而且DS1302的使用寿命长,误差小。

对于数字电子万年历采用直观的数字显示,可以同时显示年、月、日、周日、时、分、秒和温度等信息,还具有时间校准等功能。

该电路采用AT89S52单片机作为核心,能够显示从2000至2099年的年、月、日、星期、时、分、秒。

同时还可以对当前环境温度进行实时测量。

系统具有读取方便、显示直观、功能多样、电路简洁、成本低廉等诸多优点,符合电子仪器仪表的发展趋势,具有广阔的市场前景。

关键词:单片机,时钟芯片,多功能万年历,数码管,温度传感器ABSTRACTWith the rapid development of science and technology, the passage of time, tofrom the view of the sun, pendulum clock to the present clock, humans continue to study, and continuously record. DALLAS United States that have launched small trickle charge current to a low-power real time clock circuitry of the DS1302. It can be year, month, day, Sunday, hours, minutes, seconds for time, but also has a leap year compensation to a variety of functions, and the DS1302's long life, small error. For the digital electronic calendar using an intuitive digital display can simultaneously display year, month, day, Sunday, hours, minutes, seconds, and temperature and other information, but also a time-calibration and other functions.The circuit uses AT89S52 microcontroller as the core,, can demonstrate from 2000 to 2099 year, month, Japan, week, divides, the second and carries on the integral point to report time.. The system has the read to be convenient, the demonstration is direct-viewing, the function is diverse, the electric circuit is succinct, cost inexpensive and so on many merits, conforms to the electronic instrumentation measuring appliance's trend of development, has the broad market prospect.KEY WORDS: monolithic integrated circuit;real time clock;multi-purpose ten thousand calendars;LED;temperature sensor.一、设计要求与方案论证1.1 设计要求:①系统具有年、月、日、星期、时、分等功能;②系统具有温度计功能;③系统具备年、月、日、星期、时、分校准功能;1.2 系统基本方案选择和论证1.2.1单片机芯片的选择方案和论证:方案一:采用89C51芯片作为硬件核心,采用Flash ROM,内部具有4KB ROM 存储空间,能于3V的超低压工作,而且与MCS-51系列单片机完全兼容,但是运用于电路设计中时由于不具备ISP在线编程技术, 当在对电路进行调试时,由于程序的错误修改或对程序的新增功能需要烧入程序时,对芯片的多次拔插会对芯片造成一定的损坏。

基于单片机的万年历设计报告一、研究意义随着当今世界经济的快速发展和信息化时代的来临,各种各样的小型智能家电产品陆续出现在我们的生活当中。

日历是人们不可或缺的日常用品。

但一般日历都为纸制用品,使用不便,寿命不长。

电子万年历采用智能电子控制和显示技术,改善了纸制日历的缺陷。

本设计以AT89S52单片机为核心,构成单片机控制电路,AT89C52是一种带8K字节闪速可编程可擦除只读存储器(PEROM)的低电压、高性能CMOS 8位为控制器。

该器件采用ATMEL 非易失存储器制造技术制造,与工业标准的80C51和80C52指令集和输出管脚相兼容。

结合DS1302时钟芯片和24C02 FLASH存储器,完成时间的自动调整和掉电保护,全部信息用液晶显示。

时间、日期调整由三个按键来实现,并可对闹铃开关进行设置。

日历能显示阳历和阴历年、月、日以及星期、时、分、秒。

在显示阴历月份时,能标明是否闰月。

二、总体方案设计本设计以AT89S52单片机为核心,构成单片机控制电路,结合DS1302时钟芯片和24C02 FLASH存储器,显示阳历的年、月、日、星期、时、分、秒和阴历的年、月、日,在显示阴历时间时,能标明是否闰月,同时完成对它们的自动调整和掉电保护,全部信息用液晶显示出来。

输入接口由三个按键来实现,用这三个按键可以对日期和时间进行调整,并可以对闹铃的开关和闹铃的时间进行设置。

闹铃功能通过蜂鸣器来实现。

软件控制程序实现所有的功能。

整机电路使用+5V稳压电源,可稳定工作。

系统框图如图2-1所示,其软硬件设计简单,时间记录准确,可广泛应用于长时间连续显示的系统中。

三、系统硬件设计按照系统设计功能的要求,初步确定设计系统由主控模块、时钟模块、存储模块、键盘接口模块、显示模块和闹铃模块共6个模块组成,电路系统构成框图如图3-1所示。

主控芯片使用52系列AT89S52单片机,时钟芯片使用美国DALLAS公司推出的一种高性能、低功耗、带RAM的实时时钟芯片DS1302,存储模块采用美国ATMEL公司生产的低功耗CMOS串行EEPROM存储芯片AT24C02。

图书分类号:密级:毕业设计(论文)基于AT89S52单片机的电子万年历BASED ON AT89S52 MONOLITHIC INTEGRATED CIRCUIT ELECTRONIC TEN THOUSAND CALENDARS学生姓名廖东东学院名称信电工程学院专业名称电子信息工程技术指导教师潘晓博年月日摘要现在是一个知识爆炸的新时代,新产品、新技术层出不穷,电子技术的发展更是日新月异。

可以毫不夸张的说,电子技术的应用无处不在,电子技术正在不断地改变我们的生活,改变着我们的世界。

在这快速发展的年代,时间对人们来说是越来越宝贵,在快节奏的生活时,人们往往忘记了时间,一旦遇到重要的事情而忘记了时间,这将会带来很大的损失。

因此我们需要一个定时系统来提醒这些忙碌的人,而数字化的钟表给人们带来了极大的方便。

由于单片机具有灵活性强、成本低、功耗低、保密性好等特点,所以电子日历时钟一般都以单片机为核心,外加一些外围设备来实现。

近些年,随着科技的发展和社会的进步,人们对数字钟的要求也越来越高,传统的时钟已不能满足人们的需求。

多功能数字钟不管在性能还是在样式上都发生了质的变化,有电子闹钟、数字闹钟等等。

单片机在多功能数字钟中的应用已是非常普遍的,人们对数字钟的功能及工作顺序都非常熟悉。

但是却很少知道它的内部结构以及工作原理。

由单片机作为数字钟的核心控制器,可以通过它的时钟信号进行计时实现计时功能,将其时间数据经单片机输出,利用显示器显示出来,通过按键可以进行定时、校时功能。

输出设备显示器可以用液晶显示技术和数码管显示技术。

随着科技的快速发展,时间的流逝,至从观太阳、摆钟到现在电子钟,人类不断研究,不断创新纪录。

美国DALLAS公司推出的具有涓细电流充电能的低功耗实时时钟电路DS1302。

它可以对年、月、日、周日、时、分、秒进行计时,还具有闰年补偿等多种功能,而且DS1302的使用寿命长,误差小。

对于数字电子万年历采用直观的数字显示,可以同时显示年、月、日、周日、时、分、秒和温度等信息,还具有时间校准等功能。

摘要在当代繁忙的工作与生活中,时间与我们每一个人都有非常密切的关系,每个人都受到时间的影响。

为了更好的利用我们自己的时间,我们必须对时间有一个度量,因此产生了钟表。

钟表的发展是非常迅速的,从刚开始的机械式钟表到现在普遍用到的数字式钟表,即使现在钟表千奇百怪,但是它们都只是完成一种功能——计时功能,只是工作原理不同而已,在人们的使用过程中,逐渐发现了钟表的功能太单一,没有更大程度上的满足人们的需求。

因此在这里,我想能不能把一些辅助功能加入钟表中去。

在此设计中所设计的钟表不但具有普通钟表的功能,它还能实现一个额外的功能:温度测量。

且数字电子万年历采用直观的数字显示,可以同时显示年、月、日、周日、时、分、秒和温度等信息,还具有时间校准等功能。

该电路采用AT89C52单片机作为核心,功耗小,能在3V的低压工作,电压可选用3~5V电压供电.。

具有较高的实用性。

关键词:单片机AT89C52;万年历; DS18B20温度传感器;时钟芯片DS12C887AbstractIn contemporary work and busy life, time and every one of us has a very close relationship, each person affected by time. In order to better use of our own time, we must have a measure of time, resulting in a watch. Clocks is a very rapid development, from the beginning of the mechanical watches that is now widely used in digital watches, clocks, even though it is now unusual, but they are just completed a feature - a time function, working principle is different in people's use of the process, and gradually found a single watch function too, there is no greater demand to meet the people. So here, I would like to be able to watch a number of auxiliary functions to join in to.In the design of the watches designed not only has the general functionality of watches and clocks, it can achieve an additional function: temperature measurement. And digital electronic calendar using intuitive digital display, you can also display year, month, day, weekdays, hours, minutes, seconds and temperature information, but also time-calibration functions. AT89C52 single-chip microcomputer of the circuit as the core of power in small, low-pressure in the work of 3V, voltage can be selected 3 ~ 5V supply voltage.. Have a high relevance.Key words:single-chip microcomputer AT89C52; calendar; DS18B20 temperature sensor; clock chip DS12C887目录绪论 (1)1. 方案设计 (2)1.1 课题开发背景 (2)1.2 设计的目的 (2)1.3 设计的意义 (3)1.4 国内外发展 (3)1.5 总体方案论证与选择 (3)1.6 模块方案论证与选择 (4)1.6.1 时钟模块 (4)1.6.2 键盘模块 (4)1.6.3 显示模块 (5)1.6.4 温度传感器模块 (5)2. 系统总体设计 (6)2.1 电路设计框图 (6)2.2 系统硬件概述 (7)2.3 单片机AT89C52功能介绍 (7)2.4 时钟模块设计 (13)2.5 温度采集模块 (16)2.6 显示模块 (22)2.7 电源电路部分 (26)2.7.1 电路组成 (26)2.7.2 三端稳压集成电路7805 (27)2.8 键盘部分 (28)2.9 报警模块 (30)2.9.1 报警电路 (30)2.9.2 NE555芯片 (30)结论与展望 (32)结论 (32)单片机的发展趋势 (32)致谢 (33)参考文献 (34)附录一 (35)绪论电子钟已成为人们日常生活中必不可少的物品,广泛用于个人家庭以及车站、码头、剧院、办公室等公共场所,给人们的生活、学习、工作、娱乐带来极大的方便。

课程设计报告题目多功能数字钟课程名称电子系统设计与工程实践院部名称电子与信息工程学院专业电子信息工程班级电子1001班学生姓名李盖(1010910101)指导教师荣峰多功能数字钟完成人:李盖(电子1001)摘要:随着人类科技文明的发展,人们对于时钟的要求在不断地提高。

时钟已不仅仅被看成一种用来显示时间的工具,在很多实际应用中它还需要能够实现更多其它的功能。

高精度、多功能、小体积、低功耗,是现代时钟发展的趋势。

在此次设计中,电路具有显示时间的其本功能,还可以实现对时间的调整。

具有小巧,价格低廉,走时精度高,使用方便,功能多等特点。

本设计的控制核心是单片机(STC90C516RD+),采用蜂鸣器、液晶显示器(LCD12864)、及其他电路构成。

实现了时间设置、闹铃设置、闹铃开和关、显示节日、显示生日、显示农历、生日时播放音乐、整点报时以及温度采集等功能。

关键词:多功能时钟,温度采集,闹铃,农历,显示节日1、设计要求1.利用LCD显示“年、月、日、星期、时、分、秒”信息,并可通过键盘修改当前时间。

2.具有闹钟时间设置和闹铃功能,利用蜂鸣器进行闹铃。

当闹铃发生时,能够通过按键取消闹铃。

3.利用温度传感器检测环境温度,并显示在LCD上。

2、总体设计2.1系统组成系统由单片机主控模块、时钟模块、测温模块、报警模块、显示模块、键盘接口模块共6个模块组成,电路系统框图下图所示:图1 系统框图2.2工作原理本设计核心器件之一时钟芯片DS1302,其主要特点是采用串行数据传输,可为掉电保护电源提供可编程的充电功能,并且可以关闭充电功能。

采用普通32.768KHz晶振。

采用STC90C51作为主控芯片,利用它定期的读取时钟芯片DS1302中的时间并显示在LCD上;通过算法得出阴历日期并显示在LCD 上。

2.3用户至上的设计通过合理的布局,将键盘设置在LCD屏的下方,方便操作;其他的元路隐藏在LCD的后面使外观整洁简约。

目录一、引言 (2)二、方案论证选择 (3)2.1设计要求 (3)1.基本要求 (3)2.发挥部分 (3)2.2系统框图 (3)分钟+调整 (3)秒钟 (3)时钟+调整 (3)秒表 (3)闹钟功能 (3)定时报闹 (3)万年历功能 (3)三、电路仿真与设计 (4)3.1核心芯片及芯片管脚图 (4)3.2时、分计数电路模块设计 (4)3.3切换电路模块设计 (5)3.4调整电路模块设计 (6)(1)方案一:利用74125的三态。

(6)(2)方案二:利用74162的置数端(LOAD),置数调整。

(7)3.5整点报时电路模块设计 (8)3.6秒表电路模块设计 (9)3.6定时报闹电路模块设计 (11)3.7万年历电路模块设计 (12)四、遇到的问题.......................................................................... 错误!未定义书签。

五、心得体会.............................................................................. 错误!未定义书签。

一、引言电子钟亦称数显钟(数字显示钟),是一种用数字电路技术实现时、分、秒计时的装置,与机械时钟相比,直观性为其主要显著特点,且因非机械驱动,具有更长的使用寿命,相较石英钟的石英机芯驱动,更具准确性。

电子钟已成为人们日常生活中必不可少的必需品,广泛用于个人家庭以及车站、码头、剧院、办公室等公共场所,给人们的生活、学习、工作、娱乐带来极大地方便。

相对于其他时钟类型,它的特点可归结为“两强一弱”:比机械钟强在观时显著,比石英钟强在走时准确,但是它的弱点为显时较为单调。

数字钟的核心即数字电子技术课程中有关时序逻辑电路、组合逻辑电路的内容。

这些也是我们学电子的学生应该掌握的最基本知识。

通过这次试验,不仅可以加深我对数字电子技术课程的理解,也可以提高自己的动手能力以及实际问题中解决问题的能力,培养对数字电子技术的兴趣。

1. 综述1.1 课题背景1.1.1 概述随着电子技术的迅速发展,特别是随着大规模集成电路的产生而出现的微型计算机,给人类生活带来了极大的方便。

走入家庭,从洗衣机、微波炉到音响、汽车,到处都可以见到单片机应用的踪影。

如果说微型计算机技术的出现使现代科学研究得到了质的飞跃,那么也可以毫不夸张的说:“单片机技术的出现则是给现代工业测控领域带来了一次新的工业革命”。

目前,单片机以其可靠性高和智能性等特点被广泛应用到工业控制系统、数据采集系统、智能化仪器仪表、办公自动化等领域中,并已经进入家庭,因此,单片机技术的开发和应用水平已经逐步成为一个国家自动化发展水平的标志之一。

本课题就是以单片机为主体与其它常用器件组合设计而成。

代表了单片机的主流发展方向。

本课题实现一个实用而又相对简单的电子万年历。

在市场上精致而且漂亮的万年历有很多,不过任何一个事物都不是完美的,都有可以进一步发展的余地。

本设计由51系列单片机和时钟芯片DS1302以及LED实现,功能齐全且实用。

1.1.2 单片机的发展历程单片机是微型计算机的一个重要分支,也是一种非常活跃和颇具生命力的机种,特别适用于工业控制领域。

1971年微处理器研制成功不久,就出现了单片机,但最早的单片机是1位的,处理能力有限。

单片机的发展共分四个阶段:第一阶段是初级阶段,功能非常简单;第二阶段是低性能阶段,以INTEL公司制造的MCS-48系列单片机为代表。

第三阶段为高性能单片机阶段,这个阶段推出的单片机普遍带有串行接口,多级中断系统,16位定时器/计数器,片内ROM、RAM容量加大,直到现在仍被广泛应用,是目前应用数量较多的单片机。

第四阶段是8位单片机巩固发展以及16位单片机、32位单片机推出阶段,以满足不同的用户需要。

纵观单片机几十年的发展历程,单片机的今后发展方向将向多功能、高性能、高速度、低功耗、低价格、外围电路内装化以及内存储器容量增加和FLASH存储器化方向发展。

电子万年历设计学生:XXX 指导教师:XXX内容摘要:这次设计以生活中常用的万年历挂钟为例,从系统功能说明出发,对控制系统的组成结构、系统设备选型进行了分析。

在硬件设计一节给出了详细的硬件电路设计图,并对各功能部件与AT90S8535单片机的连接进行了详细的讲解。

在软件设计一节给出了系统的程序控制流程图,对各部分程序进行了分析说明。

最后简要地介绍了系统集成与测试的方法。

万年历挂钟设计的方案很多。

在本次设计中选用高性能低功耗的AVR架构单片机AT90S8535作为系统的控制核心,并选用高集成度的实时时钟芯片SD2303和DS1722温度传感器来处理时间和温度检测任务。

AT90S8535单片机带有SPI接口,能非常便利地实现和DS1722的通信。

在与实时时钟芯片SD2303通信时采用了模拟IIC总线的方式。

本次设计的万年历挂钟能实现实时时间和温度的检测和显示。

通过设置的7个独立的按键来调整时间和设置闹铃。

需要指出的是,实时时钟芯片以设定的初始时间为基准进行计时,故用户在设置时间时必须保证所设置时间的合理性。

在设置闹铃时,程序会对所设置时间的合理性进行检测,任何不合理的时间设置将关闭闹铃功能。

鉴于系统设计的复杂性,万年历挂钟设计中没有加入阳历和阴历的转换。

我们可以在本设计的基础上使用专用的芯片或者使用软件算法来实现这一功能,这样万年历挂钟的功能将更加完善。

关键字:万年历 DS1722温度传感器 AT90S8535单片机Electronic calendarAbstract:The design use the calendar clock of the life as an example, starting from the system description, analyze the composition of the control system structure and system equipment selection. Software design in a given process control system flow chart of the various parts of the analysis procedure. Finally, a brief description of system integration and testing method.Calendar clock program designed many. Design in this selection of high-performance low-power AVR architecture AT90S8535 single chip as the core control system and select a high level of integration of real-time clock chip SD2303 and DS1722 temperature sensor to the processing time and temperature detection task. AT90S8535 single chip with SPI interface, can be very convenient to achieve the communication and DS1722. With real-time clock chip SD2303 communication IIC bus using a simulation approach.The calendar designed to achieve real-time clock time and temperature detection and display. Alarm in the settings, the program will be the setup time for testing the reasonableness of any unreasonable period of time set alarm feature will be closed.In view of the complexity of system design, calendar clock design are not members of the solar calendar and lunar calendar conversion. We can design based on the use of a dedicated chip, or the use of software algorithms to achieve this function, the function of this calendar clock will be more perfect.Keyword:calendar DS1722 temperature sensor A T90S8535 single chip目录前言 (1)1 电子万年历介绍 (1)1.1.1 时间显示 (1)1.1.2 时间调整 (1)1.1.3 定时闹钟 (1)1.1.4 温度显示 (1)1.1.5 掉电运行 (1)1.2 应用系统设计 (2)1.2.1 系统方案设计 (2)1.2.2 应用系统结构设计 (2)1.2.3 设备选型 (3)1.2.4 控制面板设计 (4)2 硬件电路设计 (5)2.1.1 AVRRISC结构 (5)2.1.2 数据和非易失性程序存储器 (5)2.1.3 外围器件特点 (5)2.1.4 MCU特点 (5)2.1.5 4MHz3V20℃条件下的功耗(AT90S8535) (6)2.1.6 I/O接口和封装 (6)2.2 实时时钟电路设计 (6)2.2.1 实时时钟芯片SD2303简介 (6)2.2.2 SD2303的引脚设置 (6)2.3 温度检测电路设计 (7)2.3.1 温度传感器DS1722简介 (8)2.3.2 DS1722的引脚配置 (8)2.5 键盘及闹钟电路设计 (10)3 软件设计 (11)3.1 主程序设计 (11)3.2 按键检测和处理程序 (12)3.3 系统集成与测试 (13)4 单片机控制系统抗干扰技术 (14)4.1 干扰的来源分析 (14)4.2 硬件抗干扰技术 (14)4.3 软件抗干扰技术 (14)4.4 供电系统抗干扰技术 (14)5 结束语 (15)附录 (16)参考文献 (17)电子万年历前言随着现代社会工作和生活节奏的加快,越来越需要人们对时间的准确把握,一旦遇到重要的事情而忘记了时间,这将会带来很大的损失。

物理与电子科学学院电子电工实验基于DS1302多功能数字时钟--万年历实验报告实验名称:基于DS1302多功能数字钟试验日期: 2014年 01 月 05 日专业:电子信息工程姓名:刘斌班级:物电 1105 班学号: 2011112030560一、设计理念:电子万年历是一个应用非常广泛的实用日常计时工具,带有显示温度,显示世纪,年,月,日,星期,时,分,秒和按键可调时间及其按键设置闹钟的功能,同时具有月末自动更新,闰年补偿功能,整点报时等多种功能。

环境温度检测系统在日常生活和工业应用非常广泛,能实时采集周围的温度信息进行显示。

此系统是基于STC89C52单片机设计的,包含液晶显示模块,DS1302实时时钟模块,DS18B20温度采集模块,键盘扫描模块,蜂鸣器报警模块。

STC89C52作为控制核心,具有功耗低,功能强等特点,电压可选3到5V电源供电。

显示模块采用1602液晶动态显示,相对数码管而言经济实用,占用空间小,对于显示数字、字母最为合适,而且与单片机连线简单,占用IO口相对较少。

实时时钟芯片DS1302是一款经济实惠功能强大的较新型产品,该器件提供RTC/日历,可外加器件实现定时闹钟等功能,如果检测到主电源故障,该器件可自动切换到备用电源供电,可以保证在断电情况下精准走时,计时。

温度检测显示模块采用数字式温度传感器DS18B20,该芯片具有精度高,测量范围广等优点,易与单片机连接,模块电路组成简单并同时具有温度报警功能。

关键词:STC89C52,DS1302,DS18B20,1602液晶显示,电子万年历,采集设备周围环境温度、整点报时,闹钟时分通过按键设置,时、分、秒、年、月、日、星期通过按键进行调节校准……二、设计思路:核心控制体:STC89C52单片机实时时钟芯片:DS1302数字式温度传感器:DS18B20总共设有四个按键,为节约资源考虑,每个按键都有多种功能。

四个按键分别标号为key1,key2,key3,key4。

电子时钟万年历设计报告学院:班级:组员:一、设计要求与方案论证 (3)1.1 设计要求: (3)1.1.1基本要求 (3)1.1.2发挥部分 (3)1.2 系统基本方案选择和论证 (3)1.2.1单片机芯片的选择方案和论证: (3)1.2.2 显示模块选择方案和论证: (4)1.2.3时钟芯片的选择方案和论证: (4)1.3 电路设计最终方案决定 (4)二、理论分析与计算 (4)2.1,秒数的产生由定时器T0产生: (4)三.系统的硬件设计与实现 (5)3.1 电路设计框图: (5)3.2 系统硬件概述: (6)3.3 主要单元电路的设计 (6)3.3.1单片机主控制模块的设计 (6)3.3.2显示模块的设计 (7)3.3.3闹钟模块的设计 (9)3.3.4电源稳压模块 (9)四、系统的软件设计 (10)4.1程序流程框图 (10)4.2闹钟模块流程图: (11)4.3按键调整模块流程图: (11)五、测试方案与测试结果分析 (13)5.1 测试仪器 (13)5.2软件测试平台 Keil C51 (13)5.3 模块测试 (13)5.3.1显示模块测试 (13)5.4测试结果分析与结论 (14)5.4.1测试结果分析 (14)5.4.2 测试结论 (14)六、作品总结 (14)参考文献 (14)附录一:系统电路图 (15)附录三:系统C程序 (16)一、设计要求与方案论证1.1 设计要求:1.1.1基本要求(1)准确显示:时、分、秒(24小时制)(2)显示星期(3)显示公历(4)时间、日期、星期可调节(5)断电记忆功能1.1.2发挥部分(1)闹钟功能(2)显示阴历(3)显示24节气(4)其他1.2 系统基本方案选择和论证1.2.1单片机芯片的选择方案和论证:方案一:采用89C51芯片作为硬件核心,采用Flash ROM,内部具有4KB ROM 存储空间,能于3V的超低压工作,而且与MCS-51系列单片机完全兼容,但是运用于电路设计中时由于不具备ISP在线编程技术, 当在对电路进行调试时,由于程序的错误修改或对程序的新增功能需要烧入程序时,对芯片的多次拔插会对芯片造成一定的损坏。

课程设计报告课程设计名称 SOPC原理及应用专业电子科学与技术班级电子13-1班学号姓名郑航指导教师冯丽成绩2016年1月13日目录一、设计目的 (1)二、设计内容要求 (1)三、系统软、硬件需求分析 (1)1. 硬件系统组成规划 (1)2. 软件系统规划 (2)四、设计步骤 (3)3. 新建工程“count_binary” (3)4. 添加ip核 (4)5. 添加SDRAM Controller (5)6. 添加flash (6)7. 添加外部RAM总线(Avalon三态桥) (7)8. 添加pio核 (7)9. 添加cpu核 (8)10. 添加LCD核 (9)11. 自动分配基地址并生成系统 (9)12. 设置顶层模块图 (10)13. 管脚分配并编译 (11)14. 启动Nios II IDE,新建工程 (12)15. 导入设计程序 (12)16. 编译工程并烧录 (13)五、设计结果 (14)六、源程序 (16)1. 程序......................................... 错误!未定义书签。

2. 程序......................................... 错误!未定义书签。

3. 程序......................................... 错误!未定义书签。

4. 程序 (16)七、实验心得 (28)项目基于NiosII系统的电子钟设计一、设计目的1.掌握基本的开发流程。

2.熟悉QUARTUS II软件的使用。

3.熟悉NIOS II软件的使用。

4.掌握SOPC硬件系统的搭建和NIOSII软件编程方法。

5.掌握SOPC系统设计方法。

6.进一步了解简单的设置及其编程。

二、设计内容要求NiosII系统的硬件设计,软件设计,该系统能实现一个电子钟功能。

三、系统软、硬件需求分析1.硬件系统组成规划根据系统要实现的功能和开发板配置,本项目中需要用到的Cyclone II开发板上的外围器件有:LCD:电子钟显示屏幕按钮:电子钟设置功能键Flash存储器:存储软、硬件程序SRAM存储器:程序运行时将其导入SRAM根据所用到的外设和器件特性,在SOPC Builder中建立系统要添加的模块包括:NiosII CPU定时器,按键PIO,LCD,外部RAM总线(Avalon三态桥),外部RAM接口,外部Flash接口。

2.软件系统规划要实现系统所需的功能,大量的工作应该集中在软件设计和优化上。

电子钟的软件功能主要分为显示、设置和时间算法三大部分。

①显示部分显示部分的功能包括:显示日期(年-月-日)显示时间(小时:分钟:秒)②设置部分设置部分的功能包括:设置小时,设置分钟,设置年份,设置月份,设置日期。

设置部分的程序主要用在对按键的响应。

在编写程序前要对开发板上的四个按键功能进行如下分配:SW0:换行键,可选择设置第一行或者第二行SW1:选项数字减少SW2:选项数字增加SW3:选择键,可依次选择设置小时,分钟或者年份,月份和日期③时间算法部分时间算法部分的功能包括:(a). 时间累加(b). 确定每个月的最大天数,使年、月、日能正确累加通过对软件要完成的功能进行分析可以看出,这里只有按键响应和显示部分需要涉及硬件,其它子程序可在进行硬件设计的同时开始编写。

③软件流程图四、设计步骤3.新建工程“count_binary”4.添加ip核点击 Tools->SOPC Builder,进入SOPC Builder,运行SOPC Builder,添加ip核。

5.添加SDRAM Controller6.添加flashAddress Wicth设置为22,Data Wicth设置为16。

Setup、Wait、Hold都设置为40。

7.添加外部RAM总线(Avalon三态桥)8.添加pio核添加一组PIO(Parallel I/O)宽度设置为4位,方向设置为输入,并命名为button_pio。

9.添加cpu核双击Avalon Components ( NiosII Processor,添加一个 NiosII/s 处理器并将Reset Vector改为cfi _flash_0,Exception Vector改为sdram。

10.添加LCD核11.自动分配基地址并生成系统最小系统NIos_small所需组件添加完毕,自动分配基地址和中断,分别选择“System|Auto‐Assign Base Adresses”和“System| Auto‐Assign IRQs”。

并把ip核名字改为如下图。

点击“Generate”,SOPC Builder会提示生成系统的进程,系统生成完成的时会提示“SUCCESS:SYSTEM GENERATION COMPLETED”。

单击“EXIT”按钮退出SOPC Builder。

12.设置顶层模块图回到QuartusII里面,新建一个图形设计原理图,托出刚才SOPC Builder 生成的系统图形,再设计一个PLL锁相环,如图:13.管脚分配并编译打开,把需要用到的管脚复制到qsf文件中,并把引脚的名字改成与qsf 文件中的名字一致,未使用的管脚置成三态,设置完开始编译。

14.启动Nios II IDE,新建工程至此硬件设置已完成,动Nios II IDE,新建工程选择“File| New | Project”。

在New Project对话框中选择“NiosC/C++Application” 单击“Next”,左栏中选择“Blank Project”模板,工程名为“clock”,点击“Browse…”选SOPC Builder System选择刚生成的最小系统文件“”,15.导入设计程序把编写好的、、、文件复制路径count_binary\software\clock里,复制完成后,回到NiosII IDE下,右键点击clock,选择Refresh,刷新一下软件工程列表,打开加号就会看到添加的四个文件,双击可以看到C语言程序源码。

16.编译工程并烧录右击工程名选择“System Library Properties”,进入系统设置界面。

设置完成后选择“Project| Build all”进行编译。

编译完成后“Tools|Quartus II Programmer…”,将程序下载至开发板上的FPGA。

再选择“Run|Run As|Nios II Hardware”,在开发板的16x2 LCD上观看设计结果。

五、设计结果六、源程序程序#include ""#include <>#include <>#include <>#include ""#include "sys/"#include ""#include ""#include ""volatile int edge_capture;void LCD_Init(){lcd_write_cmd(LCD_BASE,0x38);usleep(2000);lcd_write_cmd(LCD_BASE,0x0c);usleep(2000);usleep(2000);lcd_write_cmd(LCD_BASE,0x06);usleep(2000);lcd_write_cmd(LCD_BASE,0x80);usleep(2000);}void LCD_Show_Text(char* Text){int i;for(i=0;i<strlen(Text);i++){lcd_write_data(LCD_BASE,Text[i]); usleep(2000); }}void LCD_Line1(){lcd_write_cmd(LCD_BASE,0x80);usleep(2000);}void LCD_Line2(){usleep(2000);}static void handle_button_interrupts(void* context,alt_u32 id){volatile int* edge_capture_ptr=(volatile int*)context;*edge_capture_ptr=IORD_ALTERA_AVALON_PIO_EDGE_CAP(BUTTON_PIO_BASE);IOWR_ALTERA_AVALON_PIO_EDGE_CAP(BUTTON_PIO_BASE,0);}static void init_button_pio(){void* edge_capture_ptr=(void*)&edge_capture;IOWR_ALTERA_AVALON_PIO_IRQ_MASK(BUTTON_PIO_BASE,0xf);IOWR_ALTERA_AVALON_PIO_EDGE_CAP(BUTTON_PIO_BASE,0x0);alt_irq_register(BUTTON_PIO_IRQ,edge_capture_ptr,handle_button_interr upts);}void delay(unsigned int x){while(x--);}int check_month(int month){ if((month==1)||(month==3)||(month==5)||(month==7)||(month==8)||(month==10)||(month==12))return 1;if((month==4)||(month==6)||(month==9)||(month==11))return 2;}int check_year(int year){if(((year%400)==0)||(((year%4)==0)&& ((year%100)!=0))) return 1;else return 0;}int main(void){int screen=0;int pos=0;int year,month,day,hour,minute,second;unsigned long sum;char date[16];char time[16];int year1=6;int year2=0;int year3=0;int year4=2;int month1=1;int month2=0;int day1=1;int day2=0;int hour4,hour3,hour2,hour1,minute2,minute1,second2,second1; unsigned int screenflag;hour=0;minute=0;second=0;year=2006;month=1;day=1;init_button_pio();LCD_Init();while(1){if(pos>=3)pos=0;if(screen>=2)screen=0;if(screen==0)screenflag=8;else screenflag=0;usleep(1000000);if(second<59)second++;else{second=0;if(minute<59)minute++; else{minute=0;if(hour<23)hour++;else{hour=0;if(day<30)day++;else{day=1;if(month<12)month++;else{month=1;if(year<9999)year++;else year=2005; }}}}}switch(edge_capture){case 0x08:pos=pos+1;break;case 0x02:if(pos==0){if(screen==0){if(day>1)day--;else{if(check_month(month)==0)day=30;if(check_month(month)==1)day=31;if(check_month(month)==2){if(check_year(year))day=29;else day=28; }}}if(screen==1){if(second>0)second--;else second=59;}} if(pos==1){if(screen==0){if(month>1)month--;else month=12;}if(screen==1){if(minute>0)minute--;else minute=59;}} if(pos==2){if(screen==0){if(year>0)year--;else year=2005;}if(screen==1){if(hour>0)hour--;else hour=23;}}break;case 0x04:if(pos==0){if(screen==0){if(check_month(month)==0){if(day<30)day++;else day=1;}if(check_month(month)==1){if(day<31)day++;else day=1;}if(check_month(month)==2){if(check_year(year)){if(day<29)day++;else day=1;} else{if(day<28)day++;else day=1;}}}if(screen==1){if(second<59)second++;else second=0;}}if(pos==1){if(screen==0){if(month<12)month++;else month=1;}if(screen==1){if(minute<59)minute++;else minute=0;}} if(pos==2){if(screen==0){if(year<9999)year++;else year=2005;}if(screen==1){if(hour<23)hour++;else hour=0; }} break;case 0x01:screen++;break; }edge_capture=0;{year4=year/1000;year3=(year-year4*1000)/100;year2=(year-year4*1000-year3*100)/10;year1=year%10;month2=month/10;month1=month%10;day2=day/10;day1=day%10;LCD_Line1();date[0]=year4+0x30;date[1]=year3+0x30;date[2]=year2+0x30;date[3]=year1+0x30;date[4]=' ';date[5]=' ';date[6]=month2+0x30;date[7]=month1+0x30;date[8]=' ';date[9]=' ';date[10]=day2+0x30;date[11]=day1+0x30;date[12]=' ';date[13]=' ';date[14]=' ';date[15]=' ';LCD_Show_Text(date);}{ hour4=0;hour3=0;hour2=hour/10;hour1=hour%10;minute2=minute/10;minute1=minute%10;second2=second/10;second1=second%10;time[0]=' ';time[1]=' ';time[2]=hour2+0x30;time[3]=hour1+0x30;time[4]=' ';time[5]=' ';time[6]=minute2+0x30;time[7]=minute1+0x30;time[8]=' ';time[9]=' ';time[10]=second2+0x30;time[11]=second1+0x30; time[12]=' ';time[13]=' ';time[14]=' ';time[15]=' ';LCD_Line2();LCD_Show_Text(time);}}}七、实验心得指导老师签字:年月日。