第一章 绪论

1、哈佛结构:

采用双存储空间,程序存储器和数据存储器分开,有各自独立的程序总线和数据总线,可独立编址和独立访问,可对程序进行独立传输,使取指令操作、指令执行操作、数据吞吐并行完成,大大地提高了数据处理能力和指令的执行速度,非常适合于实时的数字数字信号处理。

2、冯。诺依曼结构:

采用单存储空间,即程序和数据公用一个存储空间,使用单一的地址和数据总线,取指令和取操作数都是通过一条总线分时完成的。

当进行高速运算时,不但不能同时进行取指令和取操作数,而且还会造成数据传输通道的瓶颈现象。

3、流水线技术

每条指令可通过片内多功能单元完成取址、译码、取操作数和执行等多个步骤,实现多条指令的并行执行,从而在不提高系统时钟频率的条件下减少每条指令的执行时间。

4、DSP 的分类

1)、按基础特性分类:静态DSP 芯片和一致性DSP 芯片

2)、按用途分:通用型芯片和专用型芯片

3)、按数据格式分(即按精度或动态范围):定点DSP 和浮点DSP (大多数定点DSP 芯片都采用16bit 定点运算,只有少数DSP 芯片为24bit 定点运算)

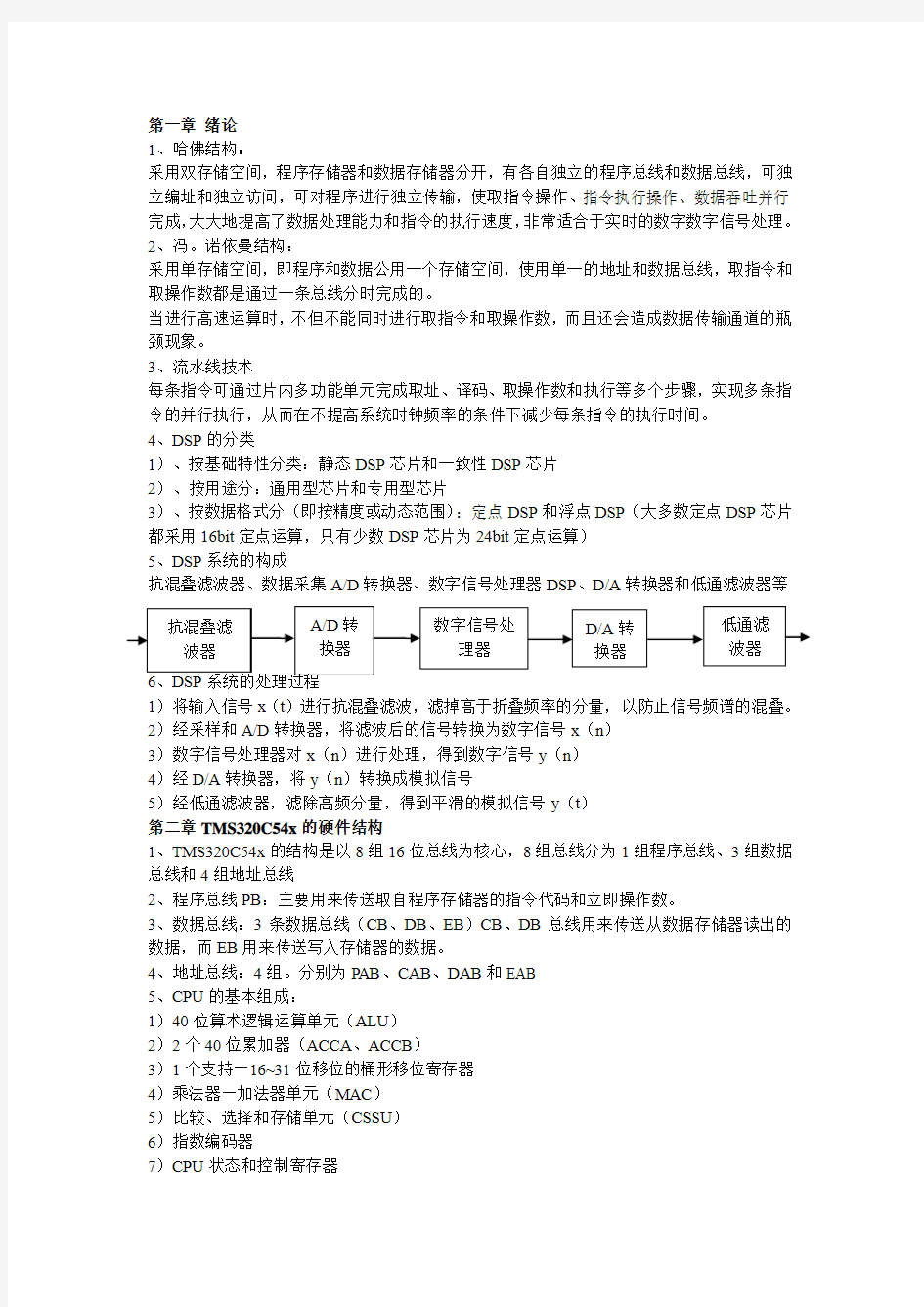

5、DSP 系统的构成

抗混叠滤波器、数据采集A/D 转换器、数字信号处理器DSP 、D/A 转换器和低通滤波器等

6、DSP 系统的处理过程

1)将输入信号x (t )进行抗混叠滤波,滤掉高于折叠频率的分量,以防止信号频谱的混叠。

2)经采样和A/D 转换器,将滤波后的信号转换为数字信号x (n )

3)数字信号处理器对x (n )进行处理,得到数字信号y (n )

4)经D/A 转换器,将y (n )转换成模拟信号

5)经低通滤波器,滤除高频分量,得到平滑的模拟信号y (t )

第二章 TMS320C54x 的硬件结构

1、TMS320C54x 的结构是以8组16位总线为核心,8组总线分为1组程序总线、3组数据总线和4组地址总线

2、程序总线PB :主要用来传送取自程序存储器的指令代码和立即操作数。

3、数据总线:3条数据总线(CB 、DB 、EB )CB 、DB 总线用来传送从数据存储器读出的数据,而EB 用来传送写入存储器的数据。

4、地址总线:4组。分别为PAB 、CAB 、DAB 和EAB

5、CPU 的基本组成:

1)40位算术逻辑运算单元(ALU )

2)2个40位累加器(ACCA 、ACCB )

3)1个支持—16~31位移位的桶形移位寄存器

4)乘法器—加法器单元(MAC )

5)比较、选择和存储单元(CSSU )

6)指数编码器

7)CPU 状态和控制寄存器

抗混叠滤

波器 A/D 转换器 数字信号处理器 D/A 转换器 低通滤波器

5、当16位数据存储器操作数通过数据总线DB 或CB 输入时,ALU 将采用以下两种方式对操作数进行预处理

1)若数据存储器操作数在低16位时,则

当SXM=0时,高24位(39~16位)用0填充

当SXM=1时,高24位(39~16位)扩展为符号

2)若数据存储器操作数在高16位时。则

当SXM=0时,39~32位和15~0位用0填充

当SXM=1时,39~32位扩展为符号,15~0位用0填充

SXM 位符号位扩展方式控制位,位于状态寄存器ST1的8位

6、溢出处理

当运算结果发生溢出时

1)若OVM=0,则对ALU 的运算结果不进行任何调整,直接送入累加器

2)若OVM=1,则需对ALU 的运行结果进行调整

当正向溢出时,将32位最大正数007FFFFFFFH 装入累加器

当负向溢出时,将32位最小负数FF80000000H 装入累加器

3)状态寄存器ST0中与目标累加器相关的溢出标志OV A/OVB 被置1

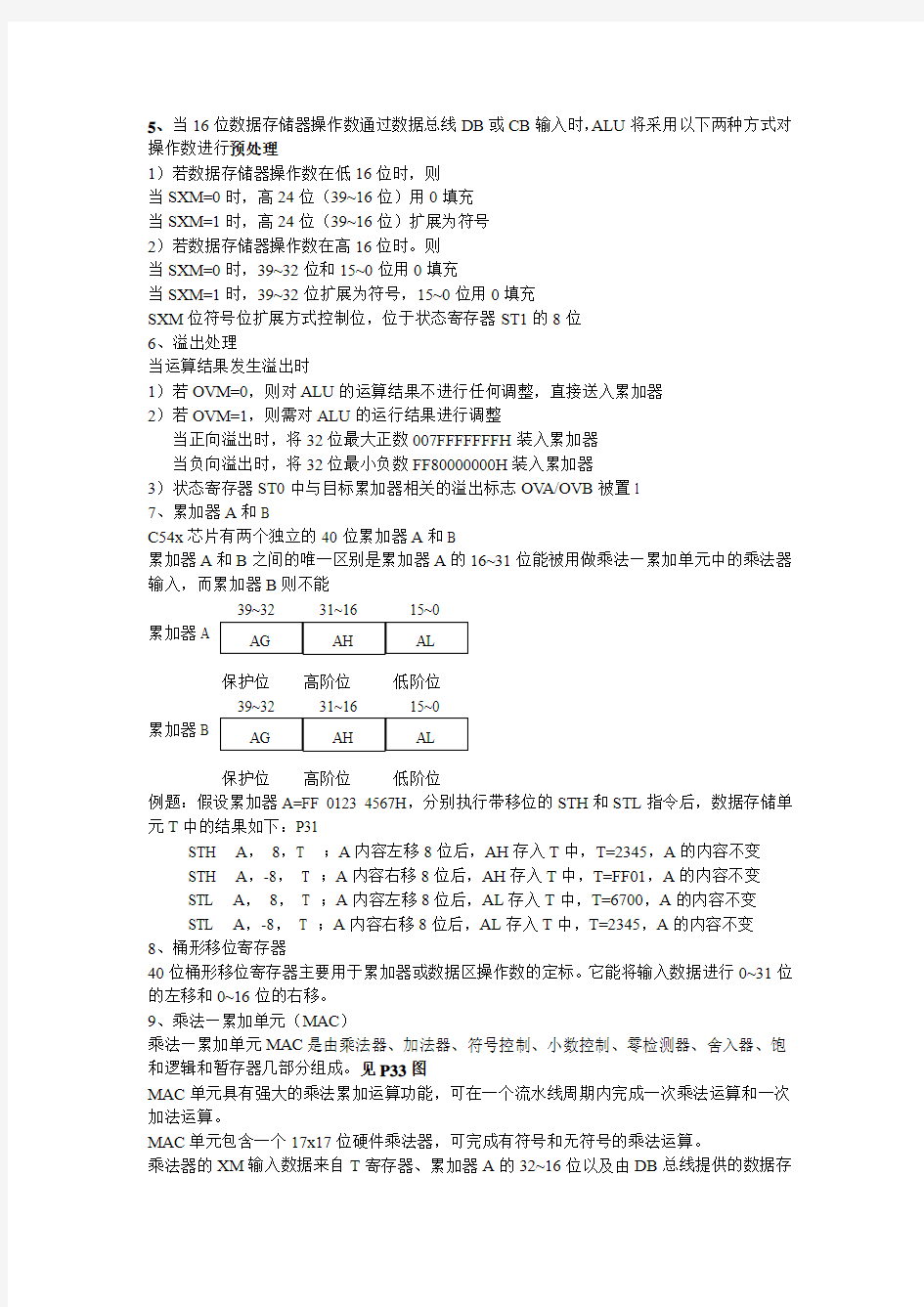

7、累加器A 和B

C54x 芯片有两个独立的40位累加器A 和B

累加器A 和B 之间的唯一区别是累加器A 的16~31位能被用做乘法—累加单元中的乘法器输入,而累加器B 则不能

39~32 31~16 15~0

累加器A

保护位 高阶位 低阶位

39~32 31~16 15~0

累加器B

保护位 高阶位 低阶位

例题:假设累加器A=FF 0123 4567H ,分别执行带移位的STH 和STL 指令后,数据存储单元T 中的结果如下:P31

STH A , 8,T ;A 内容左移8位后,AH 存入T 中,T=2345,A 的内容不变 STH A ,-8, T ;A 内容右移8位后,AH 存入T 中,T=FF01,A 的内容不变 STL A , 8, T ;A 内容左移8位后,AL 存入T 中,T=6700,A 的内容不变 STL A ,-8, T ;A 内容右移8位后,AL 存入T 中,T=2345,A 的内容不变

8、桶形移位寄存器

40位桶形移位寄存器主要用于累加器或数据区操作数的定标。它能将输入数据进行0~31位的左移和0~16位的右移。

9、乘法—累加单元(MAC )

乘法—累加单元MAC 是由乘法器、加法器、符号控制、小数控制、零检测器、舍入器、饱和逻辑和暂存器几部分组成。见P33图

MAC 单元具有强大的乘法累加运算功能,可在一个流水线周期内完成一次乘法运算和一次加法运算。

MAC 单元包含一个17x17位硬件乘法器,可完成有符号和无符号的乘法运算。

乘法器的XM 输入数据来自T 寄存器、累加器A 的32~16位以及由DB 总线提供的数据存AG AH AL AG AH AL

储器操作数;而YM输入的数据可以取自累加器A的32~16位、由DB总线和CB总线提供的数据存储器操作数以及由PB总线传送过来的程序存储器操作数。

10、MAC单元的乘法器能进行有符号数、无符号数以及有符号数与无符号数的乘法运算,根据操作数的不同情况需进行一下处理

1)若是两个有符号数相乘,则在进行乘法运算之前,先对两个16位乘数进行符号位扩展,形成17位有符号数后再进行相乘。扩展方法是:在每个乘数的最高位前增加一个符号位,其值由乘数的最高位决定。

2)若是两个无符号数相乘,则在两个16位乘数的最高位前添加“0”,扩展为17位乘数后再进行乘运算。

3)若是有符号数与无符号数相乘,则有符号数在最高位前添加1个符号位,其值由最高位决定,而无符号数在最高位前添加“0”,然后两个操作数相乘。

乘累加?P33

11、C54x提供三个16位寄存器来作为CPU状态和控制器,它们分别为:

状态寄存器0(ST0)、状态寄存器1(ST1)和处理器工作方式状态寄存器(PMST)

12、TMS320C54x共有192千字的寻址存储空间。这192千字的存数空间分成3个独立的可选择空间:

64千字的程序存储空间;

64千字的数据存储空间;

64千字的I/O空间。

13、所有的C54x芯片都包括内部随机存储器(RAM)和只读存储器(ROM)。内部RAM 又分为单寻址RAM(SARAM)和双寻址RAM(DARAM)两种类型。

14、与外部存储器相比内部存储器具有以下几个优点:

不需要插入等待状态;

与外部存储器相比,成本低;

比外部存储器功耗小

15、C54x的存储结构与处理器工作方式状态寄存器(PMST)的设置有关,用户可以通过PMST中的3个控制位(MP/MC、OVL Y和DROM)来配置存储器空间。

16、程序存储空间的配置

MP/和OVL Y控制位来设置内部只读存储器的映程序存储空间可通过PMST寄存器的MC

射地址。

MP/控制位用来决定程序存储空间是否使用内部存储器

1)MC

MP/=0时,4000H~EFFFH程序存储空间定义为外部存储器,而F000H~FEFFH程当MC

序存储空间定义内部ROM。FF00H~FFFFH程序存储空间定义为内部存储器。其工作方式为微型计算机模式。

2)OVL Y控制位用来决定程序存储空间是否使用RAM。

当OVL Y=0时,000H~3FFFH全部定义为外部程序存储空间,程序存储空间不使用RAM,此时内部RAM只作为数据存储器使用;

当OVL Y=1时,0000H~007FH保留,程序无法占用。0080H~3FFFH定义为内部DARAM。即内部RAM同时被映射到程序存储空间和数据空间。

17、数据存储空间的配置

C54x的数据存储空间共有64千字,采用片内和片外存储器统一编址。除了含有SARAM和

DARAM外,还可以通过软件将内部ROM映射到数据存储空间。用户可以通过设置PMST 中的DROM位,将部分内部ROM映射到存储空间。

若DROM=0,内部ROM不映射到数据空间;

若DROM=1,内部ROM映射到数据存储空间,并且当MP/MC=0时,内部ROM同时映射到数据空间和程序空间。每次复位时,处理器将对DROM位清零。

18、C54x的片内外设主要包括:

通用I/O引脚;

定时器;

时钟发生器

主机接口HPI;

串行通信接口;

软件可编程等待状态发生器;

可编程分区转换逻辑。

19、每一种C54x芯片都为用户提供了两个通用的I/O引脚:BIO和XF

BIO为分支转移控制输入引脚,用来监控外部设备的运行状态。

XF位外部标志输出引脚,主要用于程序向外设传输标识信息。

20、串行通信接口

同步串行口SP

缓冲同步串行口BSP

时分多路同步串行口TDM

多通道缓冲串行口McBSP

21、软件可编程等待状态发生器

软件可编程等待状态发生器能把外部总线周期扩展到最多14个机器周期,这样可以方便地与慢速的外部存储器和I/O设备接口。

第三章TMS320C54x的指令系统(重点)

1、TMS320C54x有7种基本的寻址方式:立即寻址、绝对寻址、累加器寻址、直接寻址、间接寻址、存储器映像寻址和堆栈寻址。

2、直接寻址时利用数据指针和堆栈指针寻址,其特点是数据存储器地址由基地址(数据页指针DP或堆栈指针SP)和偏移地址共同构成,共16位。

1)当CPL=0,以数据页指针寄存器DP中的9位为高位,以指令中的7位为低位,构成16数据存储单元的地址。

2)当CPL=1时,将堆栈指针SP=的16位与指令中的7位地址相加,形成16位的数据存储器地址。

3、两种特殊的间接寻址方式:循环寻址方式和位倒序寻址方式

4、循环寻址?

5、位倒序可以提高FFT等算法的效率。例如16点FFT的位倒序寻址如表P79

?

6、C54x的堆栈是从高地址向低地址方向填入的。处理器使用一个16位堆栈指针(sp)来对堆栈进行管理,SP始终向存放在堆栈中的最后一个元素。

执行压入堆栈操作时,时先减小SP后再将数据压入堆栈的;而执行堆栈弹出操作时,则是先从堆栈弹出数据,然后再增加SP的值。

7、TMS320C54x的指令系统共有129条基本指令,由于操作数的寻址方式不同,由他们可以派生205条指令。按指令的功能分类,可以分成数据传送指令、算术运算指令、逻辑运算指令、程序控制指令、并行操作指令和重复操作指令。

第四章汇编语言程序的开发工具

1、汇编器和链接器生成的目标文件,是一个可以由C54x器件执行的文件。这些目标文件的格式称为公共目标文件格式(COFF)

2、段是COFF文件中最重要的概念。所有的COFF目标文件都包含以下三种形式的段:。Text段(文本段),通常包含可执行代码

。Data段(数据段),通常包含初始化数据

。Bss段(保留空间段),通常为未初始化变量保留存储空间

3、COFF目标文件有以下两种基本类型的段

1)、初始化段:包含有数据或程序代码

。Text段是已初始化段

。Data段是已初始化段

。Sect汇编器伪指令建立的自定义段也是已初始化段

2)、未初始化段:在存储空间中,它为未初始化数据保留存储空间

。Bss段是未初始化段

。Usect汇编命令建立的自定义段也是未初始化段

4、汇编器对段的处理是通过段的伪指令来区别各个段,并将段名相同的语句汇编在一起。汇编器有5条命令可识别汇编语言的程序各部分。

。Bss(未初始化段)

。Usect(未初始化段)

。Text(已初始化段)

。Data(已初始化段)

。Sect(已初始化段)

5、段命令举例P105

6、Memory伪指令。用来定义目标系统的存储器配置空间,包括对存储器各部分命名,以及规定它们的起始地址和长度。

Sections伪指令。此命令告诉链接器如何将输入段组合成输出段,以及将输出段放在存储器中什么位置。

7、链接器命令文件举例P127

8、使用MEMORY伪指令的链接器命令文件的例子P128

9、多个文件的连接实例P132

第五章TMS320C54x的汇编语言程序设计

1、如果程序要使用堆栈,必须先进行设置,方法如下:p148

size .set 120

stack .usect "STACK",size

STM #stack+size,SP

2、程序控制中的分支操作包括:分支转移、子程序调用、子程序返回和条件操作。(能够判断即可)

3、P152---P161例题

第七章TMS320C54x片内外设、接口及应用

1、定时器结构

图p230

定时器主要由定时寄存器TIM 、定时周期寄存器PRD 、定时控制寄存器TCR (包括预标定分频系数TDDR 、预标定计数器PSC 、控制位TRB 和TSS 等)及相应的逻辑控制电路组成。其中寄存器TIM 、PRD 和TCR 都是存储映像寄存器,它们在数据寄存器中的地址分别为0024H 、0025H 和0026H 。TIM 是一个减一计数器。PRD 用来存放定时时间常数。TCR 中包含定时器的控制位和状态位。

2、定时周期=CLKOUT ?(TDDR+1)?(PRD+1)

3、中断寄存器的作用

TMS320C54x 中断系统设置两个中断寄存器,分别为中断标志寄存器IFR 和中断屏蔽寄存器IMR 。

中断标志寄存器:当一个中断出现时,IFR 中的相应的中断标志位置1,知道CPU 识别该中断为止。

中断屏蔽寄存器:如果状态寄存器ST1中的INTM=0,IMR 寄存器中的某位置1,就能开放相应的中断。

4、对于硬件可屏蔽中断,只有满足以下三个条件CPU 才能响应中断:

1)当前中断优先级最高

2)INTM 位清零

3)IMR 屏蔽位为1

第八章 TMS320C54x 的硬件设计

1、介绍DSP 硬件系统的基本设计,包括电源电路、复位电路、时钟电路等。

2、TMS320VC5402芯片采用双电源供电方式,以获得

更好的的电源性能,其工作电压分别为3.3V 和1.8V ,其中3.3V 位I/O 电源DD DV ,主要供I/O 接口使用,通常情况下可直接与外部低压器件记性接口,而不需要额外的电平变换电路。

1.8V 位内核电源DD CV ,主要为芯片的内部逻辑提供电压,包括CPU 、时钟电路和所有的外设逻辑。与3.3V 相比,1.8V 可以大大降低芯片功耗。

3、TMS320VC5402芯片加电次序

理想情况下,DSP 芯片上的两个电源同时加电,但在有些场合很那做到。若不能做到同时加电,应先对DD DV 加电,然后再对DD CV 加电,同时要求DD DV 电压不超过DD CV 电压2V 。

4、复位电路的设计

1)上电复位电路

2)手动复位电路

3)自动复位电路

5、自动复位电路工作原理:

通过电路提供的的监视线来监视系统运行,当系统正常运行时,在规定的时间内给监视线提供一个变化的高低电平信号,若在规定的时间内这个信号不发生变化,自动复位电路就认为系统运行不正常,并对系统进行复位。

6、自动复位电路工作过程图p285

当DSP 处于不正常工作时,由程序所产生的周期脉冲CLK 将会消失,自动复位电路将无法接收到监视信号,MAX706R 芯片将通过引脚7产生复位信号,使系统复位,程序重新开始运行,强迫系统恢复正常工作。

7、3.3V 与5.5V 电平转换的形式

在一个系统同时存在3.3V 和5V 系列芯片时,必须考虑它们之间的电压兼容性问题。需注

意:

1)、3.3V的芯片是否能承受5V电压;

2)、驱动器件的输出逻辑电平与负载器件要求的输入逻辑电平是否匹配

3)、驱动电路允许的最大电流是否大于负载器件所要求的输入电流。

P290图

8、根据不同的应用场合,3.3V与5.5V电平转换有四种形式:

1)、5V TTL器件驱动3.3V TTL器件(LVC)

2)、3.3V TTL器件(LVC)驱动5V TTL器件

3)、5V CMOS器件驱动3.3V TTL器件(LVC)

4)、3.3V TTL器件(LVC)驱动5V CMOS器件

9、P291图DSP与5V EPROM的接口

10、DSP系统的组成图P317

1)、TMS320VC5402芯片:作为整个系统的核心,主要用来完成语音压缩和解压缩在内的所有软件功能。

2)、模数转换电路:A/D和D/A转换器完成语音信号的模数和数模转换。

3)、FLASH存储器:用于存放系统程序和已初始化的数据。

4)、双口RAM:用来与外部交换语音压缩数据。

11、DSP系统的工作过程:

1)、系统加电DSP芯片后,由其内部存储器固化的自引导程序(Boot)将存于FLASH中的程序且数据移入内部RAM。

2)、程序和数据移至内部RAM后,DSP芯片开始运行程序,执行语音编码算法。每隔10ms 运行一次编码算法,并与双口RAM交换一次数据;

3)、DSP芯片将语音压缩后得到的数据写入双口RAM,由外部系统读出送至信道;4)、外部系统将对方的编码数据送至双口RAM,由DSP芯片从双口RAM中读出,进行数据处理,还原为合成语音。

由于TMS320VC5402芯片的运算速度在10ms内足以完成语音的压缩和解压缩算法,因此,系统可以采用全双工方式工作。

d s p课程设计正弦信发 生器的设计 标准化管理处编码[BBX968T-XBB8968-NNJ668-MM9N]

太原理工大学 DSP课程设计: 正弦信号发生器的设计 学号: 班级: 姓名: 指导教师: 一、设计目的 1、通过实验掌握DSP的软件开发过程 2、学会运用汇编语言进行程序设计 3、学会用CCS仿真模拟DSP芯片,通过CCS软件平台上应用C54X汇编语言来实现正弦信号发生装置。 二、设计原理 三、本实验产生正弦波的方法是泰勒级数展开法。泰勒级数展开法需要的单元少,具有稳定性好,算法简单,易于编程等优点,而且展开的级数越多,失真度就越小。求一个角度的正弦值取泰勒级数的前5项,得近似计算式: 四、总体方案设计

本实验是基于CCS开发环境的。CCS是TI公司推出的为开发TMS320系列DSP软件的集成开发环境,是目前使用最为广泛的DSP开发软件之一。它提供了环境配置、源文件编译、编译连接、程序调试、跟踪分析等环节,并把软、硬件开发工具集成在一起,使程序的编写、汇编、程序的软硬件仿真和调试等开发工作在统一的环境中进行,从而加速软件开发进程。通过CCS软件平台上应用C54X汇编语言来实现正弦信号发生装置。 总体思想是:正弦波的波形可以看作由无数点组成,这些点与x轴的每一个角度值相对应,可以利用DSP处理器处理大量重复计算的优势来计算x轴每一点对应的y的值(在x轴取N个点进行逼近)。整个系统软件由主程序和基于泰勒展开法的SIN子程序组成,相应的软件流程图如图。 五、设计内容 1、设置 在Family下选择C55xx,将看到所有C55xx的仿真驱动,包括软件仿真和硬件仿真; 在Platform下选择Simulator,在Available Factory Boards中只显示软件仿真驱动,选中相应的驱动; 双击C55xx Rev4.0 CPU Functional Simulator,可以在My System下看到所加入的驱动; 点击Save & Quit,将保存设置退出Setup CCStudio v3.1并启动运行CCStudio。 2、编写汇编源程序sin。 3.、建立汇编源程序

《数字信号处理》辅导 一、离散时间信号和系统的时域分析 (一) 离散时间信号 (1)基本概念 信号:信号传递信息的函数也是独立变量的函数,这个变量可以是时间、空间位置等。 连续信号:在某个时间区间,除有限间断点外所有瞬时均有确定值。 模拟信号:是连续信号的特例。时间和幅度均连续。 离散信号:时间上不连续,幅度连续。常见离散信号——序列。 数字信号:幅度量化,时间和幅度均不连续。 (2)基本序列(课本第7——10页) 1)单位脉冲序列 1,0()0,0n n n δ=?=?≠? 2)单位阶跃序列 1,0 ()0,0n u n n ≥?=?≤? 3)矩形序列 1,01 ()0,0,N n N R n n n N ≤≤-?=?<≥? 4)实指数序列 ()n a u n 5)正弦序列 0()sin()x n A n ωθ=+ 6)复指数序列 ()j n n x n e e ωσ= (3)周期序列 1)定义:对于序列()x n ,若存在正整数N 使()(),x n x n N n =+-∞<<∞ 则称()x n 为周期序列,记为()x n ,N 为其周期。 注意正弦周期序列周期性的判定(课本第10页) 2)周期序列的表示方法: a.主值区间表示法 b.模N 表示法 3)周期延拓 设()x n 为N 点非周期序列,以周期序列L 对作()x n 无限次移位相加,即可得到周期序列()x n ,即 ()()i x n x n iL ∞ =-∞ = -∑ 当L N ≥时,()()()N x n x n R n = 当L N <时,()()()N x n x n R n ≠ (4)序列的分解 序列共轭对称分解定理:对于任意给定的整数M ,任何序列()x n 都可以分解成关于/2c M =共轭对称的序列()e x n 和共轭反对称的序列()o x n 之和,即

华北水利水电大学North China University of Water Resources and Electric Power DSP课程设计 题目: FIR数字低通滤波器 学院信息工程学院 专业电子信息工程 姓名 学号 指导教师

摘要 (1) 一. 绪论 (1) 1.1设计背景 (1) 1.2设计方法分析 (1) 二.FIR滤波器设计过程 (2) 2.1 FIR滤波器原理 (2) 2.2 FIR滤波器的实现方法 (3) 2.3 FIR滤波器的MATLAB实现 (4) 2.4 设计流程图 (6) 三.MATLAB和 CCS操作步骤及仿真结果 (7) 3.1 matlab中的.M文件的编写 (7) 3.2 工程文件的建立 (12) 3.3 仿真结果及分析 (12) 四.心得与总结 (12)

摘要 当前,数字信号处理技术受到了人们的广泛关注,其理论及算法随着计算机技术和微电子技术的发展得到了飞速地发展,并被广泛应用于语音和图象处理、数字通信、谱分析、模式识别和自动控制等领域。数字滤波器是数字信号处理中最重要的组成部分之一,几乎出现在所有的数字信号处理系统中。设计中通过MATLAB环境中图形化的方式建立数字信号处理的模型进行DSP的设计和仿真验证,将设计的图形文件.mdl直接转换成C语言程序在CCS中运行。利用MATLAB 软件开发产品加速了开发周期,比直接在CCs中编程方便快捷了很多,对于任何复杂功能的DSP系统,只需要进行少量的添加和修改就能完成功能正确的C语言程序设计。 一. 绪论 1.1设计背景 一个实际的应用系统中,由于设备或者是外界环境的原因,总存在各种干扰,使信号中混入噪声,譬如音频信号中高频成分的噪声使得音乐听起来刺耳,失去了原有悦耳的音质。为了提高信号质量,可以对信号进行滤波,从噪声中提取信号,即对一个具有噪声和信号的混合源进行采样,然后经过一个数字滤波器,滤除噪声,提取有用信号。DSP(数字信号处理器)与一般的微处理器相比有很大的区别,它所特有的系统结构、指令集合、数据流程方式为解决复杂的数字信号处理问题提供了便利,本文选用TMS320C54X作为DSP处理芯片,通过对其编程来实现FIR滤波器。对数字滤波器而言,从实现方法上,有FIR滤波器和无限冲激响应(IIR)滤波器之分。由于FIR滤波器只有零点,因此这一类系统不像IIR系统那样易取得比较好的通带与阻带衰减特性。但是FIR系统有自己突出的优点:①系统总是稳定的;②易实现线性相位;③允许设计多通带(阻带)滤波器。其中后两项是IIR系统不易实现的。 1.2设计方法分析 FIR滤波器的设计方法分析 数字滤波器依据冲激响应的宽度划分为有限冲激响应(FIR)滤波器和无限冲激响应滤波(IIR)。FIR 滤波器是有限长单位冲激响应滤波器,在结构上是非递归型的,有限冲激响应滤波器(FIR),具有以下的优点:(1)可以在幅度特性随意设计的同时,保证精确、严格的线性相位;(2)由于FIR滤波器的单位脉冲响应h(n)是有限长序列,因此F I R 滤波器没有不稳定的问题;(3)由于FIR 滤

对模拟信号(一维信号,是时间的函数)进行采样后,就是 离散 信号,再进行幅度量化后就是 数字信号。2、若线性时不变系统是有因果性,则该系统的单位取样响应序列h(n)应满足的充分必要条件是 当n<0时,h(n)=0 。3、序列)(n x 的N 点DFT 是)(n x 的Z 变换在 单位圆 的N 点等间隔采样。4、)()(5241 n R x n R x ==,只有 当循环卷积长度L ≥8 时,二者的循环卷积等于线性卷积。5、已知系统的单位抽样响应为h(n),则系统稳定的充要条件是 ()n h n ∞ =-∞ <∞ ∑ 6、用来计算N =16点DFT ,直接计算需要(N 2 )16*16=256_次复乘法,采用基2FFT 算法, 需要__(N/2 )×log 2N =8×4=32 次复乘法。7、无限长单位冲激响应(IIR )滤波器的基本结构有直接Ⅰ型,直接Ⅱ型,_级联型_和 并联型_四种。8、IIR 系统的系统函数为)(z H ,分别用直接型,级联型,并联型结构实现,其中 并 联型的运算速度最高。9、数字信号处理的三种基本运算是:延时、乘法、加法 10、两个有限长序列 和 长度分别是 和 ,在做线性卷积后结果长度是__N 1+N 2-1_。11、N=2M 点基2FFT ,共有 M 列蝶形, 每列有N/2 个蝶形。12、线性相位FIR 滤波器的零点分布特点是 互为倒数的共轭对 13、数字信号处理的三种基本运算是: 延时、乘法、加法 14、在利用窗函数法设计FIR 滤波器时,窗函数的窗谱性能指标中最重要的是___过渡带宽___与__阻带最小衰减__。16、_脉冲响应不变法_设计IIR 滤波器不会产生畸变。17、用窗口法设计FIR 滤波器时影响滤波器幅频特性质量的主要原因是主瓣使数字滤波器存在过渡带,旁瓣使数字滤波器存在波动,减少阻带衰减。18、单位脉冲响应分别为 和 的两线性系统相串联,其等效系统函数时域及频域表达式分别是h(n)=h 1(n)*h 2(n), =H 1(e j ω )× H 2(e j ω )。19、稳定系统的系统函数H(z)的收敛域包括 单位圆 。20、对于M 点的有限长序列x(n),频域采样不失真的条件是 频域采样点数N 要大于时域采样点数M 。 1、下列系统(其中y(n)为输出序列,x(n)为输入序列)中哪个属于线性系统?( y(n)=x(n 2 ) ) A.窗函数的截取长度增加,则主瓣宽度减小,旁瓣宽度减小 B.窗函数的旁瓣相对幅度取决于窗函数的形状,与窗函数的截取长度无关 C.为减小旁瓣相对幅度而改变窗函数的形状,通常主瓣的宽度会增加 D.窗函数法能用于设计FIR 高通滤波4、因果FIR 滤波器的系统函数H(z)的全部极点都在(z = 0 )处。6、已知某序列z 变换的收敛域为|z|<1,则该序列为(左边序列)。7、序列)1() (---=n u a n x n ,则)(Z X 的收敛域为(a Z <。8、在对连续信号均匀 采样时,要从离散采样值不失真恢复原信号,则采样周期T s 与信号最高截止频率f h 应满足关系(T s <1/(2f h ) ) 9、 )()(101n R n x =,)()(72n R n x =,用DFT 计算二者的线性卷积,为使计算量尽可能的少,应使DFT 的长度N 满足 (16=N )。10、线性相位FIR 滤波器有几种类型( 4) 。11、在IIR 数字滤波器的设计中,用哪种方法只适 合于片断常数特性滤波器的设计。(双线性变换法)12、下列对IIR 滤波器特点的论述中错误的是( C )。 A .系统的单位冲激响应h(n)是无限长的B.结构必是递归型的C.肯定是稳定的D.系统函数H(z)在有限z 平面(0<|z|<∞)上有极点 13、有限长序列h(n)(0≤n ≤N-1)关于τ= 2 1 -N 偶对称的条件是(h(n)=h(N-n-1))。14、下列关于窗函数设计法的说法中错误的是( D )。A.窗函数的截取长度增加,则主瓣宽度减小,旁瓣宽度减小 B.窗函数的旁瓣相对幅度取决于窗函数的形状,与窗函数的截取长度无关 C.为减小旁瓣相对幅度而改变窗函数的形状,通常主瓣的宽度会增加 D.窗函数法不能用于设计FIR 高通滤波器 15、对于傅立叶级数而言,其信号的特点是(时域连续非周期,频域连续非周期)。

Knowledge 问题 谁在DSP的汇编语言中加入了NOP指令? NOP指令加入的条件是什么? About DSP 1.DSP是实时数字信号处理的核心和标志。 2.DSP分为专用和通用两种类型。专用DSP一般采用定点数据结构(一般不支持小数), 数据结构简单,处理速度快;通用DSP灵活性好,但是处理速度有所降低。 3.DSP采用取指、译码、执行三个阶段的流水线(Pipeline)技术,缩短了执行时间,提高了 运行速率。DSP具有8个Functional unit,如果并行处理的话,以600MHz的时钟计算,如果执行的指令是single cycle指令,则可以4800MIPS(指令每秒)。 4.DSP的8个functional Unit,具有独特的功能,对滤波、矩阵运算、FFT(傅里叶变换) 具有 哈弗结构 把指令空间与数据空间隔离的存储方式。 这样实现是为了实现指令的连续读取,而实现pipeline流水线结构。 传统哈弗结构:两个独立的存储空间,还使用独立总线。让取指与执行存储独立,加快执行速度。 改进型哈弗结构:指令与数据的存储空间还是独立的。但是使用公共的总线(地址总线与数据总线)。这样实现的原因是因为出现了CACHE,数据的存储动作大部分被内部的CACHE 总线承接了,所以总线冲突的情况会大大减少。同时让总线的结构与控制变得简单,CACHE 存储的速度也明显快于外设存储器。 冯诺依曼结构:是指令空间与数据空间共享的存放方式。它不能实现pipeline的执行过程。 Pipeline(流水线)技术 是把指令的取指-译码和指令的执行独立开来的技术。虽然每条指令的过程还是要经过取指-译码-执行三个阶段最少3个CPU Cycle。但是多个指令同时并行先后进行,保证总体的指

DSP课程设计-FIR高通滤波器设计 FIR 高通滤波器设计 南京师范大学物科院 从实现方法方面考虑,将滤波器分为两种,一种是IIR 滤波器,另一种是FIR 滤波器。 FIRDF 的最大优点是可以实现线性相位滤波。而IIRDF 主要对幅频特性进行逼近,相频特性会存在不同程度的非线性。我们知道,无失真传输与滤波处理的条件是,在信号的 有效频谱范围内系统幅频响应应为常数,相频响应为频率的线性函数。另外,FIR 是全零 点滤波器,硬件和软件实现结构简单,不用考虑稳定性问题。所以,FIRDF 是一种很重要 的滤波器,在数字信号处理领域得到广泛应用。 FIRDF 设计方法主要分为两类:第一类是基于逼近理想滤波器特性的方法,包括窗函 数法、频率采样法和等波纹最佳逼近法;第二类是最优设计法。其中窗函数计法的基本思 想是用FIRDF 逼近希望的滤波特性。本次设计主要采用窗函数设计法,对理想滤波器进行逼近,从而实现高通滤波器的设计。 在MATLAB 软件中,有一系列函数用于设计滤波器,应用时十分方便。因此,在本次 设计中,滤波器的设计主要采用MATLAB 软件,编写适当的程序,得到滤波器的单位脉冲 响应。 本设计对滤波器的硬件仿真主要使用CCS 软件,通过对滤波器的硬件仿真,可以较为真实的看出滤波器的滤波效果。 关键字:高通、FIRDF 、线性相位、Hanning 窗、MATLAB 、CCS 1. 设计目标 产生一个多频信号,设计一个高通滤波器消除其中的低频成分,通过CCS 的graph view波形和频谱显示,并和MATLAB 计算结果比较 2. 设计原理 2.1 数字滤波器 数字滤波器(digital filter)是由数字乘法器、加法器和延时单元组成的一种装置。 其功能是对输入离散信号的数字代码进行运算处理,以达到改变信号频谱的目的。由于电 子计算机技术和大规模集成电路的发展,数字滤波器已可用计算机软件实现,也可用大规 模集成数字硬件实时实现。数字滤波器广泛用于数字信号处理中,如电视、VCD 、音响等。

绪论:本章介绍数字信号处理课程的基本概念 0.1信号、系统与信号处理 1?信号及其分类 信号是信息的载体,以某种函数的形式传递信息。这个函数可以是时间域、频率域或其它域,但最基础的域是时域。 分类: 周期信号/非周期信号 确定信号/随机信号能量信号/功率信号 连续时间信号/离散时间信号/数字信号按自变量与函数值的取值形式不同分类: 2?系统 系统定义为处理(或变换)信号的物理设备,或者说,凡是能将信号加以变换以达到人们要求的各种设备都称为系统。 3. 信号处理 信号处理即是用系统对信号进行某种加工。包括:滤波、分析、变换、综合、压缩、估计、识别等等。所谓“数字信号处理”,就是用数值计算的方法,完成对信号的处理。 0.2数字信号处理系统的基本组成 数字信号处理就是用数值计算的方法对信号进行变换和处理。不仅应用于数字化信号的处理, 而且也可应用于模拟信号的处理。以下讨论模拟信号数字化处理系统框图。 精选

PrF ADC DSP DAC PoF (1)前置滤波器 将输入信号X a(t )中高于某一频率(称折叠频率,等于抽样频率的一半)的分量加以滤除。 (2)A/D变换器 在A/D变换器中每隔T秒(抽样周期)取出一次X a(t)的幅度,抽样后的信号称为离散信号。在A/D 变换器中的保持电路中进一步变换为若干位码。 (3)数字信号处理器(DSP) (4)D/A变换器 按照预定要求,在处理器中将信号序列x(n)进行加工处理得到输出信号y(n)。由一个二进制码流产生一个阶梯波形,是形成模拟信号的第一步。 (5)模拟滤波器 把阶梯波形平滑成预期的模拟信号;以滤除掉不需要的高频分量,生成所需的模拟信号y a(t)。 0.3数字信号处理的特点 (1)灵活性。(2)高精度和高稳定性。(3)便于大规模集成。(4)对数字信号可以存储、运算、系统可以获得高性能指标。 0.4数字信号处理基本学科分支 数字信号处理(DSP)一般有两层含义,一层是广义的理解,为数字信号处理技术 ----- D igitalSignalProcessing 另一层是狭义的理解,为数字信号处理器----- DigitalSignalProcesso。 0.5课程内容 该课程在本科阶段主要介绍以傅里叶变换为基础的“经典”处理方法,包括:(1)离散傅里叶变换及其快速算法。(2)滤波理论(线性时不变离散时间系统,用于分离相加性组合的信号,要求信号 频谱占据不同的频段)。 在研究生阶段相应课程为“现代信号处理”(AdvancedSignalProcessin)信号对象主要是随机信 号,主要内容是自适应滤波(用于分离相加性组合的信号,但频谱占据同一频段)和现代谱估计。 简答题: 1 ?按自变量与函数值的取值形式是否连续信号可以分成哪四种类型?

数字信号处理报告 数学与信息科学学院 信息与计算科学 学号:41312261 姓名:高萌瑶

数字信号处理 信号处理的问题在各个领域都非常普遍,信号的表现形式也多种多样。若将信号看作自变量时间影响的因变量,则也可细分为如下几种:信号的自变量和函数值均取连续值,称之为模拟信号或时域离散信号;若自变量取离散值,而函数值取连续值,则称此信号为时域离散信号;若自变量和函数值均取离散值,则称为数字信号。 1.模拟信号数字处理方法 在现实生活中及工程技术领域中涉及的信号一般都是模拟信号,即在时域与频域均连续的信号。对模拟信号的处理是通过一些模拟器件,如:晶体管、电阻、电容等,完成对信号的处理。模拟信号处理时改变参数时不具备一些灵活性,而且在计算精度方面也不能得到较高的精度,故处理模拟信号时我们更倾向于将其经过采样和量化编码形成数字信号,再采用数字信号处理技术进行处理。最后,如果需要,则可以将数字信号再转换为模拟信号,进行恢复。 图1 模拟信号数字处理框图 1.1采样间隔与采样信号表示 对模拟信号进行采样可以看作一个模拟信号通过一个电子开关S 。假设电子开关每隔周期T 合上一次,每次合上的时间为T τ<<,在电子开关输出端得到其 采样信号^()a x t 。该电子开关的作用等效成一宽度为τ,周期为T 的矩形脉冲串()P t τ相乘的结果。 如果电子开关合上的时间0τ→,则形成理想采样,此时上面的脉冲串变成单位冲激串,用()P t δ表示。()P t δ中每个单位冲激处在采样点上,强度为1。理想采样则是()a x t 与()P t δ相乘的结果。 用公式表示为: ^()() ()()()()()n a a a n P t t nT x t x t P t x t t nT δδδδ∞=-∞∞ =-∞= -=?=-∑∑ 其中上式中()t δ是单位冲激信号,在上式中只有当t nT =时,才可能有非零值,因此将采样信号表示为下式: ^ ()()()a a n x t x nT t nT δ∞ =-∞=-∑ 1.2采样速率与模拟信号最高频率的关系 为了使采样信号不失真的恢复原模拟信号,需寻找速率s f 与模拟信号最高频率c f 之间的关系。在傅里叶变换中,两个信号在时域相乘的傅里叶变换等于两个信号分别的傅里叶变换的卷积,因此: ()FT[(t)] ()FT[(t)]()FT[P (t)]a a a a X j x X j x P j δδ∧∧ Ω=Ω=Ω=

数字信号处理学习心得 体会

数字信号处理学习心得 一、课程认识和内容理解 《数字信号处理》是我们通信工程和电子类专业的一门重要的专业基础课程,主要任务是研究数字信号处理理论的基本概念和基本分析方法,通过建立数学模型和适当的数学分析处理,来展示这些理论和方法的实际应用。 数字信号处理技术正飞速发展,它不但自成一门学科,更是以不同形式影响和渗透到其他学科:它与国民经济息息相关,与国防建设紧密相连;它影响或改变着我们的生产、生活方式,因此受到人们普遍的关注。信息科学是研究信息的获取、传输、处理和利用的一门科学,信息要用一定形式的信号来表示,才能被传输、处理、存储、显示和利用,可以说,信号是信息的表现形式。这学期数字信号处理所含有的具体内容如下: 第一单元的课程我们深刻理解到时域离散信号和时域离散系统性质和特点;时域离散信号和时域离散系统时域分析方法;模拟信号的数字处理方法。 第二单元的课程我们理解了时域离散信号(序列)的傅立叶变换,时域离散信号Z变换,时域离散系统的频域分析。 第三单元的课程我们学习了离散傅立叶变换定义和性质,离散傅立叶变换应用——快速卷积,频谱分析。 第四单元的课程我们重点理解基 2 FFT算法——时域抽取法﹑频域抽取法,FFT的编程方法,分裂基FFT算法。 第五单元的课程我们学了网络结构的表示方法——信号流图,无限脉冲响

应基本网络结构,有限脉冲响应基本网络结构,时域离散系统状态变量分析法。 第六单元的课程我们理解数字滤波器的基本概念,模拟滤波器的设计,巴特沃斯滤波器的设计,切比雪夫滤波器的设计,脉冲响应不变法设计无限脉冲响应字数字滤波器,双线性变换法设计无限脉冲响应字数字滤波器,数字高通﹑带通﹑带阻滤波器的设计。 第七单元的课程我们学习了线性相位有限脉冲响应(FIR)数字滤波器,窗函数法设计有限脉冲响应(FIR)数字滤波器,频率采样法设计有限脉冲响应(FIR)数字滤波器 二、专业认识和未来规划 通信工程是一门工程学科,主要是在掌握通信基本理论的基础上,运用各种工程方法对通信中的一些实际问题进行处理。通过该专业的学习,可以掌握电话网、广播电视网、互联网等各种通信系统的原理,研究提高信息传送速度的技术,根据实际需要设计新的通信系统,开发可迅速准确地传送各种信息的通信工具等。 对于我们通信专业,我觉得是个很好的专业,现在这个专业很热门,这个专业以后就业的方向也很多,就业面很广。我们毕业以后工作,可以进入设备制造商、运营商、专有服务提供商以及银行等领域工作。当然,就业形势每年都会变化,所以关键还是要看自己。可以从事硬件方面,比如说PCB,别小看这门技术,平时我们在试验时制作的简单,这一技术难点就在于板的层数越多,要做的越稳定就越难,这可是非常有难度的,如果学好了学精了,也是非常好找工作的。也可以从事软件方面,这实际上要我们具备比较好的模电和数电的

数字信号处理教案 余月华

课程特点: 本课程是为电子、通信专业三年级学生开设的一门课程,它是在学生学完了信号与系统的课程后,进一步为学习专业知识打基础的课程。本课程将通过讲课、练习使学生掌握数字信号处理的基本理论和方法。课程内容包括:离散时间信号与系统;离散变换及其快速算法;数字滤波器结构;数字滤波器设计;数字信号处理系统的实现等。 本课程逻辑性很强, 很细致, 很深刻;先难后易, 前三章有一定的难度, 倘能努力学懂前三章(或前三章的0080), 后面的学习就会容易一些;只要在课堂上专心听讲, 一般是可以听得懂的, 但即便能听懂, 习题还是难以顺利完成。这是因为数字信号分析技巧性很强, 只了解基本的理论和方法, 不辅以相应的技巧, 是很难顺利应用理论和方法的。论证训练是信号分析课基本的,也是重要的内容之一, 也是最难的内容之一。 因此, 理解证明的思维方式, 学习基本的证明方法, 掌握叙述和书写证明的一般语言和格式, 是信号分析教学贯穿始终的一项任务。 鉴于此, 建议的学习方法是: 预习, 课堂上认真听讲, 必须记笔记, 但要注意以听为主, 力争在课堂上能听懂七、八成。 课后不要急于完成作业, 先认真整理笔记, 补充课堂讲授中太简或跳过的推导, 阅读教科书, 学习证明或推导的叙述和书写。基本掌握了课堂教学内容后, 再去做作业。在学习中, 要养成多想问题的习惯。 课堂讲授方法: 1. 关于教材: 《数字信号处理》 作者 丁玉美 高西全 西安电子科技大学出版社 2. 内容多, 课时紧: 大学课堂教学与中学不同的是每次课介绍的内容很多, 因此, 内容重复的次数少, 讲课只注重思想性与基本思路, 具体内容或推导特别是同类型或较简的推理论证及推导计算, 可能讲得很简, 留给课后的学习任务一般很重。. 3. 讲解的重点: 概念的意义与理解, 理论的体系, 定理的意义、条件、结论、定理证明的分析与思路, 具有代表性的证明方法, 解题的方法与技巧,某些精细概念之间的本质差别. 在教学中, 可能会写出某些定理证明, 以后一般不会做特别具体的证明叙述. 4. 要求、辅导及考试: a. 学习方法: 适应大学的学习方法, 尽快进入角色。 课堂上以听为主, 但要做课堂笔记,课后一定要认真复习消化, 补充笔记,一般课堂教学与课外复习的时间比例应为1 : 3 。 b. 作业: 大体上每两周收一次作业, 一次收清。每次重点检查作业总数的三分之一。 作业的收交和完成情况有一个较详细的登记, 缺交作业将直接影响学期总评成绩。 c. 辅导: 大体两周一次。 d. 考试: 只以最基本的内容进行考试, 大体上考课堂教学和所布置作业的内容。 课程的基本内容与要求 第一章. 时域离散信号与时域离散系统 1. 熟悉6种常用序列及序列运算规则; 2. 掌握序列周期性的定义及判断序列周期性的方法; 3. 掌握离散系统的定义及描述方法(时域描述和频域描述); 4. 掌握LSI 系统的线性移不变和时域因果稳定性的判定; 第二章 时域离散信号与系统的傅立叶变换分析方法

DSP课程设计 DSP原理及应用课程设计一、设计题目——正弦波信号发生器 二、设计目的 1、掌握用汇编语言编写输出正弦波信号的程序 2、掌握正弦波信号的 DSP 实现原理和 C54X 编程技巧 3、进一步加深对CCS 的认识 4、能通过 CCS 的图形显示工具观察正弦信号波形三、实验设备 PC 兼容机一台,操作系统为 WindowsXP,安装Code Composer Studio 3.1软件。 四、设计原理 在通信、仪器和工业控制等领域的信号处理系统中常常会用到信号发生器来产生正弦波! 产生正弦波的方法一是查表法,二是泰勒级数展开法!查表法主要用于对精度要求不很高的场合,而泰勒级数展开法是一种比查表法更为有效的方法,它能精确地计算出一个角度的正弦和余弦值,且只需要较少的存储空间。本实验将利用泰勒级数展开法利用计算一个角度的正弦值和余弦值程序可实现正弦波。 (1)产生正弦波的算法:在高等数学中,正弦函数和余弦函数可以展开成泰勒级数,其表达式为: 3579xxxxsin(x),x,,,,,... 3!5!7!9! 2468xxxx cos(x),1,,,,,...2!4!6!8! 若要计算一个角度的正弦和余弦值,可取泰勒级数的前五项进行近似计算。 3579xxxxx,x,,,,,sin()...3!5!7!9! 2222xxxx(1(1(1(1)))),x,,,,,,,,23456789 2468xxxx cos(x),1,,,,,... 2!4!6!8!

2222xxxx,,,,, 1(1(1(1))) ,,,2345678 由这两个式子可推导出递推公式,即 sin(nx),2cos(x)sin[(n,1)x],sin[(n,2)x] cos(nx),2cos(x)sin[(n,1)x],cos[(n,2)x] 由递推公式可以看出,在计算正弦和余弦值时,不仅需要已知 ,而且还需要、和。 cos(x)sin(n,1)xsin(n,2)xcos(n,2)x (2)正弦波的实现 1、计算一个角度的正弦值 利用泰勒级数的展开式,可计算一个角度x的正弦值,并采用子程序的调用方式。在调用前先在数据存储器d_xs单元中存放x的弧度值,计算结果存放在 d_sinx单元中。 实现计算一个角度的正弦值的程序片段如下: sinx: .def d_xs,d_sinx .data table_s .word 01C7H ;C1=1/(8*9) .word 030BH ;C2=1/(6*7) .word 0666H ;C3=1/(4*5) .word 1556H ;C4=1/(2*3) d_coef_s .usect "coef_s",4 d_xs .usect "sin_vars",1 d_squr_xs .usect "sin_vars",1 d_temp_s .usect "sin_vars",1 d_sinx .usect "sin_vars",1 d_l_s .usect "sin_vars",1

绪论:本章介绍数字信号处理课程的基本概念。 0.1信号、系统与信号处理 1.信号及其分类 信号是信息的载体,以某种函数的形式传递信息。这个函数可以是时间域、频率域或其它域,但最基础的域是时域。 分类: 周期信号/非周期信号 确定信号/随机信号 能量信号/功率信号 连续时间信号/离散时间信号/数字信号 按自变量与函数值的取值形式不同分类: 2.系统 系统定义为处理(或变换)信号的物理设备,或者说,凡是能将信号加以变换以达到人们要求的各种设备都称为系统。 3.信号处理 信号处理即是用系统对信号进行某种加工。包括:滤波、分析、变换、综合、压缩、估计、识别等等。所谓“数字信号处理”,就是用数值计算的方法,完成对信号的处理。 0.2 数字信号处理系统的基本组成 数字信号处理就是用数值计算的方法对信号进行变换和处理。不仅应用于数字化信号的处理,而且

也可应用于模拟信号的处理。以下讨论模拟信号数字化处理系统框图。 (1)前置滤波器 将输入信号x a(t)中高于某一频率(称折叠频率,等于抽样频率的一半)的分量加以滤除。 (2)A/D变换器 在A/D变换器中每隔T秒(抽样周期)取出一次x a(t)的幅度,抽样后的信号称为离散信号。在A/D 变换器中的保持电路中进一步变换为若干位码。 (3)数字信号处理器(DSP) (4)D/A变换器 按照预定要求,在处理器中将信号序列x(n)进行加工处理得到输出信号y(n)。由一个二进制码流产生一个阶梯波形,是形成模拟信号的第一步。 (5)模拟滤波器 把阶梯波形平滑成预期的模拟信号;以滤除掉不需要的高频分量,生成所需的模拟信号y a(t)。 0.3 数字信号处理的特点 (1)灵活性。(2)高精度和高稳定性。(3)便于大规模集成。(4)对数字信号可以存储、运算、系统可以获得高性能指标。 0.4 数字信号处理基本学科分支 数字信号处理(DSP)一般有两层含义,一层是广义的理解,为数字信号处理技术——DigitalSignalProcessing,另一层是狭义的理解,为数字信号处理器——DigitalSignalProcessor。 0.5 课程内容 该课程在本科阶段主要介绍以傅里叶变换为基础的“经典”处理方法,包括:(1)离散傅里叶变换及其快速算法。(2)滤波理论(线性时不变离散时间系统,用于分离相加性组合的信号,要求信号频谱占据不同的频段)。 在研究生阶段相应课程为“现代信号处理”(AdvancedSignalProcessing)。信号对象主要是随机信号,主要内容是自适应滤波(用于分离相加性组合的信号,但频谱占据同一频段)和现代谱估计。 简答题: 1.按自变量与函数值的取值形式是否连续信号可以分成哪四种类型? 2.相对模拟信号处理,数字信号处理主要有哪些优点? 3.数字信号处理系统的基本组成有哪些?

DSP设计笔记 CPLD可以控制不同的复位信号。CPLD的寄存器映射到EMIF的CE1数据空间,它的地址是0x90080000。U12是CPLD。 SN74LVTH16245A是三态总线收发器。- OE 输出使能,DIR是直接控制输入端。DIC与- OE 的 状态决定着A、B两总线的传输方向。当他们同为低电位时,数据由B总线传输到A总线; 当- OE 为低DIR为高时,数据由A总线传输到B总线;当- OE 为高时,收发器处于不工作状态。 DSP与PC机的PCI总线高速数据传输 [日期: 2004-12-6] 来源:国外电子元器件作者:肖逾男宋元 胜 [字体:大中 小] 摘要:介绍了TI公司的高性能浮点式数字信号处理芯片TMS320C6713的接口信号及控制寄存器,并在此基础上,指出了该DSP通过PCI总线与PC机进行高速数据传输的实现方法,同时给出了TMS320C6713和PC机通过PCI9052总线接口芯片实现接口的硬件原理图。 关键词:DSP;数据传输;TMS320C6713 PCI9052 TMS320C6713是TI公司在TMS320C6711的基础上推出的C6000系列新一代浮点DSP芯片,它是目前为止C6000系列DSP芯片中性能最高的一种。TMS320C6713可在255MHz的时钟频率下实现1800MIPS/1350MFLOPS的定点和浮点运算,因而可极大地满足通信、雷达、数字电视等高科技领域对信号处理实时性的要求。同时其主机口(HPI)可灵活地和PCI总线控制器相连接。而PC机则可通过PCI总线控制器直接访问TMS320C6713的存储空间和外围设备,从而实现PC机与TMS320C6713之间的高速数据传输。

《DSP原理及应用课程设计题目》 1、基于TMS320VC5402的DSP最小系统设计 要求: (1)绘制系统框图(VISIO); (2)包括电源设计、复位电路设计、时钟电路设计、存储器设计、JTAG接口设计等,用Protel软件绘制原理图和PCB图; (3)编写测试程序; (4)从理论上分析,设计的系统要满足基本的信号处理要求; (5)参考文献、论文格式规范。 2、基于TMS320VC5402的频谱分析系统设计(可作为毕业设计) 要求: (1)系统设计中,C5402完成数据处理,AT89S52单片机完成控制和显示,绘制出系统框图(VISIO); (2)包括电源设计、复位电路设计、时钟电路设计、A/D转换设计、电平转换设计、JTAG接口设计等,用Protel软件绘制原理图和PCB图; (3)给出程序流程图,设计频谱分析系统软件(C5402的数据处理软件、单片机的控制及显示软件); (4)通过对系统的全面分析得出设计结论(被处理信号的频率范围、采用的信号处理算法等); (5)参考文献,论文格式规范。

3、基于TMS320VC5402的FIR数字滤波器的设计 要求: (1)绘制系统框图(VISIO); (2)包括电源设计、复位电路设计、时钟电路设计、存储器设计、A/D转换设计、JTAG接口设计等,用Protel软件绘制原理图和PCB图; (3)给出所设计的FIR低通滤波器的技术指标,用MATLAB求解滤波器的参数并仿真; (4)给出程序流程图,编写程序,在CCS中完成仿真; (5)参考文献、论文格式规范。 4、基于TMS320VC5402的IIR数字滤波器的设计 要求: (1)绘制系统框图(VISIO); (2)包括电源设计、复位电路设计、时钟电路设计、存储器设计、A/D转换设计、JTAG接口设计等,用Protel软件绘制原理图和PCB图; (3)给出所设计的IIR滤波器的技术指标,用MATLAB求解滤波器的参数并仿真; (4)给出程序流程图,编写程序,在CCS中完成仿真; (5)参考文献、论文格式规范。

数字信号处理学习心得 XXX ( XXX学院XXX班) 一、课程认识和内容理解 《数字信号处理》是我们通信工程和电子类专业的一门重要的专业基础课程,主要任务是研究数字信号处理理论的基本概念和基本分析方法,通过建立数学模型和适当的数学分析处理,来展示这些理论和方法的实际应用。 数字信号处理技术正飞速发展,它不但自成一门学科,更是以不同形式影响和渗透到其他学科:它与国民经济息息相关,与国防建设紧密相连;它影响或改变着我们的生产、生活方式,因此受到人们普遍的关注。信息科学是研究信息的获取、传输、处理和利用的一门科学,信息要用一定形式的信号来表示,才能被传输、处理、存储、显示和利用,可以说,信号是信息的表现形式。这学期数字信号处理所含有的具体内容如下: 第一单元的课程我们深刻理解到时域离散信号和时域离散系统性质和特点;时域离散信号和时域离散系统时域分析方法;模拟信号的数字处理方法。 第二单元的课程我们理解了时域离散信号(序列)的傅立叶变换,时域离散信号Z变换,时域离散系统的频域分析。 第三单元的课程我们学习了离散傅立叶变换定义和性质,离散傅立叶变换应用——快速卷积,频谱分析。 第四单元的课程我们重点理解基2 FFT算法——时域抽取法﹑频域抽取法,FFT的编程方法,分裂

基FFT算法。 第五单元的课程我们学了网络结构的表示方法——信号流图,无限脉冲响应基本网络结构,有限脉冲响应基本网络结构,时域离散系统状态变量分析法。 第六单元的课程我们理解数字滤波器的基本概念,模拟滤波器的设计,巴特沃斯滤波器的设计,切比雪夫滤波器的设计,脉冲响应不变法设计无限脉冲响应字数字滤波器,双线性变换法设计无限脉冲响应字数字滤波器,数字高通﹑带通﹑带阻滤波器的设计。 第七单元的课程我们学习了线性相位有限脉冲响应(FIR)数字滤波器,窗函数法设计有限脉冲响应(FIR)数字滤波器,频率采样法设计有限脉冲响应(FIR)数字滤波器 二、专业认识和未来规划 通信工程是一门工程学科,主要是在掌握通信基本理论的基础上,运用各种工程方法对通信中的一些实际问题进行处理。通过该专业的学习,可以掌握电话网、广播电视网、互联网等各种通信系统的原理,研究提高信息传送速度的技术,根据实际需要设计新的通信系统,开发可迅速准确地传送各种信息的通信工具等。 对于我们通信专业,我觉得是个很好的专业,现在这个专业很热门,这个专业以后就业的方向也很多,就业面很广。我们毕业以后工作,可以进入设备制造商、运营商、专有服务提供商以及银行等领域工作。当然,就业形势每年都会变化,所以关键还是要看自己。可以从事硬件方面,比如说PCB,别小看这门技术,平时我们在试验时制作的简单,这一技术难点就在于板的层

<数字信号处理的FPGA实现> Verilog写状态机大概有这样几点要求: 1、组合逻辑完成状态转移的条件判断,时序逻辑完成状态机的状态转移。 2、组合逻辑和时序逻辑分别在两个不同的always块中完成,根据状态机状态通过译码逻辑产生的与状态机无关的逻辑部分不要放在专用的状态机always块中。 3、状态编码预先定义为parameter,状态较少的状态机推荐使用one-hot方式编码,以减小译码逻辑的复杂度,提高性能。 4、建议单独使用一个模块来描述状态机。 5、状态机应有一个default状态,在上电复位的时候作为初始状态。 6、注意状态机组合逻辑中的if...else语句,不要出现latch。 7、对于复杂状态机,最好采用状态机嵌套方式完成。 其实上面很多都是按照Synopsys LEDA的coding style的要求的,状态机的写法相对固定,因此很多Design entry的工具可以自动生成状态机代码,Xilinx也有工具支持直接由状态转移图输入完成状态机的编码。所以关键还是画好状态转移图,其他就相对简单了。 visual hdl+ISE+synplify Pro+modelsim! 1.设计输入 1)设计的行为或结构描述。 2)典型文本输入工具有UltraEdit-32和Editplus.exe.。 3)典型图形化输入工具-Mentor的Renoir。 4)我认为UltraEdit-32最佳。 2.代码调试 1)对设计输入的文件做代码调试,语法检查。 2)典型工具为Debussy。 3.前仿真 1)功能仿真 2)验证逻辑模型(没有使用时间延迟)。 3)典型工具有Mentor公司的ModelSim、Synopsys公司的VCS和VSS、Aldec公司的Active、Cadense公司的NC。 4)我认为做功能仿真Synopsys公司的VCS和VSS速度最快,并且调试器最好用,Mentor 公司的ModelSim对于读写文件速度最快,波形窗口比较好用。 4.综合 1)把设计翻译成原始的目标工艺 2)最优化 3)合适的面积要求和性能要求 4)典型工具有Mentor公司的LeonardoSpectrum、Synopsys公司的DC、Synplicity公司的Synplify。 5)推荐初学者使用Mentor公司的LeonardoSpectrum,由于它在只作简单约束综合后的速度和面积最优,如果你对综合工具比较了解,可以使用Synplicity公司的Synplify。 5.布局和布线 1)映射设计到目标工艺里指定位置 2)指定的布线资源应被使用

目录 1设计原理及内容 (1) 1.1语音编码原理 (1) 1.2设计内容 (1) 1.2.1 基本部分 (1) 1.2.2 扩展部分 (1) 2设计资源介绍 (2) 2.1多通道缓冲串行口MCBSP...................................................... .2 2.1.1 工作原理 (2) 2.1.2 相关头文件 (2) 2.2 TLC320AD50 CODEC编码译码器 (2) 2.3 存储器 (3) 2.4压扩硬件 (4) 2.5 麦克风和耳机接口 (5) 3 设计思想 (5) 3.1实验方案 (5) 4 .程序设计 (6) 4.1 程序流程图 (6) 4.2各个分块程序设计 (7) 5.程序清单 (9) 6 操作步骤和结果 (19) 7 参考文献 (20)

1.设计原理与实验内容 1.1语音编码原理: (1)概念:语音编码一般分为两类:一类是波形编码,一类是被称为“声码器技术”的编码。PCM编码即脉冲编码调制。波形编码的最简单形式就是脉冲编码调制(Pulse code modulation),这种方式将语音变换成与其幅度成正比的二进制序列,而二进制数值往往采用脉冲表示,并用脉冲对采样幅度进行编码,所以叫做脉冲编码调制。脉冲编码调制没有考虑语音的性质,所以信号没有得到压缩。 (2)量化:脉冲编码调制用同等的量化级数进行量化,即采用均匀量化,而均匀量化是基本的量化方式。但是均匀量化有缺点,在信号动态范围较大而方差较国际上有两种非均匀量化的方法:A律和μ律,μ律是最常用的一种。在美国,7位μ律是长途电话质量的标准。而我国采用的是A律压缩,而且有标准的(3)DPCM&ADPCM: 降低传输比特率的方法之一是减少编码的信息量,这要消除语音信号中的冗余度。相邻的语音样本之间存在明显的相关性,因此对相邻样本间的差信号进行编码,便可使信息量得到压缩。因为差分信号比原语音信号的动态范围和平均能量都小。这种编码叫Differential PCM,简称DPCM,即差分脉冲编码调制。 1.2 设计内容: 1.2.1基本部分: (1)使用DSP实现语音压缩和解压缩的基本算法,算法类型自定,例如可以采用G.711、G.729等语音压缩算法。 (2)采用A/D转换器从MIC输入口实时采集语音信号,进行压缩后存储到DSP的片内和片外RAM 存储器中,存储时间不小于10秒。 (3)存储器存满之后,使用DSP进行实时解压缩,并从SPEAKER输出口进行回放输出。(4)使用指示灯对语音存储和回放过程进行指示。 1.2.2发挥部分: 使用多种算法进行语音的压缩、存储和解压缩,比较它们之间的优缺点。 2. 设计资源介绍 2.1多通道缓冲串行口MCBSP 2.1.1工作原理 C5402 具有2 个高速的全双工同步串行口,可用来与系统中的其它C54x 器