DSP设计笔记

- 格式:doc

- 大小:105.00 KB

- 文档页数:9

Knowledge问题谁在DSP的汇编语言中加入了NOP指令?NOP指令加入的条件是什么?About DSP1.DSP是实时数字信号处理的核心和标志。

2.DSP分为专用和通用两种类型。

专用DSP一般采用定点数据结构(一般不支持小数),数据结构简单,处理速度快;通用DSP灵活性好,但是处理速度有所降低。

3.DSP采用取指、译码、执行三个阶段的流水线(Pipeline)技术,缩短了执行时间,提高了运行速率。

DSP具有8个Functional unit,如果并行处理的话,以600MHz的时钟计算,如果执行的指令是single cycle指令,则可以4800MIPS(指令每秒)。

4.DSP的8个functional Unit,具有独特的功能,对滤波、矩阵运算、FFT(傅里叶变换)具有哈弗结构把指令空间与数据空间隔离的存储方式。

这样实现是为了实现指令的连续读取,而实现pipeline流水线结构。

传统哈弗结构:两个独立的存储空间,还使用独立总线。

让取指与执行存储独立,加快执行速度。

改进型哈弗结构:指令与数据的存储空间还是独立的。

但是使用公共的总线(地址总线与数据总线)。

这样实现的原因是因为出现了CACHE,数据的存储动作大部分被内部的CACHE 总线承接了,所以总线冲突的情况会大大减少。

同时让总线的结构与控制变得简单,CACHE 存储的速度也明显快于外设存储器。

冯诺依曼结构:是指令空间与数据空间共享的存放方式。

它不能实现pipeline的执行过程。

Pipeline(流水线)技术是把指令的取指-译码和指令的执行独立开来的技术。

虽然每条指令的过程还是要经过取指-译码-执行三个阶段最少3个CPU Cycle。

但是多个指令同时并行先后进行,保证总体的指令吞吐速率理想情况下可以保证在每个指令只要一个CPU CYCLE。

Pipeline技术必须要有哈弗结构支持,即必须把指令空间与数据空间隔离存放。

流水线阻断流水线中阻断现象也十分普遍,下面就各种阻断情况下的流水线性能进行详细分析。

1GPIO作为通用I/O口使用a)EALLOW;//防止私自写或覆盖寄存器的内容,加了这句,接下来可以操作寄存器了b)GpioCtrlRegs.GPAMUX1.bit.GPIO0 = 0; // GPIO0复用为普通I/O功能c)GpioCtrlRegs.GPADIR.bit.GPIO0 = 1; // 1,设置为输出;0设置为输入d)EDIS;//加了这句,接下来不可以操作寄存器注:EALLOW,EDIS总是成对出现2中断过程(代码以配置SCIB模块的接收中断为例,LSPCLK是37.5MHz)中断共分三级,1,外设级;2,PIE级;3,CPU级;外设级的中断标志必须手动清零;PIE级和CPU级的中断标志位由硬件自动清零。

中断响应例程:第一步,配置中断源,即允许产生什么类型点中断。

例如,定时器中断,串口中断,外部中断等。

ScibRegs.SCICTL2.bit.RXBKINTENA =1;允许接收中断第二步,配置PIE(外部中断扩展)a) InitPieCtrl();//初始化Pie控制b) InitPieVectTable();//初始化Pie向量表控制c) EALLOW;d) PieVectTable.SCIRXINTB=&scibreceive;//指定中断服务程序地址e) EDIS;f) PieCtrlRegs.PIECTRL.bit.ENPIE=1;//使能从PIECTRL中读取中断向量g) PieCtrlRegs.PIEIER9.bit.INTx3=1;//使能SCIB的接收中断h) IER |= M_INT9;//允许外部中断i) EINT;j) ERTM;第三步,中断响应在中断服务程序里,必须用PieCtrlRegs.PIEACK.all = PIEACK_GROUP9;//清楚中断已响应标识,再写自己等程序代码3串口配置InitScibGpio();scib_echoback_init();4AD转换InitAdc();//允许ADC时钟,带隙和参考电路上电,核中模拟电路上电AdcRegs.ADCTRL2.all = 0x2000;//ADC模块开始转换程序在FLASH运行时,需要加如下两句代码:(不知道具体原因)MemCopy(&RamfuncsLoadStart, &RamfuncsLoadEnd, &RamfuncsRunStart);InitFlash();。

dsp重点知识点总结1. 数字信号处理基础数字信号处理的基础知识包括采样定理、离散时间信号、离散时间系统、Z变换等内容。

采样定理指出,为了保证原始信号的完整性,需要将其进行采样,并且采样频率不能小于其最高频率的两倍。

离散时间信号是指在离散时间点上取得的信号,可以用离散序列表示。

离散时间系统是指输入、输出和状态都是离散时间信号的系统。

Z变换将时域的离散信号转换为Z域的函数,它是离散时间信号处理的数学基础。

2. 时域分析时域分析是对信号在时域上的特性进行分析和描述。

时域分析中常用的方法包括时域图形表示、自相关函数、互相关函数、卷积等。

时域图形表示是通过时域波形来表示信号的特性,包括幅度、相位、频率等。

自相关函数是用来描述信号在时间上的相关性,互相关函数是用来描述不同信号之间的相关性。

卷积是一种将两个信号进行联合的运算方法。

3. 频域分析频域分析是对信号在频域上的特性进行分析和描述。

频域分析中常用的方法包括频谱分析、傅里叶变换、滤波器设计等。

频谱分析是通过信号的频谱来描述信号在频域上的特性,可以得到信号的频率成分和相位信息。

傅里叶变换是将时域信号转换为频域信号的一种数学变换方法,可以将信号的频率成分和相位信息进行分析。

滤波器设计是对信号进行滤波处理,可以剔除不需要的频率成分或增强需要的频率成分。

4. 数字滤波器数字滤波器是数字信号处理中的重要组成部分,通过对信号进行滤波处理,可以实现对信号的增强、降噪、分离等效果。

数字滤波器包括有限冲激响应(FIR)滤波器和无限冲激响应(IIR)滤波器两种类型。

有限冲激响应(FIR)滤波器是一种只有有限个系数的滤波器,它可以实现线性相位和稳定性处理。

无限冲激响应(IIR)滤波器是一种有无限个系数的滤波器,它可以实现非线性相位和较高的滤波效果。

5. 离散傅里叶变换(DFT)和快速傅里叶变换(FFT)离散傅里叶变换(DFT)是将时域离散信号转换为频域离散信号的一种数学变换方法,其计算复杂度为O(N^2)。

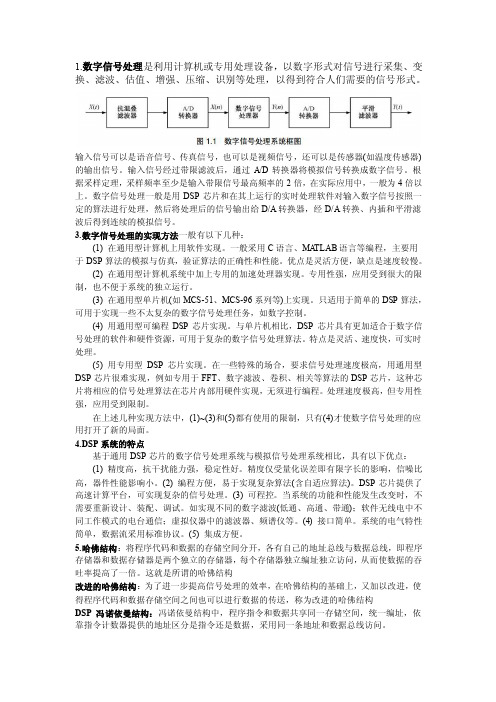

1.数字信号处理是利用计算机或专用处理设备,以数字形式对信号进行采集、变换、滤波、估值、增强、压缩、识别等处理,以得到符合人们需要的信号形式。

输入信号可以是语音信号、传真信号,也可以是视频信号,还可以是传感器(如温度传感器)的输出信号。

输入信号经过带限滤波后,通过A/D转换器将模拟信号转换成数字信号。

根据采样定理,采样频率至少是输入带限信号最高频率的2倍,在实际应用中,一般为4倍以上。

数字信号处理一般是用DSP芯片和在其上运行的实时处理软件对输入数字信号按照一定的算法进行处理,然后将处理后的信号输出给D/A转换器,经D/A转换、内插和平滑滤波后得到连续的模拟信号。

3.数字信号处理的实现方法一般有以下几种:(1) 在通用型计算机上用软件实现。

一般采用C语言、MA TLAB语言等编程,主要用于DSP算法的模拟与仿真,验证算法的正确性和性能。

优点是灵活方便,缺点是速度较慢。

(2) 在通用型计算机系统中加上专用的加速处理器实现。

专用性强,应用受到很大的限制,也不便于系统的独立运行。

(3) 在通用型单片机(如MCS-51、MCS-96系列等)上实现。

只适用于简单的DSP算法,可用于实现一些不太复杂的数字信号处理任务,如数字控制。

(4) 用通用型可编程DSP芯片实现。

与单片机相比,DSP芯片具有更加适合于数字信号处理的软件和硬件资源,可用于复杂的数字信号处理算法。

特点是灵活、速度快,可实时处理。

(5) 用专用型DSP芯片实现。

在一些特殊的场合,要求信号处理速度极高,用通用型DSP芯片很难实现,例如专用于FFT、数字滤波、卷积、相关等算法的DSP芯片,这种芯片将相应的信号处理算法在芯片内部用硬件实现,无须进行编程。

处理速度极高,但专用性强,应用受到限制。

在上述几种实现方法中,(1)~(3)和(5)都有使用的限制,只有(4)才使数字信号处理的应用打开了新的局面。

4.DSP系统的特点基于通用DSP芯片的数字信号处理系统与模拟信号处理系统相比,具有以下优点:(1) 精度高,抗干扰能力强,稳定性好。

时钟发生器:参考时钟有两种方法产生 1 在EXTCLK引脚上直接接入一个外部时钟,如一体化振荡器的输出信号,这时XIN接地,XOUT悬空2 将EXRCLK接地,通过XIN和XOUT接入晶振,电容。

锁相环电路:作用是锁定参考时钟相位,一旦达到同步锁定后,将自动跟踪参考时钟的相位,并对输入的参考时钟进行5倍频,使倍频后的时钟与参考时钟实现同步JTAG 仿真接口TCK 测试时钟输入TDI 测试数据输入,数据通过TDI输入JTAG口TDO 测试数据输出,数据通过TDO从JTAG口输出TMS 测试模式选择,TMS用来设置JTAG口处于某种特定的测试模式/TRST 测试复位,可选输入引脚,低电平有效EMU0,EMU1 以激活JTAG口,实现仿真功能,接上拉电阻4.7K到3.3V。

TCK—RET:测试信号的返回,保证目标系统与测试时钟信号同步PD:检测信号固定为5V存储器分配方式有两种:微计算机引导方式,微处理器方式,方式选择有MCBL/BP,两种差异在于是否允许引导,如果不引导是微处理器方式,反之是微计算机引导方式。

CACHE 用于存放最近使用过的重复率比较高的指令代码,对于最近出现过的指令,可直接从CACHE中取指,从而减少取指所开销的时间,加速程序运行。

DSP有两个32位定时器0,1记为TCLK0,TCLK1 。

定时器的工作过程 1 时钟选择器从内部时钟,外部时钟,极性控制选择计数器的时钟源,周期寄存器存放需要计数的个数,计数器用于累计实际的计数值2 比较器对周期寄存器和计数器的值进行比较,二者相等时3 脉冲发生器产生定时器的输出信号,同时将信息反馈到定时器的全局控制寄存器的状态位TSTAT。

DMA控制器能够在没有CPU操作干预下执行输入输出功能。

因此TMS320有可能和慢速的外部存储器及串行的A/D,D/A等交换数据,而不会降低CPU的计算能力。

其结果实改进系统的性能,提高数据处理能力。

DMA进行数据传输的主要工作是从一个存储位置读出数据并将其写另一个存储器中的指定位置。

1、cj431电压基准芯片,2.5v2、电平标准3、驱动器74HC245(为增强PWM的驱动负载能力)4、增加输入端的抗干扰能力:在芯片的输入端加上拉电阻加电源或者下拉电阻接地,没有用到的采样端口尽量不要悬空。

5、D/A电路方案通用扩展语言GEL和c相似,但是有所不同。

GEL语言是C语言的一个子集。

与c语言不同的是gel不需要指定函数返回值的类型。

Gel中的while语句和c中的while语句相同,gel不支持标准c的break和continue语句6、一个完整的dsp工程包括头文件(.h),库文件(.lib),源文件(.c),以及配置文件.Cmd使用关键字MENUITEM可以在gel菜单下选择用户自定义的菜单项,然后用hotmenu、dialog或slider等关键字,在这个新的下拉菜单中添加新的菜单项。

7、关于添加文件遇到的问题8、变量查找:edit→find:Ctrl+f9、调试时,添加断点的快捷方法如下点击图上的小手即可10、单步调试第一个的意思是单击一步走一步,第二个的意思是指在单步运行时遇到子函数不进入子函数内部进行而是把它当成一步来执行,第三个的意思是当执行到子函数内部时使用这个按钮就可以执行完剩下的部分返回上一层函数。

如果想在一个窗口内同时看到c和汇编,则有操作View→mixed source/asm 11、观察变量右击变量→add to watch window 可以得到变量的值、类型、地址等。

12、位域定义、结构体以及共同体的知识结构体先定义再声明Union SCIFFCT_REG {Uint16 all;Struct SCIFFCT_BITS bit;};//---------------------------------------------------------------------------// SCI Register File://Struct SCI_REGS {Union SCICCR_REG SCICCR; // Communications control register Union SCICTL1_REG SCICTL1; // Control register 1Uint16 SCIHBAUD; // Baud rate (high) registerUint16 SCILBAUD; // Baud rate (low) registerUnion SCICTL2_REG SCICTL2; // Control register 2Union SCIRXST_REG SCIRXST; // Receive status registerUint16 SCIRXEMU; // Receive emulation buffer registerUnion SCIRXBUF_REG SCIRXBUF; // Receive data bufferUint16 rsvd1; // reservedUint16 SCITXBUF; // Transmit data bufferUnion SCIFFTX_REG SCIFFTX; // FIFO transmit registerUnion SCIFFRX_REG SCIFFRX; // FIFO receive registerUnion SCIFFCT_REG SCIFFCT; // FIFO control registerUint16 rsvd2; // reservedUint16 rsvd3; // reservedUnion SCIPRI_REG SCIPRI; // FIFO Priority control};//---------------------------------------------------------------------------// SCI External References & Function Declarations://Extern volatile struct SCI_REGS SciaRegs;Extern volatile struct SCI_REGS ScibRegs;由于scihbaud和scilbaud定义时为unit16型的,所以不能用.all或者.bit 的方式来访问,只能直接给寄存器整体进行赋值。

DSP学习心得笔记---------------- 白建成.baijc.icekoor引言:学习DSP的时间有两个多月了,收获很多新知识,我们要每天都有进步才行,以下内容没有特别的顺序,跟具自己的学习情况写的,如果有不对的地方希望指出来,如果有不懂得也可以问我,大家相互交流很重要,我的一个邮箱:baijc@欢迎联系!建立新工程过程中:问题1:"GPIO_Study.c", line 61: fatal error: could not open source file "DSP280x_Device.h"1 fatal error detected in the compilation of "GPIO_Study.c".解决方法:因为project →build options→compiler→preprocessor中,要包含的头文件的地址没有加进去,你可以找到头文件的地址,然后加进去。

问题2:undefined first referencedsymbol in file--------- ----------------_c_int00 D:\DSP study\test3\Debug\DSP280x_CodeStartBranch.objFS$$MPY D:\DSP study\test3\Debug\DSP280x_CpuTimers.objFS$$TOL D:\DSP study\test3\Debug\DSP280x_CpuTimers.obj>> error: symbol referencing errors - './Debug/test3.out' not built或者下面的问题:undefined first referencedsymbol in file--------- ----------------_c_int00 D:\DSPstudy\GPIO_Study\Debug\DSP280x_CodeStartBranch.obj>> error: symbol referencing errors - './Debug/GPIO_Study.out' not built解决办法都是下面:这个问题是因为没有加在库文件,请在project →build options→linker→libraries 中加入rts2800.lib。

GPIO寄存器一共分为两大类:一类是控制寄存器:主要由功能控制寄存器GPxMUX,方向控制寄存器GPxDIR,输入限定控制寄存器GPxQUAL组成。

另一类是数据寄存器:主要由数据寄存器GPxDAT,置位寄存器GPxSET,清除寄存器GPxCLEAR和取反寄存器GPxTOGGLE 组成。

假设已经设置为数字I/O口,那么输入输出又是怎么定义的呢?如下所示:输入限定控制寄存器、可以通过这个寄存器对输入信号进行量化限制、改善输入信号从而去除不希望的噪声污染。

连续采样到多个相同的电平时才认为是该电平、滤除了干扰信号。

LED闪烁实验系统初始化函数、GPIO初始化函数、主函数、延时子函数在寄存器中结构体的运用Struct GPADIR_BITS { // bits descriptionUint16 GPIOA0:1; // 0Uint16 GPIOA1:1; // 1Uint16 GPIOA2:1; // 2Uint16 GPIOA3:1; // 3Uint16 GPIOA4:1; // 4Uint16 GPIOA5:1; // 5Uint16 GPIOA6:1; // 6Uint16 GPIOA7:1; // 7Uint16 GPIOA8:1; // 8Uint16 GPIOA9:1; // 9Uint16 GPIOA10:1; // 10Uint16 GPIOA11:1; // 11Uint16 GPIOA12:1; // 12Uint16 GPIOA13:1; // 13Uint16 GPIOA14:1; // 14Uint16 GPIOA15:1; // 15};Union GPADIR_REG {Uint16 all;Struct GPADIR_BITS bit;};第10章 CPU定时器32位定时器周期寄存器、32位计数器寄存器、16位定时器分频器寄存器(决定了每一步的时间)、16位的预定标计数器寄存器只有定时器0是能用的第11章中断系统可屏蔽中断、不可屏蔽中断中断使能寄存器IER某一位为1则屏蔽该对应中断高两位保留、低14位对应着相应的14个中断中断标志寄存器IFR:说明CPU中断提出了相应中断请求若相对应位为0、则说明没有未处理的对应中断若相对应位为1、则说明至少有一个对应中断没有处理INTM 总开关PIE中断控制器组的概念:被分布在不同的组里μC/OS-II由Micrium公司提供,是一个可移植、可固化的、可裁剪的、占先式多任务实时内核,它适用于多种微处理器,微控制器和数字处理芯片(已经移植到超过100种以上的微处理器应用中)。

一、三相电压源变换器的结构1.1 自励式三相电压源变换器的原理图图1 自励式三相电压源变换器的原理结构图1.1.1 原理结构图(如图1所示)1.1.2 各元件的作用与选择:交流侧连接电感L :滤波,减小高次谐波电压造成的脉动,同时起到将变换器和交流电网隔离的作用。

直流侧的电容C :整流时,保持输出直流电压稳定,并滤出输出电压的低次谐波成分;逆变时,为逆变的正常工作提供电压支撑,相当于电压源,保证电压基本无脉动;当交流侧为阻感负载时,需要提供无功功率,直流电容起到缓冲无功能量的作用,反并联的二极管,起到将交流侧到直流侧反馈的无功能量提供通道的作用。

往往该二极管选择快速关断二极管。

1.1.3 何谓自励与他励?自励时直流电压如何建立或控制的?自励:不借助于外部其他辅助电路的激励,由该电路自身的特点,完成对直流侧电压的建立。

自励时直流侧电压建立过程如下:在第一阶段,关断所有的IGBT 器件,利用反向并联的二极管对直流电容进行充电, 这时相当于三相全桥整流。

一般而言, 经过第一阶段的充电,直流侧电压可达520V 左右。

待直流电压稳定后,进行第二阶段的充电,即斩波升压。

任选一支IGBT ,在适当时刻进行开关操作。

如图1所示,以系统线电压AB U 作为同步参考信号,当AB U 为负时,开通VT1,这时有电流流经VT1和VD3经过一段时间后,La 和Lb 中积聚了一定的能量,关断VT1,该回路电流突变,于是电感La 和Lb 中的磁场能转化为电场能而产生过电压。

该过电压与系统电压一起通过二极管对直流电容充电,这时还是相当于三相全桥整流,只不过三相电压幅值更高而已。

重复上述操作,直至直流电压满足要求。

采用这种方法可以做到直流侧电压升压无超调。

直流侧电压达到要求之后,打开所有PWM 脉冲,变换器即并入电网。

他励:就是借助于外部辅助电路,一般为整流器,来为逆变器建立直流侧电压的过程。

充电达到并网的条件即可并网。

逆变器输出电压如何与电网电压实现同步,这是并网变换器的共性问题。

DSP设计笔记CPLD可以控制不同的复位信号。

CPLD的寄存器映射到EMIF的CE1数据空间,它的地址是0x90080000。

U12是CPLD。

SN74LVTH16245A是三态总线收发器。

-OE 输出使能,DIR是直接控制输入端。

DIC与-OE的状态决定着A、B两总线的传输方向。

当他们同为低电位时,数据由B总线传输到A总线;当-OE 为低DIR为高时,数据由A总线传输到B总线;当-OE为高时,收发器处于不工作状态。

DSP与PC机的PCI总线高速数据传输[日期:2004-12-6]来源:国外电子元器件作者:肖逾男宋元胜[字体:大中小]摘要:介绍了TI公司的高性能浮点式数字信号处理芯片TMS320C6713的接口信号及控制寄存器,并在此基础上,指出了该DSP通过PCI总线与PC机进行高速数据传输的实现方法,同时给出了TMS320C6713和PC机通过PCI9052总线接口芯片实现接口的硬件原理图。

关键词:DSP;数据传输;TMS320C6713 PCI9052TMS320C6713是TI公司在TMS320C6711的基础上推出的C6000系列新一代浮点DSP芯片,它是目前为止C6000系列DSP芯片中性能最高的一种。

TMS320C6713可在255MHz的时钟频率下实现1800MIPS/1350MFLOPS的定点和浮点运算,因而可极大地满足通信、雷达、数字电视等高科技领域对信号处理实时性的要求。

同时其主机口(HPI)可灵活地和PCI总线控制器相连接。

而PC机则可通过PCI总线控制器直接访问TMS320C6713的存储空间和外围设备,从而实现PC机与TMS320C6713之间的高速数据传输。

在TMS320C6713DSP与PC机实现高速数据传输的方案中,可选用PLX公司的PCI9052作为两者之间的接口;同时选用PLX公司的NM93CS46作为加载PCI9052配置信息的串行EEPROM;而用TI公司的SN74CBTD3384作为PCI9052与TMS320C6713HPI之间的电平转换芯片。

1TMS320C6713的HPI简介1.1TMS320C6713HPI的接口信号TMS320C6713的HPI是一个16位宽的并行端口。

主机(上位机)掌管着该端口的主控权,可通过HPI直接访问TMS320C6713的存储空间和外围设备。

表1给出了TMS320C6713HPI接口信号的基本特征。

下面对它们的具体工作方式进行说明:HD[15:0]:可以用作数据和地址的共用总线,通过HD[15:0]传送的数据包括控制寄存器的设置值、初始化的访问地址以及要传输的数据。

HCNTL[1:0]:用于控制当前访问的是HPI的哪一个寄存器,该信号同时还提供了一个对HPI数据寄存器(HPID)进行地址自增的访问方式。

在该方式下,主机会连续地访问一个线性存储区域,而无需反复向HPIA写入需要的地址。

表2给出了HCNTL[1:0]控制信号的功能。

HHWIL信号:用于表明并区分HD[15:0]上传输的是32位数据中的高16位还是低16位。

由于TMS320C6713芯片结构决定了它与主机间所有的数据交换都是32位,而HPI端口为16位,所以每次数据访问都需要进行两次存取,而由HPI自动将HD[15:0]上连续的两个16位数据合成32位,当然,也可以用其进行反向分解。

HAS信号:用于复用地址数据总线的主机。

它可使HCNTL、HHWIL和HR/W信号在一个存取周期中快速地实现状态转换。

对于地址数据复用的总线来说,也可以为数据/地址的切换留出更多的时间。

HCS、HDS1和HDS2信号:这三种信号可在片内组合为一个低有效的HSTROBE信号,如图1所示。

其作用是,在读取时,在HSTROBE信号的下降沿锁存输入的HPI控制信号,包括HHWIL、HR/W和HC-NTL[1:0];而在写入时,其下降沿和读取时作用相同,其上升沿则锁存写入的数据。

HRDY信号:用于表明HPI是否已准备好传输数据,其作用是在接口时序上插入等待状态。

如果前一次HPI的访问尚未完成,那么当前访问的第一个半字的存取需要等待,此时,HPI会置HRDY信号为高。

表1 HPI接口信号描述表2 HCNTL[1:0]控制信号的功能1.2TMS320C6713HPI的控制寄存器在TMS320C6713HPI中,可利用三个寄存器来完成主设备和CPU的通信,它们是HPI数据寄存器(HPID)、HPI地址寄存器(HPIA)和HPI控制寄存器(HPIC)。

主机可对这三个寄存器进行读写,而CPU只能对HPIC进行访问。

HPID中存放的是主机从存储空间中读取的数据,或者是主机向TMS320C6713的存储空间中写入的数据。

HPIA中存放的是主机访问TMS320C6713存储空间的地址,其最低两位固定为零。

HPIC中存放的是TMS320C6713的控制信息,其高16位和低16位内容相同。

主机对HPI进行访问的次序为:初始化HPIC、初始化HPIA、从HPID寄存器中读取或向其写入数据。

在初始化HPIC时,HWOB位的设置是关键,它决定着高16位与低16位的传输次序。

2PCI9052与TMS320C6713HPI的接口PCI9052是PLX公司继PCI9050之后推出的用于低成本适配器的总线目标接口芯片。

它支持PCI2.1协议规范,在33MHz的总线时钟频率下,其峰值传输速度可达132MB/s,因而可大大改善数据传输中的瓶颈问题。

同时它还具有方便灵活的开发特点,正是这些特点使其在PCI从模式接口卡的设计中得到了广泛的应用。

表3给出了PCI9052与TMS320C6713HPI接口信号的基本特征。

下面是对它们具体工作方式的一些说明:LAD[31:0]:利用该信号可通过设置LASIBRD局部地址空间总线区域描述寄存器的总线宽度位来调整总线宽度,当LASIBRD[23:22]=00时,采用LAD[7:0]8位宽度,当LASIBRD[23:22]=01时,采用LAD[15:0](16位),当LASIBRD[23:22]=10时,采用LAD[31:0](32位)。

LBE[3:0]字节使能信号是在总线宽度的基础上编码的。

对于32位总线,LBE[3:0]表示哪一个字节被选中:LBE0对应[7:0],LBE1对应[15:8],LBE2对应[23:16],LBE3对应[31:24];而对于16位总线,LBE0对应[7:0],LBE1对应地址的第1位,LBE2不用,LBE3对应[15:8];对于8位总线,LBE0对应地址的第0位,LBE1对应地址的第1位,LBE2和LBE3不用。

CS1和CS2分别带有与之对应的片选基地址寄存器(CSIBASE)。

CSIBASE 0 为片选使能位,其中CSIBASE[27:1]为片选空间位。

从片选空间位的第1位向第27位扫描时,遇到第1个“1”即决定了片选空间的大小,其余位则为片选空间的基地址。

LINT1和LINT2可通过中断控制/状态寄存器INCSR的中断使能位INCSR[6]进行使能,同时可设置其它相关信息。

表3 PCI9052与TMS320C6713的接口信号描述3与PC的高速数据传输TMS320C6713HPI与PCI9052的具体连线如图2所示。

实际上,在具体电路设计时,整个方案的实现除了需要TMS320C6713和PCI9052外,还需要有SN74CBTD3384和NM93CS46。

由于TMS320C6713的I/O是在3.3V电压下工作,而PCI9052在5V电压下工作,所以TMS320C6713与PCI9052之间必须采用SN74CBTD3384进行电平转换。

SN74CBTD3384是TI公司生产的10位总线转换器,它的输入、输出引脚一一对应,并分别排列在芯片的两侧封装。

图2中共选用了三片SN74CBTD3384。

NM93CS46是PLX公司生产的串行EEPROM存储器,用于加载PCI9052配置信息。

其中按一定顺序存放着设备号(DID)、供应商代号(VID)、子设备号(SDID)、子供应商代号(SVID)、PCI总线与局部总线之间的地址空间映射关系、片选地址、控制位、状态位及其它杂项配置等。

上电时,PCI总线的RST信号有效,同时PCI9052输出局部复位信号LRESET,并检查NM93CS46是否有效。

若有效,且第一个16位字不是FFFFh,那么PCI9050将根据串行EEPROM的值来设置内部寄存器,否则采用默认值。

考虑到TMS320C6713HPI与PCI9052间的时序配合问题,通常在连线过程中,还必须注意下列几个问题:(1)由于PC机中数据与地址总线是复用的,所以PCI9052的MODE引脚应接地,而PCI9052中局部数据与地址总线是非复用的,所以TMS320C6713的HAS引脚应接高电平。

(2)由于TMS320C6713的HR/W信号与PCI9052的W/R信号极性相反,因此必须通过非门进行连接。

(3)由于TMS320C6713与PCI9052分别工作在不同的时钟频率下,所以TMS320C6713的HRDY信号输出必须通过D触发器的同步后才能送入逻辑电路,以供PCI9052的LRDY信号使用。

(4)LRDY信号的逻辑表达式为:LRDY=RD.WR+(CS1+ADS+HRDY),因此,只有RD或WR有效,且CS、ADS、HRDY也有效时,LRDY才能有效。

另外,要保证TMS320C6713HPI与PCI9052的稳定协调工作,除了要设计合理的硬件电路外 还必须对PCI9052的内部寄存器进行准确配置。

关于PCI9052内部寄存器的具体配置方法,可以参考PLX公司的用户手册,这里不再赘述。

笔者已将该方案应用于某电力系统精确故障定位及录波装置中。

其中,由TMS320C6713DSP芯片构成的高速数据采集卡用来控制电力系统中各电参数的采集、存储与故障判断。

当其HPI被设置为带地址自增的读方式时,可在一次故障记录结束后,由PC机将存储在TMS320C6713外扩SDRAM中的大量数据一次性读入。

读入的数据可用来计算故障发生的精确位置,分析系统中各电参数的变化情况,同时记录各继电保护装置的动作情况。