几种DSP与外接存储器的连接方法

俞斌贾雅琼

引言

存储器接口分为ROM接口和RAM接口两种。ROM包括EPROM和FLASH,而RAM 主要是指SRAM。TMS320C5409具有32K字的片内RAM和16K字的掩膜ROM。但是在DSP应用的很多场合,尤其是带信号存储的DSP应用来说,TMS320C5409的片内存储资源是远远不够用的。因此,设计一个TMS320C5409硬件系统一般应该包括其与EPROM/FLASH 和SRAM的接口设计,以存放程序和数据。本文介绍TMS320C5409与存储器的接口设计方案。

2 DSP与SRAM的接口设计

除了内部32k字RAM和16K字ROM之外,TMS320C5409还可以扩展外部存储器。其中,数据总空间总共为64k字(0000H~FFFFH),I/O空间为64K字(0000H~FFFFH),程序空间为8M。8M的程序空间的寻址是通过额外的7根地址线(A16~A22)实现的,由XPC 寄存器控制。根据程序和数据的空间配置,扩展的方法主要有3种。

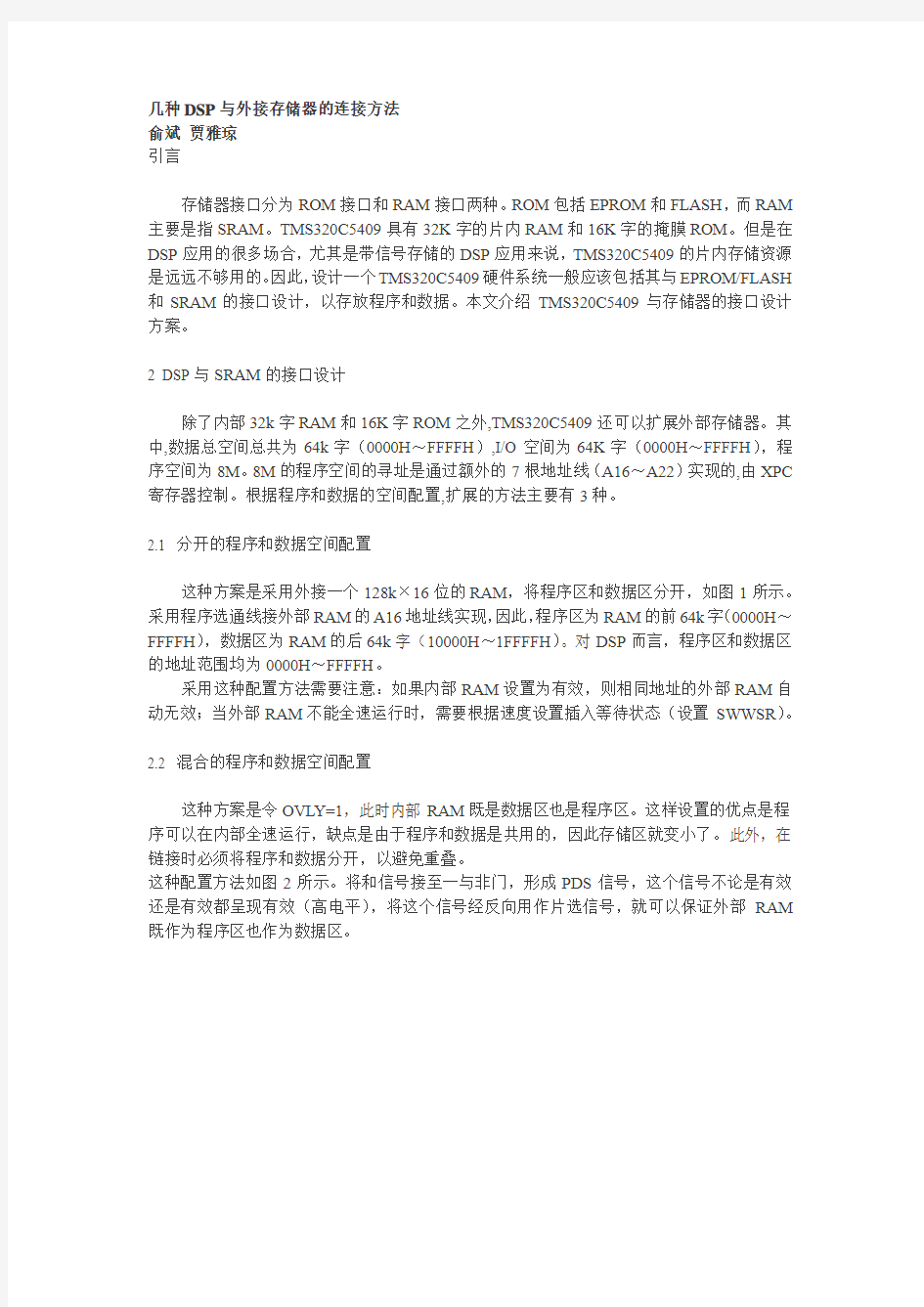

2.1 分开的程序和数据空间配置

这种方案是采用外接一个128k×16位的RAM,将程序区和数据区分开,如图1所示。采用程序选通线接外部RAM的A16地址线实现,因此,程序区为RAM的前64k字(0000H~FFFFH),数据区为RAM的后64k字(10000H~1FFFFH)。对DSP而言,程序区和数据区的地址范围均为0000H~FFFFH。

采用这种配置方法需要注意:如果内部RAM设置为有效,则相同地址的外部RAM自动无效;当外部RAM不能全速运行时,需要根据速度设置插入等待状态(设置SWWSR)。

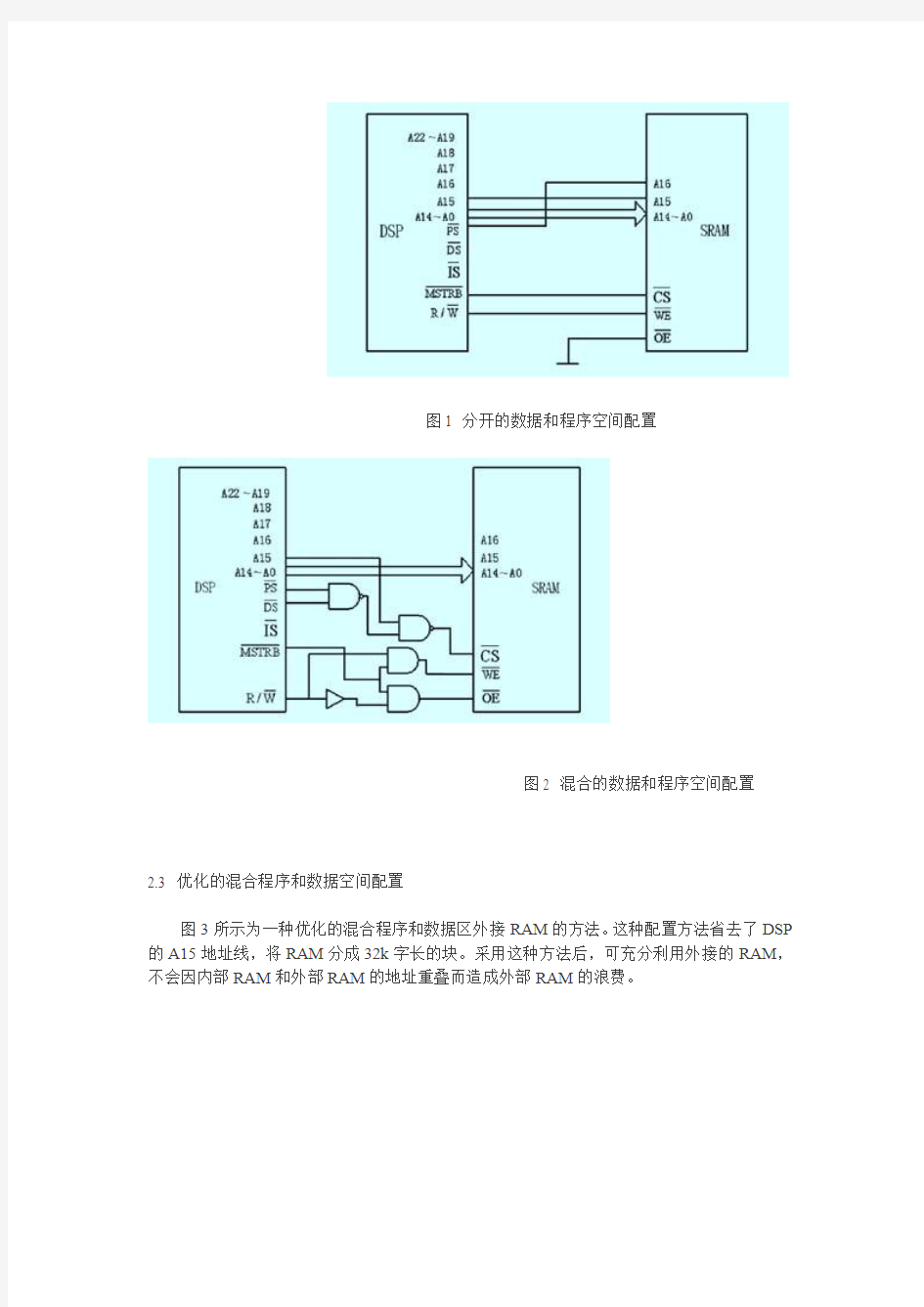

2.2 混合的程序和数据空间配置

这种方案是令OVL Y=1,此时内部RAM既是数据区也是程序区。这样设置的优点是程序可以在内部全速运行,缺点是由于程序和数据是共用的,因此存储区就变小了。此外,在链接时必须将程序和数据分开,以避免重叠。

这种配置方法如图2所示。将和信号接至一与非门,形成PDS信号,这个信号不论是有效还是有效都呈现有效(高电平),将这个信号经反向用作片选信号,就可以保证外部RAM 既作为程序区也作为数据区。

图1 分开的数据和程序空间配置

图2 混合的数据和程序空间配置

2.3 优化的混合程序和数据空间配置

图3所示为一种优化的混合程序和数据区外接RAM的方法。这种配置方法省去了DSP 的A15地址线,将RAM分成32k字长的块。采用这种方法后,可充分利用外接的RAM,不会因内部RAM和外部RAM的地址重叠而造成外部RAM的浪费。

图3 优化的混合数据和程序空间配置

由于外部扩展的空间很大,因此DSP程序区另外的地址空间也能访问到外部RAM。这种优化的外部RAM配置方法,使得在使用DSP的内部RAM的情况下,能够充分利用外部扩展RAM。

图4 DSP与FLASH的接口

3 DSP与FLASH的接口设计

图4为DSP与FLASH的一种接口配置。图中FLASH采用Silicon Storage 公司的新一代256K×16位CMOS FLASH Memory产品SST39VF400A作为DSP的外部数据存储器,

地址总线和数据总线接至DSP的外部总线,接至DSP的。DSP上的XF引脚用于启动编程。当XF为低时,FLASH处于读状态;当XF为高时,FLASH可擦或编程。为了满足SST39VF400A的时序要求,XF与相“或”后接至,引脚与相“或”后接至。

4 FLASH的擦写

4.1 片外FLASH擦写原理

在实际应用中,选择的片外存储器通常是片外的RAM或FLASH Memory。但是,由于RAM中数据掉电即丢失,不适合长期保存数据,因此当需要保存到片外存储器的是一些无需频繁读/写但需要长期保存的数据时,如字模数据、端口地址等,通常选择使用片外的FLASH扩展DSP芯片的存储器空间。但是,使用片外的FLASH必须要解决对其的擦写问题。

在实际应用中,对FLASH的擦写主要有两种方式:一是使用通用编程器对FLASH芯片进行擦写;二是直接由DSP对FLASH进行擦写。这里介绍一种利用存储器映射技术,通过对DSP芯片编程实现片外FLASH擦写的方法。

CCS5000 IDE是TI公司专为TMS320C5409设计的开发平台,该平台具有简单明了的图形用户界面和丰富的软件开发工具。利用GPIO0口可以生成合适的片外FLASH和片内RAM片选信号,从而实现片外FLASH和片内RAM访问的切换,在电路上可以将GPIO0信号与数据选择信号或程序选择信号相“或”实现。

4.2 片外FLASH擦写流程

编写FLASH擦写程序的流程图如图5所示。

图5 FLASH擦写程序流程图

(1)将character[180][32]设置为全局变量。

(2)将程序编译下载到DSP芯片中,打开工程目录中output文件夹中的.map文件,

找到character数组在RAM中存放的起始地址和长度。

(3)使用Save Memory命令将RAM中对应于character数组的地址段的数据以二进制形式保存在计算机上。

(4)打开FLASH擦写程序,修改数据在片内RAM中存储的起始地址和FLASH擦写的起始地址和数据长度,编译下载后,单步执行,直到擦写完FLASH,并将地址映射方式设置为映射到片内RAM处,数据便写到片外FLASH的相应地址中。

这一种通过地址映射方式的方法可适用于多种场合,针对多个FLASH芯片使用多个GPIO 端口进行地址的扩展,即可实现对其进行擦写操作;若将部分擦写程序放置到片外FLASH 中并作相应设置,即可实现系统得自举运行。

5 Bootload的设计

BootLoader是嵌入式系统加电后在操作系统内核运行之前运行的第一段代码。BootLoader用于初始化硬件设备、建立内存空间的映射图,从而将系统的软硬件环境带到一个合适的状态,以便为最终调用操作系统内核准备好正确的环境。通常,Boot Loader是严重地依赖于硬件而实现的,特别是在嵌入式世界。因此,在嵌入式世界里建立一个通用的Boot Loader几乎是不可能的。BootLoader一般它只在系统启动时非常短的时间内运行。对

于嵌入式系统来说,这是至关重要的一步。

TMS320C54x内部具有16K×16位的掩模ROM,其内部具有Bootloader程序,工作在微计算机方式下可以启动ROM中的引导程序,将用户程序从EPROM(FLASH)、串行口、I/O口或HPI口引导到内部RAM或外部的高速SRAM中全速运行。TMS320C5409硬件复位后采样引脚如果为低,则DSP从FF80H开始执行片内的引导程序,FF80H包含一条跳转到Bootloader程序的语句,Bootloader程序将用户程序下载到RAM中运行。在硬件复位期间,如果TMS320C5409的为高电平,则从片外的0FF80H开始执行程序。选择过程如图6所示。

图6 自举加载方式的选择过程

6 结束语

实践证明,在DSP的使用中,以上介绍的DSP与其外围存储器的接口设计是切实可行的。

第三章 DSP芯片开发工具的 特点及应用

§3.1 DSP开发环境 §3.2 通用目标文件格式COFF §3.3 编程工具特点及应用 §3.4 调试工具的特点及应用

XCHL

《DSP原理及应用》讲稿

1

宏源程序 文件

C语音 源文件 汇编语音 源文件

§3.1 DSP 开发环境

汇 编 语 音 开 发 流 程

归档器 宏文件库

C编译器 汇编语音 源文件 建库应 用程序 实时 支持库 Computer 调试工具

汇编器

归档器

COFF通用 目标文件

目标 文件库 十六进制 转换程序 EPROM中 的十六进制 代码程序 绝对 列表器

链接器 可执行的单个 COFF文件

交叉引用 TMS320C2XX 芯片 列表器 返回本章首页

2

XCHL

《DSP原理及应用》讲稿

§3.2 通用目标文件格式COFF

COFF文件格式是基于段(section)的概念建立的,即程序被分 解成各种段的组合体:如文本段、数据段等。这种文件格式便于 实现模块化程序设计,即程序员设计时只需基于代码段和数据段 等概念进行,不需关注每条命令或每个数据的具体目标地址。至 于它们的最终将处于存储器的哪个位置,将由链接器来安排。

? ? ? ? ? ?

段的概念及分类 段的创立 段的组合及其在存储器中的映象 程序重定位 COFF文件内的符号 COFF文件的装载

?

《DSP原理及应用》讲稿

返回本章首页

XCHL

3

第一章绪论 1.数字信号处理算法一般的实现方法有哪些?(详见课本 P2) 2.简述数字信号处理器的主要特点; 答:(1)存储器采用哈佛或者改进的哈佛结构;(2)内部采用了多级流水; (3)具有硬件乘法累加单元;(4)可以实现零开销循环;(5)采用了特殊的寻址方式;(6)高效的特殊指令;(7)具有丰富的片内外设。 3.举例请给出数字信号处理器的运算速度指标; 答:常见的运算速度指标有如下几种: (1)指令周期:执行一条指令所需的最短时间,数值等于主频的倒数;指令周期通常以ns(纳秒)为单位。例如,运行在200MHz的TMS320VC5510的指令周 期为5ns。 (2)MIPS:每秒百万条指令数。 (3)MAC时间:一次乘法累加操作花费的时间。大部分DSP芯片可在一个指令周期内完成MAC操作; (4)FFT执行时间:完成N点FFT所需的时间。FFT运算是数字信号处理中的典型算法而且应用很广,因此该指标常用于衡量DSP芯片的运算能力。 4. 简述哈佛结构的概念。 解:哈佛结构试验种将程序指令存储器和数据存储器分开的存储器结构。 哈佛机构是一种并行体系结构,它的主要特点是将程序和数据存储在不同的 存储空间中,即程序存储器和数据存储器是两个独立的存储器,每个存储器 独立编址,独立访问。 5. DSP与单片机,DSP与嵌入式处理器的主要区别是什么? 解:DSP运算能力强,擅长很多的重复数据运算,而MCU则适合不同信息 源的多种数据的处理诊断和运算,侧重于控制,速度并不如DSP。一般来说 MCU偏重于控制,DSP侧重于运算,MCU区别于DSP的最大特点在于它的通

用性,反应在指令集和寻址模式中。通常我们将的单片机和嵌入式芯片一般属于MCU,单片机8位和16位居多,ARM以32位居多。 6.TMS320C54x型DSP采用结构对程序存储器和数据存储器进行控制 7. DSP处理器按数据格式分为两类,分别是和 8. 从数据总线的宽度来说,TMS320C54x型DSP是位的DSP处理器 9.目前市场上DSP生产厂商位居榜首的是( D ) (5) A Motorola B ADI C Zilog D TI 第二章TMS320C54x的硬件结构 10. TMS320C54x DSP 芯片的存储器结构如何?(详见课本 P9) TMS320C54x 存储器由3 个独立的可选择空间组成:程序空间、数据空间和I/O 空间。程序存储器空间包括程序指令和程序中所需要的常数表格;数据存储器空间用于存储需要程序处理的数据或程序处理后的结果;I/O 空间用于与外部存储器映象的外设接口,也可以用于扩展外部数据存储空间。 C54x存储器空间通常可以分为3个可单独选择的空间: 64K程序空间、64K数据空间和64K I/O 空间。CPU状态寄存器的MP/MC、OVLY和 DROM位影响实际存储器的配置。 所有TMS320C54x 芯片都包括随机访问存储器(RAM)和只读存储器(ROM)。RAM可分成若干块,每一个块可以在一个机器周期内读两次或读一

三、TMS320C54X的指令系统 TMS320C5000指令系统TMS320C54x的指令集 TMS320C54x的指令集有近两百条指令,按功能分为如下几类: ?算术运算指令?逻辑运算指令?程序控制指令?装入和存储指令 一、算术运算指令 算术运算指令可分为如下几类: ?加法指令?减法指令?乘法指令?乘加指令?乘减指令?双数/双精度指令?特殊操作指令定点DSP中数据表示方法 当它表示一个整数时,其最低位(D0)表示1,D1位表示2的1次方,次高位(D14)表示2的14方。 如果表示一个有符号数时,最高位(D15)为符号位,0表示正数,1表示负数。例如,7FFFH 表示最大的正数32767(十进制),而0FFFFH表示最大的负数-1(负数用2的补码方式显示)。实现16位定点加法 ‘C54X中提供了多条用于加法的指令,如ADD,ADDC,ADDM和ADDS。其中ADDS用于无符号数的加法运算,ADDC用于带进位的加法运算(如32位扩展精度加法),而ADDM专用于长立即数的加法。 1、加法指令 使用ADD完成加法 LD temp1, A ;将变量temp1装入寄存器A ADD temp2, A ;将变量temp2与寄存器A相加 ;结果放入A中 STL A, temp3 ;将结果(低16位)存入变量 ;temp3中。 注意:这里完成计算temp3=temp1+temp2,我们没有特意考虑temp1和temp2是整数还是小数,在加法和下面的减法中整数运算和定点的小数运算都是一样的。

利用ADDS实现32位数据装入: LD #0,DP ; 设置数据页指针LD 60H,16,A ; 将60H的内容装到A的高16位ADDS 61H, A ;将61H的内容加到A的低16位DLD 60H,B ; 直接装入32位到B寄存器 2、减法指令 TMS320C54x汇编指令集:符号与缩写:

https://www.doczj.com/doc/e28652678.html,/news/html/70/show1598.htm 摘要:介绍美国Cygnal公司生产的C8051F02X系列单片机的外部存储器接口、I/O 端口配置方法和有关注意的问题;在此基础上列举两个关于EMIF、I/O的配置应用。 关键词:C8051F02X EMIF I/O 交叉开关 美国Cygnal公司C8051F02X系列单片机是集成在一起芯片上的混合信号系统级单片机。该单片机具有32/64位数字I/O端口(引脚)、25MIPS高速流水线式8051微控制器内核、64KB在系统可编程Flash存储器、64KB地址的外部存储器接口、4352(4096+256)B片内RAM、各自独立的SPI、SMBUS/I2C和两个UART串行接口等特点。其最突出的优点就是,通过设置交叉开关寄存器控制片内数字资源映射到外部I/O引脚,这就允许用户根据自己的特定应用,选择通用I/O端口和所需要数字资源。当然,在设置数字交叉开关寄存器时,应该首先考虑EMIF的配置问题。其配置不同,将导致单片机通过不同的端口(低或高)访问片外存储器和存储器映像的I/O部件,以及数字交叉开关是否分配外部设备给P0.7(WR)、P0.6(RD)、P0.5(ALE)引脚。(如图EMIF设置为多路器模式。) 1 EMIF和I/O配置方法 1.1 外部存储器接口(EMIF)配置 C8051F02X系列MCU有4KB的RAM可以只映射在片内,也可以映射在64KB外部数据存储器地址空间,还可以同时映射到片内和片外(4KB地址以内在片内存储器空间访问,4KB以上经过EMIF访问)三种方式。对于后两种存储器工作模式,需通过外部存储器接口使用MOVX和DPTR或MOVX和R0(R1)指令访问外部数据存储器和存储器映像的I/O设备。但是对于高8位地址,必须由外部存储器接口寄存器(EMI0CN)提供;而EMIF可将外部数据存储器接口映射到低端口(P0~P3)(F020/2/3系列)或高端口(P4~P7)(F020/2系列),以及配置为复用模式或非复用模式等。配置外部存储器接口的步骤下: *设置EMIF为低端口或高端口; *设置EMIF为复用模式或非复用模式;

第6章 DSP片内外设 教学提示:TMS320C54x DSP的片内外设是集成在芯片内部的外部设备。本章将以C5402 DSP为主详细介绍其可编程定时器、串行口、主机接口、通用I/O以及软件等待状态发生器和分区转换逻辑。 教学要求:掌握可编程定时器、标准同步串行口、标准8位主机接口、通用I/O的特点和操作过程,能够应用。了解多通道缓冲串口(McBSP)、8位增强主机接口HPI-8、软件等待状态发生器和分区转换逻辑。 6.1 DSP片内外设概述 TMS320C54x DSP的片内外设是集成在芯片内部的外部设备。CPU核对片内外设的访问是通过对相应的控制寄存器的访问来完成的。外部设备集成在芯片内部主要有以下优点: (1) 片内外设访问速度快。因为片外外设必须通过与程序、数据总线共用的外部总线来访问,访问速度慢,而片内外设的访问或操作速度大大快于外部I/O空间中的片外外设。 (2) 可以简化电路板的设计。如将A/D转换、D/A转换、定时器集成在片内。 (3) 提供一些必须的特殊功能。这些特殊功能必须以片内外设的方式来实现,如JTAG 口、等待状态发生器等。 TI公司将相关的片内外设分为两大类:片内外设和增强型片内外设。其中片内外设主要包括串行接口、定时器、通用I/O引脚和标准主机接口(HPI8)。增强型外设主要包括多通道缓冲串口(McBSP)、主机接口(8位增强HPI-8、16位增强HPI-16)、DMA控制器。 所有的C54x DSP的CPU结构及功能完全相同,但是片内的外设配置多少不同。任何一款C54x DSP拥有的片内外设都只是以上列举的片内外设的一部分。 片内外设的操作是通过相关的控制寄存器来实现的,寄存器被映射到数据存储空间的第0页(地址20h~5Fh)。具体的映射关系如表6-1所示。 表6-1 C5402外设存储器映像寄存器 地址(十六进制) 名称描述 McBSP0数据接收寄存器2 20 DRR20 McBSP0数据接收寄存器1 21 DRR10 McBSP0数据发送寄存器2 22 DXR20 McBSP0数据发送寄存器1 23 DXR10 定时器0寄存器 24 TIM 定时器0周期计数器 25 PRD

第一章 1.简述典型实时数字信号处理系统组成部分。 答:包括:抗混叠滤波器(Anti-aliasing filter)、模数转换器ADC(Analog-to-Digital Converter)、数字信号处理、数模转换器DAC(Digital-to-Analog Converter)和抗镜像滤波器(Anti-image filter) 。 2.简述X86处理器完成实时数字信号处理的优缺点。 答:利用X86处理器完成实时数字信号处理。特点是处理器选择范围宽,主板及外设资源丰富,有多种操作系统可供选择,开发、调试较为方便;缺点是数字信号处理能力不强,硬件组成较为复杂,系统体积、重量较大,功耗较高,抗环境影响能力较弱。 3.简述数字信号处理器的主要特点。 答:(1)存储器采用哈佛或者改进的哈佛结构;(2)内部采用了多级流水;(3)具有硬件乘法累加单元;(4)可以实现零开销循环;(5)采用了特殊的寻址方式;(6)高效的特殊指令;(7)具有丰富的片内外设。 4.给出存储器的两种主要结构,并分析其区别。 答:存储器结构分为两大类:冯·诺依曼结构和哈佛结构。冯·诺依曼结构的特点是只有一个存储器空间、一套地址总线和一套数据总线;指令、数据都存放在这个存储器空间中,统一分配地址,所以处理器必须分时访问程序和数据空间。哈佛结构程序存储器空间和数据存储器空间分开,具有多套地址、数据总线,哈佛结构是并行体系结构,程序和数据存于不同的存储器空间,每个存储器空间独立编址、独立访问。 5.简述选择数字信号处理器所需要考虑的因素。 答:应考虑运算速度、算法格式和数据宽度、存储器类型、功耗和开发工具。 6.给出数字信号处理器的运算速度指标,并给出其具体含义。 答:常见的运算速度指标有如下几种: (1)指令周期:执行一条指令所需的最短时间,数值等于主频的倒数;指令周期通常以ns(纳秒)为单位。例如,运行在200MHz的TMS320VC5510的指令周期为 5ns。 (2)MIPS:每秒百万条指令数。 (3)MOPS:每秒百万次操作数。 (4)MFLOPS:每秒百万次浮点操作数。 (5)BOPS:每秒十亿次操作数。 (6)MAC时间:一次乘法累加操作花费的时间。大部分DSP芯片可在一个指令周期内完成MAC操作; (7)FFT执行时间:完成N点FFT所需的时间。FFT运算是数字信号处理中的典型算法而且应用很广,因此该指标常用于衡量DSP芯片的运算能力。

DSP原理及应用实验报告 片上外设实验 1——GPIO控制实验 姓名学号 一、实验目的 1.了解GPIO片上外设; 2.掌握延时程序应用; 3.用GPIO口实现LED指示灯控制。 二、实验设备及地点 设备:SEED-DTK系列DSP实验箱 地点: 三、实验原理 1.实验的原理性说明 通用目的输入输出(GPIO)片内外设提供了专用的通用目的引脚,可以配置位输入或输出。当配置为一个输出时,用户可以写一个内部寄存器以控制输出引脚上驱动的状态。当配置为输入引脚时,用户可以通过内部寄存器的状态检测到输入的状态。另外,GPIO 片内外设可以用不同的中断/事件产生 CPU 中断和 EDMA 事件。 一旦在 GPIO 使能寄存器(GPEN)被使能,GPIO 引脚可以用作通用目的输入/输出。 用户可以使用 GPIO 方向寄存器(GPDIR)独立配置每条

GPIO 引脚为输入或输出。当配置为输出(GPXDIR 位=1),GPIO 值寄存器(GPVAL)的 GPXVAL 位的值就被送到相应的 GPn 引脚。当配置为输入(GPXDIR 位=0)时,输入状态可以从相应的 GPXVAL 读取TMS320VC5502 有 1-位通用输出引脚XF和8-位通用I/O 引脚 GPIO[7:0],其中GPIO3、GPIO5与McBSP2 复用引脚。SEED-DEC5502模板上这些引脚的使用情况如下XF 用于点亮 LED 指示灯D1。XF = 1,点亮;XF = 0,熄灭。 GPIO[2:0]:经电平转换后连至外设扩展总线的备用引脚。 GPIO3:与McBSP2的CLKX2复用引脚,当配置为GPIO3时,用作COM1的。 GPIO4:经电平转换后连至外设扩展总线的备用引脚。 GPIO5:与McBSP的FSX2复用引脚,当配置为GPIO5时,用作COM1的。 GPIO6:经电平转换后连至外设扩展总线的备用引脚。 GPIO7:用于点亮 LED 指示灯 D5。XF = 1,点亮;XF = 0,熄灭。 程序流程图如下:

第二章 3、处理器工作方式状态寄存器PMST 中的MP/MC、OVLY 和DROM 三个状态位对C54x的存储空间结构各有何影响? 当OVLY= 0 时,程序存储空间不使用内部RAM。当OVLY= 1 时,程序存储空间使用内部RAM。内部RAM 同时被映射到程序存储空间和数据存储空间。当MP/ MC=0 时,4000H~EFFFH 程序存储空间定义为外部存储器;F000H~FEFFH 程序存储空间定义为内部ROM;当MP/ MC=1 时,4000H~FFFFH 程序存储空间定义为外部存储。DROM=0:0000H~3FFFH——内部RAM ;4000H~FFFFH——外部存储器;DROM=1 : 0000H~3FFFH——内部RAM;4000H~EFFFH——外部存储器;F000H~FEFFH——片内ROM;FF00H~FFFFH——保留。 4 、TMS320C54x 芯片的片内外设主要包括哪些电路? ①通用I/O 引脚②定时器③时钟发生器④主机接口HPI⑤串行通信接口⑥软件可编程等待状态发生器⑦可编程分区转换逻辑 5、TMS320C54x 芯片的流水线操作共有多少个操作阶段?每个阶段执行什么任务?完成一条指令都需要哪些操作周期? 六个操作阶段:①预取指P;将PC 中的内容加载PAB ②取指F; 将读取到的指令字加载PB③译码D; 若需要,数据 1 读地址加载DAB;若需要,数据2 读地址加载CAB;修正辅助寄存器和堆栈指针④寻址A; 数据 1 加载DB;数据 2 加载CB;若需要,数据3 写地址加载EAB⑤读数R; 数据1 加载DB;数据2 加载CB;若需要,数据3 写地址加载EAB;⑥执行X。执行指令,写数据加载EB。 6、TMS320C54x 芯片的流水线冲突是怎样产生的?有哪些方法可以避免流水线冲突?答:’C54x 的流水线结构,允许多条指令同时利用CPU 的内部资源。由于CPU 的资源有限,当多于一个流水线上的指令同时访问同一资源时,可能产生时序冲突。解决办法①由CPU 通过延时自动解决;②通过程序解决,如重新安排指令或插入空操作指令。为了避免流水冲突,可以根据等待周期表来选择插入的NOP 指令的数量。 7、TMS320C54x 芯片的串行口有哪几种类型? 四种串行口:标准同步串行口SP,缓冲同步串行口BSP,时分多路串行口TDM,多路缓冲串行口McBSP。 8 、TMS320VC5402 共有多少可屏蔽中断?它们分别是什么?NMI 和RS 属于哪一类中断源?答:TMS320VC5402 有13 个可屏蔽中断,RS 和NMI 属于外部硬件中断。 9、试分析下列程序的流水线冲突,画出流水线操作图。如何解决流水冲突? STLM A,AR0 STM #10,AR1 LD *AR1,B 解:流水线图如下图: 解决流水线冲突:最后一条指令(LD *AR1,B)将会产生流水线冲突,在它前面加入一条NOP 指令可以解决流水线冲突。 10、试根据等待周期表,确定下列程序段需要插入几个NOP 指令。 ①LD @GAIN, T STM #input,AR1 MPY *AR1+,A 解:本段程序不需要插入NOP 指令 ②STLM B,AR2 STM #input ,AR3 MPY *AR2+,*AR3+,A 解:本段程序需要在MPY *AR2+,*AR3+,A 语句前插入1条NOP 指令

一、填空题 第一章 1.数字信号处理特点大量的实时计算(FIR IIR FFT),数据具有高度重复(乘积和操作在滤波、卷积和FFT中等常见)。 2.信号处理的作用信号改善;信号检测、估计等 3.信号处理的方法信号波形分析/变换、滤波、现代谱估计/分析、自适应滤波等。 4.信息系统包括采集、传输、处理、等。5.数字信号处理常用算法有FIR 滤波、IIR 滤波、离散傅里叶变换、卷积、离散余弦变换等 6.处理器速度的提高得益于器件水平、处理器结构、并行技术等。7.DSP结构特点包括采用哈佛结构体系、采用流水线技术、硬件乘法器、多处理单元、特殊的DSP指令。 8.DSP芯片按用途分为通用型DSP 、专用型DSP 。9.DSP芯片按数据格式分为浮点型、定点型。 第二章 1.C28x芯片具有C27X、C28X、C2XLP操作模式。2.C28x芯片模式选择由ST1中的AMODE和OBJMODE位组合来选定模式。 3.CPU内核由CPU、仿真逻辑、接口组成。 4.CPU主要特性是保护流水线、独立寄存器空间算术逻辑单元(ALU)、地址寄存器算术单元(ARAU)、循环移位器乘法器。 5.CPU信号包括存储器接口信号、时钟和控制信号、复位和中断信号、仿真信号。 6.TMS320F2812组成特点是32位、定点、改进哈佛结构、循环的寻址方式。7.存储器接口有3组地址总线。 8.存储器接口有3组数据总线。 9.存储器接口地址总线有PAB、DRAB、DWAB、 10.CPU中断控制寄存器有IFR 、IER 、DBGIER。 11.ACC累加器是32位的,可表示为ACC、AH、AL。12.被乘数寄存器是32 位的,可表示为XT、T、TL 。13.乘数结果寄存器是32位的,可表示为P 、PH、PL。14.数据页指针寄存器16 位的,有65536 页,每页有64个存储单元。数据存储空间容量是4M字。 15.堆栈指针复位后SP指向地址是0x000400h 。 第三章 1.DSP芯片内部包含存储器类型有片内双访问存储器(DARAM)、片内单访问程序/数据RAM(SARAM)、掩膜型片内ROM存储器、闪速存储器(Flash)一次性可编程存储器(OTP)。 2.C28x具有32 位的数据地址和22位的程序地址,总地址空间可达4G字(每个字16位)的数据空间和4M字的程序空间。 3.在程序地址中保留了64个地址作为CPU的32个中断向量。

TMS320LF2407片内外设寄存器2 描述和说明:LF2407片内外设寄存器定义 ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ 片内外围寄存器定义 ******************************************************************************* ******************************************************************************* ABRPT 0x01f---分析断点

PIACKR0 0x7014---外设中断应答寄存器0 PIACKR1 0x7015---外设中断应答寄存器1

******************************************************************************* *******************************************************************************

******************************************************************************* ---外围串行接口(SPI寄存器) SPIPC1 0x704D---SPI端口控制寄存器1

几种DSP与外接存储器的连接方法 俞斌贾雅琼 引言 存储器接口分为ROM接口和RAM接口两种。ROM包括EPROM和FLASH,而RAM主要是指SRAM。TMS320C5409具有32K字的片内RAM和16K字的掩膜ROM。但是在DSP 应用的很多场合,尤其是带信号存储的DSP应用来说,TMS320C5409的片内存储资源是远远不够用的。因此,设计一个TMS320C5409硬件系统一般应该包括其与EPROM/FLASH和SRAM的接口设计,以存放程序和数据。本文介绍TMS320C5409与存储器的接口设计方案。 2 DSP与SRAM的接口设计 除了内部32k字RAM和16K字ROM之外,TMS320C5409还可以扩展外部存储器。其中,数据总空间总共为64k字(0000H~FFFFH),I/O空间为64K字(0000H~FFFFH),程序空间为8M。8M的程序空间的寻址是通过额外的7根地址线(A16~A22)实现的,由XPC寄存器控制。根据程序和数据的空间配置,扩展的方法主要有3种。 2.1 分开的程序和数据空间配置 这种方案是采用外接一个128k×16位的RAM,将程序区和数据区分开,如图1所示。采用程序选通线接外部RAM的A16地址线实现,因此,程序区为RAM的前64k字(0000H~FFFFH),数据区为RAM的后64k字(10000H~1FFFFH)。对DSP而言,程序区和数据区的地址范围均为0000H~FFFFH。 采用这种配置方法需要注意:如果内部RAM设置为有效,则相同地址的外部RAM自动无效;当外部RAM不能全速运行时,需要根据速度设置插入等待状态(设置SWWSR)。 2.2 混合的程序和数据空间配置 这种方案是令OVLY=1,此时内部RAM既是数据区也是程序区。这样设置的优点是程序可以在内部全速运行,缺点是由于程序和数据是共用的,因此存储区就变小了。此外,在链接时必须将程序和数据分开,以避免重叠。 这种配置方法如图2所示。将和信号接至一与非门,形成PDS信号,这个信号不论是有效还

CME-M5 外部存储器接口(EMIF)总线使用指南 一、EMIF 总线概述 外部存储器总线(EMIF, External Memory Interface)总线是京微雅格(CME) 的8051 硬核与FPGA 之间的并行8 位总线接口,主要的信号有6 个,分别为: memaddr[22:0]:23 位地址总线,对应8M 地址空间; memdatao[7:0]:8 位数据输出总线; memdatai[7:0]:8 位数据输入总线; memrd:总线读信号; memwr:总线写信号; memack:总线应答信号;与EMIF 操作时序有关的8051 的内部寄存器为CKCON 寄存器,一般8051 的初始化程序需 要在主函数的初始化更改该寄存器的初始化值,以实现最快的总线访问效率。 1. EMIF 总线相关的MCU 寄存器:CKCON CKCON 主要作用是设置存储器地址总线memaddr[22:0]和读写memwr/ memerd 信号的宽度,已实现对不同外设时序的操作,若宽度仍不够,也可以 通过memack 实现硬件延时,理论上可以实现任意宽度的地址总线地址和读写 信号。 CKCON 寄存器的默认值为:0x71 通过设置CKCON 的第4-6 位,可以改变CPU 的运行效率,最小值 是001,不可设置为000;当设置为111,运行的效率最慢;所以推荐客户在CPU 开始运行就改变4-6 位的值为001,以使CPU 运行的效率最快。 通过设置CKCON 的第0-2 位,可以改变EMIF 总线的 memrd,memwr,memaddr 的宽度,最小值是000,对应memrd,memwr,memaddr 的宽度为1 个时钟周期;当设置为111 时,对应memrd,memwr,memaddr 的宽度为8 个时钟周期;所以推荐客户在CPU 开始运行就改变4-6 位的值为000,以使

D S P原理及应用课后 习题答案

简述DSP芯片的主要特点 哈佛结构----将程序和数据存储在不同的存储空间中,即程序存储器和数据存储器是两个相互独立的存储器,每个存储器独立编址,独立访问。 多总线结构---保证在一个机器周期内可以多次访问程序存储空间和数据存储空间。 指令系统的流水线操作--减少指令执行时间,增强处理器的处理能力。取址,译码,取操作和执行四个阶段。 专用的硬件乘法器--使乘法累加运算能在单个周期内完成。 特殊的DSP指令、快速的指令周期、硬件配置强。 详细描述冯诺依曼结构和哈佛结构,并比较不同? 冯诺依曼结构--数据和程序共用总线和存储空间,在某一时刻,只能读写程序或者读写数据。将指令、数据、地址存储在同一个存储器统一编址,依靠指令计数器提供的地址来区分是指令‘数据还是地址,取指令和取操作数都访问同一存储器,数据吞吐率低。 哈佛结构----将程序和数据存储在不同的存储空间中,即程序存储器和数据存储器是两个相互独立的存储器,每个存储器独立编址,独立访问。改进的还允许在程序存储空间和数据存储空间之间相互传送数据。 DSP系统的设计过程? 确定DSP系统设计的性能指标;进行算法优化与模拟;选择DSP芯片和外围芯片;进行硬件电路的设计;进行软件设计;进行软硬件综合调试。 请描述TMS320C54x的总线结构? C54X采用先进的哈佛结构并具有八组总线, 其独立的程序总线和数据总线允许同时读取指令和操作数,实现高度的并行操作。程序总线PB传送从程序存储器来的指令代码和立即数。 3组数据总线连接各种元器件。CB和DB总线传送从数据存储器读出的操作数,EB总线传送写入到存储器中的数据。(1分) 4组地址总线PAB\CAB\DAB\EAB传送执行指令所需的地址。 TMS320C54x片内存储器一般包括哪些种类?如何配置片内存储器? C54X片内存储器一般包括两种类型:ROM(只读存储器),RAM(随机访问存储器)。RAM又可分为双访问DARAM和单访问SARAM。 简述TMS320C54X芯片的CPU各组成部分及其功能。 CPU状态和控制寄存器:用于设置各种工作条件和工作方式的状态以及存储器配置状态和控制信息。 40位算术逻辑单元、40位累加器A和B:两者共同完成算术运算和逻辑运算。 桶形移位寄存器:使处理器能完成数字定标,位提取,对累加器进行归一化处理等操作。 乘法器/加法器单元:在单周期内完成一次乘法累加运算。 比较选择和存储单元:是专门为Viterbi算法设计的加法,比较,选择操作的硬件单元。 指数编码器:用于支持单周期指令EXP的专用硬件。 TMS320C54x存储器包括哪几个空间? 64k程序存储空间:程序指令和程序中所需的常数表格 64k数据存储空间:存储需要程序处理的数据或程序处理后的结果 64kI/O存储空间:存储与外部存储器映像的外设接口 TMS320C54x有几种状态和控制寄存器?它们的功能?

第一章绪论 1、简述DSP系统的构成和工作过程。 答:DSP系统的构成: 一个典型的DSP系统应包括抗混叠滤波器、数据采集A/D转换器、数字信号处理器DSP、D/A转换器和低通滤波器等。 DSP系统的工作过程: ①将输入信号x(t)经过抗混叠滤波,滤掉高于折叠频率的分量,以防止信号频谱的混叠。 ②经过采样和A/D转换器,将滤波后的信号转换为数字信号x(n)。 ③数字信号处理器对x(n)进行处理,得数字信号y(n)。 ④经D/A转换器,将y(n)转换成模拟信号; ⑤经低通滤波器,滤除高频分量,得到平滑的模拟信号y(t)。 9、简述DSP系统的设计步骤。 答:①明确设计任务,确定设计目标。 ②算法模拟,确定性能指令。 ③选择DSP芯片和外围芯片。 ④设计实时的DSP芯片系统。 ⑤硬件和软件调试。 ⑥系统集成和测试。 第二章TMS320C54x硬件结构 1、TMS320C54X芯片的基本结构都包括哪些部分? 答:①中央处理器 ②内部总线结构 ③特殊功能寄存器 ④数据存储器RAM ⑤程序存储器ROM ⑥I/O口 ⑦串行口 ⑧主机接口HPI ⑨定时器 ⑩中断系统 2、TMS320C54X芯片的CPU主要由哪几部分组成? 答:①40位的算术运算逻辑单元(ALU)。 ②2个40位的累加器(ACCA、ACCB)。 ③1 个运行-16至31位的桶形移位寄存器。 ④17×17位的乘法器和40位加法器构成的乘法器-加法器单元(MAC)。 ⑤比较、选择、存储单元(CSSU)。 ⑥指令编码器。 ⑦CPU状态和控制寄存器。 3、TMS320VC5402共有多少可屏蔽中断?它们分别是什么?RS和N M I属于哪一类中断源? 答:TMS320VC5402有13个可屏蔽中断,RS和N M I属于外部硬件中断。 4、试分析下列程序的流水线冲突,画出流水线操作图。如何解决流水冲突? STLM A,AR0 STM #10,AR1 LD *AR1,B 解:流水线图如下图: 1 2 3 4 5 6 7 8 9 预取指取指译码寻址读数执行 STLM A,AR0 写AR1 预取指取指译码寻址读数执行