LAR AR1,#0FH RPT 14 NORM *-上述程序执行后,AR1=#0eH,

ACCH=2000(10进制。对一个16位整数 x 进行上述程序处理实际上就是做这样一个等效变换: x ? 2Q 15?Q x= ?2 32768 其中,寄存器 AR1 包含的值为 15-Q ,累加器 ACC 高 16 位包含的值为 x ? 2 Q ,其数值在 16384~32768之间。例3.15 实现以2为底的对数的C定点模拟程序 int logtab0[10]={-32768,-28262,-24149,-20365,-16862, -13600,-10549,-7683,-4981,-2425}; /*Q15*/ int logtab1[10]={22529,20567,18920,17517,16308, 15255,14330,13511,12780,12124}; /*Q13*/ int logtab2[10]={16384,18022,19660,21299,22938, 24576,26214,27853,29491,31130};

/*Q15*/ int log2_fast(int Am { int point,point1; int index,x0,dx,dy,y; point=0;

while(Am<16384 {point++;Am=Am<<1;} /*对Am进行规格化*/ /*输入为Q4,输出为Q9*/ point1=(15-point-4*512; /*求查表地址*/ index=((Am-16384*20L>>15; dx =Am-logtab2[index]; dy=((longdx*logtab1[index]>>13; /*Q9*/ y=

(dy+logtab0[index]>>6; y=point1+y; return (y; } 上述程序中,输入值Am采用Q4表示,输出采用Q9表示,如果输入输出的Q值与上面程序中的不同,则应做相应的修改。 3.5 小结本章讨论了 DSP 芯片进行定点运算所涉及的一些基本问题,这些问题包括:数的定标,DSP程序的定点模拟,DSP芯片的定点运算以及定点实现非线性函数的快速实现方法等。充分理解这些问题对于用定点芯片实现DSP算法具有非常重要的作用。 ·52·

数字信号处理第三章实验程序 3.1计算离散时间傅里叶变换 % Program P3_1 % Evaluation of the DTFT clf; % Compute the frequency samples of the DTFT w = -4*pi:8*pi/511:4*pi; num = [2 1];den = [1 -0.6]; h = freqz(num, den, w); % Plot the DTFT subplot(2,1,1) plot(w/pi,real(h));grid title('Real part of H(e^{j\omega})') xlabel('\omega /\pi'); ylabel('Amplitude'); subplot(2,1,2) plot(w/pi,imag(h));grid title('Imaginary part of H(e^{j\omega})') xlabel('\omega /\pi'); ylabel('Amplitude'); pause subplot(2,1,1) plot(w/pi,abs(h));grid title('Magnitude Spectrum |H(e^{j\omega})|') xlabel('\omega /\pi'); ylabel('Amplitude'); subplot(2,1,2) plot(w/pi,angle(h));grid title('Phase Spectrum arg[H(e^{j\omega})]') xlabel('\omega /\pi'); ylabel('Phase in radians'); Q3.1离散时间傅里叶变换的原始序列是H(e^jw)=(2+z^-1)/(1-0.6z^-1)。Pause的作用是暂停等待用户输入任意键后接着执行以下命令。 Q3.2

定点与浮点运算DSP 的比较 DSP数字信号处理器是一种特别适合于进行数字信号处理的微处理器,主要用于实时快速地实现各种数字信号处理算法。定点运算DSP 在应用中已取得了极大的成功,而且仍然是DSP 应用的主体。然而,随着对DSP 处理速度与精度、存储器容量、编程的灵活性和方便性要求的不断提高、自80 年代中后期以来,各DSP 生产厂家陆续推出了各自的32bit浮点运算DSP。 和定点运算DSP 相比,浮点运算DSP 具有许多优越性:浮点运算DSP 比定点运算DSP 的动态范围要大很多。 定点DSP 的字长每增加1bit,动态范围扩大6dB。16bit 字长的动态范围为96dB。程序员必须时刻关注溢出的发生。例如,在作图像处理时,图像作旋转、移动等,就很容易产生溢出。这时,要么不断地移位定标,要么作截尾。前者要耗费大量的程序空间和执行时间,后者则很快带来图像质量的劣化。总之,是使整个系统的性能下降。在处理低信噪比信号的场合,例如进行语音识别、雷达和声纳信号处理时,也会发生类似的问题。 32bit 浮点运算DSP 的动态范围可以作到1536dB,这不仅大大扩大了动态范围,提高了运算精度,还大大节省了运算时间和存储空间,因为大大减少了定标,移位和溢出检查。 由于浮点DSP 的浮点运算用硬件来实现,可以在单周期内完成,因而其处理速度大大高于定点DSP。这一优点在实现高精度复杂算法时尤为突出,为复杂算法的实时处理提供了保证。 32bit 浮点DSP 的总线宽度较定点DSP 宽得多,因而寻址空间也要大得多。这一方面为大型复杂算法提供了可能、因为省的DSP 目标子程序已使用到几十MB 存储器或更多;另一方面也为高级语言编译器、DSP 操作系统等高级工具软件的应用提供了条件。 DSP 的进一步发展,必然是多处理器的应用。新型的浮点DSP 已开始在通信口的设置和强化、资源共享等方面有所响应。 TMS320C6000家族为高性能DSP,包括: TMS320C62X定点DSP系列、TMS320C64X定点DSP系列、TMS320C67X定点DSP系列。 TMS320C62X系列 工作频率:150-300MHz,运行速度:1200-2400MIPS,内部2个乘法器、6个算术逻辑单元,超长指令字(VLIW)结构,大容量的片内存储器和大范围的寻址能力,4个DMA接口,2个多通道缓存串口,2个32位片内外设。 TMS320C64X系列 工作频率:400-600MHz,运行速度:3200-4800MIPS,具有特殊功能的指令集。 TMS320C67X系列,为高性能浮点DSP 工作频率:100-225MHz,运行速度:600-1350MIPS,具有4个浮点/定点算术逻辑单元,2个定点算术逻辑单元,2个浮点/定点乘法器。

DSP芯片的定点运算---Q格式(转) 2008-09-03 15:47 DSP芯片的定点运算 1.数据的溢出: 1>溢出分类: 上溢(overflow): 下溢(underflow) 2>溢出的结果: Max Min 上溢在圆圈上按数据逆时针移动;下溢在圆圈上顺时钟移动。 例:signed int :32767+1=-32768;-32768-1=32767 unsigned char:255+1=0;0-1=255 3>为了避免溢出的发生,一般在DSP中可以设置溢出保护功能。当发生溢出时,自动将结果设置为最大值或最小值。 2.定点处理器对浮点数的处理: 1>定义变量为浮点型(float,double),用C语言抹平定点处理器和浮点处理器 的区别,但是程序的代码庞大,运算速度也慢。 2>放大若干倍表示小数。比如要表示精度为0.01的变量,放大100倍去运算, 运算完成后再转化。但是这个做法比较僵硬,如要将上面的变量重新定义成 0.001精度,又需要放大1000倍,且要重新编写整个程序,考虑溢出等问题。 3>定标法:Q格式:通过假定小数点位于哪一位的右侧,从而确定小数的精度。 Q0:小数点在第0位的后面,即我们一般采用的方法 Q15 小数点在第15位的后面,0~14位都是小数位。 转化公式:Q=(int)(F×pow(2,q)) F=(float)(Q×pow(2,-q)) 3.Q格式的运算 1>定点加减法:须转换成相同的Q格式才能加减 2>定点乘法:不同Q格式的数据相乘,相当于Q值相加 3>定点除法:不同Q格式的数据相除,相当于Q值相减 4>定点左移:左移相当于Q值增加 5>定点右移:右移相当于Q减少 4.Q格式的应用格式 实际应用中,浮点运算大都时候都是既有整数部分,也有小数部分的。所以要选择 一个适当的定标格式才能更好的处理运算。一般用如下两种方法: 1>使用时使用适中的定标,既可以表示一定的整数复位也可以表示小数复位,如 对于2812的32位系统,使用Q15格式,可表示-65536.0~65535.999969482 区间内的数据。

实验一 CCS使用及DSP 基本数学运算 一、实验目的: 1、熟悉CCS 集成开发环境,掌握工程的生成方法; 2、熟悉SEED-DTK5416实验环境; 3、掌握CCS 集成开发环境的调试方法; 4、了解数在计算过程中的定标,掌握数的定点、浮点表示方法,定点、浮点基本运算以及定点、浮点间的相互转换。 二、实验内容: 1、 DSP源文件的建立; 2、 DSP程序工程文件的建立; 3、编译与链接的设置,生成可执行的DSP 文件; 4、进行DSP 程序的调试与改错; 5、学习使用CCS 集成开发工具的调试工具; 6、观察实验结果; 三、实验知识背景: 在DSP 编程过程中,数以二进制、十进制、与十六制表示均可。在定点DSP 的运算过程中,数一般采用二进制与二进制补码的形式进行运算的。其中二进制数只能代表正数不能代表负的数,而二进制补码记数系统弥补了这一缺点。它的构成如下; 在二进制的基础上,加一符号位。符号位位于二进制数的最高位

当为正数时,符号位为0,为负数时,符号位为1 当采用二进制补码进行数的运算时,具有如下的两个优点: 可以将加法与减法统一成加法运算 符号位可以进行扩展,而其数值不变,这可以使一个比较小的数存放到比较大的寄存器当中 例: 1×2 + 0×1 = -2 (11110)2 = 1×(-16)+ 1×8 + …… + 当将其符号位扩展三位,放入一8位的寄存器中 1×2 + 0×1 = -2 (11111110)2 = 1×(-128)+ 1×64 + …… + 这将为运算提供极大的方便,因而在定点的DSP 中,大多数情况采用二进制补码形式。 C5000系列的DSP 硬件只支持定点运算,浮点运算要通过软件来实现。其运算字长为16位,也就是说,DSP 所能表示的整数的范围也就决定了,其范围为-32768到32767。而在很多情况下,数学运算过程中不一定是整数,而且动态范围也不是固定不变的。如何解决这个问题?对于只支持定点运算的CPU 来说,在硬件上并没有提供小数点定位的机制。只有靠软件中人为地假设将小数点放在16位数据中的不同位置,就可以表示不同大小与不同精度的数据了,这就是数的定标。 数的定标有Q 与S 两种表示方法。在Q 表示法中,Q 代表(Quantity of Fractional Bits)数中尾数部分的位数,即小数点右边的位数。而S 表示法中,S 代表数中整数部分的位数,即小数点左边的位数。实用中一般用Q 表示法,例:Q 0表示小数点在第0位的右边,即为整数。Q 15表数小数点在第15位的右边,即为小于1的小数(以二进制补码表示,第15位为符号位)。下表给出了16位数的16种不同的Q 表示法。并列出了它们所能表示的十进

第三章习题答案 3.1 (1)非周期 (2)N=1 (3)N=10 (4)N=4 (5)N=20 3.2 02s f f ωπ =,1s s f T = (1)0153,2f ωπ== ;0.3s T =,05 f π = (2)010,25f ωπ==;0.3s T =,050 3 f = (3)0,0.55f πω==;0.3s T =,01 3 f = (4)03.5,8.75f ωπ==;0.3s T =,035 6 f = (5) ()() ()(){ } 0.20.2 1 0.20.2 0.20.2(0.2)(0.2) 1 c o s (0.2)() 2130.6c o s (0.2)() 1.8()0.6() 211.8 0.6()0. 6() 2110.910.610.6j n j n n n j n j n n n j n j n j j n e e F n u n F e e u n F e u n F e u n e e ππππππωπωπππ-+-----+=+?? ??-=-?+-??? ?? ? ????=-?-+-? ??? ?? =-+ ?++?? 3.3 function [X]=myDTFT(x, n, w) % 计算DTFT % [X]=myDTFT(x, n, w) %X=输出的DTFT 数组 %x=输入的有限长序列 %n=样本位置行向量 %w=频率点位置行向量 X=x*exp(-j*n ’*w) 3.4 (1) 7 ()10.3j j X e e ω ω -= - (2)20.51 ()(10.5)10.5j j j j e X e e e ωω ωω ---=--- (3)2()0.80.1610.4j j j e X e e ω ω ω --=??-

DSP中的浮点小数与定点小数 在DSP世界中,由于DSP芯片的限制,经常使用定点小数运算。所谓定点小数,实际上就是用整数来进行小数运算。下面先介绍定点小数的一些理论知识,然后以C语言为例,介绍一下定点小数运算的方法。在TI C5000 DSP系列中使用16比特为最小的储存单位,所以我们就用16比特的整数来进行定点小数运算。 先从整数开始,16比特的储存单位最多可以表示0x0000到0xffff,65536种状态,如果它表示C语言中的无符号整数的话,就是从0到65535。如果需要表示负数的话,那么最高位就是符号位,而剩下的15位可以表示32768种状态。这里可以看出,对于计算机或者DSP芯片来说,符号并没有什么特殊的储存方式,其实是和数字一起储存的。为了使得无论是无符号数还是符号数,都可以使用同样的加法减法规则,符号数中的负数用正数的补码表示。 我们都知道-1 + 1 =0,而0x0001表示1,那么-1用什么来表示才能使得-1 + 1 =0呢?答案很简单:0xffff。现在就可以打开Windows的计算器,用16进制计算一下0xffff+0x0001,结果是0x10000。那么0x10000和0x0000等价麽,我们刚才说过用16比特来表达整数,最高位的1是第17位,这一位是溢出位,在运算寄存器中没有储存这一位,所以结果是低16位,也就是0x0000。现在我们知道负数的表达方式了。举个例子:-100。首先我们需要知道100的16进制,用计算器转换一下,可以知道是0x0064,那么-100就是0x10000 - 0x0064,用计算器算一下得0xff9c。还有一种简单的转换符号的方法,就是取反加一:把数x写成二进制格式,每位0变1,1变0,最后把结果加1 就是-x了。 好,复习了整数的相关知识之后,我们进入定点小数运算环节。所谓定点小数,就是小数点的位置是固定的。我们是要用整数来表示定点小数,由于小数点的位置是固定的,所以就没有必要储存它(如果储存了小数点的位置,那就是浮点数了)。既然没有储存小数点的位置,那么计算机当然就不知道小数点的位置,所以这个小数点的位置是我们写程序的人自己需要牢记的。 先以10进制为例。如果我们能够计算12+34=46的话,当然也就能够计算1.2+3.4 或者0.12+0.34了。所以定点小数的加减法和整数的相同,并且和小数点的位置无关。乘法就不同了。12*34=408,而1.2*3.4=4.08。这里1.2的小数点在第1位之前,而4.08的小数点在第2位之前,小数点发生了移动。所以在做乘法的时候,需要对小数点的位置进行调整?!可是既然我们是做定点小数运算,那就说小数点的位置不能动!!怎么解决这个矛盾呢,那就是舍弃最低位。也就说 1.2*3.4=4.1,这样我们就得到正确的定点运算的结果了。所以在做定点小数运算的时候不仅需要牢记小数点的位置,还需要记住表达定点小数的有效位数。上面这个例子中,有效位数为2,小数点之后有一位。 现在进入二进制。我们的定点小数用16位二进制表达,最高位是符号位,那么有效位就是15位。小数点之后可以有0 - 15位。我们把小数点之后有n位叫做Qn,例如小数点之后有12位叫做Q12格式的定点小数,而Q0就是我们所说的整数。 Q12的正数的最大值是0 111.111111111111,第一个0是符号位,后面的数都是1,那么这个数是十进制的多少呢,很好运算,就是0x7fff / 2^12 =

[摘要] 让你说出知道的芯片的名称,你可能会一时想不起,也不能一一罗列DSP 芯片都有哪些。或许是对DSP芯片深刻的了解才了然于心,由于种种原因的忘却;或许是因为大家在说DSP芯片好,既然大家都说好,那才是真的好,至于怎样好,可能是似懂非懂。那好吧,不管是懂还是不懂,现在让我们从新的视角来读懂这个芯片的世界,让你发现不曾明白的细节 让你说出知道的芯片的名称,你可能会一时想不起,也不能一一罗列DSP芯片都有哪些。或许是对DSP芯片深刻的了解才了然于心,由于种种原因的忘却;或许是因为大家在说DSP芯片好,既然大家都说好,那才是真的好,至于怎样好,可能是似懂非懂。那好吧,不管是懂还是不懂,现在让我们从新的视角来读懂这个芯片的世界,让你发现不曾明白的细节。 DSP芯片,也称数字信号处理器,采用特殊的软硬件结构,是一种专注于进行数字信号处理运算的微处理器,其主要应用是实时快速地实现各种数字信号处理,是数字信号处理理论实用化过程的重要技术工具。在语音处理、图像处理等技术领域得到了广泛的应用。那根据对DSP芯片的理解来对比与其他芯片的最要的区别是什么?杭州海康威视数字技术股份有限公司的高级嵌入式开发经理黄田认为,DSP芯片与其它芯片的最大区别在于它拥有针对各种算法设计的大量专用指令,比如各种向量运算。另外DSP芯片在设计时更多地考虑到数据总线的带宽以及吞吐量,避免数据访问成为影响算法性能的瓶颈。 芯片的基本结构 为了快速地实现数字信号处理运算,DSP芯片一般都采用特殊的软硬件结构。下面简单介绍DSP芯片的基本结构。 (1)哈佛结构 主要特点是将程序和数据存储在不同的存储空间中,即程序存储器和数据存储器是两个相互独立的存储器,每个存储器独立编址,独立访问。与两个存储器相对应的是系统中设置了程序总线和数据总线,从而使数据的吞吐率提高了一倍。由于程序和数据在两个分开的空间,因此取指和执行能完全重叠。 (2)流水线操作 流水线与哈佛结构相关,DSP芯片广泛采用流水线以减少指令执行时间,从而增强了处理器的处理能力。处理器可以并行处理二到四条指令,每条指令处于流水线的不同阶段。下面所列是一个三级流水线操作的例子: CLLOUT1

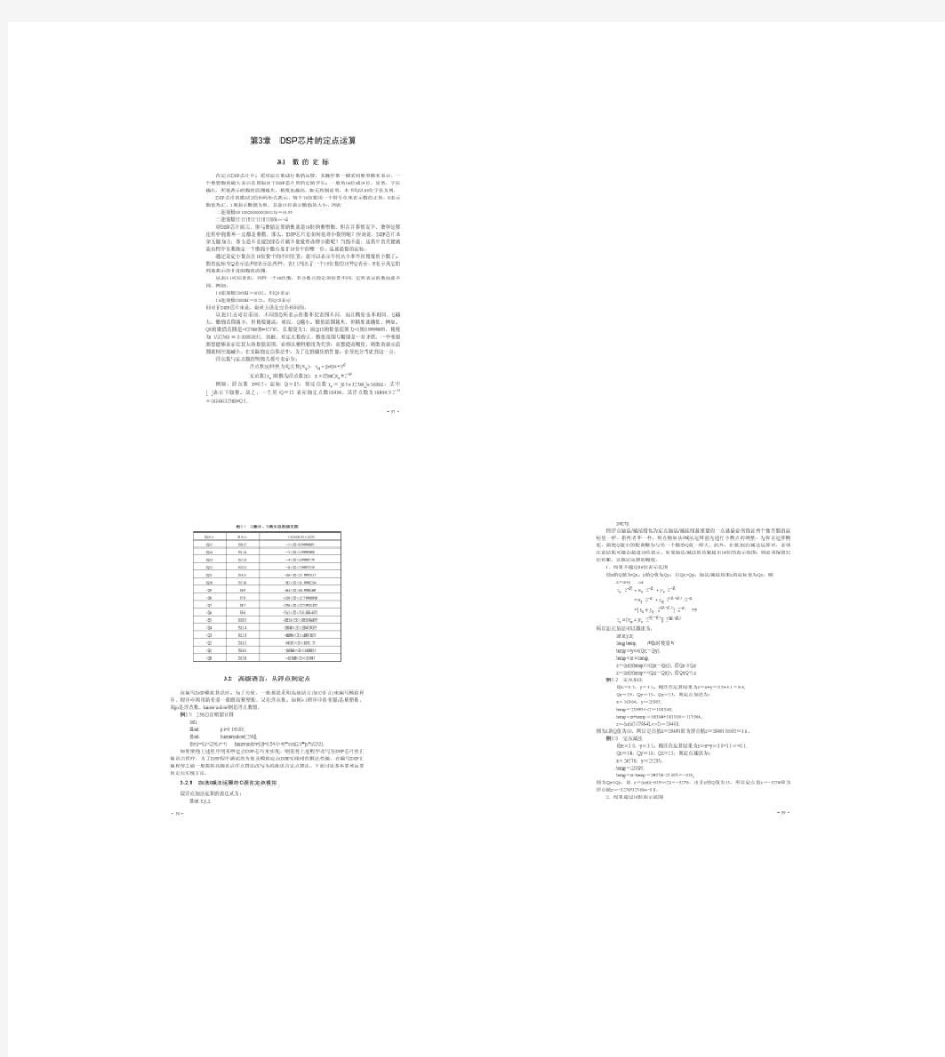

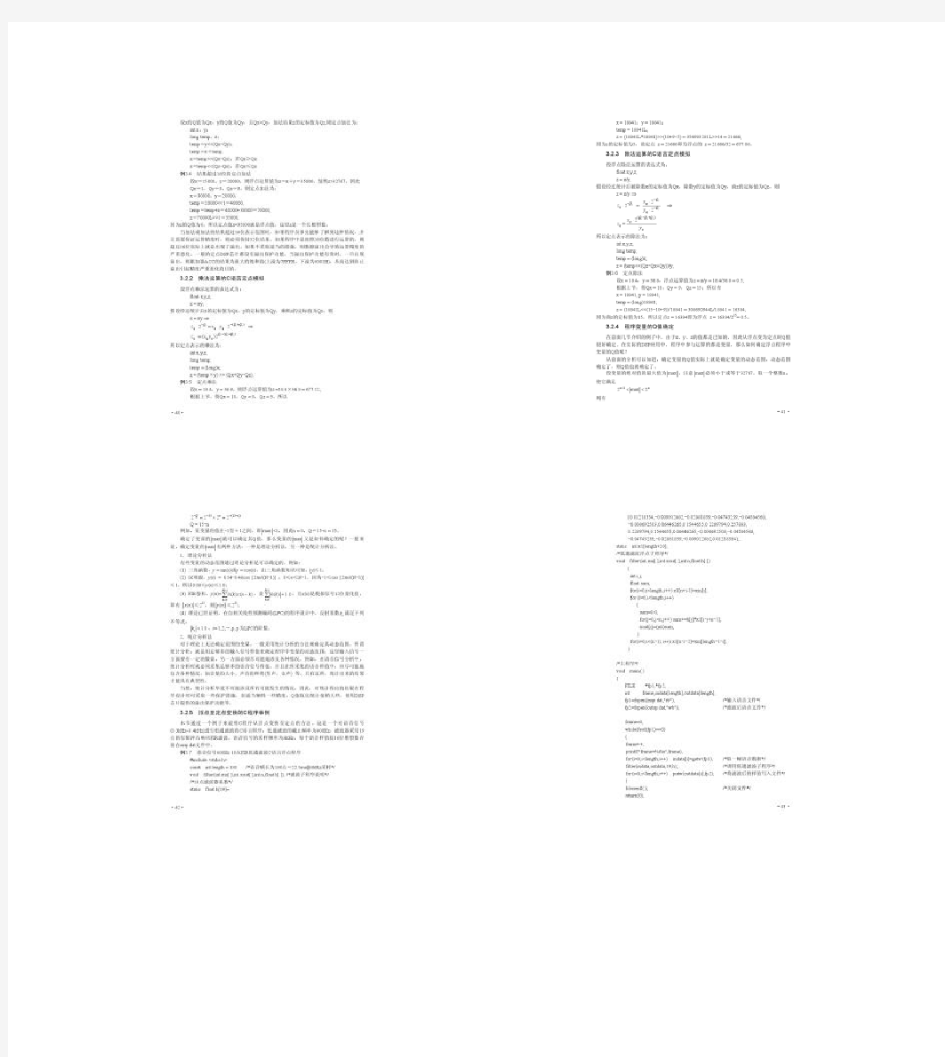

一DSP定点算数运算 1 数的定标 在定点DSP芯片中,采用定点数进行数值运算,其操作数一般采用整型数来表示。一个整型数的最大表示范围取决于DSP芯片所给定的字长,一般为16位或24位。显然,字长越长,所能表示的数的范围越大,精度也越高。如无特别说明,本书均以16位字长为例。DSP芯片的数以2的补码形式表示。每个16位数用一个符号位来表示数的正负,0表示数值为正,l则表示数值为负。其余15位表示数值的大小。因此, 二进制数0010000000000011b=8195 二进制数1111111111111100b= -4 对DSP芯片而言,参与数值运算的数就是16位的整型数。但在许多情况下,数学运算过程中的数不一定都是整数。那么,DSP芯片是如何处理小数的呢?应该说,DSP芯片本身无能为力。那么是不是说DSP芯片就不能处理各种小数呢?当然不是。这其中的关键就是由程序员来确定一个数的小数点处于16位中的哪一位。这就是数的定标。 通过设定小数点在16位数中的不同位置,就可以表示不同大小和不同精度的小数了。数的定标有Q表示法和S表示法两种。表1.1列出了一个16位数的16种Q表示、S表示及它们所能表示的十进制数值范围。 从表1.1可以看出,同样一个16位数,若小数点设定的位置不同,它所表示的数也就不同。例如, 16进制数2000H=8192,用Q0表示 16进制数2000H=0.25,用Q15表示 但对于DSP芯片来说,处理方法是完全相同的。 从表1.1还可以看出,不同的Q所表示的数不仅范围不同,而且精度也不相同。Q越大,数值范围越小,但精度越高;相反,Q越小,数值范围越大,但精度就越低。例如,Q0 的数值范围是一32768到+32767,其精度为1,而Q15的数值范围为-1到0.9999695,精度为1/32768=0.00003051。因此,对定点数而言,数值范围与精度是一对矛盾,一个变量要想能够表示比较大的数值范围,必须以牺牲精度为代价;而想精度提高,则数的表示范围就相应地减小。在实际的定点算法中,为了达到最佳的性能,必须充分考虑到这一点。 浮点数与定点数的转换关系可表示为: 浮点数(x)转换为定点数(xq):xq=(int)x* 2Q 定点数(xq)转换为浮点数(x):x=(float)xq*2-Q 例如,浮点数x=0.5,定标Q=15,则定点数xq=L0.5*32768J=16384,式中LJ表示下取整。反之,一个用Q=15表示的定点数16384,其浮点数为163幼*2-15=16384/32768=0.5。浮点数转换为定点数时,为了降低截尾误差,在取整前可以先加上0.5。 表1.1 Q表示、S表示及数值范围 Q表示 S表示十进制数表示范围 Q15 S0.15 -1≤x≤0.9999695 Q14 S1.14 -2≤x≤1.9999390 Q13 S2.13 -4≤x≤3.9998779 Q12 S3.12 -8≤x≤7.9997559 Q11 S4.11 -16≤x≤15.9995117 Q10 S5.10 -32≤x≤31.9990234 Q9 S6.9 -64≤x≤63.9980469 Q8 S7.8 -128≤x≤127.9960938 Q7 S8.7 -256≤x≤255.9921875

第3章 DSP 芯片的定点运算 3.1 数 的 定 标 在定点DSP 芯片中,采用定点数进行数值运算,其操作数一般采用整型数来表示。一个整型数的最大表示范围取决于DSP 芯片所给定的字长,一般为16位或24位。显然,字长越长,所能表示的数的范围越大,精度也越高。如无特别说明,本书均以16位字长为例。 DSP 芯片的数以2的补码形式表示。每个16位数用一个符号位来表示数的正负,0表示数值为正,1则表示数值为负。其余15位表示数值的大小。因此 二进制数0010000000000011b =8195 二进制数1111111111111100b =-4 对DSP 芯片而言,参与数值运算的数就是16位的整型数。但在许多情况下,数学运算过程中的数不一定都是整数。那么,DSP 芯片是如何处理小数的呢?应该说,DSP 芯片本身无能为力。那么是不是说DSP 芯片就不能处理各种小数呢?当然不是。这其中的关键就是由程序员来确定一个数的小数点处于16位中的哪一位。这就是数的定标。 通过设定小数点在16位数中的不同位置,就可以表示不同大小和不同精度的小数了。数的定标有Q 表示法和S 表示法两种。表3.1列出了一个16位数的16种Q 表示、S 表示及它们所能表示的十进制数值范围。 从表3.1可以看出,同样一个16位数,若小数点设定的位置不同,它所表示的数也就不同。例如: 16进制数2000H =8192,用Q0表示 16进制数2000H =0.25,用Q15表示 但对于DSP 芯片来说,处理方法是完全相同的。 从表3.1还可以看出,不同的Q 所表示的数不仅范围不同,而且精度也不相同。Q 越大,数值范围越小,但精度越高;相反,Q 越小,数值范围越大,但精度就越低。例如,Q0的数值范围是-32768到+32767,其精度为1,而Q15的数值范围为-1到0.9999695,精度为 1/32768 = 0.00003051。因此,对定点数而言,数值范围与精度是一对矛盾,一个变量要想能够表示比较大的数值范围,必须以牺牲精度为代价;而想提高精度,则数的表示范围就相应地减小。在实际的定点算法中,为了达到最佳的性能,必须充分考虑到这一点。 浮点数与定点数的转换关系可表示为: 浮点数(x)转换为定点数():Q q x 2x (int)*= 定点数(q x )转换为浮点数(x):Q q x -*=2)float (x 例如,浮点数 x=0.5,定标 Q =15,则定点数q x =??16384327685.0=?,式中 ??表示下取整。反之,一个用 Q =15 表示的定点数16384,其浮点数为16384×2-15 =16384/32768=0.5。

∞ ∑ 3.3 x %1(n) = x (n + 8r) 说明x%1(n)的周期是8 r=?∞ 2π ? j π kn N ?1 7 7 ? j kn = e ∴X% 1(k) = x %1(n)W Nkn = e ∑ ∑ ∑ 8 4 n=0 n=0 n=0 ? j π 0×n 7 X 1(0) = e ∑ 4 = 3 n=0 ? j π n 7 X 1(1) = e ∑ 4 = (1+ 2 / 2) (1? j ) n=0 ? j π 2n ? j π 3n 7 X 1(2) = e 7 = ? j ;X 1(3) = e ∑ ∑ 4 4 = (1? 2 / 2) (1+ j ) n=0 n=0 ? j π 4n ? j π 5n 7 X 1(4) = e 7 =1;X 1(5) = e ∑ ∑ 4 4 =(1? 2 / 2) (1? j ) = (1+ 2 / 2) (1+ j ) n=0 n=0 ? j π 6n ? j π 7n 7 X 1(6) = e 7 = j ;X 1(7) = e ∑ ∑ 4 4 n=0 n=0

3.6 解:(1)x(n) =δ(n ) N ?1 根据定义有:X(k) = x (n)W = δ(n )W Nkn =1 N ?1 ∑ ∑ kn N n=0 n=0 (2)x (n) =δ(n ?n 0),0 < n 0 < N N ?1 X (k ) = x (n)W = δ (n ? n 0)W N kn =W N kn N ?1 ∑ ∑ kn 0< n 0 < N 0 N n=0 n=0 (3)x (n) = a n 0 < n < N ?1 1?(a W N k )N 1?a N 1?(a W N k ) 1?aW N k N ?1 X (k ) = x (n)W N kn = ∑ = n=0

定点dsp与浮点dsp的比较 DSP数字信号处理器是一种特别适合于进行数字信号处理的微处理器,主要用于实时快速地实现各种数字信号处理算法 定点运算DSP数字信号处理器在应用中已取得了极大的成功,而且仍然是D SP应用的主体。然而,随着对DSP处理速度与精度、存储器容量、编程的灵活性和方便性要求的不断提高、自80年代中后期以来,各DSP生产厂家陆续推出了各自的32bit浮点运算DSP。 定点DSP指令集 定点DSP指令集是按两个目标来设计的: ·使处理器能够在每个指令周期内完成多个操作,从而提高每个指令周期的计算效率。 ·将存贮DSP程序的存储器空间减到最小(由于存储器对整个系统的成本影响甚大,该问题在对成本敏感的DSP应用中尤为重要)。 和定点运算DSP相比,浮点运算DSP具有许多优越性: 浮点运算DSP比定点运算DSP的动态范围要大很多。定点DSP的字长每增加1bit,动态范围扩大6dB。16bit字长的动态范围为96dB。程序员必须时刻关注溢出的发生。例如,在作图像处理时,图像作旋转、移动等,就很容易产生溢出。这时,要么不断地移位定标,要么作截尾。前者要耗费大量的程序空间和执行时间,后者则很快带来图像质量的劣化。总之,是使整个系统的性能下降。在处理低信噪比信号的场合,例如进行语音识别、雷达和声纳信号处理时,也会发生类似的问题。而32bit浮点运算DSP的动态范围可以作到1536dB,这不仅大大扩大了动态范围,提高了运算精度,还大大节省了运算时间和存储空间,因为大大减少了定标,移位和溢出检查。 由于浮点DSP的浮点运算用硬件来实现,可以在单周期内完成,因而其处理速度大大高于定点DSP。这一优点在实现高精度复杂算法时尤为突出,为复杂算法的实时处理提供了保证。 32bit浮点DSP的总线宽度较定点DSP宽得多,因而寻址空间也要大得多。这一方面为大型复杂算法提供了可能、因为省的DSP目标子程序已使用到几十MB存储器或更多;另一方面也为高级语言编译器、DSP操作系统等高级工具软件的应用提供了条件。 DSP的进一步发展,必然是多处理器的应用。新型的浮点DSP已开始在通信口的设置和强化、资源共享等方面有所响应 ====================================================== TI科学家谈浮点DSP未来发展 自十多年前浮点数字信号处理器(DSP)诞生以来,便为实时信号处理提供了算术上更为先进的备选方案。不过,定点器件至今仍是业界的主流--当然低成本是主要原因。定点DSP每器件产品的价格很低,这对大规模大众市场应用而言是相当重要的优势。 相比较而言,浮点DSP能够实现更快速而简便的开发,因此对开发成本比单位制造成本重要的小规模应用而言,更是最佳的选择。

好,我先抛点玉吧 DSP芯片的定点运算 3.1 数的定标 在定点DSP芯片中,采用定点数进行数值运算,其操作数一般采用整型数来表示。一个整型数的最大表示范围取决于DSP芯片所给定的字长,一般为16位或24位。显然,字长越长,所能表示的数的范围越大,精度也越高。如无特别说明,本书均以16位字长为例。 DSP芯片的数以2的补码形式表示。每个16位数用一个符号位来表示数的正负,0表示数值为正,1则表示数值为负。其余15位表示数值的大小。因此 二进制数0010000000000011b=8195 二进制数1111111111111100b=-4 对DSP芯片而言,参与数值运算的数就是16位的整型数。但在许多情况下,数学_运算过程中的数不一定都是整数。那么,DSP芯片是如何处理小数的呢?应该说,DSP芯片本身无能为力。那么是不是说DSP芯片就不能处理各种小数呢?当然不是。这其中的关键就是由程序员来确定一个数的小数点处于16位中的哪一位。这就是数的定标。 通过设定小数点在16位数中的不同位置,就可以表示不同大小和不同精度的小数了。数的定标有Q表示法和S表示法两种。表3.1列出了一个16位数的16种Q表示、S表示及它们所能表示的十进制数值范围。从表3.1可以看出,同样一个16位数,若小数点设定的位置不同,它所表示的数也就不同。例如: 16进制数2000H=8192,用Q0表示 16进制数2000H=0.25,用Q15表示 但对于DSP芯片来说,处理方法是完全相同的。 从表3.1还可以看出,不同的Q所表示的数不仅范围不同,而且精度也不相同。Q越大,数值范围越小,但精度越高;相反,Q越小,数值范围越大,但精度就越低。例如,Q0的数值范围是-32768到+32767,其精度为1,而Q15的数值范围为-1到0.9999695,精度为1/32768 = 0.00003051。因此,对定点数而言,数值范围与精度是一对矛盾,一个变量要想能够表示比较大的数值范围,必须以牺牲精度为代价;而想提高精度,则数的表示范围就相应地减小。在实际的定点算法中,为了达到最佳的性能,必须充分考虑到这一点。 浮点数与定点数的转换关系可表示为: 浮点数(x)转换为定点数( ): 定点数( )转换为浮点数(x): 例如,浮点数x=0.5,定标Q=15,则定点数=,式中表示下取整。反之,一个用Q=15 表示的定点数16384,其浮点数为16384×2-15 =16384/32768=0.5。 表3.1 Q表示、S表示及数值范围 Q表示S表示十进制数表示范围 Q15 S0.15 -1≤X≤0.9999695 Q14 S1.14 -2≤X≤1.9999390 Q13 S2.13 -4≤X≤3.9998779 Q12 S3.12 -8≤X≤7.9997559 Q11 S4.11 -16≤X≤15.9995117 Q10 S5.10 -32≤X≤31.9990234 Q9 S6.9 -64≤X≤63.9980469 Q8 S7.8 -128≤X≤127.9960938 Q7 S8.7 -256≤X≤255.9921875

3.4系列的Z 变换与连续信号的拉普拉斯变 换、傅里叶变换的关系 序列的Z 变换与连续信号的拉普拉斯变换、傅里叶变换的关系 拉普拉斯变换 拉普拉斯逆变换 傅里叶变换 傅里叶逆变换 序列x(n)的Z 变换 逆Z 变换 抽样信号的拉普拉斯变换 []?∞ ∞--==dt e t x t x LT s X st a )()()([]? ∞ +∞ --==j j st a dt e t x s X LT t x σσ)()()(1 Ω +=j s σ[]?∞ ∞ -Ω-==Ωdt e t x t x FT j X t j )()()([]?∞ ∞-Ω-Ω Ω=Ω=d e j X j X FT t x t j )()()( 1Ω =j s ()()n n X z x n z ∞ -=-∞ =∑ ,2,1,0,)(21)(1 ±±==?-n dz z z X j n x c n π()()()()()∑∑? ?∑?∞ -∞ =-∞ -∞=∞ ∞ --∞ ∞--∞ -∞=∞∞ --∧ ∧∧ = -=-==??????=n nsT a n st a st n a st a a a e nT x dt e nT t nT x dt e nT t nT x dt e t x t x LT s X δδ)()()(

抽样序列的z 变换为 3.4.1拉氏变换与Z 变换变换的关系就是复变量s 平面到复变量z 平面的映射: 令 s=σ+j Ω, z=re j ω 得到: re j ω =e (σ+j Ω)T =e σT e j ΩT , 因而 r=e σT , ω=ΩT 3.4.2 ω= ΩT Ω=0 、π/T 、3π/T 、 Ω0与ω的对应关系 Ω变化时与ω的对应关系 s 平面到z 平面的映射是多值映射。 (傅里叶变换是拉普拉斯变换在虚轴的特例,即s =j Ω,因而映射 到z 平面上为单位圆,代入 抽样序列的z 变换 sT e z =()[]()∑∞ -∞ =-= =n n z n x n x ZT z X ) (()e ?() (e )(2.89) sT sT a z X z X X s ===

数字信号处理(方勇)第三章习题答案

3-1 画出) 5.01)(25.01() 264.524.14)(379.02()(2 1 1 211------+--+--=z z z z z z z H 级联型网络 结构。 解: 2 3-2 画出112112(23)(465) ()(17)(18) z z z H z z z z --------+= --+级联型网络结构。 解: () x n () y n 24 3-3 已知某三阶数字滤波器的系统函数为 12 11252333()111(1)(1) 322 z z H z z z z -----++= -++,试画出其并联型网 络结构。 解:将系统函数()H z 表达为实系数一阶,二阶子 系统之和,即:

()H z 1 1122111111322 z z z z ----+= +-++ 由上式可以画出并联型结构如题3-3图所示: ) 题3-3图 3-4 已知一FIR 滤波器的系统函数为 121()(10.70.5)(12) H z z z z ---=-++,画出该FIR 滤波器 的线性相位结构。 解: 因为1 21123()(10.70.5)(12)1 1.30.9H z z z z z z z ------=-++=+-+, 所 以由第二类线性相位结构画出该滤波器的线性相位结构,如题3-4图所示:

() x n 1-1 -1 z - 题3-4图 3-5 已知一个FIR 系统的转移函数为: 12345()1 1.25 2.75 2.75 1.23H z z z z z z -----=+--++ 求用级联形式实现的结构流图并用 MATLAB 画出其零点分布及其频率响应曲线。 解: 由转移函数可知,6=N ,且)(n h 偶对称,故 为线性相位系统,共有5个零点,为5阶系统,因而必存在一个一阶系统,即1±=z 为系统的零点。而最高阶5 -z 的系数为+1,所 以1-=z 为其零点。)(z H 中包含1 1-+z 项。所以: 11()()(1)H z H z z -=+。 1() H z 为一四阶子系统,设

实验一 CCS使用及DSP基本数学运算 一、实验目的: 1、熟悉CCS集成开发环境,掌握工程的生成方法; 2、熟悉SEED-DTK5416实验环境; 3、掌握CCS集成开发环境的调试方法; 4、了解数在计算过程中的定标,掌握数的定点、浮点表示方法,定点、浮点基本运算 以及定点、浮点间的相互转换。 二、实验内容: 1、 DSP源文件的建立; 2、 DSP程序工程文件的建立; 3、编译与链接的设置,生成可执行的DSP文件; 4、进行DSP程序的调试与改错; 5、学习使用CCS集成开发工具的调试工具; 6、观察实验结果; 三、实验知识背景: 在DSP编程过程中,数以二进制、十进制、与十六制表示均可。在定点DSP的运算过程中,数一般采用二进制与二进制补码的形式进行运算的。其中二进制数只能代表正数不能代表负的数,而二进制补码记数系统弥补了这一缺点。它的构成如下; 在二进制的基础上,加一符号位。符号位位于二进制数的最高位 当为正数时,符号位为0,为负数时,符号位为1 当采用二进制补码进行数的运算时,具有如下的两个优点: 可以将加法与减法统一成加法运算 符号位可以进行扩展,而其数值不变,这可以使一个比较小的数存放到比较大的寄存器当中 例: (11110)2 = 1×(-16)+ 1×8 + …… + 1×2 + 0×1 = -2 当将其符号位扩展三位,放入一8位的寄存器中 (11111110)2 = 1×(-128)+ 1×64 + …… + 1×2 + 0×1 = -2 这将为运算提供极大的方便,因而在定点的DSP中,大多数情况采用二进制补码形式。 C5000系列的DSP硬件只支持定点运算,浮点运算要通过软件来实现。其运算字长为16位,也就是说,DSP所能表示的整数的范围也就决定了,其范围为-32768到32767。而在很多情况下,数学运算过程中不一定是整数,而且动态范围也不是固定不变的。如何解决这个问题?对于只支持定点运算的CPU来说,在硬件上并没有提供小数点定位的机制。只有靠软件中人为地假设将小数点放在16位数据中的不同位置,就可以表示不同大小与不同精度的数据了,这就是数的定标。 数的定标有Q与S两种表示方法。在Q表示法中,Q代表(Quantity of Fractional Bits)数中尾数部分的位数,即小数点右边的位数。而S表示法中,S代表数中整数部分的位数,即小数点左边的位数。实用中一般用Q表示法,例:Q0表示小数点在第0位的右边,即为整数。Q15表数小数点在第15位的右边,即为小于1的小数(以二进制补码表示,第15位为符号位)。下表给出了16位数的16种不同的Q表示法。并列出了它们所能表示的十进

最近在对前做的一个DSP项目进行改版,正好借此机会把学习的东西总结一番,此总结针对TI的TMS320F2812而言,编译器为CCS3.1。希望对自己或大家有所帮助。 第1章DSP芯片的定点运算 1.数据的溢出: 1>溢出分类: 上溢(overflow): 下溢(underflow) 2>溢出的结果: 例:signed int :32767+1=-32768;-32768-1=32767 unsigned char:255+1=0;0-1=255 3>为了避免溢出的发生,一般在DSP中可以设置溢出保护功能。当发 生溢出时,自动将结果设置为最大值或最小值。 2.定点处理器对浮点数的处理: 1>定义变量为浮点型(float,double),用C语言抹平定点处理器和浮 点处理器的区别,但是程序的代码庞大,运算速度也慢。 2>放大若干倍表示小数。比如要表示精度为0.01的变量,放大100倍 去运算,运算完成后再转化。但是这个做法比较僵硬,如要将上面的 变量重新定义成0.001精度,又需要放大1000倍,且要重新编写整 个程序,考虑溢出等问题。 3>定标法:Q格式:通过假定小数点位于哪一位的右侧,从而确定小 数的精度。 Q0:小数点在第0位的后面,即我们一般采用的方法 Q15 小数点在第15位的后面,0~14位都是小数位。 转化公式:Q=(int)(F×pow(2,q)) F=(float)(Q×pow(2,-q)) 3.Q格式的运算 1>定点加减法:须转换成相同的Q格式才能加减 2>定点乘法:不同Q格式的数据相乘,相当于Q值相加 3>定点除法:不同Q格式的数据相除,相当于Q值相减 4>定点左移:左移相当于Q值增加

第三章习题 1. Consider a Wiener filtering problem characterized by the following values for the correlation matrix R of the tap-input vector x (n) and cross-correlation vector p between x (n) and the desired response d(n): ?? ????=??????=25.05.015.05.01P R (a) Suggest a suitable value for the step-size parameter μ that would ensure convergence of the method of steepest descent, based on the given value for matrix R . (b) Using the value proposed in part (a), determine the recursions for computing the elements )(1n w and )(2n w of the tap-weight vector w (n). For this computation, you may assume the initial values 0)0()0(21==w w . (c) Investigate the effect of varying the step-size parameter μ on the trajectory of the tap-weight vector w (n) as a varies from zero to infinity. 2. The error performance of a real-valued filter, using a single tap weight w , is defined by ,))(0(20min w w r J J -+= where r(0) is the autocorrelation function of the tap input x (n) for zero lag, min J is the minimum mean-square error, and o w is the Wiener solution for the optimum value of the tap weight w . (a) Determine the bounds on the step-size parameter μof the steepest-descent algorithm used to recursively compute the optimum solution o w . (b) Plot the curve for cost function of the filter. 3. Continuing with Problem 2, do the following: (a) Formulate the learning curve of the filter in the terms of its only