文章编号:1002-2082(2007)06-0712-04

基于FPGA 的实时中值滤波器设计

刘健鹏,陈卫东,钱 钧

(西安应用光学研究所,陕西西安710065)

摘 要:在图像生成和采集过程中引入的各种噪声会使图像质量变差。为了实现对图像的实时预处理,首先介绍中值滤波器的基本原理和算法,然后在现场可编程门阵列(FPGA )上根据中值滤波的根基数算法,采用流水技术设计一种快速实时中值滤波器,给出按行输出的图像处理过程中存储前2行图像数据的方法。仿真结果表明:该中值滤波器可实时完成CCD 输出图像的预处理,达到了抑制噪声及保持图像细节的目的。

关键词:图像预处理;中值滤波器;现场可编程门阵列;实时性

中图分类号:T N 713 文献标志码:A

Design of real -time median filter based on FPGA

LIU Jian -peng ,CHEN Wei -dong ,QIA N Jun

(X i ′an Institute o f Applied O ptics,Xi ′an 710065,China)

Abstract :Since all kinds of no ises introduced in the pro cess o f the video fo rming and sampling inevitably lead to a bad quality o f video im ages,the basic principle and algor ithm of the median filter ar e presented to realize the real -time im ag e pre -processing for succeeding pr ocessing .T he rapid r eal -time m edian filter was designed with "flow ing technolog y "according to an algo rithm in the field-pr ogram mable g ate array (FPGA).The method to stor e the first tw o lines o f the image data in the line output based im age processing is g iv en.The simulation result sho ws that the median filter can im plement the real -tim e pre -pr ocessing of CCD output images ,and achieve the goal of noise suppression and image details keeping.

Key words :image pre-pr ocessing ;m edian filter;FPGA;real-tim e median filtering

引言

在图像生成、采集及传输过程中,不可避免的引入各种噪声使图像质量变差。因此必须对图像进行预处理,抑制图像噪声,以利于后续处理。但由于图像预处理的计算量庞大,使用软件实现图像预处理比较慢,达不到实时处理的要求,因此选用硬件实现。

现场可编程门阵列(FPGA )是基于查找表结构的可编程器件,具有丰富的寄存器资源,而且可通过系统的重新配置来改变逻辑功能,使得设计的灵活性大大提高。随着FPGA 器件容量、功能以及

可靠性的提高,它已经成为数字电路系统领域的主要设计方式之一。使用FPGA 设计不但能大大缩减电路的体积,提高电路的稳定性,而且其先进的开发工具使整个系统的设计调试周期大大缩短。因此FPGA 技术已经广泛应用在通信、电子、信号处理、

工业控制等领域。

中值滤波是一种常用的图像预处理方法,它的响应基于图像滤波所截取的窗口中像素的排序,然后由排序得到的中值代替窗口中心像素的值。对于随机噪声,中值滤波不仅具有优良的去噪能力,而且比小尺寸的线性平滑滤波的图像模糊程度明显

收稿日期:2006-12-13; 修回日期:2007-04-12

作者简介:刘健鹏(1981-),男,陕西扶风人,硕士,主要从事图像处理方面的研究。

第28卷第6期2007年11月 应用光学Journal of A pplied O ptics

V o l.28N o.6

N ov.2007

要低,因此得到了普遍的应用。但是传统的中值滤波算法需要进行大量的数据比较运算,数据排序费时较多,不利于图像的实时处理。

1 中值滤波的基本算法及其传统实

现方法

信号中值是信号值按大小排序后排在中间位置的数值,对于图像信号{x i ,j ∶i ,j ∈N },中值定义为

y i ,j =M {x i ,j ∶i ,j ∈W }

式中N 表示自然数集;W 表示截取的图像窗口。窗口W 通常有线性窗、方形窗、十字窗和菱形等多种形式。

传统的中值滤波算法实现过程如下:选择一个n ×n 的窗口(n 通常取奇数),并使该窗口沿图像数据移动;每次移动后,对窗口内的像素值进行排序,并用排序得到的中值替换窗口中心位置的像素值。

对于一幅M ×N 的图像,如果不考虑边界滤波,图像数据需要进行(M -n +1)×(N -n +1)次对窗口像素灰度值的排序。因此当图像数据量比较大时,中值滤波的传统算法实时性较差。

2 一种快速算法

本文首先介绍中值滤波的根基数算法。它是一种便于硬件实现的中值滤波快速算法,能实时完成图像的中值滤波。假设数字图像的像素集合为{x i ,j ∶i ,j ∈W },其像素x i ,j 用二进制表示为(b 1

i ,j ,b 2

i ,j ,…,b L

i ,j ),中值y i ,j =M {x i ,j ∶i ,j ∈W }}用二进制表示为(u 1,u 2,…,u L ),其中L 为像素值二进制表示

的位数。

如果多数元素的b 1i ,j 位等于1(0),根据中值的定义,不难得到u 1=1(0)。即如果已知集合中各元素的最高位,就可以确定中值的最高位。为了确定中值的前K 位,只需对像素集合{x i ,j ∶i ,j ∈W }中各像素的前K 位进行运算即可。

因此把像素集合{x i ,j ∶i ,j ∈W }分成2组:第1组是像素最高位b 1i ,j 等于1的像素集合,定义此集合为S (b 1i ,j =1)。第2组为最高位是0的像素集合,该集合定义为S (b 1i ,j =0)。如果在像素集合{x i ,j ∶i ,j ∈W }中,子集S (b 1i ,j =1)中元素的个数多于子集S (b 1

i ,j =0)中元素的个数,y i ,j 显然在S (b 1

i ,j =1)中,而S (b 1

i ,j =0)中的元素都小于y i ,j ,子集S (b 1

i ,j =0)中的

元素变成无效数据。为了保持y i ,j 在像素集合{x i ,j ∶i ,j ∈W }中仍然处在第(N +1)/2的位置,将子

集S (b 1i ,j =0)中的元素的所有位都置为0。这样处理后,虽然子集S (b 1i ,j =0)中元素数值改变,但是它们仍然都小于y i ,j ,并不改变y i ,j 的数值,也没有改变y i ,j 在像素集合{x i ,j ∶i ,j ∈W }中的位置。同理,如

果子集S (b 1i ,j =1)中元素的个数少于子集S (b 1i ,j =0)

中元素的个数,y i ,j 显然在S (b 1i ,j =1)中,将子集S (b 1i ,j =1)中元素的所有位都置为1。如此处理后,虽然子集S (b 1i ,j =1)中元素数值改变,但是它们仍然都大于y i ,j ,并不改变y i ,j 的数值,也没有改变y i ,j 在像素集合{x i ,j ∶i ,j ∈W }中的位置。按照这样的算

法依次计算下去,就可以计算出y i ,j 的u 1,u 2,…,u L ,最终求得y i ,j 。

3 硬件设计实现

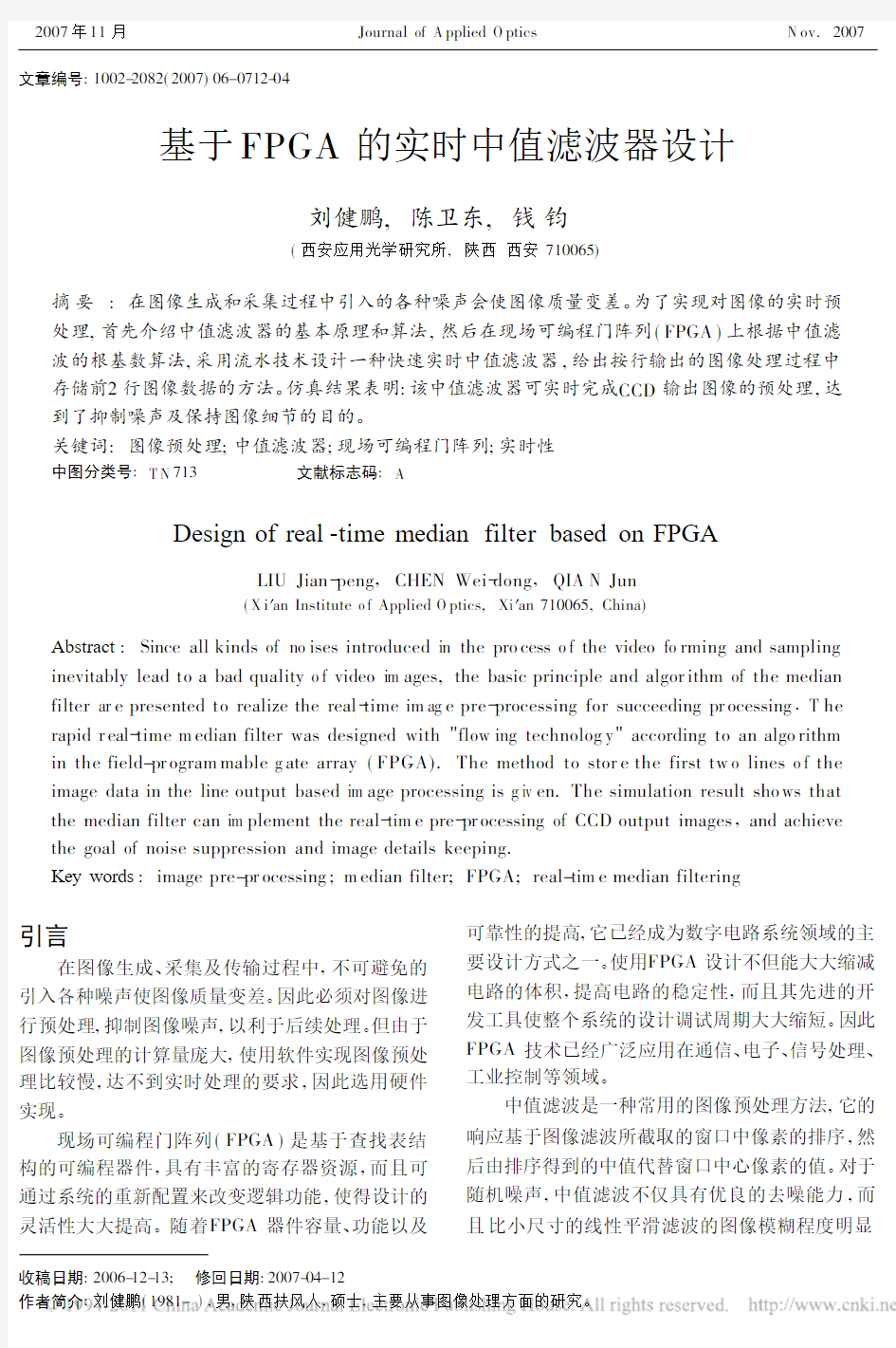

按照上述快速算法,笔者在Xilinx 公司的XC 2S 300E 上设计并实现了3×3十字窗口的实时中值滤波处理。由于视频图像是按行输出的,因此在进行3×3十字窗口的中值滤波时,需要对前2行的图像数据进行存储。如何存储前2行图像数据是实现实时中值滤波器的一个关键因素。图1所示是实时中值滤波器的硬件框图,它由3部分组成:

图1 中值滤波器的硬件框图

Fig .1 The hardware block diagram of median f ilter

1)快速FIFO 单元

为了缩短电路的延时时间,有效地存储前2行数据,设计中利用Xilinx ISE 7.1的IP 核生成2个快速FIFO 来负责分别缓存一行的数据。CCD 输出的PAL 制式的视频图像经过同步信号分离,A/D 采样量化后,在读写信号的控制下被写入FIFO 和从FIFO 中读出。A /D 输出的第(i -2)行数据在同步时钟作用下,先按序存入FIFO1,然后按时间顺序存到FIFO2中,与此同时第(i -1)行数据存入FIFO 1,它们和第i 行有相同列坐标的采样输入数据同时送到中值滤波模块中进行处理。

2)中值滤波单元

图1中虚线框中的部分是本设计的核心中值滤波单元。这部分的输入信号是视频数据连续3行有相同列坐标的3个数据pixin,pixb,pixc 和时钟

?

713? 应用光学2007,28(6) 刘健鹏,等:基于FP GA 的实时中值滤波器设计

clk ,输出是滤波处理结果中值lutout 。中值滤波采用VHDL 语言设计,利用FPGA 的硬件资源,首先生成3×3的矩形存储窗口,将3行数据分别按行移位后,存入存储窗口;然后根据滤波窗口的形式,将参与计算的5个数据取出;最后利用上述快速算法求出十字滤波窗口的中值。部分代码如下://3×3矩形存储窗口

sig nal apix a :std logic vector (7dow nto 0);sig nal apix b :std logic v ector (7do w nto 0);sig nal apix c:std lo gic v ecto r(7do wnto 0);sig nal bpixa:std logic v ector(7do w nto 0);sig nal bpixb :std lo gic vecto r (7dow nto 0);sig nal bpixc:std log ic vector (7dow nto 0);sig nal cpixa:std lo gic v ecto r(7do wnto 0);sig nal cpixb :std log ic vector (7dow nto 0);sig nal cpixc :std log ic vector (7dow nto 0);//定义新变量并赋值(选取十字窗口)

pix 1:=apix b; pix 2:=bpix a; pix 3:=bpix b;pix 4:=bpixc ; pix 5:=cpix b ;//VHDL 语言实现快速算法

fo r i in 7dow nto 0loop qq:=“0000”;

//统计第i 位是1的数据个数if(pix 1(i)='1')then

qq:=qq +1; end if;if(pix 2(i)='1')then

qq:=qq +1; end if;if(pix 3(i)='1')then

qq:=qq +1; end if;if (pix 4(i )='1')then

qq :=qq +1; end if ;if (pix 5(i )='1')then

qq :=qq +1; end if ;

//如果多数数据的第i 位是0,则将首位是1的数据各位都置为1

if (qq <3)then

data (i ):='0';if (pix 1(i )='1')then

pix 1:="11111111"; end if ;if (pix 2(i )='1')then

pix 2:="11111111"; end if ;if(pix3(i)='1')then

pix 3:="11111111"; end if;if(pix4(i)='1')then

pix 4:="11111111"; end if;

if(pix5(i)='1')then

pix 5:="11111111"; end if;

//反之,如果多数数据的第i 位是1,则将首位是0的数据各位都置为0

data (i ):='1';if (pix 1(i )='0')then

pix 1:="00000000"; end if ;if (pix 2(i )='0')then

pix 2:="00000000"; end if ;if (pix 3(i )='0') then

pix 3:="00000000"; end if;if(pix4(i)='0')then

pix 4:="00000000"; end if;if(pix5(i)='0')then

pix 5:="00000000"; end if;end if;end loop;

lutout<=data;3)控制电路单元

控制电路单元完成对数据流向的控制,为了保持输入数据的顺序性,数据输入流向始终控制为

A /D →FIFO 1→FIFO 2。

数据读出则是同时读出三个有相同列坐标的数据到中值滤波单元。

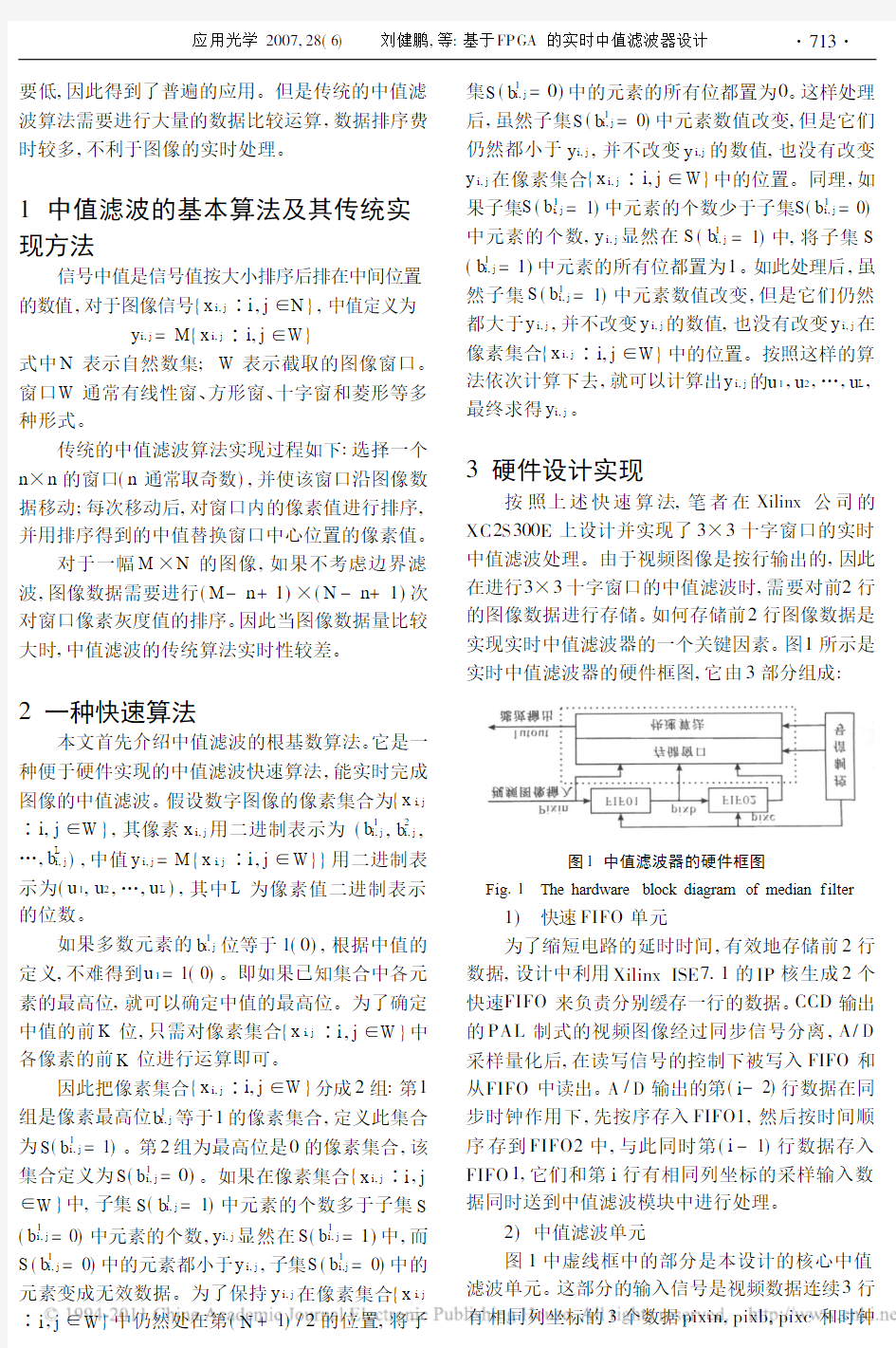

4 时序仿真

使用Xilinx ISE Simulator 进行行为级仿真,仿真的时序图如图2

所示。

图2 时序仿真图

Fig .2 Time sequence simulation diagram

?

714? 应用光学 2007,28(6) 刘健鹏,等:基于F PG A 的实时中值滤波器设计

5 结论

根据中值滤波的根基数算法,采用流水技术实现了实时中值滤波器的设计。通过对CCD输出的视频信号进行3×3十字窗口快速中值滤波处理,图像噪声得到有效抑制,质量显著改善。本设计在Xilinx公司的FPGA XC2S300E上利用V HDL得以实现,并且只需修改VHDL代码就可实现任意形式窗口的中值滤波器设计。

参考文献:

[1] 冈萨雷斯,阮秋琦,阮宇智.数字图像处理[M].2版.

阮秋琦,阮宇智,译.北京:电子工业出版社,2005.

G ON ZA L EZ R G.Digital image pro cessing[M].2nd

ed.tr anslat ed by R U A N Q iu-qi,RU A N Y u-zhi.

Beijing:Publishing House of Electr ic Industr y,2005.

(in Chinese)

[2] AT A M A N E,A A T ER V K,WO N G K M.A fast

methed for r eal-time median filter ing[J].IEEE

T r ansact ions on A SSP,1980,28(4):415-421.

[3] 李刚强,田斌,易克初.F PG A设计中关键问题的研究

[J].电子技术应用,2002(6):68-71.

LI G ang-qia ng,T IA N Bin,Y I Ke-chu.K ey pr oblem

resear ch on F PG A design[J].A pplicatio n of

Electr onic T echno log y T echnique,2002(6):68-71.

(in Chinese)

[4] 曾桂林.电视跟踪在光电火控系统中的应用及发展趋

势[J].应用光学,2001,22(2):1-5.

ZEN G G ui-lin.A pplicatio ns o f T V tr acking in

electr oo pt ic sy st ems and its development[J].Jo ur nal

of A pplied Optics,2001,22(2):1-5.(in Chinese) [5] 陈家祯,郑子华,叶锋.基于可编程芯片的图像实时中

值滤波实现[J].长沙大学学报,2006,20(2):62-64.

CHEN Jia-zhen,ZHENG Zi-hua,Y E F eng.

Realizatio n o f m edium filter ing o f imag e data based

on pr og ramma ble chip[J].Jo urnal o f Chang sha

U niver sity,2006,20(2):62-64.(in Chinese)

?

715

?

应用光学2007,28(6) 刘健鹏,等:基于FP GA的实时中值滤波器设计

1、F PGA技术简介 现场可编程门阵列FPGA是80年代末开始使用的大规模可编程数字IC器件,它充分利用EDA技术进行器件的开发与应用。用户借助于计算机不仅能自行设计自己的专用集成电路芯片,还可在计算机上进行功能仿真和时序仿真,及时发现问题,调整电路,改进设计方案。这样,设计者不必动手搭接电路、调试验证,只需短时间内在计算机上操作即可设计出与实际系统相差无几的理想电路。而且,FPGA器件采用标准化结构,体积小、集成度高、功耗低、速度快,可无限次反复编程,因此成为科研产品开发及其小型化的首选器件,其应用极为广泛。 3.1 FPGA工作原理 FPGA采用了逻辑单元阵列LCA(Logic Cell Array)这样一个概念,内部包括可配置逻辑模块CLB(Configurable Logic Block)、输入输出模块IOB(Input Output Block)和内部连线(Interconnect)三个部分。现场可编程门阵列(FPGA)是可编程器件,与传统逻辑电路和门阵列(如PAL,GAL及CPLD器件)相比,FPGA具有不同的结构。FPGA利用小型查找表(16×1RAM)来实现组合逻辑,每个查找表连接到一个D触发器的输入端,触发器再来驱动其他逻辑电路或驱动I/O,由此构成了既可实现组合逻辑功能又可实现时序逻辑功能的基本逻辑单元模块,这些模块间利用金属连线互相连接或连接到I/O模块。FPGA的逻辑是通过向内部静态存储单元加载编程数据来实现的,存储在存储器单元中的值决定了逻辑单元的逻辑功能以及各模块之间或模块与I/O间的联接方式,并最终决定了FPGA所能实现的功能,FPGA允许无限次的编程。 3.2 FIR滤波器特点 1)采用FPGA设计ASIC电路(专用集成电路),用户不需要投片生产,就能得到合用的芯片。 2)FPGA可做其它全定制或半定制ASIC电路的中试样片。 3)FPGA内部有丰富的触发器和I/O引脚。 4)FPGA是ASIC电路中设计周期最短、开发费用最低、风险最小的器件之一。 5) FPGA采用高速CMOS工艺,功耗低,可以与CMOS、TTL电平兼容。同时,FPGA还存在以下五大优势。 1)性能:利用硬件并行的优势,FPGA打破了顺序执行的模式,在每个时钟周 期内完成更多的处理任务,超越了数字信号处理器(DSP)的运算能力。著名 的分析与基准测试公司BDTI,发布基准表明在某些应用方面,FPGA每美元的 处理能力是DSP解决方案的多倍。2在硬件层面控制输入和输出(I/ O)为满足应用需求提供了更快速的响应时间和专业化的功能。 2)上市时间:尽管上市的限制条件越来越多,FPGA技术仍提供了灵活性和快 速原型的能力。用户可以测试一个想法或概念,并在硬件中完成验证,而无需

基于FPGA的计数器的程序设计方案 1.1 FPGA简介 FPGA(Field-Progrmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了 原有可编程器件门电路数有限的缺点。 自1985 年Xilinx 公司推出第一片中大规模现场可编程逻辑器件(FP2GA) 至 今,FPGA 已经历了十几年的历。在这十几年的过程中,可编程器件有了惊人的发展: 从最初的1200 个可利用门,到今天的25 万可利用门,规模增大了200 多倍; FPGA 供应商也从Xilinx 的一枝独秀,到今天近20 个厂商的分庭抗争;FPGA 从单一的基于SRAM结构到今天各种结构类型的出现,都充分体现了可编程器件这一巨大市场的吸引力。FPGA 不仅可以解决电子系统小型化、低功耗、高可靠性等问题,而且其开 发周期短、开发软件投入少、芯片价格 不断降低。由于目前电子产品生命周期相对缩短,相近功能产品的派生设计增多 等特点,促使FPGA 越来越多地取代了ASIC 的市场,特别是对国内众多的科研单位来说,小批量、多品种的产品需求,使得FPGA 成为首选。 1.2 硬件描述语言VHDL特点 功能强大、设计灵活。VHDL具有功能强大的语言结构,可以用简洁明确的源代码来描述复杂的逻辑控制。它具有多层次的设计描述功能,层层细化,最后可直接生成电路级描述。VHDL支持同步电路、异步电路和随机电路的设计,这是其他硬件描述语言所不能比拟的。VHDL还支持各种设计方法,既支持自底向上的设计,又支持自顶向下的设计;既支持模块化设计,又支持层次化设计。支持广泛、易于修改。由于VHDL已经成为IEEE标准所规范的硬件描述语言,目前大多数EDA工具几乎都支持VHDL,这为VHDL的进一步推广和广泛应用奠定了基础。在硬件电路设计过程中,主要的设计文件是用VHDL编写的源代码,因为VHDL易读和结构化,所以易于修改设计。强大的系统硬件描述能力。VHDL具有多层次的设计描述功能,既可以描

目录 摘要 ............................................................. I 1 前言 (1) 2 交通红绿灯控制电路的发展与技术现状 (2) 2.1 交通控制系统以及交通红绿灯控制电路的发展现状 (2) 2.2 智能交通红绿灯控制电路技术的现状 (3) 3 VHDL、FPGA、Quartus ii简介 (5) 3.1 VHDL简介 (5) 3.1.1 VHDL简介 (5) 3.1.2 VHDL语言的特点 (6) 3.2 FPGA简介 (8) 3.2.1 PLD器件的设计特点 (8) 3.2.2 FPGA的基本结构 (10) 3.2.3 采用FPGA设计逻辑电路的优点 (11) 3.3 Quartus II 的简介 (12) 4 具体方案论证与设计 (13) 4.1 具体方案论证 (13) 4.2系统算法设计 (15) 4.3 具体电路原理图 (16) 4.4 电路仿真图 (16) 5 实验结果 (17) 总结 (18) 参考文献 ......................................... 错误!未定义书签。附录: .. (19)

基于FPGA的十字路口交通信号灯 摘要 本文主要介绍十字路口交通灯控制器的设计。首先,介绍交通控制系统以及交通红绿灯控制电路的发展现状;然后采用硬件描述语言进行的交通灯控制器设计。重点介绍了控制系统各部分的设计,以及各个模块之间的同步处理。为了克服交通信号灯控制系统传统设计方法的弊端,更加适应城镇交通现状,利用VHDL语言、采用层次化混合输入方式,设计了具有3种信号灯和倒计时显示器的交通信号灯控制系统,在 QuartusⅡ下进行仿真,并下载到FPGA中制作成实际的硬件电路进行了模拟运行.使用该方法设计的交通灯控制系统电路简单、运行可靠、易于实现,可实现对交通信号的控制和显示功能。 关键词 FPGA;QUARTUS ii;HDPLD;十字路口交通灯控制器; Based on FPGA intersection traffic lights Abstract This paper describes the design of intersection traffic signal controller.First, the introduction of traffic control systems and traffic light control circuit of the development status; then using language designed for the traffic light controller.Focus on various parts of the control system

开题报告 电子信息工程 基于FPGA的CIC滤波器的设计与仿真 一、综述本课题国内外研究动态,说明选题的依据和意义 基于多速率信号处理原理,设计了用于下变频的CIC抽取滤波器,由于CIC滤波器结构只用到加法器和延迟器,没有乘法器,很适合用FPGA来实现。滤波器的结构简单, 需要的存储量小, 是被证明在高速抽取和插值系统中非常有效的单元。 随着数字信号处理算法的不断优化,数字信号处理器(Digital Signal Processors, DSPs)性能的不断提高,数字信号处理技术越来越被广泛地应用在各个领域。数字信号处理技术正朝着高速高性能方向发展,因此这对数字信号处理的手段和工具也提出了更高的要求。 随着现场可编程门阵列(Field Programmable Gate Array, FPGA)制造工艺的不断改进,其集成度和性能的不断提高,采用FPGA对数字信号进行处理越来越受到重视。与DSP相比,FPGA有着不可比拟的优势。一方面,与DSP靠程序指针来运行程序相比,FPGA执行算法的本质是靠电路并行执行的,因此在同样的时钟频率下,使用FPGA完成数字信号处理算法要比使用DSP快得多。另一方面,由于FPGA编程灵活,资源可重新配置,使得在实现数字信号处理时更加灵活,成本更低。因此,FPGA性能的不断提高,能够满足未来复杂数字信号高速实时处理的要求。 用FPGA设计滤波器,无非是是设计一些乘累加单元,其滤波器的各种特性即滤波参数可以通过MATLAB仿真获得。所以首先要做的是确定你滤波器的设计要求,在MATLAB中仿真设计出该滤波器,从而导出滤波器系数,才能在FPGA中使用。 CIC滤波器由于其无需乘法器以及结构特殊,在移动电视直放站的数字信号处理中,可以高效地胜任抽取滤波的任务。然而C1C滤波器也有缺陷,一者通带下垂严重,二者信号折叠带衰减不充分,而且此两者难以兼顾。RS修正法和Kaiser—Hamming补偿法联合使用于CIC滤波器的改进技术中,有效地解决了该问题。 在移动通信系统中,软件无线电的概念已显得越来越重要。众所周知SRC滤波部分的一个重点就是抑制潜在的混叠部分,有一种时变CIC滤波器,他同样是通过先A倍内插再B倍抽样来实现采样率的转换。因此,改进的CIC滤波器在软件无线电中有大的重

引言 随着城乡的经济发展,车辆的数量在迅速的增加,交通阻塞的问题已经严重影响了人们的出行。 现在的社会是一个数字化程度相当高的社会,很多的系统设计师都愿意把自己的设计设计成集成电路芯片,芯片可以在实际中方便使用。随着EDA技术的发展,嵌入式通用及标准FPGA器件的呼之欲出,片上系统(SOC)已经近在咫尺。FPGA/CPLD 以其不可替代的地位及伴随而来的极具知识经济特征的IP芯片产业的崛起,正越来越受到业内人士的密切关注。FPGA就是在这样的背景下诞生的,它在数字电路中的地位也越来越高,这样迅速的发展源于它的众多特点。交通等是保障交通道路畅通和安全的重要工具,而控制器是交通灯控制的主要部分,它可以通过很多种方式来实现。在这许许多多的方法之中,使用FPGA和VHDL语言设计的交通灯控制器,比起其他的方法显得更加灵活、易于改动,并且它的设计周期性更加短。 城市中的交通事故频繁发生,威胁着人们的生命健康和工作生活,交通阻塞问题在延迟出行时间的同时,还会造成更多的空气污染和噪声污染。在这种情况下,根据每个道路的实际情况来设置交通灯,使道路更加通畅,这对构建和谐畅通的城市交通有着十分重要的意义。

第一章软件介绍 1.1 QuartusⅡ介绍 本次毕业设计是基于FPGA下的设计,FPGA是现场可编程门阵列,FPGA开发工具种类很多、智能化高、功能非常的强大。可编程QuartusⅡ是一个为逻辑器件编程提供编程环境的软件,它能够支持VHDL、Verilog HDL语言的设计。在该软件环境下,设计者可以实现程序的编写、编译、仿真、图形设计、图形的仿真等许许多多的功能。在做交通灯控制器设计时选择的编程语言是VHDL语言。 在这里简单的介绍一下QuartusⅡ的基本部分。图1-1-1是一幅启动界面的图片。在设计前需要对软件进行初步的了解,在图中已经明显的标出了每一部分的名称。 图 1-1-1 启动界面 开始设计前我们需要新建一个工程,首先要在启动界面上的菜单栏中找到File,单击它选择它下拉菜单中的“New Project Wizard”时会出现图1-1-2所显示的对话框,把项目名称按照需要填好后单击Next,便会进入图 1-1-3 显示的界面。

摘要 自适应滤波器是统计信号处理的一个重要组成部分。在现代滤波处理技术中,自适应滤波器的处理效果尤为突出。在众多滤波器中,特别是在一些对信号处理的实时性要求比较高,体积功耗有严格限制的场合,使用FPGA硬件实现的数字滤波器更为广泛。 本论文从自适应滤波器研究的重要意义入手,介绍了线性自适应滤波器的算法,对几种基于最小均方误差准则或最小平方误差准则的自适应滤波器算法进行研究,就滤波器的基本原理及设计方法做了简单的介绍,最终设计基于FPGA的LMS算法设计复数自适应滤波器,对设计方法进行叙述,并以VHDL语言编写程序进行仿真测试。 关键词:自适应滤波器;FPGA;自适应算法LMS;有限冲激响应滤波器

FPGA-based design of adaptive filter Student:TAN xx Teacher:CHEN xx Abstract:Adaptive filter is a statistical signal processing as an important component. Processing technology in the modern filter, the adaptive filter, particularly in the treatment effect. Among the filters, especially in some of the real-time signal processing requirements of higher power, there are strict restrictions on the size of the occasion, the use of FPGA hardware to achieve a wider range of digital filters. In this paper, adaptive filter from the importance of research to start to introduce the linear adaptive filter algorithm, based on several criteria MMSE or least square error criteria for the study of adaptive filter algorithm, it filters The basic principle and design method of a brief introduction, the final design of FPGA-based design of complex LMS adaptive filter algorithm, the design methods described, and VHDL languages in maxplus simulation test platform. Keywords: adaptive filter;FPGA;LMS adaptive algorithm;finite impulse response filter

郑州轻工业学院 电子技术课程设计 题目 _基于FPGA的计数器设计___ _________________________ 学生姓名 _ XXX_________________ 专业班级 _电子信息工程10-01班____ 学号 _5401001030XXX__________ 院(系)电气信息工程学院___ ____ 指导教师 _杜海明耿鑫____________ 完成时间20XX年06月22日_______

郑州轻工业学院 课程设计任务书 题目基于FPGA的计数器的程序设设计_______________ 专业、班级电子信息工程学号姓名 _____ 主要内容、基本要求、主要参考资料等: 主要内容: 要求学生使用硬件描述语言(Verilog 或者VHDL)设计基于FPGA的计数器的 源程序。实现如下功能:显示1个0-9999的四位计数器;四位七段数码管的译码与 显示。理解数码管的译码原理,同时需要做一个分频器,理解时钟分频的原理及意 义。 基本要求: 1、学会quartusII的使用,掌握FPGA 的程序设计方法。 2、掌握硬件描述语言语法。 3、程序设计完成后要求在quartusII中实现功能仿真。 主要参考资料: 1、. [M]..20XX,4 2、陈怀琛.MATLAB及在电子信息课程中的应用[M].北京:电子工业出版 社.20XX,1 完成期限:20XX.6.21—20XX.6.25 指导教师签名: ________________ 课程负责人签名: ___________________ 20XX年6月18日

目录

基于FPGA的计数器的程序设设计 摘要 本文介绍了一种基于FPGA的,由顶层到底层设计的数字频率计。本文主要包括该频率计的设计基础和实现方法以及译码与显示等内容,描述了它的设计平台、工作原理和软硬件实现。本设计主要有分频器、四位计数器、16位锁存器以及数码管显示电路。计数器设计采用VHDL硬件描述语言编程,极大地减少了硬件资源的占用,仿真与分析结果表明,该数字频率计性能优异,软件设计语言灵活,硬件简单,速度快。 关键词FPGA 计数器 VHDL

电子科技大学 实 验 报 告 一、实验室名称:虚拟仪器实验室 二、实验项目名称:交通灯设计实验 三、实验学时:4学时 四、实验原理

假设交通灯处于南北和东西两条大街的“十”字路口,如图1所示。用FPGA 开发板的LED 灯来模拟红、黄、绿3种颜色信号,并按一定顺序、时延来点亮LED ,如图2所示。图3给出了交通灯的状态转移图。设计使用频率为1Hz 的时钟来驱动电路(注1:仿真时采用1MHz 的时钟来驱动电路),则停留1个时钟可得到1S 的延时,类似停留3个时钟可得到3S 的延时,停留15个时钟可得到15S 的延时(注2:开发板工作时钟为50MHz )。 北 南 西东 图1. 六个彩色LED 可以表示一组交通信号灯 图2. 交通灯状态 南北 东西 红 黄 绿 红 黄 绿 S0 1 0 0 0 0 1 S1 1 0 0 0 1 0 S2 1 0 0 1 0 0 S3 0 0 1 1 0 0 S4 0 1 0 1 0 0 S5 1 0 0 1 0 0

图3. 交通灯的状态转移图 顶层模块 时钟分频模块状态机跳转模块 图4. 交通灯的原理框图 五、实验目的 本实验是有限状态机的典型综合实验,掌握如何使用状态转移图来定义Mealy状态机和Moore状态机,熟悉利用HDL代码输入方式进行电路的设计和仿真的流程,掌握Verilog语言的基本语法。并通过一个交通灯的设计掌握利用EDA软件(Xilinx ISE 13.2)进行HDL代码输入方式的电子线路设计与仿真的详细流程。。 六、实验内容 在Xilinx ISE 13.2上完成交通灯设计,输入设计文件,生成二进制码流文件下载到FPGA开发板上进行验证。 七、实验器材(设备、元器件)

FPGA实现FIR抽取滤波器的设计FIR(fini te impulse response)滤波器是数字信号处理系统中最基本的元件,它可以在保证任意幅频特性的同时具有严格的线性相频特性,同时其单位冲激响应是有限的,没有输入到输出的反馈,系统稳定。因此,FIR滤波器在通信、图像处理、模式识别等领域都有着广泛的应用。在工程实践中,往往要求对信号处理要有实时性和灵活性,而已有的一些软件和硬件实现方式则难以同时达到这两方面的要求。随着可编程逻辑器件的发展,使用FPG A来实现FIR滤波器,既具有实时性,又兼顾了一定的灵活性,越来越多的电子工程师采用FPGA器件来实现FIR滤波器。 1 FIR滤波器工作原理 在进入FIR滤波器前,首先要将信号通过A/D器件进行模数转换,使之成为8bit的数字信号,一般可用速度较高的逐次逼进式A/D转换器,不论采用乘累加方法还是分布式算法设计FIR滤波器,滤波器输出的数据都是一串序列,要使它能直观地反应出来,还需经过数模转换,因此由FPGA构成的FIR滤波器的输出须外接D/A模块。FPGA有着规整的内部逻辑阵列和丰富的连线资源,特别适合于数字信号处理任务,相对于串行运算为主导的通用DSP芯片来说,其并行性和可扩展性更好,利用FPGA乘累加的快速算法,可以设计出高速的FIR数字滤波器。

2 16阶滤波器结构 在滤波过程中实现抽取,对于抽取率为N的抽取滤波器而言,当进来N个数据时滤波器完成1次滤波运算,输出1次滤波结果。抽取滤波器的结果和先滤波后抽取的结果是一致的,只是对于同样的数据,进行滤波运算的次数大大减少。在数字系统中采用拙取滤波器的最大优点是增加了每次滤波的可处理时间,从而达到实现高速输入数据的目的。采样数据与滤波器系数在控制电路的作用下,分别对应相乘并与前一个乘积累加,经过多次(有多少阶就要多少次)反复的乘累加最后输出滤波结果,将相同系数归类,16阶滤波器公式: 乘法器的数量减少一半,但加法器的数量增多了,但相对乘法运算来说,加法运算所占用的资源少的多,运算的速度也快得多。 3 滤波器系数的求取 使用Matlab集成的滤波器设计工具FDAtool,可以完成多种滤波器的数值设计、分析与评估,设计16阶低通滤波器参数如下:

基于FPGA的计数器的程序设计 摘要 本文介绍了一种基于FPGA的,由顶层到底层设计的数字计数器。本文主要包括该计数器的设计基础和实现方法以及译码与显示等内容,描述了它的设计平台、工作原理和软硬件实现。本设计主要有分频器、四位计数器、16位锁存器以及数码管显示电路四个模块组成。计数器各模块设计采用VHDL硬件描述语言编程,极大地减少了硬件资源的占用,仿真与分析结果表明,该数字计数器性能优异,软件设计语言灵活,硬件简单,速度快。 关键词FPGA计数器VHDL分频器

目录 基于FPGA的计数器的程序设计 (1) 摘要 (1) 1 绪论 (3) 1.1 FPGA简介 (3) 1.2硬件描述语言VHDL简介 (3) 1.3开发工具Quartus II简介 (4) 2整体设计方案 (4) 3各功能模块设计及仿真 (5) 3.1分频器的设计 (5) 3.1.1分频器设计原理 (5) 3.1.2源程序及波形仿真 (6) 3.1.3分频器RTL 电路图 (7) 3.2计数器的设计 (7) 3.2.1分频器设计原理 (7) 3.2.2源程序及波形仿真 (8) 3.2.3 RTL 电路图 (11) 3.3锁存器的设计 (11) 3.3.1锁存器设计原理 (11) 3.3.2锁存器源程序及波形仿真 (12) 3.3.3锁存器RTL电路图 (13) 3.4显示部分的设计 (13) 3.4.1七段数码管显示原理 (13) 3.4.2七段数码管显示源程序及波形仿真 (15) 3.4.3七段数码管显示RTL 电路图 (16) 4系统顶层设计 (17) 4.1.1自顶向下的设计方法 (17) 4.1.2 顶层设计源程序及其仿真波形 (17) 4.1.3系统顶层RTL 电路图 (20) 5总结 (21) 参考文献 (22)

cic滤波器的FPGA实现 发布时间:2016-01-26 15:07:21 技术类别:CPLD/FPGA 一、关于多采样率数字滤波器 很明显从字面意思上可以理解,多采样率嘛,就是有多个采样率呗。前面所说的FIR,IIR滤波器都是只有一个采样频率,是固定不变的采样率,然而有些情况下需要不同采样频率下的信号,具体例子我也不解释了,我们大学课本上多速率数字信号处理这一章也都举了不少的例子。 按照传统的速率转换理论,我们要实现采样速率的转换,可以这样做,假如有一个有用的正弦波模拟信号,AD采样速率是f1,现在我需要用到的是采样频率是f2的信号,传统做法是将这个经过f1采样后的信号进行DA转换,再将转换后的模拟信号进行以f2采样频率的抽样,得到采样率为f2的数字信号,至此完成采样频率的转换 但是这样的做法不仅麻烦,而且处理不好的话会使信号受到损伤,所以这种思想就被淘汰了,现在我们用到的采样率转换的方法就是抽取与内插的思想。 二、抽取 先来总体来解释一下抽取的含义:前面不是说,一个有用的正弦波模拟信号经采样频率为f1的抽样信号抽样后得到了数字信号,很明显这个数字信号序列是在f1频率下得到的,现在,假如我隔几个点抽取一个信号,比如就是5吧,我隔5个点抽取一个信号,是不是就是相当于我采用了1/5倍f1的采样频率对模拟信号进行采样了?所以,抽取的过程就是降低抽样率的过程,但是我们知道,这是在时域的抽样,时域的抽样等于信号在频域波形的周期延拓,周期就是采样频率,所以,为了避免在频域发生频谱混叠,抽样定理也是我们要考虑的因素 下面来具体来介绍 如上图所示,假如上面就是某一有用信号经采样频率f1抽样得到的频谱,假设这时候的采样频率为8 Khz ,可以通过数格子得到,从0到F1处有8个空格,每个空格代表1Khz,有些朋友可能会问,这不是在数字频域吗,单位不是π吗,哪来的hz?是的,这里是数字频域,采样频率F1处对应的是2π,这里只是为了好解释,我们用模拟频率来对应数字频率。 上面是采样频率为8K的数字信号频域图,现在我要对这个数字信号进行时域抽取,从而来降低信号的采样率,我们知道,一旦我们对数字信号进行时域抽取,那么采样率下降,而采样率就是数字信号频域的波形周期,那么也就是周期下降,所以,我们对信号进行抽取要有个度,要在满足抽样定理的条件下对信号进行抽取,否则就会发生频谱混叠。

基于FPGA的数字滤波器的设计Graduation Design(Thesis) of Chongqing University Design of Digital Filter Based on FPGA Undergraduate: Huang Jianhua Supervisor: Yang Lisheng Major:ElectronicInformation Engineering

College of Communication Engineering Chongqing University June 2013

摘要 数字信号处理在通信、雷达、声纳等中有着广泛的应用。数字滤波器的设计是数字信号处理的关键技术之一,有着十分重要的理论和实际意义。随着数字技术的不断发展,在许多场合,数字滤波器正在快速取代模拟滤波器。FPGA(现场可编程门阵列)在现代数字电路设计中发挥着越来越重要的作用。从设计简单的接口电路到设计复杂的状态机,FPGA所扮演的角色已经不容忽视。 本论文完成了基于FPGA的FIR和IIR数字滤波器的设计与实现。本论文首先理论分析讨论了数字滤波器的设计方法,并使用MATLAB工具验证采用哪种窗函数来设计FIR数字滤波器,使用哪种模拟滤波器原型映射IIR数字滤波器。然后根据模拟滤波器的技术指标来确定数字滤波器的技术指标,在MATLAB环境下按照数字滤波器的技术指标设计数字滤波器,并得到滤波器系数,编程实现系数量化,并且比较分析量化前后系统响应的差异,由此得到合适的量化等级。然后在ISE软件平台下根据MATLAB工具得到的量化系数,使用VHDL语言进行FIR和IIR滤波器算法模块编程,同时对AMP电路(可编程预放大器)模块、AD电路(模拟到数字转换器)模块和DA电路(数字到模拟转换器)模块分别进行编程配置,并且对各模块进行严格的软件仿真验证,其中AMP电路模块、AD电路模块和DA电路模块必须进行硬件验证。最后将所有软件和硬件验证无误的模块整合,下载到FPGA硬件中,进行功能验证。验证结果符合设计要求。 关键词:FIR滤波器,IIR滤波器,MATLAB,FPGA,VHDL

基于FPGA的定时器/计数器的设计与实现 摘要 本课题旨在用EDA工具与硬件描述语言设计一个基于Altera公司的FPGA 16位计数器\定时器,可对连续和非连续脉冲进行计数,并且计数器在具有计数定时功能基础上,实现简单脉宽调制功能和捕获比较功能。本设计采用QuartusII编译开发工具使用VerilogHDL 设计语言进行设计,并采用了由上而下的设计方法对计数器进行设计,体现了VerilogHDL 在系统级设计上自上而下设计风格的优点。本设计中采用了三总线的设计方案,使设计更加简洁与规范。本设计所有模块与功能均在Quartus II 7.0_1.4G_Liwz版本下通过编译与仿真,实现了定时器/计数器的设计功能。 关键词:VerilogHDL硬件描述语言;QuartusII;FPGA;定时器/计数器

FPGA-based timer / counter design and implementation This topic aims to use EDA tools to design a 16 bit counter \ timer based on Altera's FPGA by hardware descripe language, which can count continuous and discontinuous pulset, and the counter with the function of capture and PWM. This design uses VerilogHDL language and top-down design method to design the counter on QuartusII compile tool, the design reflect the advantages of VerilogHDL top-down design in system-level design. The design uses a three-bus design, which make design much more specifications and concise. The design and function of all modules are compiled and simulationed on the Quartus II 7.0_1.4G_Liwz versions, and achieve the timer / counter’s features. Key words: VerilogHDL hardware description language; QuartusII; FPGA; timer / counter

目录 引言 (4) 第一章FPGA的设计流程 (5) 1.1 FPGA概述 (5) 1.2 FPGA设计流程 (9) 1.3硬件描述语言HDL(Hardware Description Language) (10) 1.4 FPGA开发工具Quartus Ⅱ软件设计流程 (13) 第二章有限冲激响应(FIR)滤波器的原理及设计 (16) 2.1数字信号处理基础原理 (16) 2.2 FIR滤波器背影知识 (19) 2.3 FIR数字滤波器原理 (21) 2.4 利用窗函数法设计FIR滤波器 (26) 第三章FIR 数字滤波器的FPGA实现 (31) 3.1串行FIR滤波器原理 (31) 3.2分布式算法基础 (32) 3.3直接型FIR滤波器的原理结构图 (34) 3.4具有转置结构的FIR滤波器 (36) 第四章结论与总结 (40) 谢辞 (42) 参考文献 (43)

摘要:本论文课题是《基于FPGA的FIR滤波器设计与实现》。数字滤波器是语音与图象处理、模式识别、雷达信号处理、频谱分析等应用中的一种基本的处理部件,它能满足滤波器对幅度和线性相位的严格要求,避免模拟滤波器所无法克服的电压漂移、温度漂移和噪声等问题。有限冲激响应(FIR)滤波器能在设计任意幅频特性的同时保证严格的线性相位特性。因此在许多应用领域都显示了强大的生命力,具有重要应用意义。本文介绍了用VHDL实现线性相位FIR(有限长单位冲激响应)滤波器。提出了一种基于FPGA的FIR滤波器设计方案。介绍了基于FPGA的FIR滤波器的数字信号处理的算法设计,采用直接型和转置型的基本结构来设计,其运算效率明显提高,并结合先进的EDA软件进行高效的设计和实现,并给出了用Quartus Ⅱ运行的仿真结果。该设计对FPGA硬件资源的利用高效合理,用VHDL编程,在PFGA中实现了高采样率的FIR滤波器。关键字:FIR滤波器;FPGA;VHDL;MATLAB;Quartus Ⅱ

基于FPGA的CIC数字滤波器的设计 摘要:级联积分梳状(Cascade Integrator Comb,CIC)滤波器是数字系统中实现大采样率变化的多速率滤波器,已经证明是在高速抽取和插值系统中非常有效的单元,在数字下变频(DDC)和数字上变频(DUC)系统中有广泛的应用。它不包含乘法器,只是由加法器,减法器和寄存器组成,而且需要的加法器的数目也减少了许多,因此CIC滤波器比FIR和IIR滤波器更节省资源,并且实现简单而高速。本文主要讨论了CIC滤波器的基本原理和基于FPGA的仿真实现方法,具体是采用Verilog HDL语言编程,将滤波器分为积分器模块和梳状器模块2个部分,对每个模块进行具体的功能分析和设计实现,最后通过Modelsim 仿真对滤波器的性能进行分析,验证了设计的正确性。 关键词:CIC滤波器;抽取;FPGA;Verilog HDL the Design of Cascade Integrator Comb Filter Based on FPGA Abstract:CIC (Cascade Integrator Comb, CIC) filter is a digital system to achieve large changes in multi-rate sampling rate filter, which has been proven to be a very effective unit in the high-speed extraction and interpolation system. It is widely used in the digital down conversion (DDC ) and digital up conversion (DUC) systems. It does not contain the multiplier, but just composes by adders, subtractors and registers, and the number of needing adders is reduced a lot. So it takes fewer resources than FIR filter and IIR filter. And the speed of CIC filter is very high and it is also very convenient to realize.This article discusses the basic principles of CIC filter and the simulation way based on FPGA. The modules were described with Verilog HDL. Firstly, the filter was divided into two parts which were integration module and the comb module. Then the function of each module were analyzed and designed. Finally the performance of the filter was analyzed under ModelSim and the correctness of the design was verified. Keywords:CIC filter; Decimation; FPGA; Verilog HDL 1. 引言: 数字滤波是数字信号分析中最重要的组成部分之一,数字滤波与模拟滤波相比,具

总体设计要求和技术要点 1.任务及要求 (1)设计一个交通信号灯控制器,由一条主干道和一条支干道汇合成十字路口,在每个入口处设置红、绿、黄三色信号灯,红灯亮禁止通行,绿灯亮允许通行,黄灯亮则给行驶中的车辆有时间停在禁行线外。 (2)红、绿、黄发光二极管作信号灯,用传感器或逻辑开关作检测车辆是否到来的信号。 (3)主干道处于常允许通行的状态,支干道有车来时才允许通行。主干道亮绿灯时,支干道亮红灯;支干道亮绿灯时,主干道亮红灯。 (4)主、支干道均有车时,两者交替允许通行,主干道每次放行45秒,支干道每次放行25秒,设立45秒、25秒计时、显示电路。 (5)在每次由绿灯亮到红灯亮的转换过程中,要亮5秒黄灯作为过渡,使行驶中的车辆有时间停到禁行线外,设立5秒计时、显示电路。 (6)按《湖南涉外经济学院课程设计管理办法》要求提交课程设计报告。 工作内容及时间进度安排 第17周:周1---周2 :立题、论证方案设计 周3---周5 :程序设计与调试 第18周:周1---周3 :硬件调试与测试、撰写课程设计报告 周4---周5 :验收答辩 课程设计成果 1.与设计内容对应的软件程序 2.课程设计总结报告

摘要 本实验为自主选题设计实验,实验选择具有倒计时显示功能的红黄绿三色交通设计,实验中采用VHDL 作为设计功能描述语言,选用Altera公司的EP1K30144-PIN TQFP最为主控芯片,实验报告中简要介绍了FPGA器件,并给出了设计原理图,详细的介绍了交通灯的设计流程,实验报告中还附有实验代码实验结果照片图。 Abstract This experiment designed for independent choice experiment, experiment choice which has the function of the countdown display red yellow green traffic design, description language (VHDL as design function is applied in the experiments, the most main control chip select MAX II EPM240T100C5 Altera company, experiment report, this paper briefly introduces the MAX II device series, and gives the design diagram, detailed introduces the traffic lights of the design process, the experiment report with the code results photo graph.

FIR带通滤波器的FPGA实现 时间:2009-11-11 09:14:40 来源:现代电子技术作者:石兴华,吴光敏引言 在FPGA应用中,比较广泛而基础的就是数字滤波器。根据其单位冲激响应函数的时域特性可分为无限冲击响应(Infinite Impulse Response,IIR)滤波器和有限冲击响应(Finite Impulse Response,FIR)滤波器。DSP Builder集成了Altera和Matlab/Simulink基于FPGA的信号处理的建模和设计。该工具可以将数字信号处理算法(DSP)系统表示成为一个高度抽象的模块,在不降低硬件性能的前提下,自动将系统映射为一个基于FPGA的硬件设计方案。即支持设计者在Matlab中完成算法设计,在Simulink软件中完成系统集成,然后通过SignalCompiler(模块名)生成在QuartusⅡ软件中可以使用的硬件描述语言,最终实现硬件系统的设计。FIR滤波器是DSPBuilder应用中最为常用的模块之一,在此基于上述基础,设计实现了基于模块的FIR数字带通滤波器。 1 基于DSP Builder的滤波系统设计 1.1 FIR滤波器原理 有限冲激响应(Finite Impulse Response,FIR)滤波器是由有限个采样值组成,实现的方式是非递归、稳定的,在满足幅频响应要求的同时,可以获得严格的线性相位特性,因此在高保真的信号处理等领域得到广泛应用。 对于一个FIR滤波器系统,它的冲击相应总是有限长的,其系统函数可记为: 最基本的FIR滤波器可表示为: 式中:z(n)是输入采样序列;h(n)是滤波器系数;L是滤波器阶数;y(n)表示滤波器输出序列,为x(n)和h(n)的卷积。FIR滤波器基本结构如图1所示。 对于一个4阶滤波器子系统其输出可表示为: 可见在这个子系统中共需要4个延时器,4个乘法单元和一个4输入的加法器,并可以根据实际需要选择调用子系统构成多阶滤波器。 1.2 滤波的总体要求及实现

学士学位论文论文题目: 基于FPGA的数字滤波器设计 院 (部)名称:电气信息工程学院 学生姓名: 专业:测控技术与仪器学号: 指导教师姓名:

摘要 本论文设计了一个基于FPGA(现场可编程逻辑门阵列)FIR(有限脉冲响应)31阶低通滤波器,通带截止频率为0.1MHz,通带波纹最大1dB,阻带最小衰减-50dB,数据的输入输出宽度为8位,采样频率5MHz。 滤波器分为模拟滤波器和数字滤波器,在信号系统邻域中,一般除了A/D 转换前期的滤波和D/A转换后的滤波使用模拟滤波器,基本上其他的滤波一般优先考虑数字滤波器。数字滤波器与模拟滤波器相比有许多的优点:频域易控制,性能指标好;容易实现线性相位的系统,而且稳定,基本上不受外界影响;可重用性和灵活性比较高,只需编程就可以修改其特性,设计周期短。 数字滤波是推动数字信号处理与相关芯片快速发展的一个要素。本论文的FPGA芯片选用Altera公司Cyclone2系列的EP2C8Q208C8N芯片,模数转换使用ADC9280,数模转换使用DAC9708,来实现数字滤波器,FPGA与ASIC、DSP相比,具有明显的优势,在功耗,体积,成本都优于ASIC、DSP,并且处理效率高,可编程性好,并行处理能力非常强,能完成DSP很难完成的许多功能。 本论文首先简单的介绍数字滤波器、FIR滤波器、FIR的窗口函数选择以及FPGA分布式算法的实现,并对系统硬件各功能模块进行了说明;然后根据系统总体设计的要求指标,使用MATLAB来设计确定系数,因为FPGA不能表示浮点数,所以对系数进行了量化,使用verilog HDL硬件语言编程,Modelsim进行功能仿真;最后使用实物来验证结果,并达到预期的目的。 关键词:FPGA,FIR滤波器,MATLAB,分布式算法