北京邮电大学

《数字电路与逻辑设计》期中考试试题 2012.3.24

班级 姓名 班内序号

注意:所有答案(包括选择题和计算题)一律写在试卷纸上,如果卷面位置不够,请写在试卷的背后,否则不计成绩。

一、(每题1分,共20分)判断(填√或×)、选择(单项选择)题 (请先在本试卷上答题之后,将全部答案汇总到本题末尾的表格中。) 1.组合逻辑电路中不存在记忆单元。( √ )

2.晶体管的饱和越深,其对灌电流负载的驱动能力越强,但工作速度越慢。( √ )

3.TTL 门的某输入端通过100K Ω电阻接电源端时,可认为该输入是逻辑“1”。( √ )

4.为了增加驱动能力,相同输入时的相同逻辑门输出可以互连在一起使用。( √ )

5.当两个或两个以上输入信号同时变化,变化前后输出相同,而在输入信号变化时可能出现输出瞬间逻辑错误,称为静态逻辑冒险。( × ) 6.正逻辑的或非门,对应负逻辑的与非门。( √ )

7.TTL 与非门的关门电平V OFF 越接近阈值电压V T ,其噪声容限越大。( √ ) 8.当i j ≠时,必有两个最大项之积0i j M M ?=。( × )

9. 用最简与或式表示一个函数时,其表达式可能不是唯一的。( √ ) 10.反相器的拉电流负载电阻过小时,主要对输出的高电平产生影响。( √ ) 11.逻辑项ABCD 的相邻项有: C 。

A.ABCD

B.BCD A

C.ABC D ?

D. C A B D ? 12.判断下列两个函数式中,是否存在逻辑冒险。 B 。

1(,,)Y A B C A BC =+ 2(,,)Y A B C ABC ABC =+

A.不存在,存在

B. 不存在,不存在

C.存在,不存在

D. 存在,存在 13.通过适当连接和控制,可以实现数据双向传输的门电路是 D 。 A. 集电极开路输出的TTL 门电路; B. 互补式输出的TTL 门电路; C. ECL 门电路; D. 三态输出的门电路。

14.若某TTL 门电路的输出端最大灌电流负载能力为16mA ,最大拉电流负载能力为-12mA(流出输出端)。其输入端低电平的输入最大电流为-1mA(流出输入端),输入端高电平时的输入最大电流为0.1mA(流入输入端),该门电路的扇出系数为: A 。

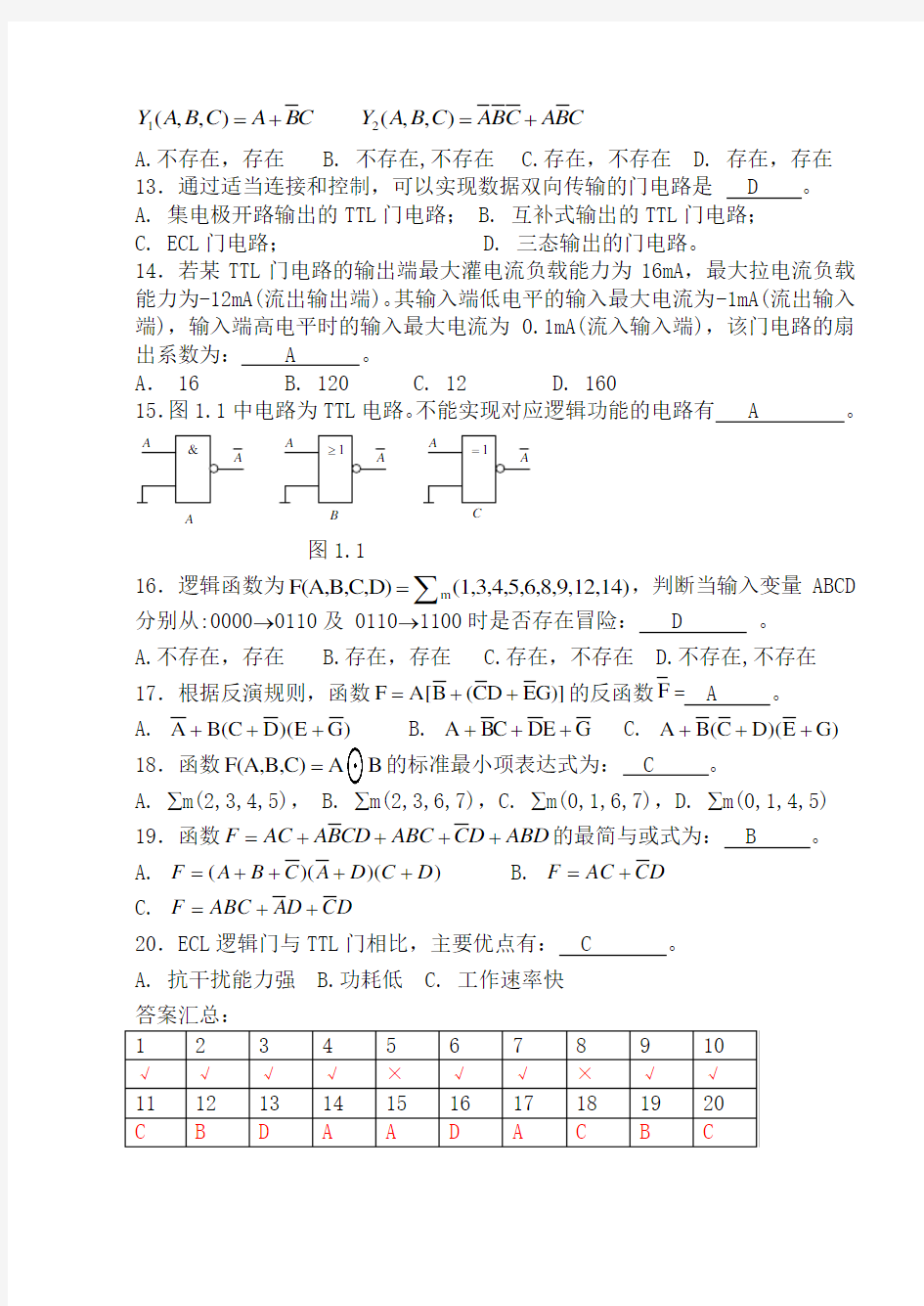

A . 16 B. 120 C. 12 D. 160 15.图1.1中电路为TTL 电路。不能实现对应逻辑功能的电路有 A 。

A

B

图1.1

16.逻辑函数为m F(A,B,C,D)(1,3,4,5,6,8,9,12,14)=∑,判断当输入变量ABCD 分别从:0000→0110及 0110→1100时是否存在冒险: D 。 A.不存在,存在

B.存在,存在

C.存在,不存在

D.不存在,不存在 17.根据反演规则,函数F A[B (CD EG)]=++的反函数F = A 。 A. A B(C D)(E G) +++ B. A B C DE G +++ C. A B(C D)(E G) +++

18.函数F(A,B,C)A

B =的标准最小项表达式为:

C 。

A. ∑m(2,3,4,5),

B. ∑m(2,3,6,7),

C. ∑m(0,1,6,7),

D. ∑m(0,1,4,5) 19.函数F AC ABCD ABC CD ABD =++++的最简与或式为: B 。 A. ()()()F A B C A D C D =++++ B. F AC CD =+

C. F ABC AD CD =++

20.ECL 逻辑门与TTL 门相比,主要优点有: C 。 A. 抗干扰能力强 B.功耗低 C. 工作速率快

二、(共10分)某器件的内部电路简图如图2.1所示。

(1),说明当输入端C分别0和1时,电路的输出F与输入A、B的逻辑关系。(2),画出该器件的符号。

图2.1

答案:

(1),当C=1时,F=高阻(3分)

当C=0时,F AB

=(3分)

(2),

C

A

B

(4分)

三、(10分)逻辑电路如图3.1所示。(1)按照图示电路写出F的原始表达式;(2)将表达式简化为与或式,并填入图3.2的卡诺图;(3)写出用与或非门实现该函数的最简表达式;(4)在图3.3中标明输入信号(未用输入端不许悬空)。

图3.1 图3.2 图3.3

答案:

(1)

F ABC B ABD ACD D ABD

=?????(2分)

(2)

=+??++??(2分)

F AB B C D AD B C D

2分)

=?++(2分)

(3)F B D AC ABD

(4)

2分)

(10分)图4.1中,已知OC门的输出晶体管管截止时的漏电流为I OH=200μA,四、

导通时允许的最大负载电流为I OL(max)=10mA(输出电压不大于0.5V时);负载门(与门及或门)的低电平(0.5V时)输入电流为I IL=-1mA,高电平(3V 时)输入电流为I IH=50μA,V cc=5V,要求OC门的输出高电平V OH≥3.0V,输出低电平V OL≤0.5V 。求R的范围。

图4.1

答案:输出高电平:53

50.20.2R K -≤

=Ω+ (5分)

输出低电平:50.5

643103R mA

-≥=Ω- (5分)

五.(10分)用8选1数据选择器设计一个函数发生电路,实现

(,,,)(1,3,5,7,8,9,10,11)M F A B C D =∏。8选1数据选择器的输出逻辑函数式为: 021*********()()()W D A A A D A A A D A A A =??+?+

32104210()()D A A A D A A A ++?521062107210()()()D A A A D A A A D A A A +++

(1),将函数F 填入卡诺图(图5.1),按照图5.2的地址要求圈出8个子图。(2),在片脚图(图5.2)中标明D 0-D 7的输入信号。

A B C

图5.2

图5.1

A

B

C

函数填入及子图正确2分

数据端正确,各1分,共8分

六、(10分) 74LS155是地址端公用的双数据分配器,功能表如表6-1所示,请附加最少的门实现如下两输出函数(在给出的图6.1上完成设计,A为高位;)。

1(,,)

F A B C A B C A B C B C

=??+??+?

2(,,)(0123567)

m

F A B C=∑,,,,,,

表6-1 74LS155功能表

6.1

3分,F2,3分,F1,4分

七、(10分)试用两片4位数码比较器74LS85组成三个数的判断电路。要求能够判别

三个4位二进制数()0123a a a a A 、()0123b b b b B 、()0123c c c c C 相等(输出F 1=0,F 2=1)及A 最大(输出F 1=1,F 2=0)。在图7.1上完成设计,可附加与门。(芯片74LS85的3个输出端,分别表示在A>B 时

Y A>B =1;A=B 时Y A=B =1;A

答案:评分:3个输入各2分,2个输出各2分

01230123

八、(10分)用或非门实现函数,,,)F

A B C D AC A BD A CD =+?+(,要求没有逻辑冒险。(1),将函数填入图8.1的卡诺图;(2),画出逻辑电路。

图8.1

答案:6分+4分

F

九、应用问题简答:

已知供电电压为5V 的74S 系列器件的I OH =-1mA ,I OL =20mA ,74LS 系列器件的I OH =-0.4mA ,I OL =8mA 。

5V

+5V

()

d ()

c ()b ()a

图9.1

1.现需驱动一个发光二极管(正向压降为 1.5V ),要求发光时的电流I LED =10mA 。

(1)应使用74S 系列还是74LS 系列器件?74S 系列(2分) (2)应使用图9.1(a )电路还是(b )电路?(b )电路(2分) (3)简述图中R 的作用。限流(2分)

2. 若需驱动一个5V 继电器,继电器的电流为I J =5mA 。(图中D 的作用是抑制自感生的高电压,起到保护器件的作用)。

(1)可以选择哪个系列的器件?74S 或74LS (2分)

(2)应使用图9.1(c )电路还是(d )电路?(d )电路(2分)

期末考试试题(答案) 考试科目:数字逻辑电路 试卷类别:3卷 考试时间:110 分钟 XXXX 学院 ______________系 级 班 姓名 学号 题号 一 二 三 四 总分 得分 一、选择题(每小题2分,共20分) 1. 八进制(273)8中,它的第三位数2 的位权为___B___。 A .(128)10 B .(64)10 C .(256)10 D .(8)10 2. 已知逻辑表达式C B C A AB F ++=,与它功能相等的函数表达式_____B____。 A .A B F = B . C AB F += C .C A AB F += D . C B AB F += 3. 数字系统中,采用____C____可以将减法运算转化为加法运算。 A . 原码 B .ASCII 码 C . 补码 D . BCD 码 4.对于如图所示波形,其反映的逻辑关系是___B_____。 A .与关系 B . 异或关系 C .同或关系 D .无法判断 5. 连续异或1985个1的结果是____B_____。 A .0 B .1 C .不确定 D .逻辑概念错误 得分 评卷人 装 订 线 内 请 勿 答 题

6. 与逻辑函数D C B A F+ + + =功能相等的表达式为___C_____。 D C B A F+ + + =B.D C B A F+ + + = D.D C B A F+ + = 7.下列所给三态门中,能实现C=0时,F=AB;C=1时,F为高阻态的逻辑功能的是____A______。 8. 如图所示电路,若输入CP脉冲的频率为100KHZ,则输出Q的频率为 _____D_____。 A.500KHz B.200KHz C.100KHz D.50KHz 9.下列器件中,属于时序部件的是_____A_____。 A.计数器B.译码器C.加法器D.多路选择器 装

2003数字逻辑考题 一 填空题 (每空1分,共15分) 1 [19]10=[ 11010 ]Gray (假设字长为5bit ) 2 若X=+1010,则[X]原=( 00001010 ),[-X]补=( 11110110 ),(假设字长为8bit ) 3 [26.125]10=[ 1A.2 ]16=[ 00100110.000100100101 ]8421BCD 4 65进制的同步计数器至少有( 7 )个计数输出端。 5 用移位寄存器产生11101000序列,至少需要( 3 )个触发器。 6 要使JK 触发器按'*Q Q =工作,则JK 触发器的激励方程应写为(1,1 );如果用D 触发器实现这一转换关系,则D 触发器的激励方程应写为( Q ’ )。 7 在最简状态分配中,若状态数为n ,则所需的最小状态变量数应为([log 2n] )。 8 有n 个逻辑变量A ,B ,C ….W ,若这n 个变量中含1的个数为奇数个,则这n 个变量相异或的结果应为( 1 )。 9 一个256x4bit 的ROM 最多能实现( 4 )个( 8 )输入的组合逻辑函数。 10 一个EPROM 有18条地址输入线,其内部存储单元有( 218 )个。 11 所示CMOS 电路如图Fig.1,其实现的逻辑函数为F=( A NAND B (AB)' ) (正逻辑)。 二 判断题 (每问2分,共10分) 1 ( T )计数模为2n 的扭环计数器所需的触发器为n 个。 2 ( F )若逻辑方程AB=AC 成立,则B=C 成立。 3 ( F )一个逻辑函数的全部最小项之积恒等于1。 4 ( T )CMOS 与非门的未用输入端应连在高电平上。 5 ( F )Mealy 型时序电路的输出只与当前的外部输入有关。 Fig.1 三 (16分) 1 化简下列函数(共6分,每题3分) 1) ()()∑=15,13,11,10,9,8,7,3,2,0,,,m D C B A F 2) ()()()∑∑+=14,5,3,013,12,10,8,6,1,,,d m D C B A F F +E D

北京邮电大学 《数字电路与逻辑设计》期中考试试题 2015.4.11 班级姓名班内序号 题号一二三四五六七八总成绩 分数20 12 10 10 10 20 10 8 得分 注意:所有答案(包括选择题和计算题)一律写在试卷纸上,如果卷面位置不够,请写在试卷的背后,否则不计成绩。 一、(每题1分,共20分)判断(填√或×)、单项选择题 (请先在本试卷上答题之后,将全部答案汇总到本题末尾的表格中。) 1.ECL逻辑门与TTL门相比,主要优点是抗干扰能力强。(╳)2.CMOS门电路在使用时允许输入端悬空,并且悬空的输入端相当于输入逻辑“1”。( ╳ ) 3.若对4位二进制码(B 3B 2 B 1 B )进行奇校验编码,则校验位C= B 3 ⊕B 2 ⊕B 1 ⊕B ⊕1。 (√) 4.根据表1-1,用CMOS4000系列的逻辑门驱动TTL74系列的逻辑门,驱动门与负载门之间的电平匹配不存在问题(√) 5. 根据表1-1,用CMOS4000系列的逻辑门驱动TTL74系列的逻辑门,驱动门与负载门之间的电流驱动能力不存在问题(╳) 表1-1常用的TTL和CMOS门的典型参数

6.当i j ≠时,必有两个最小项之和+0i j m m =。(╳) 7. CMOS 门电路的静态功耗很低,但在输入信号动态转换时会有较大的电流,工作频率越高,静态功耗越大。(╳) 8. 逻辑函数的表达式是不唯一的,但其标准的最小项之和的表达式是唯一的。(√) 9.用数据分配器加上门电路可以实现任意的逻辑函数。( √ ) 10.格雷BCD 码具有单位距离特性(任意两个相邻的编码之间仅有一位不同)且是无权代码。(√) 11.关于函数F A C BCD AB C =++g ,下列说法中正确的有 B 。 A. 不存在冒险; B. 存在静态逻辑冒险,需要加冗余项ABD 和ACD 进行消除; C. 存在静态功能冒险,需要加冗余项ABD 和ACD 进行消除; D. 当输入ABCD 从 0001→0100变化时存在静态逻辑冒险。 12.逻辑函数F=A ⊕B 和G=A ⊙B 满足关系 D 。 A.F G = B.0F G += C.1F G =g D.0F G =e 13.若逻辑函数∑=)6,3,2,1(),,(m C B A F ,∑=)7,5,4,3,2,0(),,(m C B A G ,则 =?G F A 。 A.32m m + B.1 C.AB D.AB 14.若干个具有三态输出的电路输出端接到一点工作时,必须保证 B 。 A.任何时刻最多只能有一个电路处于高阻态,其余应处于工作态。 B.任何时刻最多只能有一个电路处于工作态,其余应处于高阻态。 C.任何时刻至少有一个电路处于高阻态,其余应处于工作态。 D.任何时刻至少有一个电路处于工作态,其余应处于高阻态。 15.可以用来传输连续变化的模拟信号的电路是 D 。 A. 三态输出的门电路。; B. 漏极开路的CMOS 门电路; C. ECL 门电路; D. CMOS 传输门 16.逻辑表达式[()]F AB C D E B =++?的对偶式为 B 。

这是我以前到处搜刮来的,自己看看吧。 唐老师是中国网通集团宽带业务应用国家工程实验室副总共,兼职导师,硕士只有两个名额,博士有一个名额, 05年上院线的4个人都要了,06年,竞争比较激烈分比较高,07年上院线的4个,唐老师只有两个名额,要了两个,并且帮另外两个同学调剂到其他导师那里.08年,只有一个报考唐老师的上线,唐老师接受了一个调剂的. 其实所谓的方向,都是遇到什么做什么,并非那么死. 如果跟唐老师读研的话,运营商的各个方向,只要有兴趣,老师都会尽量给你实习的机会. 另外,如果能找到更好的实习机会或者出国,唐老师一定会积极鼓励的. 往年: 大宋(含宋梅)老师 350+ 刘杰老师350+ (这些年有刘杰老师偏高大宋老师走低的趋势) 老邓院长那320(招不满的情况下就另计了,会择优收一些调剂) 张校长(含王卫东老师) 320 新来的刘元安院长(含唐碧华老师)没有往年参考数据,前电院四小龙分低不了吧呵呵 新来的继教的老师没有参考数据不详 吕奶奶(依每年看情况不详) 光方向(不详) 写在前面的话:整个暑期都泡在北邮人考研版上,发现很多同学对与考研问题不断,但问题的重复率也很高,因此对此稍做整理,方便同学考研解惑,希望对你们有帮助 注:以下问题及其答案大部分都是在版块内搜集的,如有错误欢迎大家纠正 因为北邮院系改革,而且很多老师都没有到位,因此报考专业可能出现变化,一切以即将出的09招生简章为准

Q:北邮的研究生报考时给其他学校不一样,要先报导师,但不知道具体怎么回事 A:08时的计算机,使用的是报导师组(就是选定一个专业方向)的方式。如果考上了,那么复试就是在导师组内复试,调剂也优先考虑组内调剂,不行才会考虑组外调剂。 Q:北邮是否有专业课辅导班?如何报考? A:北邮本校是没有专业课辅导班。所谓的通原辅导班是由外面辅导机构所办。海文和北邮合作的专业课辅导是李莉,李宗豪讲,是北邮代课老师。但是在下特此声明,命题的老师不会也不可能出来讲课的,这是不允许的。 Q:该什么时候联系导师啊? A:保研的现在研究;考研的在报考前考虑一下,实际加紧联系就在出成绩那段时间了。 Q:请问院系重组对研究生学院有什么影响? A:暂时未知,有消息及时通知 Q:北邮计算机今年复试是不是要上机? A:08头一年上机,明年应该还会有 Q:08年电院分数线是多少?其他学院呢? A:电院320 信院305 计科300 电子300 Q:非应届毕业生一定要去北邮参加研究生考试么? A:答:不需要,各地有考试点 Q:信息工程院的密码学怎么样,专业课是考高等代数吗? A:信号通原数学都行,只有专业,导师到时候再分配 Q:电信工程院有哪些牛导? A:在外界看来电院最厉害的是三大牛导:张平王文博杨大成 Q:北邮考研有歧视吗? A:没有。这个问题很多人问过,老师一律平等对待,好好考好初试。 Q:北邮哪个老师做嵌入式的比较牛? A:邝坚 Q:复试的时候导师主要以什么作参考?导师比较看重什么?比如项目经验,学校? A:每个导师看中的方面都不一样,无法回答。好好过了初试再去费心复试的问题

数字逻辑第五章课后习题答案 5-1、解:(1) 列出电路的激励函数和输出函数表达式: 1111J K CP CP ==??=? 22321,1J Q K CP Q ?==??=?? 323331 ,1 J Q Q K CP Q ?==?? =?? Q 1n+1); Q 2n+1); Q 3 n+1) (2) (4) 功能描述:由状态图可知,此电路为一带自启动能力的六进制计数器。 1 2 3 4 5 6 7 8 CP Q 1 Q 2 Q 3 时间图

5-2、解:表5.29所示为最小化状态表,根据状态分配原则,无“列”相邻(行相邻在脉冲异步时序电路中不适用。),在“输出”相邻中,应给AD、AC分配相邻代码。取A为逻辑0,如下卡诺图所示,状态赋值为:A=00,B=11;C=01;D=10。于是,二进制状态表 如下,根据D触发器的激励表可画出CP2、D2、CP1、D1、Z的卡诺图, 二进制状态表 状态编码 D触发器的激励表

5-3、解: 原始状态图 5-4、解:(1)写出电路的激励函数和输出函数表达式: Y 2=x 2+x 12x 1(2)作状态流程表: (3)作时间图:

设输入状态x2x1的变化序列为00 01 11 10 00 10 11 01.初始总态为(x2x1,y2y1)=(00,00). 从本题的状态流程表推演出总响应序列为 总态响应序列表 x2 x1 y2 y1 Z 时间图 (4)电路功能:当输入状态x2x1的变化序列为01 11 10 00时,电路输出高电平1,其余情况输出低电平0.因此,该电平异步时序电路为01 11 10 00序列检测器。 5-5、解: 时间图如下

北京邮电大学历史沿革及历任校(院) 长简介 北京邮电大学简单介绍 北京邮电大学简称北邮(BUPT)位于北京市西土城路10号。是教育部直属、工业和信息化部共建、是我国信息科技人才的重要培养基地,是一所以信息科技为特色,工学门类为主体,工管文理相结合的多科性大学,是中国信息科技人才的重要培养基地,被誉为"信息通信的黄埔军校"。 北京邮电大学历史沿革 北京邮电大学创建于1955年,原名北京邮电学院,是以天津大学电讯系、电话电报通讯和无线电通信广播两个专业及重庆大学电机系电话电报通讯专业为基础组建的, 1993年经原国家教委批准,"北京邮电学院"更名为"北京邮电大学"。是中华人民共和国第一所邮电高等学府。原隶属邮电部,2000年全国院校调整后,直属教育部管理。 北京邮电大学设置极其所有专业 北京邮电大学设有信息与通信工程学院;计算机学院;经济管理学院;自动化学院;电子工程学院;人文学院;理学院;软件学院;国

际学院;民族教育学院;继续教育学院;网络学院等院。详细专业请登录官方网站或百度百科查询。 现任北京邮电大学校(院)长:方滨兴。国际代码(毕业证编号):10013 北京邮电大学历任校(院)长: 钟夫翔(1955年至1956年任北京邮电学院院长);孟贵民(1957年至1981年任北京邮电学院院长);叶培大(1981年至1985年任北京邮电学院院长);胡健栋(1985年至1989年任北京邮电学院院长);朱祥华(1989年至1998年任北京邮电大学校长);林金桐(1998年至2007年任北京邮电大学校长);方滨兴(2007年至今任北京邮电大学校长) 本文来自:https://www.doczj.com/doc/c17602093.html,/beijing/yangb/bjyddx.html 由https://www.doczj.com/doc/c17602093.html, https://www.doczj.com/doc/c17602093.html, https://www.doczj.com/doc/c17602093.html, https://www.doczj.com/doc/c17602093.html, https://www.doczj.com/doc/c17602093.html,整理上传

中国石油大学(北京)远程教育学院 《数字逻辑》期末复习题 一、单项选择题 1. TTL 门电路输入端悬空时,应视为( A ) A. 高电平 B. 低电平 C. 不定 D. 高阻 2. 最小项D C B A 的逻辑相邻项是( D ) A .ABCD B .D B C A C .C D AB D .BCD A 3. 全加器中向高位的进位1+i C 为( D ) A. i i i C B A ⊕⊕ B.i i i i i C B A B A )(⊕+ C.i i i C B A ++ D.i i i B C A )(⊕ 4. 一片十六选一数据选择器,它应有( A )位地址输入变量 A. 4 B. 5 C. 10 D. 16 5. 欲对78个信息以二进制代码表示,则最少需要( B )位二进制码 A. 4 B. 7 C. 78 D. 10 6. 十进制数25用8421BCD 码表示为(B ) A.10 101 B.0010 0101 C.100101 D.10101 7. 常用的BCD 码有(C ) A:奇偶校验码 B:格雷码 C:8421码 D:ASCII 码 8. 已知Y A AB AB =++,下列结果中正确的是(C ) A:Y=A B:Y=B C:Y=A+B D: Y A B =+ 9. 下列说法不正确的是( D ) A:同一个逻辑函数的不同描述方法之间可相互转换 B:任何一个逻辑函数都可以化成最小项之和的标准形式 C:具有逻辑相邻性的两个最小项都可以合并为一项 D:任一逻辑函数的最简与或式形式是唯一的 10. 逻辑函数的真值表如下表所示,其最简与或式是(C )

A: ABC ABC ABC ++ B: ABC ABC ABC ++ C: BC AB + D: BC AC + 11.以下不是逻辑代数重要规则的是( D ) 。 A. 代入规则 B. 反演规则 C. 对偶规则 D. 加法规则 12.已知函数E)D (C B A F +?+=的反函数应该是( A ) 。 A. [])E (D C B A F +?+?= B. [])E D (C B A F +?+?= C. [])E (D C B A F +?+?= D. [] )E D (C B A F +?+?= 13.组合逻辑电路一般由( A )组合而成。 A 、门电路 B 、触发器 C 、计数器 D 、寄存器 14.求一个逻辑函数F 的对偶式,可将F 中的( A )。 A 、“·”换成“+”,“+”换成“·”,常数中的“0”“1”互换 B 、原变量换成反变量,反变量换成原变量 C 、变量不变 D 、常数中的“0”换成“1”,“1”换成“0” 15.逻辑函数()()()()=++++=E A D A C A B A F ( A ) 。 A. AB+AC+AD+AE B. A+BCED C. (A+BC)(A+DE) D. A+B+C+D+E 16.下列逻辑电路中,不是组合逻辑电路的有( D ) A 、译码器 B 、编码器 C 、全加器 D 、寄存器 17.逻辑表达式A+BC=( C )

期末考试试题(答案) 一、选择题(每小题2分,共20分) 1.八进制(273)8中,它的第三位数2 的位权为___B___。 A.(128)10B.(64)10C.(256)10 D.(8)10 2. 已知逻辑表达式C B C A AB F+ + =,与它功能相等的函数表达式 _____B____。 A.AB F=B.C AB F+ = C.C A AB F+ =D.C B AB F+ = 3. 数字系统中,采用____C____可以将减法运算转化为加法运算。 A.原码B.ASCII码C.补码D.BCD码4.对于如图所示波形,其反映的逻辑关系是___B_____。 A.与关系B.异或关系C.同或关系D.无法判断 5.连续异或1985个1的结果是____B_____。 A.0B.1 C.不确定D.逻辑概念错误 6. 与逻辑函数D C B A F+ + + =功能相等的表达式为___C_____。 A.D C B A F+ + + =B.D C B A F+ + + = C.D C B A F=D.D C B A F+ + = 7.下列所给三态门中,能实现C=0时,F=AB;C=1时,F为高阻态的逻辑功能的是____A______。 B A F & ? F B A &

8. 如图所示电路,若输入CP脉冲的频率为100KHZ,则输出Q的频率为_____D_____。 A. 500KHz B.200KHz C. 100KHz D.50KHz 9.下列器件中,属于时序部件的是_____A_____。 A.计数器B.译码器C.加法器D.多路选择器 10.下图是共阴极七段LED数码管显示译码器框图,若要显示字符“5”,则译码器输出a~g应为____C______。 A. 0100100 B.1100011 C. 1011011 D.0011011 二、填空题(每小题2分,共20分) 11.TTL电路的电源是__5__V,高电平1对应的电压范围是__2.4-5____V。 12.N 个输入端的二进制译码器,共有___N2____个输出端。对于每一组输入代码,有____1____个输出端是有效电平。 13.给36个字符编码,至少需要____6______位二进制数。 14.存储12位二进制信息需要___12____个触发器。

数字逻辑试题1答案 一、填空:(每空1分,共20分) 1、(20.57)8 =( 10.BC )16 2、(63.25) 10= ( 111111.01 )2 3、(FF )16= ( 255 )10 4、[X]原=1.1101,真值X= -0.1101,[X]补 = 1.0011。 5、[X]反=0.1111,[X]补= 0.1111。 6、-9/16的补码为1.0111,反码为1.0110 。 7、已知葛莱码1000,其二进制码为1111, 已知十进制数为92,余三码为1100 0101 8、时序逻辑电路的输出不仅取决于当时的输入,还取决于电路的状态 。 9、逻辑代数的基本运算有三种,它们是_与_ 、_或__、_非_ 。 10、1⊕⊕=B A F ,其最小项之和形式为_ 。AB B A F += 11、RS 触发器的状态方程为_n n Q R S Q +=+1_,约束条件为0=SR 。 12、已知B A F ⊕=1、B A B A F +=2,则两式之间的逻辑关系相等。 13、将触发器的CP 时钟端不连接在一起的时序逻辑电路称之为_异_步时序逻辑电路 。 二、简答题(20分) 1、列出设计同步时序逻辑电路的步骤。(5分) 答:(1)、由实际问题列状态图 (2)、状态化简、编码 (3)、状态转换真值表、驱动表求驱动方程、输出方程 (4)、画逻辑图 (5)、检查自起动 2、化简)(B A B A ABC B A F +++=(5分) 答:0=F 3、分析以下电路,其中RCO 为进位输出。(5分) 答:7进制计数器。

4、下图为PLD 电路,在正确的位置添 * , 设计出B A F ⊕=函数。(5分) 5分 注:答案之一。 三、分析题(30分) 1、分析以下电路,说明电路功能。(10分) 解: ∑∑==) 7,4,2,1()7,6,5,3(m Y m X 2分 A B Ci X Y 0 0 0 0 0 0 0 1 0 1 0 1 0 0 1 0 1 1 1 0 1 0 0 0 1 1 0 1 1 0 1 1 0 1 0 1 1 1 1 1 8分

本科试卷(八) 一、选择题(每小题2分,共30分) 1.逻辑函数F1=∑m (2,3,4,8,9,10,14,15), 它们之间的关系是________。 A . B . C . D .、互为对偶式 2. 最小项的逻辑相邻项是________。 A .ABCD B. C. D. 3. 逻辑函数F (ABC )=A ⊙C 的最小项标准式为________。 A.F=∑(0,3) B. C.F=m 0+m 2+m 5+m 7 D. F=∑(0,1,6,7) 4. 一个四输入端与非门,使其输出为0的输入变量取值组合有_______种。 A. 15 B. 8 C. 7 D. 1 5. 设计一个四位二进制码的奇偶位发生器(假定采用偶检验码),需要_______个异或门。 A .2 B. 3 C. 4 D. 5 6. 八路数据选择器如图1-1所示,该电路实现的逻辑函数是F=______。 A . B . C . D . 图1-1 7. 下列电路中,不属于时序逻辑电路的是_______。 A .计数器 B .触发器 C .寄存器 D .译码器 8. 对于JK 触发器,输入J=0,K=1,CP 脉冲作用后,触发器的次态应为_____。 A .0 B. 1 C. 保持 D. 翻转 9. Moore 型时序电路的输出_____。 A.与当前输入有关 B. 与当前状态有关 C. 与当前输入和状态都有关 D. 与当前输入和状态都无关 2F ABC ABCD ABC ABC ACD =++++12F F =12F F =12F F =1F 2F ABCD ABCD ABCD ABCD C A C A F +=AB AB +AB AB +A B ⊕A B +

华东师范大学期末试卷(B) 2009 — 2010 学年第 一 学期 课程名称:___数字逻辑________ 学生姓名:___秦宽________________ 学 号:_2013041046__________________ 专 业:____软件工程_______ 年级/班级:13级软件工程 课程性质:公共必修、公共选修、专业必修、专业选修 一、填空题 (20分,每空2分) 1. (2010)D =( )B = ( )H = ( )8421BCD 答案:(111 1101 1010)B = (7DA )H = (0010 0000 0001 0000)8421BCD 2. 仓库门上装了两把暗锁,A 、B 两位保管员各管一把锁的钥匙,必须二人同时开锁才能进库。这种逻辑关系为 。 答案:与逻辑 3. 逻辑函数式F=AB+AC 的对偶式为 ,最小项表达式为∑=m F ( )。 答案:))((C A B A F D ++= ∑=m F (5,6,7) 2.逻辑函数D AC CD A C AB D C ABD ABC F ''''''+++++=的最简与或式是 。 答案:'D A + 4. 从结构上看,时序逻辑电路的基本单元是 。 答案:触发器 5. JK 触发器特征方程为 。 答案:Q K JQ ''+ 6.A/D 转换的一般步骤为:取样,保持, ,编码。 答案:量化

二、选择题 (20分,每题2分) 1. 计算机键盘上有101个键,若用二进制代码进行编码,至少应为( )位。 A) 6 B) 7 C) 8 D) 51 答案:B 2. 在函数F=AB+CD 的真值表中,F=1的状态有( )个。 A) 2 B) 4 C) 6 D) 7 答案:D 3. 为实现“线与”逻辑功能,应选用( )。 A) 与非门 B) 与门 C) 集电极开路(OC )门 D) 三态门 答案:C 4. 图1所示逻辑电路为( )。 A) “与非”门 B) “与”门 C)“或”门 D) “或非”门 图1 答案:A 5. 在下列逻辑部件中,属于组合逻辑电路的是( )。 A) 计数器 B) 数据选择器 C) 寄存器 D) 触发器 答案:B 6. 已知某触发器的时钟CP ,异步置0端为R D ,异步置1端为S D ,控制输入端V i 和输出Q 的波形如图2所示,根据波形可判断这个触发器是( )。 B C

1.电子电路分为模拟电子电路和数字电子电路。数值的度量采用直流电压或电流的连续值,称模拟量。 2.数字电路比模拟电路有许多优点。如:电路便于集成化、系列化生产,成本低廉,使用方便;抗干扰性强,可靠性高,精度高;处理功能强,不仅能实现数值运算,还可以实现逻辑运算和判断;可编程数字电路可容易地实现各种算法,具有很大的灵活性;数字信号更易于存储、加密、压缩、传输和再现。 3.数字量具有精度高、传输高效、易存储、易处理等优点(上升沿10%—90%) 4.自然码:有权码,每位代码都有固定权值,结构形式与二进制数完全相同,最大计数为2n-1,n为二进制数的位数 5.可靠性代码:(1) 奇偶校验码(2) 格雷码(Gray 码,又称循环码(循环码的一种)<格雷码的特点是任何相邻的两个码组中,仅有一位代码不同,抗干扰能力强,主要用在计数器中> 6.数字电路是传递和处理数字信号的电子电路。它有组合逻辑电路和时序逻辑电路两大类。 7.数字电路的优点:便于高度集成化,工作可靠性强,抗干扰能力强,保密性好等。 8.时序逻辑电路中一定包含:触发器。时序电路中必须有:时钟。从本质上讲,控制器是一种时序电路。时序逻辑电路:逻辑功能特点:任何时刻的输出不仅取决于该时刻的输入信号(输入变量)的状态,而且与电路原有的状态(原来的输出)(Qn+1 = f(Qn, input))有关。即历史状态相关性。时序逻辑电路具有记忆功能(适当的控制) 电路结构特点:由存储电路和组合逻辑电路组成。包含锁存器或触发器它的输出往往反馈到输入端,与输入变量一起决定电路的输出状态。 //时序逻辑电路的类型(都跟触发器或其组合有关)同步时序逻辑电路:所有触发器的时钟端连在一起。所有触发器在同一个时钟脉冲CP 控制下同步工作。 异步时序逻辑电路:时钟脉冲CP 只触发部分触发器,其余触发器由电路内部信号触发。因此,触发器不在同一时钟作用下同步工作。 9.一位十进制计数器至少需要4个触发器 10.锁存器、触发器和门电路是构成数字电路的基本单元。 锁存器、触发器有记忆功能,由它构成的电路在某时刻的输出不仅取决于该时刻的输入,还与电路原来状态有关。而门电路(组合电路)无记忆功能,由它构成的电路在某时刻的输出完全取决于该时刻的输入,与电路原来状态无关 11.布尔代数的三个最重要规则是代入规则,反演规则和对偶规划 12.数字量的特定是数值为离散量,运算结果也是离散量。 13.二进制系统的两个数字0和1是一个开关量,常称比特。用来表示1和0的电平称为逻辑电平。 14.自然二进制有叫有权码。循环码(又叫单位距离码):任何相邻的两个码字中,仅有一位不同。 15.二进制对十进制编码,简称BCD码。8421码(eg:1592是0001 0101 1001 0010)<当相加和大于9时加6修正,无1010~1111>余3码:在8421码的基础上加0011。优点执行十进制相加时,能正确的产生进位信号,而且会给减法运算带来方便。格雷码是使任何两个相邻的代码只有一个二进制状态不同(主要用于计数器)。格雷码是一种循环码。无权码:余 3 码和格雷码。有利于得到更好的译码波形。可靠性代码(奇偶校验码,格雷码) 16.化简的意义:使逻辑式最简,以便设计出最简的逻辑电路,从而节省元器件,优化生产工艺,降低成本和提高系统可靠性。 17.逻辑函数的描述工具:布尔代数{(布尔代数中的变量称为逻辑变量)<0和1代表两种对立的逻辑状态>};真值表(n变量,2^n种可能);逻辑图法();卡诺图法(变量数基本上少于5);波形图;硬件描述语言法。 18.正逻辑,负逻辑,三态门(逻辑1,逻辑0,高阻抗)<使能端有效时(逻辑1)输出状态取决于输入状态> 19.卡诺图

………密………封………线………以………内………答………题………无………效…… 电子科技大学2012 -2013学年第二学期期末考试 A 卷 课程名称:_数字逻辑设计及应用__ 考试形式:闭卷考试日期: 20 13 年 07 月05 日 考试时长:_120___分钟 课程成绩构成:平时 30 %,期中 30 %,实验0 %,期末 40 % 本试卷试题由___七__部分构成,共__7___页。 题号一二三四五六七八九十合计 得分 I. Fill out your answers in the blanks (3’ X 10=30’) 1. If a 74x138 binary decoder has 110 on its inputs CBA, the active LOW output Y5 should be ( 1 or high ). 2. If the next state of the unused states are marked as “don’t-cares” when designing a finite state machine, this approach is called minimal ( cost ) approach. 3.The RCO_L of 4-bit counter 74x169 is ( 0 or low) when counting to 0000 in decreasing order. 4. To design a "001010" serial sequence generator by shift registers, the shift register should need ( 4 ) bit at least. 5. One state transition equation is Q* = JQ’+K’Q. If we use T flip-flop with enable to complete the equation,the enable input of T flip-flop should have the function EN = ( JQ’+KQ ). (参见课件Flip-flops Transforming Skills.ppt) 6. A 4-bit Binary counter can have ( 16 ) normal states at most, 4-bit Johnson counter with no self-correction can have ( 8 ) normal states, 4-bit linear feedback shift-register (LFSR) counter with self-correction can have ( 16 ) normal states. 7. If we use a ROM, whose capacity is 16 × 4 bits, to construct a 4-bit binary code to gray code converter, when the address inputs are 1001, ( 1101) will be the output. 8. When the input is 10000000 of an 8 bit DAC, the corresponding output voltage is 2V. The output voltage is

2012北邮数字逻辑期中试题-评分及答案

北京邮电大学 《数字电路与逻辑设计》期中考试试题 2012.3.24 班级姓名班内序号 题号一二三四五六七八九 总成 绩 分 数 20 10 10 10 10 10 10 10 10 注意:所有答案(包括选择题和计算题)一律写在试卷纸上,如果卷面位置不够,请写在试卷的背后,否则不计成绩。 一、(每题1分,共20分)判断(填√或×)、选择(单项选择)题 (请先在本试卷上答题之后,将全部答案汇总到本题末尾的表格中。)1.组合逻辑电路中不存在记忆单元。(√) 2.晶体管的饱和越深,其对灌电流负载的驱动能力越强,但工作速度越慢。( √ ) 3.TTL门的某输入端通过100KΩ电阻接电源端时,可认为该输入是逻辑“1”。(√) 4.为了增加驱动能力,相同输入时的相同逻辑门输出可以互连在一起使用。 2

3 ( √ ) 5.当两个或两个以上输入信号同时变化,变化前后输出相同,而在输入信号变化时可能出现输出瞬间逻辑错误,称为静态逻辑冒险。( × ) 6.正逻辑的或非门,对应负逻辑的与非门。( √ ) 7.TTL 与非门的关门电平V OFF 越接近阈值电压V T ,其噪声容限越大。( √ ) 8.当i j ≠时,必有两个最大项之积0i j M M ?=。( × ) 9. 用最简与或式表示一个函数时,其表达式可能不是唯一的。( √ ) 10.反相器的拉电流负载电阻过小时,主要对输出的高电平产生影响。( √ ) 11.逻辑项ABCD 的相邻项有: C 。 A.ABCD B.BCD A C.ABC D ? D. C A B D ? 12.判断下列两个函数式中,是否存在逻辑冒险。 B 。 1(,,)Y A B C A BC =+ 2(,,)Y A B C ABC ABC =+ A.不存在,存在 B. 不存在,不存在 C.存在,不存在 D. 存在,存在 13.通过适当连接和控制,可以实现数据双向传输的门电路是 D 。 A. 集电极开路输出的TTL 门电路; B. 互补式输出的TTL 门电路; C. ECL 门电路; D. 三态输出的门电路。 14.若某TTL 门电路的输出端最大灌电流负载能力为16mA ,最大拉电流负载能力为-12mA(流出输出端)。其输入端低电平的输入最大电流为-1mA(流出输入端),输入端高电平时的输入最大电流为0.1mA(流入输入端),该门电路的扇出系数为: A 。 A . 16 B. 120 C. 12 D. 160 15.图1.1中电路为TTL 电路。不能实现对应逻辑功能的电路有 A 。 & A A 1 ≥A A 1 =A A A B 图1.1

北京邮电大学 授予具有研究生毕业同等学力人员硕士、博士学位 工作细则 第一章总则 第一条:根据《中华人民共和国学位条例》、《中华人民共和国学位条例暂行实施办法》及《国务院学位委员会关于授予具有研究生毕业同等学力人员硕士、博士学位的规定》的规定,结合我校具体情况制订本细则。 第二条:凡是拥护《中华人民共和国宪法》,遵守法律、法规,品行端正,在教学、科研、专门技术、管理等方面做出成绩,具有研究生毕业同等学力,学术水平或专门技术水平已达到学位授予标准的人员,均可按本细则规定申请相应的学位。申请人不得同时向我校和其它学位授予单位提出申请。 第三条:我校经国务院学位委员会批准获权的博士、硕士学科专业均可开展同等学力申请学位工作。 第四条:硕士、博士学位授予的标准按照《中华人民共和国学位条例》和《中华人民共和国学位条例暂行实施办法》及《北京邮电大学学位授予工作细则》的规定执行。 第二章硕士学位申请人资格审查及学位申请办法第五条:申请人必须已获得学士学位,并在获得学士学位后工作三年以上,在申请学位的专业或相近专业做出成绩。

第六条:申请人应在规定期限内提交以下材料: 1、学士学位证书(原件)、最后学历证明(原件),及复印件各一份; 2、已发表或出版的与申请学位专业相关的学术论文、专著或其它成果的有关证明原件及复印件一份; 3、申请人所在单位提供的申请人的简历、思想政治表现、工作成绩、科研成果、业务能力、理论基础、专业知识和外语程度等方面情况的材料(加印密封); 4、跨专业申请者应提交补修所申请专业本科段的两门专业基础课和两门专业课的成绩单。 第七条:我校每年四月份受理同等学力人员申请硕士学位,申请人持第六条规定的材料到研究生部办理申请。经资格审查后,每年七月底之前书面通知申请人是否接受其申请。 第三章硕士学位申请人专业知识结构及水平的认定第八条:申请人必须按照接受申请当年我校《研究生培养方案》的规定,修满相应学科专业攻读硕士学位研究生的全部课程,考试合格,由研究生部建立申请人考试成绩档案。凡课程考试不符合我校《研究生培养方案》或未经我校批准在外校所修的研究生课程,其成绩不予认可。 第九条:申请人课程学习可按以下办法执行: 1、跟随我校研究生同堂学习,同卷同时考试,成绩合格,取得相应的学分。 2、通过自学后直接申请课程考试,考试由研究生部组织,在每学

邮电大学 《数字电路与逻辑设计》期中考试试题 2015.4.11 班级班序号 注意:所有答案(包括选择题和计算题)一律写在试卷纸上,如果卷面位置不够,请写在试卷的背后,否则不计成绩。 一、(每题1分,共20分)判断(填√或×)、单项选择题 (请先在本试卷上答题之后,将全部答案汇总到本题末尾的表格中。)1.ECL逻辑门与TTL门相比,主要优点是抗干扰能力强。(╳)2.CMOS门电路在使用时允许输入端悬空,并且悬空的输入端相当于输入逻辑“1”。( ╳) 3.若对4位二进制码(B3B2B1B0)进行奇校验编码,则校验位C= B3⊕B2⊕B1⊕B0⊕1。(√) 4.根据表1-1,用CMOS4000系列的逻辑门驱动TTL74系列的逻辑门,驱动门与负载门之间的电平匹配不存在问题(√) 5. 根据表1-1,用CMOS4000系列的逻辑门驱动TTL74系列的逻辑门,驱动门与负载门之间的电流驱动能力不存在问题(╳) 表1-1常用的TTL和CMOS门的典型参数

6.当i j ≠时,必有两个最小项之和+0 m m=。(╳) i j 7. CMOS门电路的静态功耗很低,但在输入信号动态转换时会有较大的电流,工作频率越高,静态功耗越大。(╳) 8. 逻辑函数的表达式是不唯一的,但其标准的最小项之和的表达式是唯一的。(√) 9.用数据分配器加上门电路可以实现任意的逻辑函数。(√) 10.格雷BCD码具有单位距离特性(任意两个相邻的编码之间仅有一位不同)且是无权代码。(√) =++g,下列说法中正确的有 B 。11.关于函数F A C BCD AB C A. 不存在冒险; B. 存在静态逻辑冒险,需要加冗余项ABD和ACD进行消除; C. 存在静态功能冒险,需要加冗余项ABD和ACD进行消除; D. 当输入ABCD从0001→0100变化时存在静态逻辑冒险。 12.逻辑函数F=A⊕B和G=A⊙B满足关系D。

学习中心/函授站_ 姓名学号 西安电子科技大学网络与继续教育学院 2020 学年下学期 《数字逻辑电路》期末考试试题 (综合大作业) 题号一二三四总分 题分30 10 30 30 得分 考试说明: 1、大作业试题于2020 年10 月15 日公布: (1)毕业班学生于2020 年10 月15 日至2020 年11 月1 日在线上传大作业答卷; (2)非毕业班学生于2020 年10 月22 日至2020 年11 月8 日在线上传大作业答卷; (3)上传时一张图片对应一张A4 纸答题纸,要求拍照清晰、上传完整; 2、考试必须独立完成,如发现抄袭、雷同均按零分计; 3、答案须用《西安电子科技大学网络与继续教育学院标准答题纸》手写 完成,要求字迹工整、卷面干净。 一、单项选择题(每小题2 分,共40 分) 1、下列各数中与十进制数101 不相等的数是( D )。 A.(0100 0011 0100)余3BCD B.(141)8C.(1100101)2D.(66)16 2、八进制数(35)8的8421BCD 是( B )。 A.0011 1000B.0010 1001C.0011 0101D.0010 1100 3、为使与非门输出为1 则输入( A )。 A.只要有0 即可B.必须全为0C.必须全为1D.只要有1 即可 4、函数F AC BC AB与其相等的表达式是( B )。 A.BC B.C+AB C.AC AB D.AB

5、使函数F AB AC BC 等于 0 的输入 ABC 的组合是( C )。 A .ABC=111 B .ABC=110 C .ABC=100 D .ABC=011 6、四变量的最小项ABCD 的逻辑相邻项是( A )。 A .ABCD B .ABCD C .ABC D D .ABCD 7、函数F ABC B .C (A D )BC 的对偶式是( C )。 A . G (A B C )(B C )(AD B C ) B .G A B C (B C )AD B C C .G A B C (B C )(A D B C ) D .G A B C (B C )A D B C 8、F A B C ADE BDE ABC 的最简式为( A )。 A .1 B .ABC DE C .ABC D .A+BDE+CDE 9、 函数F AC BC AB 的最简与非式为( D )。 10、 函数F A B C A .B .D AC ACD AB .D 的最简与或式为 ( D )。 A .F BC AD B .F B C AD C .F AB AC BD D .F AB AC BD 11、 函数F (ABCD ) (0,1,3,4,5,7,12),约束条件为BCD ABD 0 ,其 最简与或非式是( C )。 A .F A .C AD BD B .F CD AB AD A . B . C . D . B A B A C B C B B A . C A B A . . A B C A