邮电大学

《数字电路与逻辑设计》期中考试试题 2015.4.11

班级班序号

题号一二三四五六七八总成绩

分数20 12 10 10 10 20 10 8

得分

注意:所有答案(包括选择题和计算题)一律写在试卷纸上,如果卷面位置不够,请写在试卷的背后,否则不计成绩。

一、(每题1分,共20分)判断(填√或×)、单项选择题

(请先在本试卷上答题之后,将全部答案汇总到本题末尾的表格中。)

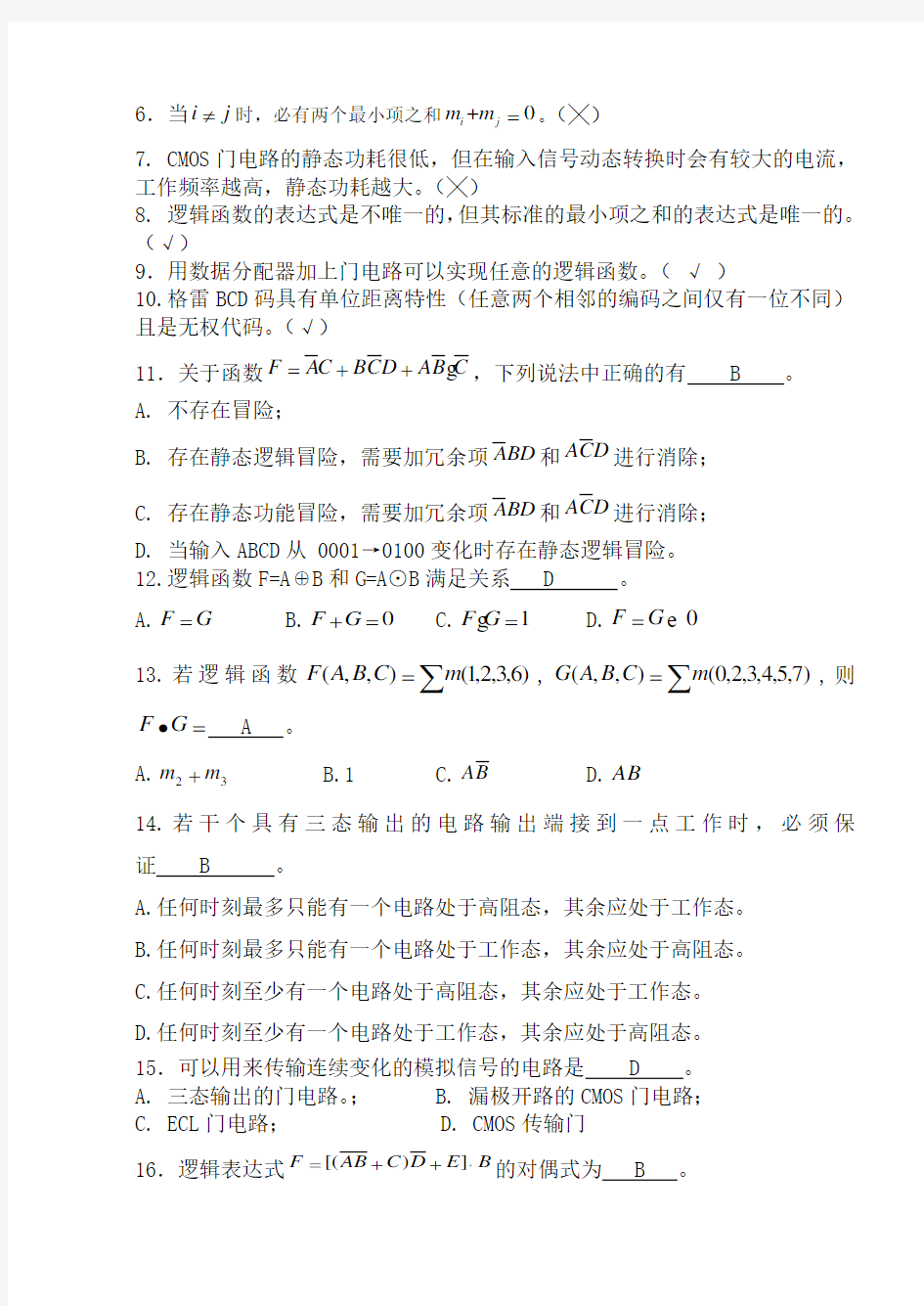

1.ECL逻辑门与TTL门相比,主要优点是抗干扰能力强。(╳)2.CMOS门电路在使用时允许输入端悬空,并且悬空的输入端相当于输入逻辑“1”。( ╳ )

3.若对4位二进制码(B

3B

2

B

1

B

)进行奇校验编码,则校验位C= B

3

⊕B

2

⊕B

1

⊕B

⊕1。

(√)

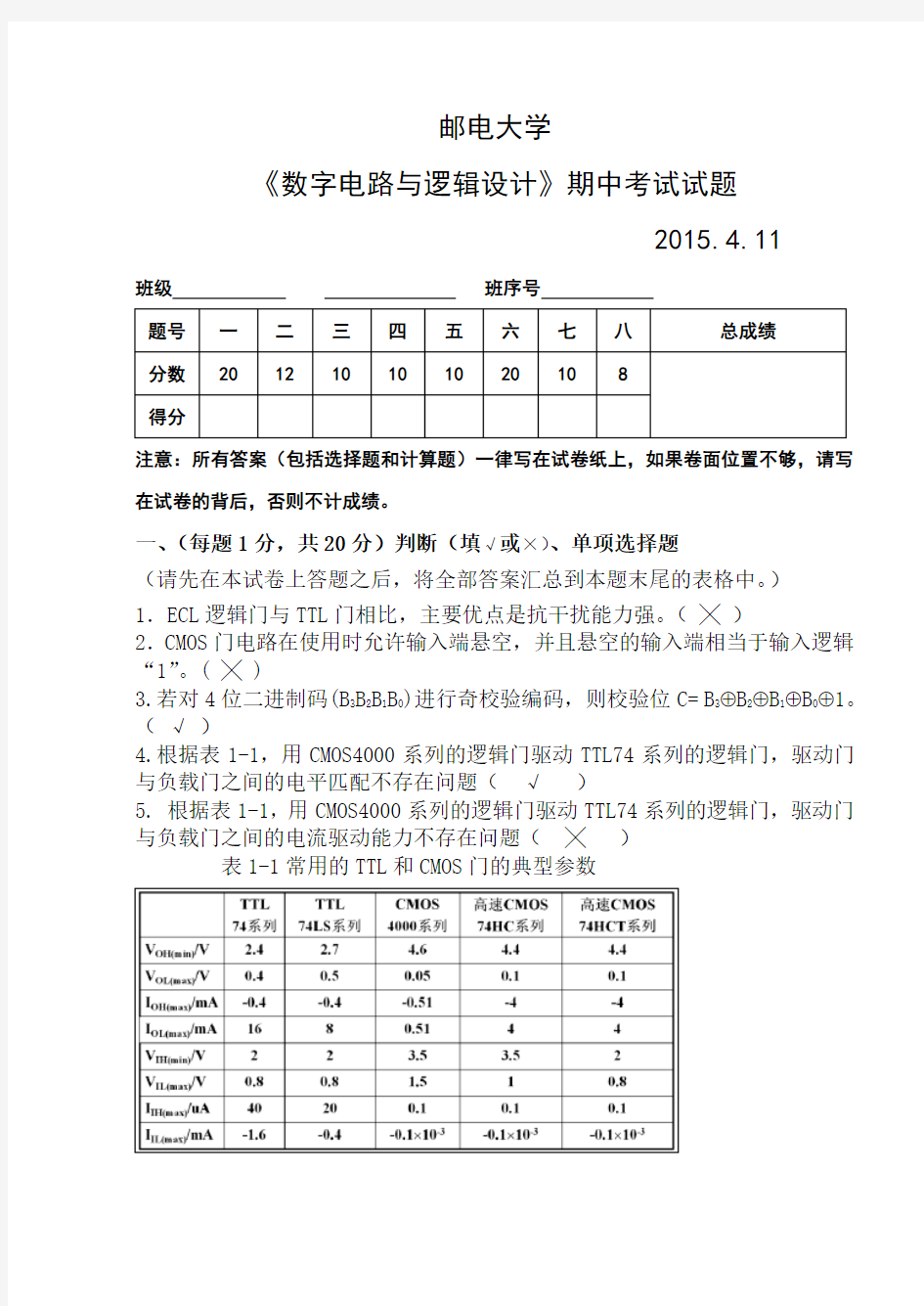

4.根据表1-1,用CMOS4000系列的逻辑门驱动TTL74系列的逻辑门,驱动门与负载门之间的电平匹配不存在问题(√)

5. 根据表1-1,用CMOS4000系列的逻辑门驱动TTL74系列的逻辑门,驱动门与负载门之间的电流驱动能力不存在问题(╳)

表1-1常用的TTL和CMOS门的典型参数

6.当i j ≠时,必有两个最小项之和+0i j m m =。(╳)

7. CMOS 门电路的静态功耗很低,但在输入信号动态转换时会有较大的电流,工作频率越高,静态功耗越大。(╳) 8. 逻辑函数的表达式是不唯一的,但其标准的最小项之和的表达式是唯一的。(√)

9.用数据分配器加上门电路可以实现任意的逻辑函数。( √ )

10.格雷BCD 码具有单位距离特性(任意两个相邻的编码之间仅有一位不同)且是无权代码。(√) 11.关于函数F A C BCD AB C =++g ,下列说法中正确的有 B 。 A. 不存在冒险;

B. 存在静态逻辑冒险,需要加冗余项ABD 和ACD 进行消除;

C. 存在静态功能冒险,需要加冗余项ABD 和ACD 进行消除;

D. 当输入ABCD 从 0001→0100变化时存在静态逻辑冒险。 12.逻辑函数F=A ⊕B 和G=A ⊙B 满足关系 D 。 A.F G =

B.0F G +=

C.1F G =g

D.0F G =e

13.若逻辑函数∑=)6,3,2,1(),,(m C B A F ,∑=)7,5,4,3,2,0(),,(m C B A G ,则

=?G F A 。 A.32m m +

B.1

C.AB

D.AB

14.若干个具有三态输出的电路输出端接到一点工作时,必须保证 B 。

A.任何时刻最多只能有一个电路处于高阻态,其余应处于工作态。

B.任何时刻最多只能有一个电路处于工作态,其余应处于高阻态。

C.任何时刻至少有一个电路处于高阻态,其余应处于工作态。

D.任何时刻至少有一个电路处于工作态,其余应处于高阻态。 15.可以用来传输连续变化的模拟信号的电路是 D 。

A. 三态输出的门电路。;

B. 漏极开路的CMOS 门电路;

C. ECL 门电路;

D. CMOS 传输门

16.逻辑表达式[()]F AB C D E B =++?的对偶式为 B 。

A . [()]F A

B

C

D

E B =+?+?+ B. ()

F A B C D E B =+?+?+

C. ()F

A B C D E B =++?+ D. [()]F AB C D E B =++?

17.下列说法中正确的是 D 。

A .三态门的输出端可以直接并联,实现线或逻辑功能。 B. OC 门的输出端可以直接并联,实现线或逻辑功能。 C .OD 门的输出端可以直接并联,实现线或逻辑功能。 D .ECL 门的输出端可以直接并联,实现线或逻辑功能。

18.某集成电路芯片,查手册知其最大输出低电平U OLmax =0.5V ,最大输入低电平U ILmax =0.8V ,最小输出高电平U OHmin =2.7V ,最小输入高电平U IHmin =2.0V ,则其低电平噪声容限U NL 和高电平噪声容限U NH 分别是 C 。

A. 1.5V 、2.2V

B.2.2V 、1.2V

C. 0.3V 、0.7V

D.1.9V 、1.5V 19.下列说法中不属于组合电路的特点的是 C 。 A. 组合电路由逻辑门构成; B. 组合电路不含记忆存储单元; C. 组合电路的输出到输入有反馈回路;

D.任何时刻组合电路的输出只与当时的输入有关,而与电路过去的输入无关。 20.在图1-1的CMOS 门电路中,输出为高电平的有 D 。

V

A. B. C. D. 图1-1

二、(共12分)器件的部电路如图2-1所示,A ,B 为输入,F 为输出。(1),写出L 、M 、N 、O 、F 点与输入A 、B 间的相对逻辑关系表达式。(2),画出该器件的符号。 解:

(1)L=AB M=CD

N AB CD =+ O AB CD =+ F N O AB CD ===+

(10分)

图2-1

(2) (2分)

三、(10分) 请用最少的或非门设计一个检出8421BCD 码能被4整除的逻辑电路(输入变量为ABCD ,且提供反变量):

(1)根据功能需求完成表3-1真值表的填写;

(2)并写出该函数的标准与或表达式(使用;F =∑ +∑ 形式); (3)将真值表填入图3-1的卡诺图,并用卡诺图法简化为最简或与式; (4)用或非门实现该函数,画出逻辑图。

表3-1

图3-1

解:真值表(2分)

1000 1 1001

0 1010 ╳ 1011 ╳ 1100 ╳ 1101 ╳ 1110 ╳ 1111

╳

(0,4,8)(10,11,12,13,14,15)F m ?=∑+∑ (2分)

AB

CD 000001011111

1010

100

0010

10????

?

?(2分)

F D C =?(2分) (2分)

四、(10分)请用代数法化简函数()F AB A B ABD C D E F =+⊕+++e 为最简与或表达式,画出实现此逻辑函数的最简CMOS 电路。 解:

()()F AB A B ABD C D E F AB AB AB A B D C D E F B AB A B A B =+⊕+++=+++++++=+=+=?e e

(化简8分,图2分)

S A C B S S +A 2A 1A 07

Y 6Y 5Y 4Y 3Y 2Y 1Y 0Y 11111111

00000000

000011110011001101010101

0111111110111111110111111110111111110111111110111111110111111110

111111111111011111????????

五、(10分)TTL 门构成的电路如图5-1所示,请给电阻R L 选择合适的阻值。已知OC 门输出管截止时的漏电流为I OH =200μA ,OC 门输出管导通时允许的最大负载电流为I OLmax =16mA ;负载门的低电平输入电流为I IL =1mA ,高电平输入电流为I IH =40μA , V CC ′=5V ,要求OC 门的输出高电平V OH ≥3.0V ,输出低电平V OL ≤0.4V 。 解:

n=2 m=7 m′=4

图5-1 (5

分/个)

六、(20分)求函数F=(A+B )(B+C )(A+C )的标准与或表达式,并分别用译码器74LS138(输出低电平有效,功能表见6-1)、数据选择器75LS153(功能表见6-2)、数据分配器74LS155(功能表见6-3)和最少的门电路实现此函数(输入不提供反变量,在图6-1所给的符号图上完成) 。

表6-1 74LS138功能表 表6-2 74LS153功能表

表6-3 74LS155功能表

min 'CC OH L OH IH V V R nI mI -≤+''max CC OL L OL IL V V R I m I -≥-min '53 2.9420.270.04CC OH L OH IH V V R K nI mI --≤==Ω

+?+?max '50.4

0.381641

CC OL L OL IL V V R K I m I --≥

=≈Ω

'--?ST

A 1 A 0

D 3-D 0

Y 10000

0011

0101

?

?

?

D 3-D 0D 3-D 0D 3-D 0D 3-D 0

0D 0D 1D 2D 3

EN

74LS138&

A 1

A 2

A A S

B S C

S 0Y 1Y 2Y 3Y 4Y 5Y 6Y 7

Y A

C

B

C

图6-1 解:

F=(A+B )(B+C )(A+C ) =BC A C B A ABC C AB +++ =∑m (3,5,6,7)(2分)

(18分)

七、(10分)逻辑函数

(,,,)F A B C D ABD ACD AB C D =++??。已知该函数的约束条

件为0A B C ABCD ??+=, (1)将逻辑函数及约束条件填入图7-1,利用卡诺图将函数化简为最简与或表达式;(2)将逻辑函数及约束条件填入图7-2,利用卡诺图简化为最简与或非表达式。 AB CD 0001

010011

10

1110

AB CD 0001

010011

10

1110

图7-1 图7-2 解:

(1)

AB CD 0001010011101110

11

1

1??

?

00000

00(2分)

F A D B C D =?+??(3分)

(2)

AB CD 0001010011101110

11

1

1??

?

00000

00(2分)

a 3>

b 3a 3 b 3a 0 b 0a 1 b 1a 2 b 2A>B A

输 出

比 较 输 入级联输入'''E S G a 3b 2???a 1>b 1a 1b 0a 0

1100000000000000000

00

000

0?????

??????????????????F AB AC D =++(3分)

八、(8分)由四位数码比较器7485(功能表见表8-1)和四位加法器74283构成的电路如图8-1所示,若输入为2421BCD 码,(1)在真值表8-2中完成输出的填写;(2)说明该电路完成什么编码的转换。

表8-1 7485的功能表

I

I

I

I Y3

Y2

Y1

Y0

图8-1

解:

(1)(5分)

(2)2421BCD----8421BCD(3分)

期末考试试题(答案) 考试科目:数字逻辑电路 试卷类别:3卷 考试时间:110 分钟 XXXX 学院 ______________系 级 班 姓名 学号 题号 一 二 三 四 总分 得分 一、选择题(每小题2分,共20分) 1. 八进制(273)8中,它的第三位数2 的位权为___B___。 A .(128)10 B .(64)10 C .(256)10 D .(8)10 2. 已知逻辑表达式C B C A AB F ++=,与它功能相等的函数表达式_____B____。 A .A B F = B . C AB F += C .C A AB F += D . C B AB F += 3. 数字系统中,采用____C____可以将减法运算转化为加法运算。 A . 原码 B .ASCII 码 C . 补码 D . BCD 码 4.对于如图所示波形,其反映的逻辑关系是___B_____。 A .与关系 B . 异或关系 C .同或关系 D .无法判断 5. 连续异或1985个1的结果是____B_____。 A .0 B .1 C .不确定 D .逻辑概念错误 得分 评卷人 装 订 线 内 请 勿 答 题

6. 与逻辑函数D C B A F+ + + =功能相等的表达式为___C_____。 D C B A F+ + + =B.D C B A F+ + + = D.D C B A F+ + = 7.下列所给三态门中,能实现C=0时,F=AB;C=1时,F为高阻态的逻辑功能的是____A______。 8. 如图所示电路,若输入CP脉冲的频率为100KHZ,则输出Q的频率为 _____D_____。 A.500KHz B.200KHz C.100KHz D.50KHz 9.下列器件中,属于时序部件的是_____A_____。 A.计数器B.译码器C.加法器D.多路选择器 装

电子科技大学 UNIVERSITY OF ELECTRONIC SCIENCE AND TECHNOLOGY OF CHINA 数字逻辑设计 实验报告 实验题目:电子秒表 学生姓名: 指导老师:

一、实验内容 利用FPGA设计一个电子秒表,计时范围00.00 ~ 99.00秒,最多连续记录3个成绩,由两键控制。 二、实验要求 1、实现计时功能: 域值范围为00.00 ~ 99.00秒,分辨率0.01秒,在数码管上显示。 2、两键控制与三次记录: 1键实现“开始”、“记录”等功能,2键实现“显示”、“重置”等功能。 系统上电复位后,按下1键“开始”后,开始计时,记录的时间一直显示在数码管上;按下1键“记录第一次”,次按1键“记录第二次”,再按1键“记录第三次”,分别记录三次时间。 其后按下2键“显示第一次”,次按2键“显示第二次”,再按2键“显示第三次”,数码管上分别显示此前三次记录的时间;显示完成后,按2键“重置”,所有数据清零,此时再按1键“开始”重复上述计时功能。 三、设计思路 1、整体设计思路 先对按键进行去抖操作,以正确的得到按键信息。 同时将按键信息对应到状态机中,状态机中的状态有:理想状态、开始状态、3次记录、3次显示、以及其之间的7次等待状态。 因为需要用数码管显示,故显示的过程中需要对数码管进行片选和段选,因此要用到4输入的多路选择器。 在去抖、计时、显示的过程中,都需要用到分频,从而得到理想频率的时钟信号。 2、分频设计 该实验中有3个地方需要用到分频操作,即去抖分频(需得到200HZ时钟)、计时分频(需得到100HZ时钟)和显示分频(需得到25kHZ时钟)。 分频的具体实现很简单,需首先算出系统时钟(50MHZ)和所需始终的频率比T,并定义一个计数变量count,当系统时钟的上升沿每来到一次,count就加1,当count=T时就将其置回1。这样只要令count=1~T/2时clk=‘0’,count=T/2+1~T时clk=‘1’即可。 3、去抖设计 由于用按键为机械弹性开关,故当机械触点断开、闭合时,按键开关在闭合时不会马上稳定地接通,在断开时也不会马上断开,而是在闭合及断开的瞬

北京邮电大学 《数字电路与逻辑设计》期中考试试题 2015.4.11 班级姓名班内序号 题号一二三四五六七八总成绩 分数20 12 10 10 10 20 10 8 得分 注意:所有答案(包括选择题和计算题)一律写在试卷纸上,如果卷面位置不够,请写在试卷的背后,否则不计成绩。 一、(每题1分,共20分)判断(填√或×)、单项选择题 (请先在本试卷上答题之后,将全部答案汇总到本题末尾的表格中。) 1.ECL逻辑门与TTL门相比,主要优点是抗干扰能力强。(╳)2.CMOS门电路在使用时允许输入端悬空,并且悬空的输入端相当于输入逻辑“1”。( ╳ ) 3.若对4位二进制码(B 3B 2 B 1 B )进行奇校验编码,则校验位C= B 3 ⊕B 2 ⊕B 1 ⊕B ⊕1。 (√) 4.根据表1-1,用CMOS4000系列的逻辑门驱动TTL74系列的逻辑门,驱动门与负载门之间的电平匹配不存在问题(√) 5. 根据表1-1,用CMOS4000系列的逻辑门驱动TTL74系列的逻辑门,驱动门与负载门之间的电流驱动能力不存在问题(╳) 表1-1常用的TTL和CMOS门的典型参数

6.当i j ≠时,必有两个最小项之和+0i j m m =。(╳) 7. CMOS 门电路的静态功耗很低,但在输入信号动态转换时会有较大的电流,工作频率越高,静态功耗越大。(╳) 8. 逻辑函数的表达式是不唯一的,但其标准的最小项之和的表达式是唯一的。(√) 9.用数据分配器加上门电路可以实现任意的逻辑函数。( √ ) 10.格雷BCD 码具有单位距离特性(任意两个相邻的编码之间仅有一位不同)且是无权代码。(√) 11.关于函数F A C BCD AB C =++g ,下列说法中正确的有 B 。 A. 不存在冒险; B. 存在静态逻辑冒险,需要加冗余项ABD 和ACD 进行消除; C. 存在静态功能冒险,需要加冗余项ABD 和ACD 进行消除; D. 当输入ABCD 从 0001→0100变化时存在静态逻辑冒险。 12.逻辑函数F=A ⊕B 和G=A ⊙B 满足关系 D 。 A.F G = B.0F G += C.1F G =g D.0F G =e 13.若逻辑函数∑=)6,3,2,1(),,(m C B A F ,∑=)7,5,4,3,2,0(),,(m C B A G ,则 =?G F A 。 A.32m m + B.1 C.AB D.AB 14.若干个具有三态输出的电路输出端接到一点工作时,必须保证 B 。 A.任何时刻最多只能有一个电路处于高阻态,其余应处于工作态。 B.任何时刻最多只能有一个电路处于工作态,其余应处于高阻态。 C.任何时刻至少有一个电路处于高阻态,其余应处于工作态。 D.任何时刻至少有一个电路处于工作态,其余应处于高阻态。 15.可以用来传输连续变化的模拟信号的电路是 D 。 A. 三态输出的门电路。; B. 漏极开路的CMOS 门电路; C. ECL 门电路; D. CMOS 传输门 16.逻辑表达式[()]F AB C D E B =++?的对偶式为 B 。

大学英语3词汇选择练习题 第一单元选择题 1. It __________that the necklace was made of glass. A. turned out B. made out C. looked out D. took out 解析:该题选A,题目大意是“原来那串项链是用玻璃做的”。 turn out: 结果是;证明是 The party turned out to be very successful. 晚会结果开得很成功。 2. ___________, he can finish the work in a couple of weeks. A. Giving good health B. If give good health C. Given good health D. If he is good given health 解析:该题选C,题目大意是“倘若身体好,他能在一两周内完成这项工作”。given 引导方式状语,意为“倘若,假设,考虑到”。如: 1. Given their inexperience, the y’ve done a good job.考虑到他们缺乏经验,他们 的工作已经做得不错了。 2. Given some more time, I would do the job better.假如时间再多些,我能把工作 做得更好。 3. Given good health, the old lady can look after her grand-daughter for her son.假 如身体好的话,这位老太太能帮她儿子照看孙女。 3. ___________ to speak at the meeting, I couldn’t very well refuse. A. Called up B. Called off C. Called at D. Called on 解析:该题选D,题目大意是“要让我在会上发言,我是不会拒绝的”。 call on sb. to do st h:invite/require sb. to do sth.请/要求某人做某事 1. A teacher can call on individual students to compose similar questions. 老师可以要求每个学生提出类似的问题。 2. The chairman called on his people to organize so that they could be more powerful.主席号召他的民众组织起来,这样才能更有力量。 4. The poor police had never __________ of winning. A. made a chance B. took a chance C. stood a chance D. kept a chance 解析:该题选C,题目大意是“可怜的警察毫无胜诉的机会”。 stand a chanc e:have a prospect (of sth.) 有…希望 1. stand a chance of winning the game有可能赢得这场比赛 2. I think you stand a good chance of being elected president.我认为你极有可能 当选为公司总裁。 3. Weak and lame in one leg, he never stood a chance of getting the job of taxi-driver.由于身体虚弱,并且有一条跛腿,他从未有机会得到出租车司机的工作。 5. If our neighbor continues to refuse to keep his dog under control, we have to take him to ___________. A. solicitor B. brush C. prisoner D. court 解析:该题选D,题目大意是“如果我们的邻居仍然拒绝看管好他的狗,我们就不得不法庭上见了”。 take sb. to court:控告某人,对某人提出诉讼 1. If you don't pay up, I'll take you to court. 如果你不还清欠款, 我就到法院告

一.内容摘要: 定时器的设计: 设计一个0~60分钟之内的定时器,定时开始的时候红指示灯亮,结束的时候绿指示亮,可以随意以分钟为单位,在六十分钟的范围内设定定时时间,随着定时的开始,显示器开始显示时间,即依次显示出0,1,2,3,4….直到定时结束,当定时结束的时候进行手动清零。首先设计一个秒脉冲发生器,一个计数电路,一个比较电路,然后对电路进行输出。当开始定时之前手动对要定时的时间进行预置数,然后运用秒脉冲发生器输入脉冲,用计数器对脉冲的个数进行计数,把编码器的数据与脉冲的个数通过数值比较器进行比较,最后按照要求进行红绿等输出表示定时的状态是正在进行定时,或者是已经定时结束,在定时的过程中显示定时的时间。 二.方案的论证与选择: 方案1 例如设计一个六十分钟的定时器,就需要六十进制的分钟计数器。设计秒脉冲发生器,当计数器完成六十分钟的记数时,就手动清零。需要设定其他的时间时, 只需将计数器的进制改变一下就行。这个方案只适用于特定的定时器,设定的时间 不变。如果本课设用此方案,就需要设计从1——60进制的计数器,工程量太大。 方案2, 设计一个定时器,可以在0~60分之间一分钟为单位任意可调,定时开始的时候红灯亮,定时结束的时候绿灯亮,定时结束之后手动清零,满足设计的要求,故本次课程设计中采用的是这种设计方案。

三.总设计思想框图: 总体的完整电路图: 就是将各个单元电路用导线连接起来,然后进行仿真处理,开始进行定时的时候红指示灯亮。图中所示的是定时为16分钟的定时仿真结果,完整的电路图。

2.5 V 图2 四.单元电路的设计与参数的计算 1.秒脉冲发生器的选择: (1)采用石英晶体的多谐振荡器,在RC环形振荡器电路中,接入RC可以获得较小 的频率,而且通过RC的调节可以调节频率,用于对频率稳定性要求比较高的电路,

一、阅读理解(共1道小题,共50.0分) 1.Robert Bruce was a famous Scottish general. In the early 14th century he tried to drive the English out of Scotland, but he was not successful because the English were too strong. Finally, Bruce had to run away and hide in a cave. One day, he lay in his cave thinking of the sad state of Scotland. A spider began to make a web above his head. Simply to pass the time, Bruce broke the web. Immediately the spider began to make a new one. Six times Bruce broke the web and six times the spider immediately made a new one. Bruce was surprised at this. He told himself that he would break the web a 7th time. If the spider made a new one, it would be a good lesson to him, for like the spider, he had been defeated six times. Bruce then broke the web. Again the spider made a new one. From this simple fact, Bruce became encouraged. He again got an army together. This time he was successful and drove the English out of Scotland. 1. Who was Robert Bruce? A. He was an English general. B. He was a Scottish general. C. He was a spider researcher D. He was a biologist from Scotland. 2. Why did Bruce hide in a cave? A. Because he was defeated by the English. B. Because he was afraid of the English army. C. Because he was looking for spiders D. Because he was badly injured in the battle. 3. In the beginning he broke the spider web just because______.

《数字信号处理》课程教学大纲 一、课程编号:1100020 二、课程名称:数字信号处理 ( 64学时) Digital Signal Processing 三、课程教学目的 数字信号处理是现代信息处理和传输的基础课程之一,已经成为信号和信息处理、通信和电子、计算机科学和技术等专业的学生需要学习和掌握的基本知识。 本课程以离散时间信号与系统作为对象,在介绍经典理论的基础上,适当引入了现代信号处理的理论与方法以及Matlab仿真分析软件。通过本课程的学习,使得学生能够掌握确定性离散时间信号的频谱分析原理及快速实现方法,数字滤波器的设计及实现方法。使学生能够利用计算机技术来进行数字信号的处理,并根据实际需要分析、设计数字滤波系统。 本课程是进一步学习数字通信、图像处理、随机数字信号处理、无线通信、多媒体通信等专业课程的先修课程。 四、课程教学基本要求 1.掌握离散时间信号和系统的基本标识方法 2.掌握离散时间系统的基本特性、Z变换以及离散时间信号的傅立叶变换(DTFT) 3.掌握离散傅立叶变换(DFT)以及离散傅立叶变换的快速算法(FFT) 4.掌握数字滤波器的设计方法和结构 5.了解多速率信号处理的基本内容 五、教学内容及学时分配(含实验) 理论教学(56学时) 1.绪论2学时数字信号处理的特点、实现和应用 Matlab简介 2.离散时间系统的基本特性及流图10学时抽样与重建 离散系统及其普遍关系 信号流图及Mason公式 离散时间信号的傅立叶变换 Z变换及Z反变换(留数法)

Z变换与拉普拉斯、傅立叶变换的关系 离散系统的频域分析 3.离散傅立叶变换及其快速实现14学时DFS的定义及性质 DFT的定义、性质及应用 基2时间抽选法FFT 基2频率抽选法FFT 基4时间抽选法FFT IDFT的快速算法 FFT应用(线性卷积的快速计算、CZT变换) 4.IIR数字滤波器的设计和实现12学时滤波器概述 模拟滤波器的设计 模拟滤波器的数字仿真 冲激响应不变法和双线性变换法的设计 IIR滤波器的频率变换设计 IIR数字滤波器的计算机辅助设计 IIR 滤波器的实现结构 5.FIR数字滤波器的设计10学时线性相位FIR滤波器的条件和特性概述 窗函数法 频率取样法 FIR数字滤波器的优化设计 FIR数字滤波器的实现结构 6.多速率信号的处理基础8学时抽取和内插的时域和变换域描述 抽取滤波器和内插滤波器 多相分解 正交镜像滤波器组 双通道滤波器组 实验教学(8学时)

北邮大学英语3第二次阶段作业 一、完形填空(共1道小题,共50.0分) 1.Many years ago there was a poor man. He had an orange tree 1 his garden. On the tree there were many fine oranges. 2 he found one 3 his oranges was much bigger 4 the others. It was as 5 as a football. Nobody had ever seen 6 orange. The poor man took the orange to the king. The king was so happy ___7 __he gave the man a lot of money for it. When a rich man heard of it, he said to hi mself, “It's only an orange. Why has the king given so much money 8__ it? I'II take my gold cup to the king. He'll give me 9 money.” The next day when the king received the gold cup, he said to the rich man, 'What a beautiful cup! I'll show you __10__ , please take this great orange." a. A.on B.in C.over D.with 学生答案: B; 标准答 案: B b. A.One day B.Yesterday C.When D.This morning 学生答案: A; 标准答 案: A c. A.for B.in

期末考试试题(答案) 一、选择题(每小题2分,共20分) 1.八进制(273)8中,它的第三位数2 的位权为___B___。 A.(128)10B.(64)10C.(256)10 D.(8)10 2. 已知逻辑表达式C B C A AB F+ + =,与它功能相等的函数表达式 _____B____。 A.AB F=B.C AB F+ = C.C A AB F+ =D.C B AB F+ = 3. 数字系统中,采用____C____可以将减法运算转化为加法运算。 A.原码B.ASCII码C.补码D.BCD码4.对于如图所示波形,其反映的逻辑关系是___B_____。 A.与关系B.异或关系C.同或关系D.无法判断 5.连续异或1985个1的结果是____B_____。 A.0B.1 C.不确定D.逻辑概念错误 6. 与逻辑函数D C B A F+ + + =功能相等的表达式为___C_____。 A.D C B A F+ + + =B.D C B A F+ + + = C.D C B A F=D.D C B A F+ + = 7.下列所给三态门中,能实现C=0时,F=AB;C=1时,F为高阻态的逻辑功能的是____A______。 B A F & ? F B A &

8. 如图所示电路,若输入CP脉冲的频率为100KHZ,则输出Q的频率为_____D_____。 A. 500KHz B.200KHz C. 100KHz D.50KHz 9.下列器件中,属于时序部件的是_____A_____。 A.计数器B.译码器C.加法器D.多路选择器 10.下图是共阴极七段LED数码管显示译码器框图,若要显示字符“5”,则译码器输出a~g应为____C______。 A. 0100100 B.1100011 C. 1011011 D.0011011 二、填空题(每小题2分,共20分) 11.TTL电路的电源是__5__V,高电平1对应的电压范围是__2.4-5____V。 12.N 个输入端的二进制译码器,共有___N2____个输出端。对于每一组输入代码,有____1____个输出端是有效电平。 13.给36个字符编码,至少需要____6______位二进制数。 14.存储12位二进制信息需要___12____个触发器。

目录 第一章系统概述 (1) 1.1 系统开发背景 (1) 1.2 系统开发意义 (1) 1.3 EWB在数字电子电路综合课程设计中的应用 (1) 第二章555简易电子琴设计 (2) 2.1 设计题目 (3) 2.2 设计的目的与要求 (3) 2.3 分析任务 (3) 2.3.1设计总开关模块 (3) 2.3.2设计控制模块 (3) 2.3.3设计琴键模块 (3) 2.3.4设计扬声器模块 (3) 2.4 需用器件的选择 (3) 2.4.1 555定时器 (3) 2.4.2 电容 (6) 2.4.3 电阻 (6) 2.5 总体说明 (6) 2.6 单元模块 (6) 第三章555简易电子琴的实现 (8) 3.1 单元模块的实现 (8) 3.2 电子琴的完整电路设计 (9) 3.3 参考文献 (17)

第一章系统概述 1.1系统开发背景 随着电子技术的不断发展,模拟电子技术的缺点和局限性越发明显,模拟电子技术的不稳定性、易干扰性等大大限制了其应用,且有阻碍电子 技术发展的趋势。19世纪兴起的数字电路以其先天的便捷、稳定的优点在 现代电子技术电路中占有越来越重要的地位。 数字电路与模拟电路相比有显而易见的稳定性。近年来,数字电路又有了巨大的发展。可编程逻辑器件(PAL、GAL等)的发展和普及最终使IC 的设计面向了用户(这是模拟电路无法做到的),而这毫无疑问会给用户带来巨大的便捷,从而奠定它在电子电路中的对位。 随着集成技术的进一步提高,各种新技术的出现和应用,人类历史横跨数码时代向更进一步发展已出现在各大型相关企业的宏伟蓝图中。新世 纪里谁掌握了新技术谁就得到了获胜的资本,也仅仅是资本而矣。新世纪 里电子行业的发展速度令人窒息,闻名的摩尔定律更把许多人威吓在门外。 可以展望,由数字构成的新世界即将出现。将是人类文明的又一飞跃。 1.2系统开发意义 555简易电子琴是一种用数字电路技术实现数字显示装置,与机械式数字显示装置相比具有更高的准确性和直观性,且无机械装置,具有更更长的使用寿命,因此得到了广泛的使用。555简易电子琴从原理上讲是一种典型的数字电路,其中包括了组合逻辑电路和时序电路。 因此,我们此次设计与制做555简易电子琴就是为了了解555定时器的原理,从而学会制作555简易电子琴,而且通过555简易电子琴的制作进一步的了解各种在制作中用到的中小规模集成电路的作用及实用方法。 1.3EWB在数字电子电路综合课程设计中的应用

本科试卷(八) 一、选择题(每小题2分,共30分) 1.逻辑函数F1=∑m (2,3,4,8,9,10,14,15), 它们之间的关系是________。 A . B . C . D .、互为对偶式 2. 最小项的逻辑相邻项是________。 A .ABCD B. C. D. 3. 逻辑函数F (ABC )=A ⊙C 的最小项标准式为________。 A.F=∑(0,3) B. C.F=m 0+m 2+m 5+m 7 D. F=∑(0,1,6,7) 4. 一个四输入端与非门,使其输出为0的输入变量取值组合有_______种。 A. 15 B. 8 C. 7 D. 1 5. 设计一个四位二进制码的奇偶位发生器(假定采用偶检验码),需要_______个异或门。 A .2 B. 3 C. 4 D. 5 6. 八路数据选择器如图1-1所示,该电路实现的逻辑函数是F=______。 A . B . C . D . 图1-1 7. 下列电路中,不属于时序逻辑电路的是_______。 A .计数器 B .触发器 C .寄存器 D .译码器 8. 对于JK 触发器,输入J=0,K=1,CP 脉冲作用后,触发器的次态应为_____。 A .0 B. 1 C. 保持 D. 翻转 9. Moore 型时序电路的输出_____。 A.与当前输入有关 B. 与当前状态有关 C. 与当前输入和状态都有关 D. 与当前输入和状态都无关 2F ABC ABCD ABC ABC ACD =++++12F F =12F F =12F F =1F 2F ABCD ABCD ABCD ABCD C A C A F +=AB AB +AB AB +A B ⊕A B +

一、完形填空(共1道小题,共50.0分) 1.Many years ago there was a poor man. He had an orange tree 1 his garden. On the tree there were many fine oranges. 2 he found one 3 his oranges was much bigger 4 the others. It was as 5 as a football. Nobody had ever seen 6 orange. The poor man took the orange to the king. The king was so happy ___7 __he gave the man a lot of money for it. When a rich man heard of it, he said to himself, “It's only an orange. Why has the king given so much money 8__ it? I'II take my gold cup to the king. He'll give me 9 money.” The next day when the king received the gold cup, he said to the rich man, 'What a beautiful cup! I'll show you __10__ , please take this great orange." a. A.on B.in C.over D.with 学生答案: B; 标准答 案: B b. A.One day B.Yesterday C.When D.This morning 学生答案: A; 标准答 案: A c. A.for B.in C.of D.among

华东师范大学期末试卷(B) 2009 — 2010 学年第 一 学期 课程名称:___数字逻辑________ 学生姓名:___秦宽________________ 学 号:_2013041046__________________ 专 业:____软件工程_______ 年级/班级:13级软件工程 课程性质:公共必修、公共选修、专业必修、专业选修 一、填空题 (20分,每空2分) 1. (2010)D =( )B = ( )H = ( )8421BCD 答案:(111 1101 1010)B = (7DA )H = (0010 0000 0001 0000)8421BCD 2. 仓库门上装了两把暗锁,A 、B 两位保管员各管一把锁的钥匙,必须二人同时开锁才能进库。这种逻辑关系为 。 答案:与逻辑 3. 逻辑函数式F=AB+AC 的对偶式为 ,最小项表达式为∑=m F ( )。 答案:))((C A B A F D ++= ∑=m F (5,6,7) 2.逻辑函数D AC CD A C AB D C ABD ABC F ''''''+++++=的最简与或式是 。 答案:'D A + 4. 从结构上看,时序逻辑电路的基本单元是 。 答案:触发器 5. JK 触发器特征方程为 。 答案:Q K JQ ''+ 6.A/D 转换的一般步骤为:取样,保持, ,编码。 答案:量化

二、选择题 (20分,每题2分) 1. 计算机键盘上有101个键,若用二进制代码进行编码,至少应为( )位。 A) 6 B) 7 C) 8 D) 51 答案:B 2. 在函数F=AB+CD 的真值表中,F=1的状态有( )个。 A) 2 B) 4 C) 6 D) 7 答案:D 3. 为实现“线与”逻辑功能,应选用( )。 A) 与非门 B) 与门 C) 集电极开路(OC )门 D) 三态门 答案:C 4. 图1所示逻辑电路为( )。 A) “与非”门 B) “与”门 C)“或”门 D) “或非”门 图1 答案:A 5. 在下列逻辑部件中,属于组合逻辑电路的是( )。 A) 计数器 B) 数据选择器 C) 寄存器 D) 触发器 答案:B 6. 已知某触发器的时钟CP ,异步置0端为R D ,异步置1端为S D ,控制输入端V i 和输出Q 的波形如图2所示,根据波形可判断这个触发器是( )。 B C

数字逻辑 课程设计报告 —多功能数字钟的设计与实现 姓名: 专业班级:通信1002 学号:31006010 指导老师:曾宇 设计日期:2012.06.20~2012.06.24

一、设计目的 1、学会应用数字系统设计方法进行电路设计; 2、学习使用QuartusII 9.0, 进一步提高软件的开发应用能力,增强自己的动手实践能力。 3、培养学生书写综合实验报告的能力。 二、设计任务及要求 实现多功能数字钟的设计,主要有以下功能: 1、记时、记分、记秒 2、校时、校分、秒清0 3、整点报时 4、时间正常显示 5、闹时功能(选做) 三、设计思路 3.1 计时模块 3.1.1 设计原理 计时模块如图3.1.1所示,其中计时用60进制计数器,计分和计秒用24进制计数器。 图3.1.1 计时间模块 计时间过程: 计秒:1HZ计数脉冲,0~59循环计数,计数至59时产生进位信号; 计分:以秒计数器进位信号作为分计数脉冲,0~59循环计数,59时产生进位;计时:以分计数器进位信号作为时计数脉冲,0~23循环计数,23时清0。 计数器的设计: 3.1.2 设计程序 编程分别设计24、60进制计数器,计数状态以BCD码形式输出。 24进制计数器源程序:

library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity FEN24 is port(en,clk:in std_logic; ----高电平有效的使能信号/输入时钟 co:out std_logic; h1,h0:out std_logic_vector(3 downto 0)); ----时高位/低位 end FEN24; architecture behave of FEN24 is begin process(clk) variable cnt1,cnt0:std_logic_vector(3 downto 0); ----记数 begin if(en='0')then ---“使能”为0 cnt0:="0010"; cnt1:="0001"; elsif clk'event and clk='1'then ---上升沿触发 if cnt1="0010"and cnt0="0011"then cnt0:="0000"; ----高位/低位同时为0时 cnt1:="0000"; co<='1'; else co<='0'; if cnt0="1001"then cnt0:="0000"; cnt1:=cnt1+1; else cnt0:=cnt0+1; -----高位记数累加 end if; end if; end if; h1<=cnt1; h0<=cnt0; end process; end behave; 60进制计数器源程序: library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity FEN60 is

1.电子电路分为模拟电子电路和数字电子电路。数值的度量采用直流电压或电流的连续值,称模拟量。 2.数字电路比模拟电路有许多优点。如:电路便于集成化、系列化生产,成本低廉,使用方便;抗干扰性强,可靠性高,精度高;处理功能强,不仅能实现数值运算,还可以实现逻辑运算和判断;可编程数字电路可容易地实现各种算法,具有很大的灵活性;数字信号更易于存储、加密、压缩、传输和再现。 3.数字量具有精度高、传输高效、易存储、易处理等优点(上升沿10%—90%) 4.自然码:有权码,每位代码都有固定权值,结构形式与二进制数完全相同,最大计数为2n-1,n为二进制数的位数 5.可靠性代码:(1) 奇偶校验码(2) 格雷码(Gray 码,又称循环码(循环码的一种)<格雷码的特点是任何相邻的两个码组中,仅有一位代码不同,抗干扰能力强,主要用在计数器中> 6.数字电路是传递和处理数字信号的电子电路。它有组合逻辑电路和时序逻辑电路两大类。 7.数字电路的优点:便于高度集成化,工作可靠性强,抗干扰能力强,保密性好等。 8.时序逻辑电路中一定包含:触发器。时序电路中必须有:时钟。从本质上讲,控制器是一种时序电路。时序逻辑电路:逻辑功能特点:任何时刻的输出不仅取决于该时刻的输入信号(输入变量)的状态,而且与电路原有的状态(原来的输出)(Qn+1 = f(Qn, input))有关。即历史状态相关性。时序逻辑电路具有记忆功能(适当的控制) 电路结构特点:由存储电路和组合逻辑电路组成。包含锁存器或触发器它的输出往往反馈到输入端,与输入变量一起决定电路的输出状态。 //时序逻辑电路的类型(都跟触发器或其组合有关)同步时序逻辑电路:所有触发器的时钟端连在一起。所有触发器在同一个时钟脉冲CP 控制下同步工作。 异步时序逻辑电路:时钟脉冲CP 只触发部分触发器,其余触发器由电路内部信号触发。因此,触发器不在同一时钟作用下同步工作。 9.一位十进制计数器至少需要4个触发器 10.锁存器、触发器和门电路是构成数字电路的基本单元。 锁存器、触发器有记忆功能,由它构成的电路在某时刻的输出不仅取决于该时刻的输入,还与电路原来状态有关。而门电路(组合电路)无记忆功能,由它构成的电路在某时刻的输出完全取决于该时刻的输入,与电路原来状态无关 11.布尔代数的三个最重要规则是代入规则,反演规则和对偶规划 12.数字量的特定是数值为离散量,运算结果也是离散量。 13.二进制系统的两个数字0和1是一个开关量,常称比特。用来表示1和0的电平称为逻辑电平。 14.自然二进制有叫有权码。循环码(又叫单位距离码):任何相邻的两个码字中,仅有一位不同。 15.二进制对十进制编码,简称BCD码。8421码(eg:1592是0001 0101 1001 0010)<当相加和大于9时加6修正,无1010~1111>余3码:在8421码的基础上加0011。优点执行十进制相加时,能正确的产生进位信号,而且会给减法运算带来方便。格雷码是使任何两个相邻的代码只有一个二进制状态不同(主要用于计数器)。格雷码是一种循环码。无权码:余 3 码和格雷码。有利于得到更好的译码波形。可靠性代码(奇偶校验码,格雷码) 16.化简的意义:使逻辑式最简,以便设计出最简的逻辑电路,从而节省元器件,优化生产工艺,降低成本和提高系统可靠性。 17.逻辑函数的描述工具:布尔代数{(布尔代数中的变量称为逻辑变量)<0和1代表两种对立的逻辑状态>};真值表(n变量,2^n种可能);逻辑图法();卡诺图法(变量数基本上少于5);波形图;硬件描述语言法。 18.正逻辑,负逻辑,三态门(逻辑1,逻辑0,高阻抗)<使能端有效时(逻辑1)输出状态取决于输入状态> 19.卡诺图

一、单项选择题(共20道小题,共100.0分)1Her brother ______ to leave her in the dark room alone when she disobeyed his order. 1declared 1threatened 1warned 1exclaimed 知识点:Vocabulary 学生答案:[B;]标准答案:B 得分:[5]试题分值: 5.0提示:2It is certain that he will ______ his business to his son when he gets old.1take over 1think over 1hand over 1go over 知识点:Vocabulary 学生答案:[C;]标准答案:C 得分:[5]试题分值: 5.0提示:3The president spoke at the business meeting for nearly an hour without ______ his notes. 1bringing up 1referring to 1looking for 1trying on 知识点:Vocabulary 学生答案:[B;]标准答案:B 得分:[5]试题分值: 5.0 提示: 4 With oil prices keeping ______, people are hesitating whether to buy a car or not.1 rising 1 arising 1raising 、管路敷设技术通过管线敷设技术不仅可以解决吊顶层配置不规范高中资料试卷问题,而且可保障各类管路习题到位。在管路敷设过程中,要加强看护关于管路高中资料试卷连接管口处理高中资料试卷弯扁度固定盒位置保护层防腐跨接地线弯曲半径标高等,要求技术交底。管线敷设技术中包含线槽、管架等多项式,为解决高中语文电气课件中管壁薄、接口不严等问题,合理利用管线敷设技术。线缆敷设原则:在分线盒处,当不同电压回路交叉时,应采用金属隔板进行隔开处理;同一线槽内,强电回路须同时切断习题电源,线缆敷设完毕,要进行检查和检测处理。、电气课件中调试对全部高中资料试卷电气设备,在安装过程中以及安装结束后进行高中资料试卷调整试验;通电检查所有设备高中资料试卷相互作用与相互关系,根据生产工艺高中资料试卷要求,对电气设备进行空载与带负荷下高中资料试卷调控试验;对设备进行调整使其在正常工况下与过度工作下都可以正常工作;对于继电保护进行整核对定值,审核与校对图纸,编写复杂设备与装置高中资料试卷调试方案,编写重要设备高中资料试卷试验方案以及系统启动方案;对整套启动过程中高中资料试卷电气设备进行调试工作并且进行过关运行高中资料试卷技术指导。对于调试过程中高中资料试卷技术问题,作为调试人员,需要在事前掌握图纸资料、设备制造厂家出具高中资料试卷试验报告与相关技术资料,并且了解现场设备高中资料试卷布置情况与有关高中资料试卷电气系统接线等情况,然后根据规范与规程规定,制定设备调试高中资料试卷方案。、电气设备调试高中资料试卷技术电力保护装置调试技术,电力保护高中资料试卷配置技术是指机组在进行继电保护高中资料试卷总体配置时,需要在最大限度内来确保机组高中资料试卷安全,并且尽可能地缩小故障高中资料试卷破坏范围,或者对某些异常高中资料试卷工况进行自动处理,尤其要避免错误高中资料试卷保护装置动作,并且拒绝动作,来避免不必要高中资料试卷突然停机。因此,电力高中资料试卷保护装置调试技术,要求电力保护装置做到准确灵活。对于差动保护装置高中资料试卷调试技术是指发电机一变压器组在发生内部故障时,需要进行外部电源高中资料试卷切除从而采用高中资料试卷主要保护装置。