实验一Cache模拟器的实现

一.实验目的

(1)加深对Cache的基本概念、基本组织结构以及基本工作原理的理解。

(2)掌握Cache容量、相联度、块大小对Cache性能的影响。

(3)掌握降低Cache不命中率的各种方法以及这些方法对提高Cache性能的好处。

(4)理解LRU与随机法的基本思想以及它们对Cache性能的影响。

二、实验容和步骤

1、启动Cachesim

2.根据课本上的相关知识,进一步熟悉Cache的概念和工作机制。

Cache概念:高速缓冲存

Cache工作机制:大容量主存一般采用DRAM,相对SRAM速度慢,而SRAM 速度快,但价格高。程序和数据具有局限性,即在一个较短的时间,程序或数据往往集中在很小的存储器地址围。因此,在主存和CPU之间可设置一个速度很快而容量相对较小的存储器,在其中存放CPU当前正在使用以及一个较短的时间将要使用的程序和数据,这样,可大大加快CPU访问存储器的速度,提高机器的运行效率

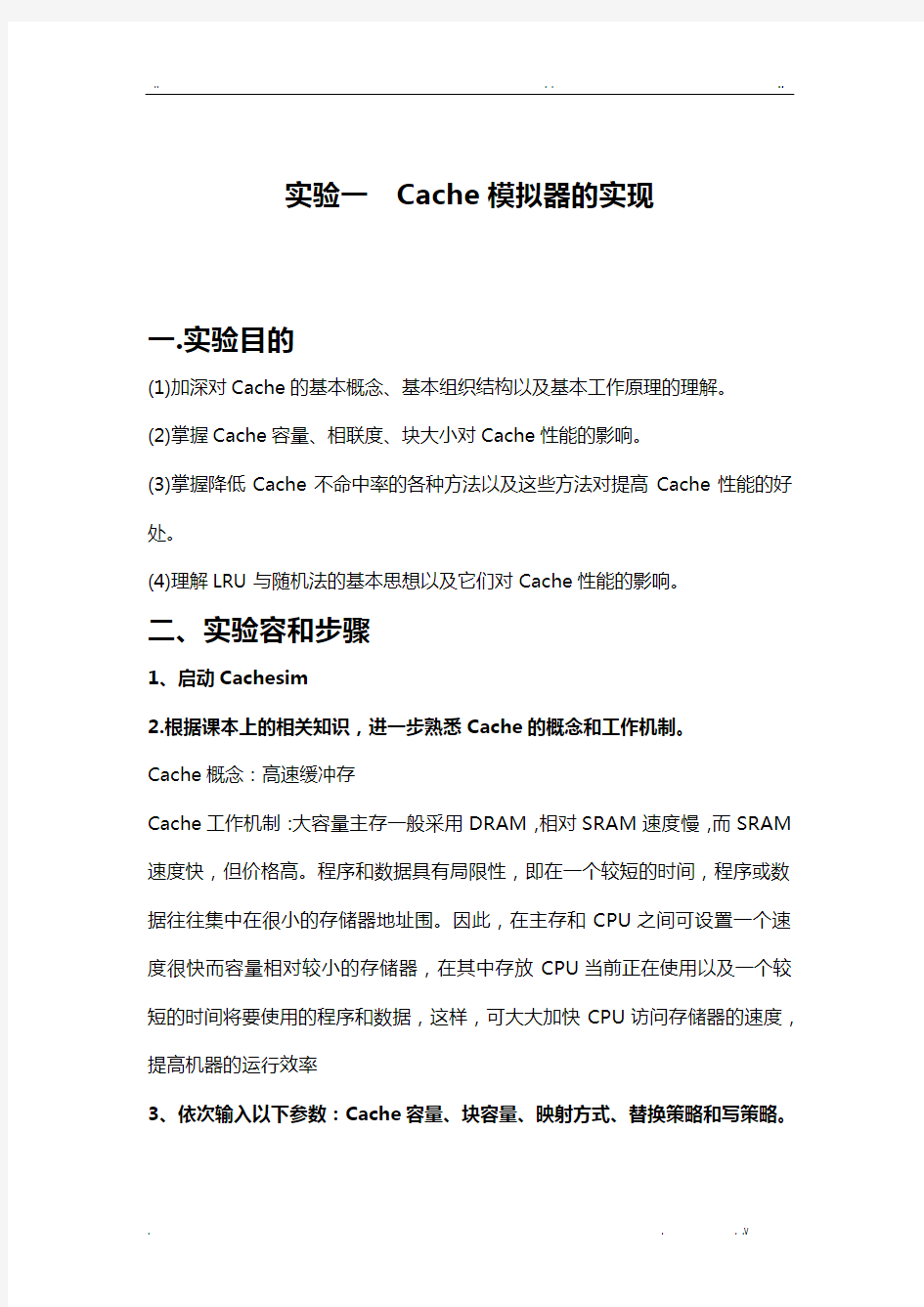

3、依次输入以下参数:Cache容量、块容量、映射方式、替换策略和写策略。

(1)Cache容量:

启动CacheSim,提示请输入Cache容量,例如1、2、4、8......。此处选择输入4。

(2)块容量:

如下图所示,提示输入块容量,例如1、2、4、8......。此处选择输入16。

(3)映射方式:

如下图所示,提示输入主存储器和高速缓存之间的assoiativity方法(主存地址到Cache地址之间的映射方式),1代表直接映射(固定的映射关系)、2代表组相联映射(直接映射与全相联映射的折中)、3代表全相联映射(灵活性大的映射关系)。此处选择全相联映射。

(4)替换策略:

如下图所示,提示输入替换策略,1代表先进先出(First-In-First-Out,FIFO)算法、2代表近期最少使用(Least Recently Used,LRU)算法、3代表最不经常使用(Least Frequently Used,LFU)、4代表随机法(Random)。此处选择先进

先出。

(5)写策略:

如下图所示,提示输入Cache的读写操作,1代表写直达法(存直达法)即写操作时数据既写入Cache又写入主存、2代表写回法(拷回法)即写操作时只把数据写入Cache而不写入主存,但当Cache数据被替换出去时才写回主存。此处选写回法

4、读取cache-traces.zip中的trace文件。

如下图所示,提示输入要测试的路径及名称,此处输入Cache-trace.zip 的路径,以及需要读取的trace文件名,此处选择读取mcf.trace。

5、运行程序,观察cache的访问次数、读/写次数、平均命中率、读/写命中率。

如下图所示,读取mcf.trace文件,程序运行结果如下:

(1)高速缓存访问次数:727230

(2)高速缓存次数:5972

(3)cache存储次数:721258

(4)平均缓存命中率:74.8615%

访问次数读出次数写入次数平均命中率读出命中率写入命中率727230 5972 721258 74.8615%

60.6999%

74.9787%

(5)高速缓存命中率:60.6999%

(6)缓存命中率:74.9787%

思考:1、Cache的命中率与其容量大小有何关系?

(1)当Cache块容量为8B、Cache容量为8KB时,平均命中率为1.02017%.

(2)当Cache块容量为8B、Cache容量为16KB时,平均命中率为1.02334%.

(3)当Cache块容量为8B、Cache容量为32KB时,平均命中率为1.03695%.

(4)当Cache块容量为8B、Cache容量为64KB时,平均命中率为1.0375%.

(5)当Cache块容量为8B、Cache容量为128KB时,平均命中率为1.03791%.

当Cache块容量为8B时,不同Cache容量下的命中率如下图所示:

Cache容

量

8 16 32 64 128

平均命中率 1.02017%

1.02334% 1.03695% 1.0375%

1.03791%

由上述图中数据及表格数据可知,当Cache块容量一定时,Cache容量越大,其cache的命中率越高。

2、Cache块大小对不命中率有何影响?

(1)当Cache块容量为8KB、Cache容量为8B时,平均命中率为1.02017%.

实验2:MIPS指令系统和MIPS体系结构 一.实验目的 (1)了解和熟悉指令级模拟器 (2)熟悉掌握MIPSsim模拟器的操作和使用方法 (3)熟悉MIPS指令系统及其特点,加深对MIPS指令操作语义的理解 (4)熟悉MIPS体系结构 二. 实验内容和步骤 首先要阅读MIPSsim模拟器的使用方法,然后了解MIPSsim的指令系统和汇编语言。(1)、启动MIPSsim(用鼠标双击MIPSsim.exe)。 (2)、选择“配置”->“流水方式”选项,使模拟器工作在非流水方式。 (3)、参照使用说明,熟悉MIPSsim模拟器的操作和使用方法。 可以先载入一个样例程序(在本模拟器所在的文件夹下的“样例程序”文件夹中),然后分别以单步执行一条指令、执行多条指令、连续执行、设置断点等的方式运行程序,观察程序的执行情况,观察CPU中寄存器和存储器的内容的变化。 (4)、选择“文件”->“载入程序”选项,加载样例程序 alltest.asm,然后查看“代码”窗口,查看程序所在的位置(起始地址为0x00000000)。 (5)、查看“寄存器”窗口PC寄存器的值:[PC]=0x00000000。 (6)、执行load和store指令,步骤如下: 1)单步执行一条指令(F7)。 2)下一条指令地址为0x00000004,是一条有 (有,无)符号载入字节 (字节,半字,字)指令。 3)单步执行一条指令(F7)。 4)查看R1的值,[R1]= 0xFFFFFFFFFFFFFF80 。 5)下一条指令地址为0x00000008,是一条有 (有,无)符号载入字 (字节,半字,字)指令。 6)单步执行1条指令。 7)查看R1的值,[R1]=0x0000000000000080 。 8)下一条指令地址为0x0000000C ,是一条无 (有,无)符号载入字节 (字节,半字,字)指令。 9)单步执行1条指令。 10)查看R1的值,[R1]= 0x0000000000000080 。 11)单步执行1条指令。 12)下一条指令地址为0x00000014 ,是一条保存字 (字节,半字,字)指令。 13)单步执行一条指令。

一、判断题 1. 在使用配置了触摸屏的多媒体计算机时,可不必使用鼠标器。 2. 盘和存之间以簇为单位交换数据。 3. 光盘是一种可读不可写的存储器。 4. VGA是显示器主机间的接口。 5. 激光打印机使用的墨水质量很高。 6. 扫描仪工作时,将被扫描的图件正面朝上。 7. 数码相机的成像技术与传统相机的成像技术基本相同。 8. CMOS是一种易失性存储器。 9. SRAM比DRAM速度慢。 10.ROM是非易失性存储器。 11.利用Cache能加快程序的运行速度,其依据的原理是Cache速度快。 12.主存储器的编址单位是字节。 13.I/O控制器可以完全脱离CPU控制I/O操作的全过程。 14.CPU总线、存储器总线和I/O总线统称系统总线。 15.I/O接口就是用于连接I/O设备的各种插头插座。 16.总线控制器包含在主板的芯片组。 17.USB接口按双向并行方式传输数据。 18.ALU与浮点运算器可以同时进行整数和实数的运算。 19.CPU主频即CPU总线频率。 20.计算机常用的输入设备为键盘、鼠标,常用的输出设备有显示器、打印机。21.不同厂家生产的计算机一定互相不兼容。 22.PC机的主存储器包含大量的存储单元,每个存储单元都可以存放8个Byte。 23.在使用输入设备进行输入时,目前还只能输入文字、命令和图像,无法输入声音。 24.为了提高CPU访问硬盘的工作效率,硬盘通过将数据存储在一个比其速度快得多的缓冲区 来提高与CPU交换的速度,这个区就是高速缓冲区,它是由DRAM芯片构成的。 25.在一台已感染病毒的计算机上读取一CD-ROM光盘中的数据,该光盘也有可能被感染病毒。 26.存储容量是数码相机的一项重要性能,不论拍摄质量如何,存储容量大的数码相机可拍摄 的相片数量肯定比存储容量小的相机多。 27.绘图仪、扫描仪、显示器、音箱等均属于输出设备。 28.PC机的主板又称为母板,上面可安装CPU、存储器、总线、I/O控制器等部件,它们是 PC机的核心。 29.由于硬盘的外部传输速率要小于部传输速率,所以外部传输速率的高低是评价硬盘整体性 能的决定性因素。 30. PC机中常用的外围设备都通过各自的扩充卡与主板相连,这些扩充卡只能插在主板上的 PCI总线插槽中。 31.大部分数码相机采用CCD成像芯片,CCD芯片中有大量的CCD像素,像素越多影像的分辨 率(清晰度)就越高,生成的数字图像也越小。 32. 高速缓存(Cache)可以看做主存的延伸,与主存统一编址,接收CPU的访问,但其速度要 比主存高得多。 33. 即插即用就是不需要设备驱动程序。 34. USB接口是一种通用的串行接口,通常连接的设备有移动硬盘、优盘、鼠标器、扫描仪

计算机组成原理 1.(45.75)10=(___________)16 2.若[X]补=1.0110,则[1/2X]补=___________。 3.若X补=1.1001,按舍入恒置1法舍去末位得__________。 4.运算器的核心部件是__________。 5.动态MOS存储器的刷新周期安排方式有____________、 _____________、_____________。 6.若地址码8位,按字节编址则访存空间可达___________,若地址码10位,则访存空间可达_____________,若地址码20位,则访存空间可达_____________。 7.CPU中用于控制的寄存器有_______________________、 __________________ 和_____________________三种;8.控制器的组成方式可分为______________________和微程序控制器两类。 9.按数据传送方式,外围接口可分为_________________和 __________________。 10.指令中的操作数一般可分为_______操作数和_______操作数。11.申请掌握使用总线的设备,被称为__________。 12.某CRT显示器,分辨率800列╳600行,如果工作在256色模式下,则至少需要_________字节的显示存储器。 选择题: 1、浮点加减中的对阶是() A.将较小的一个阶码调整到与较大的一个阶码相同 B.将较大的一个阶码调整到与较小的一个阶码相同 C.将被加数的阶码调整到与加数的阶码相同 D.将加数的阶码调整到与被加数的阶码相同 2、下列哪一个属于检错纠码() A. BCD码 B. ASCII码 C. 奇偶校验码 D. 8421码 3、指令格式可表示为()和地址码的形态 A.指令码 B. 操作码 C.微指令 D. 寄存器码 4、在不同速度的设备之间传送数据( )

实验1 Cache性能分析 1 实验目的 (1)加深对Cache的基本概念、基本组织结构以及基本工作原理的理解。 (2)掌握Cache容量、相联度、块大小对Cache性能的影响。 (3)掌握降低Cache 2 实验平台 采用MyCache模拟器。 MyCache模拟器的使用方法: (1) 双击MyCache.exe,启动模拟器。 (2) 系统打开操作界面,如下图所示: (3) 写不命中时的调块策略。可以直接从列表中选择。 (4) 访问地址可以选择来自地址流文件,也可以选择手动输入。如果是前者,则可以通过单击“浏览”按钮,从模拟器所在文件夹下的“地址流”文件夹中选取地址流文件(.din)文件,然后执行。执行得方式可以是单步,也可以选择一次执行结束。如果选择手动输入,就可以在“执行控制”区域中输入块地址,然后单击“访问”按钮。系统会在界面的右边显示访问类型、地址、块号以及块内地址。 3 实验内容和步骤 3.1 Cache容量对不命中率的影响 (1) 启动MyCache。 (2) 单击“复位”按钮,将各参数设置为默认值。 (3) 选择一个地址流文件。具体方法:选择“访问地址”→“地址流文件”选项,然后单击“浏览”按钮,从本模拟器所在的文件夹下的“地址流”文件夹中选取。 (4) 选择不同的Cache容量,包括2KB,4 KB,8 KB,16 KB,32 KB,64 KB,128 KB和256 KB,分别执行模拟器(单击“执行到底”按钮就可执行),然后在表1.1中记录各种情况下的不命中率。 地址流文件名:all.din 表1.1 不同容量下Cache的不命中率

(5)指明地址流文件名,以容量为横坐标,画出不命中率虽Cache容量变化而变化的曲线 (6) 根据该模拟结果,能得出什么结论? 相同的地址流文件,Cache容量越大,Cache的不命中率越低,命中率越高,但当Cache 容量达到一定程度时,Cache的命中率将不变。 3.2 相联度对不命中率的影响 (1) 单击“复位”按钮,将各参数设置为默认值。此时的Cache容量为64KB。 (2) 选择一个地址流文件。具体方法:选择“访问地址”→“地址流文件”选项,然后单击“浏览”按钮,从本模拟器所在的文件夹下的“地址流”文件夹中选取。 (3) 选取不同的Cache相联度,包括直接映像、2路、4路、8路、16路和32路。分别执行模拟器(单击“执行到底”按钮),然后再表1.2中记录各种情况下的不命中率。 地址流文件名:all.din (4) 把Cache的容量设置为256KB,重复(3)步骤填表1.3。

第一章 1.电子数字计算机和电子模拟计算机的区别在哪里 解:电子数字计算机中处理的信息是在时间上离散的数字量,运算的过程是不连续的;电子模拟计算机中处理的信息是连续变化的物理量,运算的过程是连续的。 2.冯·诺依曼计算机的特点是什么其中最主要的一点是什么解:冯·诺依曼计算机的特点如下: ①计算机(指硬件)应由运算器、存储器、控制器、输入设备和输出设备五大基本部件组成; ②计算机内部采用二进制来表示指令和数据; ③将编好的程序和原始数据事先存入存储器中,然后再启动计算机工作。 第③点是最主要的一点。 3.计算机的硬件是由哪些部件组成的它们各有哪些功能解:计算机的硬件应由运算器、存储器、控制器、输入设备和输出设备五大基本部件组成。它们各自的功能是: ①输入设备:把人们编好的程序和原始数据送到计算机中去,并且将它们转换成计算机内部所能识别和接受的信息方式。 ②输出设备:将计算机的处理结果以人或其他设备所能接受的形式送出计算机。 ③存储器:用来存放程序和数据。 ④运算器:对信息进行处理和运算。

⑤控制器:按照人们预先确定的操作步骤,控制整个计算机的各部件有条不紊地自动工作。 4.什么叫总线简述单总线结构的特点。 解:总线是一组能为多个部件服务的公共信息传送线路,它能分时地发送与接收各部件的信息。单总线结构即各大部件都连接在单一的一组总线上,这个总线被称为系统总线。CPU 与主存、CPU 与外设之间可以直接进行信息交换,主存与外设、外设与外设之间也可以直接进行信息交换,而无须经过CPU 的干预。 5.简单描述计算机的层次结构,说明各层次的主要特点。 解:现代计算机系统是一个硬件与软件组成的综合体,可以把它看成是按功能划分的多级层次结构。 第0级为硬件组成的实体。 第1级是微程序级。这级的机器语言是微指令集,程序员用微指令编写的微程序一般是直接由硬件执行的。 第2级是传统机器级。这级的机器语言是该机的指令集,程序员用机器指令编写的程序可以由微程序进行解释。 第3级是操作系统级。从操作系统的基本功能来看,一方面它要直接管理传统机器中的软硬件资源,另一方面它又是传统机器的延伸。第4级是汇编语言级。这级的机器语言是汇编语言,完成汇编语言翻译的程序叫做汇编程序。 第5级是高级语言级。这级的机器语言就是各种高级语言,通常用编译程序来完成高级语言翻译的工作。

实验一Cache模拟器的实现 一.实验目的 (1)加深对Cache的基本概念、基本组织结构以及基本工作原理的理解。 (2)掌握Cache容量、相联度、块大小对Cache性能的影响。 (3)掌握降低Cache不命中率的各种方法以及这些方法对提高Cache性能的好处。 (4)理解LRU与随机法的基本思想以及它们对Cache性能的影响。 二、实验内容和步骤 1、启动Cachesim 2.根据课本上的相关知识,进一步熟悉Cache的概念和工作机制。 Cache概念:高速缓冲存 Cache工作机制:大容量主存一般采用DRAM,相对SRAM速度慢,而SRAM速度快,但价格高。程序和数据具有局限性,即在一个较短的时间内,程序或数据往往集中在很小的存储器地址范围内。因此,在主存和CPU之间可设置一个速度很快而容量相对较小的存储器,在其中存放CPU当前正在使用以及一个较短的时间内将要使用的程序和数据,这样,可大大加快CPU访问存储器的速度,提高机器的运行效率 3、依次输入以下参数:Cache容量、块容量、映射方式、替换策略和写策略。Cache容量块容量映射方式替换策略写策略 8 32 全相联映射先进先出算法写回法(1)Cache容量: 启动CacheSim,提示请输入Cache容量,例如1、2、4、8......。此处选择输入4。 (2)块容量: 如下图所示,提示输入块容量,例如1、2、4、8......。此处选择输入16。

(3)映射方式: 如下图所示,提示输入主存储器和高速缓存之间的assoiativity方法(主存地址到Cache地址之间的映射方式),1代表直接映射(固定的映射关系)、2代表组相联映射(直接映射与全相联映射的折中)、3代表全相联映射(灵活性大的映射关系)。此处选择全相联映射。 (4)替换策略: 如下图所示,提示输入替换策略,1代表先进先出(First-In-First-Out,FIFO)算法、2代表近期最少使用(Least Recently Used,LRU)算法、3代表最不经常使用(Least Frequently Used,LFU)、4代表随机法(Random)。此处选择先进先出。 (5)写策略: 如下图所示,提示输入Cache的读写操作,1代表写直达法(存直达法)即写操作时数据既写入Cache又写入主存、2代表写回法(拷回法)即写操作时只把数据写入Cache而不写入主存,但当Cache数据被替换出去时才写回主存。

实验一Cache模拟器得实现 一、实验目得 (1)加深对Cache得基本概念、基本组织结构以及基本工作原理得理解。 (2)掌握Cache容量、相联度、块大小对Cache性能得影响。 (3)掌握降低Cache不命中率得各种方法以及这些方法对提高Cache性能得好处。 (4)理解LRU与随机法得基本思想以及它们对Cache性能得影响. 二、实验内容与步骤 1、启动Cachesim 2、根据课本上得相关知识,进一步熟悉Cache得概念与工作机制。 Cache概念:高速缓冲存 Cache工作机制:大容量主存一般采用DRAM,相对SRAM速度慢,而SRAM速度快,但价格高。程序与数据具有局限性,即在一个较短得时间内,程序或数据往往集中在很小得存储器地址范围内。因此,在主存与CPU之间可设置一个速度很快而容量相对较小得存储器,在其中存放CPU当前正在使用以及一个较短得时间内将要使用得程序与数据,这样,可大大加快CPU访问存储器得速度,提高机器得运行效率 3、依次输入以下参数:Cache容量、块容量、映射方式、替换策略与写策略. (1)Cache容量: 启动CacheSim,提示请输入Cache容量,例如1、2、4、8、、、、、、。此处选择输入4。 (2)块容量: 如下图所示,提示输入块容量,例如1、2、4、8、、、、、、。此处选择输入16。 (3)映射方式: 如下图所示,提示输入主存储器与高速缓存之间得assoiativity方法

(主存地址到Cache地址之间得映射方式),1代表直接映射(固定得映射关系)、2代表组相联映射(直接映射与全相联映射得折中)、3代表全相联映射(灵活性大得映射关系)。此处选择全相联映射。 (4)替换策略: 如下图所示,提示输入替换策略,1代表先进先出(First-In—First—Out,FIFO)算法、2代表近期最少使用(Least RecentlyUsed,LRU)算法、3代表最不经常使用(Least Frequently Used,LFU)、4代表随机法(Random)。此处选择先进 先出. (5)写策略: 如下图所示,提示输入Cache得读写操作,1代表写直达法(存直达法)即写操作时数据既写入Cache又写入主存、2代表写回法(拷回法)即写操作时只把数据写入Cache而不写入主存,但当Cache数据被替换出去时才写回主存。此处选写回法

第二章计算机组成原理(5) 一、选择题 1、下列关于IC卡的叙述中,错误的是______ D ___。 A.IC卡是"集成电路卡"的简称 B.IC卡中内嵌有集成电路芯片 C.IC卡不仅可以存储数据,还可以通过加密逻辑对数据进行加密 D.非接触式IC卡依靠自带电池供电 2、下列关于USB接口的说法错误的是___ A _____。 https://www.doczj.com/doc/948897934.html,B接口只有一种标准(版本) B.一个USB接口通过USB集线器可以连接多 个设备 https://www.doczj.com/doc/948897934.html,B的中文含义是通用串行总线 https://www.doczj.com/doc/948897934.html,B接口连接的设备可以热插拔,即不需要关机就可以插拔设备 3、以下打印机中,需要安装硒鼓才能在打印纸上印出文字和图案的是____ A ____。 A.激光打印机 B.压电喷墨式打印机 C.热喷墨式打印机 D.针式打印 机 4、移动存储器有多种,目前已经不常使用的是__ D __。 A. U盘 B. 存储卡 C. 移动硬盘 D. 磁带 5、销售广告标为"P4/1.5G/512MB/80G"的一台个人计算机,其CPU的时钟频率是___ B _____。 A.512MHz B.1500MHz C.80000MHz D.4MHz 6、下列关于USB接口的叙述,正确的是_A_。 https://www.doczj.com/doc/948897934.html,B接口是一种总线式串行接口 https://www.doczj.com/doc/948897934.html,B接口是一种并行接口 https://www.doczj.com/doc/948897934.html,B接口是一种低速接口 https://www.doczj.com/doc/948897934.html,B接口不是通用接口 7、显示器分辨率是衡量显示器性能的一个重要指标,它指的是整屏可显示多少__D______。 A.颜色 B.ASCII字符 C.中文字符 D.像素 8、下面属于PC机标准输入设备的是_____ A ___。 A.键盘 B.触摸屏 C.扫描仪 D.数码相机 9、下面有关计算机输入输出操作的叙述中,错误的是____ C ____。 A.计算机输入/输出操作比CPU的速度慢得多 B.两个或多个输入输出设备可以同时进行工作 C.在进行输入/输出操作时,CPU必须停下来等候I/O操作的完成 D.每个(或每类)I/O设备都有各自专用的控制器 10、下面关于硬盘存储器信息存储原理的叙述中,错误的是______ D _______。 A.盘片表面的磁性材料粒子有两种不同的磁化方向,分别用来记录 "0"和"1" B.盘片表面划分为许多同心圆,每个圆称为一个磁道,盘面上一般都有几千个磁道 C.每条磁道还要分成几千个扇区,每个扇区的存储容量一般为512字节 D.与CD光盘片一样,每个磁盘片只有一面用于存储信息 11、下面关于硬盘存储器结构与组成的叙述中,错误的是______ D _____。 A.硬盘由磁盘盘片、主轴与主轴电机、移动臂、磁头和控制电路等组成 B.磁盘盘片是信息的存储介质 C.磁头的功能是读写盘片上所存储的信息 D.盘片和磁头密封在一个盒状装置内,主轴电机安装在PC主板上 12、下面关于液晶显示器的叙述中,错误的是_____D___。

一、选择题 1.冯·诺伊曼机工作方式的基本特点是______。 A.多指令流单数据流;B.按地址访问并顺序执行指令; C.堆栈操作;D.存储器按内容选择地址。 2.______表示法主要用于表示浮点数中的阶码。 A.原码B.补码C.反码D.移码 3.一个16K×32位的存储器,其地址线和数据线的总和是______。 A.48 B.46 C.36 D.40 4. 在指令的地址字段中,直接指出操作数本身的寻址方式,称为______。 A. 隐含寻址 B. 立即寻址 C. 寄存器寻址 D. 直接寻 址 5. 信息只用一条传输线,且采用脉冲传输的方式称为______。 A.串行传输 B.并行传输 C.并串行传输 D.分时传输 6. 和外存储器相比,内存储器的特点是______。 A.容量大、速度快、成本低 B.容量大、速度慢、成本高 C.容量小、速度快、成本高 D.容量小、速度快、成本低 7. 在CPU中,暂存指令的寄存器是______。 A. 数据寄存器 B. 程序计数器 C. 状态条件寄存器 D. 指令寄存器 8. EPROM是指______。 A. 读写存储器 B. 只读存储器 C. 可编程的只读存储器 D. 光擦除可编程的只读 存储器 9. 下列数中最小的数是______。 A.(1101001)2 B.(52)8 C.(133)8 D.(30)16 10. 假定下列字符码中有奇偶校验位,但没有数据错误,采用偶校验的字 符码是______。 A.11001011 B.11010110 C.11000001 D.11001001 11. 单地址指令中为了完成两个数的算术运算,除地址码指明的一个操作 数外,另一个数常需采用______。 A. 堆栈寻址方式 B. 立即寻址方式 C.隐含寻址方式 D. 间接寻址方式 12. 用于对某个寄存器中操作数的寻址方式称为______寻址。 A. 直接 B. 间接 C. 寄存器直接 D. 寄存器间接 13. 中央处理器(CPU)包含______。 A.运算器 B.控制器 C.运算器、控制器和cache D.运算器、控制器和主存 14. 在CPU中跟踪指令后继地址的寄存器是______。 A.主存地址寄存器 B.程序计数器 C.指令寄存器 D.状态条件寄存器 15. 在集中式总线仲裁中,______方式响应时间最快。 A.链式查询 B.计数器定时查询 C.独立请求 D.以上三种相同

汕头大学实验报告 学院: 工学院系: 计算机系专业: 计算机科学与技术年级: 13实验时间: 2015.6.16 姓名: 林子伦学号: 2013101030实验名称:基于SPIM-CACHE的Cache实验 一.实验目的: (1)熟悉SPIM-CACHE模拟器环境 (2)深入认识CACHE的工作原理及其作用。 二.实验内容: (1)阅读实验指导书资料(虚拟教室提供了英文论文的电子版本); (2)下载SPIM-CACHE软件,理解英文论文的基本内容之后,给出几种典型的cache配置,运行英文论文提供的代码,记录运行时CACHE命中率等重要数据;(3)运行Fig.4代码,了解mapping functions 即映射规则 (4)运行Fig.7代码,了解temporal and spatial locality 即时空局部性,进一步理解cache的工作原理; (5)运行Fig.8代码,运行学习replacement algorithms 即替代算法,理解其工作原理。 三.实验地点,环境 实验地点:软件工程实验室 实验环境: 操作系统:Microsoft Windows 8 中文版 处理器:Intel(R) Core(TM) i3-3120M CPU @ 2.50GHz 2.50GHz 内存: 4.00GB(3.82GB 可用) 四.实验记录及实验分析(80%): 4.1实验前配置: 1) 按下图配置好Spim设置

2)关于实验中cache设置如下(具体配置根据下面实验要求) ——》 ——》 Cache size ——cache大小 Block size ——块大小 Mapping ——组相连 4.2实验一:fig4.s 实验目的:Algorithm and corresponding code to study mapping functions Cache配置:256-B size, 16-B line size, four-way set associative 实验操作: 1) Ctrl+O 打开运行代码fig4.s 代码如下: .data 0x10000480 Array_A: .word 1,1,1,1,2,2,2,2 .data 0x10000CC0 Array_B: .word 3,3,3,3,4,4,4,4 .text .globl _start _start: la $2,Array_A li $6,0 li $4,8 loop: lw $5,0($2) add $6,$6,$5 addi $2,$2,4

计算机系统结构实验报告 名称: Cache性能分析学院:信息工程 姓名:陈明 学号:S121055 专业:计算机系统结构年级:研一

实验目的 1.加深对Cache的基本概念、基本组织结构以及基本工作原理的理解; 2.了解Cache的容量、相联度、块大小对Cache性能的影响; 3.掌握降低Cache失效率的各种方法,以及这些方法对Cache性能提高的好处; 4.理解Cache失效的产生原因以及Cache的三种失效; 5.理解LRU与随机法的基本思想,及它们对Cache性能的影响; 实验平台 Vmware 虚拟机,redhat 9.0 linux 操作系统,SimpleScalar模拟器 实验步骤 1.运行SimpleScalar模拟器; 2.在基本配置情况下运行程序(请指明所选的测试程序),统计Cache总失效 次数、三种不同种类的失效次数; 3.改变Cache容量(*2,*4,*8,*64),运行程序(指明所选的测试程序), 统计各种失效的次数,并分析Cache容量对Cache性能的影响; 4.改变Cache的相联度(1路,2路,4路,8路,64路),运行程序(指明所 选的测试程序),统计各种失效的次数,并分析相联度对Cache性能的影响; 5.改变Cache块大小(*2,*4,*8,*64),运行程序(指明所选的测试程 序),统计各种失效的次数,并分析Cache块大小对Cache性能的影响; 6.分别采用LRU与随机法,在不同的Cache容量、不同的相联度下,运行程序 (指明所选的测试程序)统计Cache总失效次数,计算失效率。分析不同的替换算法对Cache性能的影响。 预备知识 1. SimpleScalar模拟器的相关知识。详见相关的文档。 2. 复习和掌握教材中相应的内容 (1)可以从三个方面改进Cache的性能:降低失效率、减少失效开销、减少Cache命中时间。 (2)按照产生失效的原因不同,可以把Cache失效分为三类: ①强制性失效(Compulsory miss)

第二章计算机组成原理(2) 一、选择题 1、以下关于计算机指令系统的叙述中,正确的是_____ B ___。 A.用于解决某一问题的一个指令序列称为指令系统 B.计算机指令系统中的每条指令都是CPU可执行的 C.不同类型的CPU,其指令系统是完全一样的 D.不同类型的CPU,其指令系统完全不一样 2、以下符号中____ C ____代表一种I/O总线标准。 A.CRT B.VGA C.PCI D.DVD 3、以下打印机中,需要安装硒鼓才能在打印纸上印出文字和图案的是____ A ____。 A.激光打印机 B.压电喷墨式打印机 C.热喷墨式打印机 D.针式打印 机 4、移动存储器有多种,目前已经不常使用的是__ D __。 A. U盘 B. 存储卡 C. 移动硬盘 D. 磁带 5、销售广告标为"P4/1.5G/512MB/80G"的一台个人计算机,其CPU的时钟频率是___ B _____。 A.512MHz B.1500MHz C.80000MHz D.4MHz 6、现在激光打印机与主机连接多半使用的是____B___接口,而以前则大多使用并行接口。 A.SATA https://www.doczj.com/doc/948897934.html,B C.PS/2 D.IEEE-1394 7、显示器分辨率是衡量显示器性能的一个重要指标,它指的是整屏可显示多少__D______。 A.颜色 B.ASCII字符 C.中文字符 D.像素 8、下面属于PC机标准输入设备的是_____ A ___。 A.键盘 B.触摸屏 C.扫描仪 D.数码相机 9、下面有关计算机输入输出操作的叙述中,错误的是____ C ____。 A.计算机输入/输出操作比CPU的速度慢得多 B.两个或多个输入输出设备可以同时进行工作 C.在进行输入/输出操作时,CPU必须停下来等候I/O操作的完成 D.每个(或每类)I/O设备都有各自专用的控制器 10、下面关于硬盘存储器信息存储原理的叙述中,错误的是______ D _______。 A.盘片表面的磁性材料粒子有两种不同的磁化方向,分别用来记录 "0"和"1" B.盘片表面划分为许多同心圆,每个圆称为一个磁道,盘面上一般都有几千个磁道 C.每条磁道还要分成几千个扇区,每个扇区的存储容量一般为512字节 D.与CD光盘片一样,每个磁盘片只有一面用于存储信息 11、下面关于硬盘存储器结构与组成的叙述中,错误的是______ D _____。 A.硬盘由磁盘盘片、主轴与主轴电机、移动臂、磁头和控制电路等组成 B.磁盘盘片是信息的存储介质 C.磁头的功能是读写盘片上所存储的信息 D.盘片和磁头密封在一个盒状装置内,主轴电机安装在PC主板上 12、下面关于液晶显示器的叙述中,错误的是_____D___。 A.它的英文缩写是LCD B.它的工作电压低,功耗小 C.它几乎没有辐射 D.它与CRT显示器不同,不需要使用显示卡 13、下面关于鼠标器的叙述中,错误的是___ C _____ A.鼠标器输入计算机的是其移动时的位移量和移动方向 B.不同鼠标器的工作原理基本相同,区别在于感知位移信息的方法不同

《计算机组成原理》模拟试题 一、填空选择题(每空1分,共30分) 1.______表示法主要用于表示浮点数中的阶码。 A. 原码 B. 补码 C. 反码 D. 移码 2.下列有关运算器的描述中,______是正确的。 A.只做算术运算,不做逻辑运算 B. 只做加法 C.能暂时存放运算结果 D. 既做算术运算,又做逻辑运算 3. CPU主要包括______。 A.控制器 B.控制器、运算器、cache C.运算器和主存 D.控制器、ALU和主存 4、针对8位二进制数,下列说法中正确的是。 A、-127的补码为10000000 B、-127的反码等于0的移码 C、+1的移码等于-127的反码 D、0的补码等于-1的反码 我的答案:B 5、已知定点整数x的原码为,且,则必有。 A、 B、 C、,且不全为0 D、,且不全为0 我的答案:A得分: 14.3分 6、已知定点小数x的反码为,且,则必有。 A、 B、

C、不全为0 D、 我的答案:D得分: 14.3分 7、若某数x的真值为-0.1010,在计算机中该数表示为1.0110,则该数所用的编码方法为码。 ?A、原 ?B、补 ?C、反 ?D、移 我的答案:B得分: 14.3分 8、某机字长为32位,采用定点小数表示,符号位为1位,尾数为31位,则可表示的最大正小数为①,最小负小数为②。 A、 B、 C、 D、 我的答案:CD 9、指令系统中采用不同寻址方式的目的主要是。 A、实现存储程序和程序控制 B、缩短指令长度,扩大寻址空间,提高编程灵活性 C、可以直接访问外存 D、提供扩展操作码的可能并降低指令译码难度 正确答案:B 我的答案:B得分: 12.5分 10、变址寻址方式中,操作数的有效地址是______。 A、基址寄存器内容加上形式地址(位移量) B、程序计数器内容加上形式地址 C、变址寄存器内容加上形式地址

Cache模拟器 一、实验目标: 程序运行时,都会对内存进行相关操作,所访问的内存地址可以被记录下来,形成memory trace文件。在本实验中,你将使用benchmark 程序产生的memory trace文件来测试Cache命中率,文件可以在https://www.doczj.com/doc/948897934.html,/classes/fa07/cse240a/proj1-traces.tar.gz上获得。每次存储器访问都包含了三个信息: 1.访问类型,’l’表示Load操作,’s’表示Store操作; 2.地址。采用32位无符号的十六进制表示; 3.存储器访问指令之间的间隔指令数。例如第5条指令和第10条指 令为存储器访问指令,且中间没有其他存储器访问指令,则间隔指令数为4。 通过写一段程序,模拟Cache模拟器的执行过程。 二、实验要求: 写一段程序模拟Cache模拟器的执行过程,并对5个trace文件进行测试,完成以下目标: 1.请统计Load类型指令和Store类型指令在这5个trace文件中的指令比例。 2.设Cache总容量为32KB,对以下所有参数进行组合(共有72种组合),测量相应5个文件的Cache命中率。通过对命中率的分析,可以发现什么规律。

行大小:32字节、64字节、128字节 相连度:8路相联、4路相联、2路相联、1路相联 替换策略:FIFO,随机替换,LRU 写策略:写直达、写回 3. 给出5个文件的最佳Cache命中率的参数组合。针对不同的trace 文件,最佳配置是否相同。 4. 测量各种组合下Cache和主存之间的数据传输量。 5. 给出5个文件的最小数据传输量的参数组合。这个组合和第3问中得到的组合是否一致。针对不同的trace文件,最佳配置是否相同。 6. Cache缺失有三种原因:1)强制缺失;2)容量缺失;3)冲突缺失。分析这三种缺失并说明你的分析方法。 7. 请给出5个trace文件在最优Cache命中率的情况下,这三种缺失所占的比例,并和教材图C.8给出的比例进行比较。 三、程序设计与实现: 本程序我打算采用java进行编写,因为java能够很好地体现面向对象编程的优点。首先需要定义相关的数据类型。 将指令定义为一个单独的指令类,好方便操作和记录统计,其中属性包括该指令的类型,比如是Load指令还是Store指令,还包括指令的地址。 class Instruction { String type; String addrs; }

计算机系统结构实验报告 一.流水线中的相关 实验目的: 1. 熟练掌握WinDLX模拟器的操作和使用,熟悉DLX指令集结构及其特点; 2. 加深对计算机流水线基本概念的理解; 3. 进一步了解DLX基本流水线各段的功能以及基本操作; 4. 加深对数据相关、结构相关的理解,了解这两类相关对CPU性能的影响; 5. 了解解决数据相关的方法,掌握如何使用定向技术来减少数据相关带来的暂停。 实验平台: WinDLX模拟器 实验内容和步骤: 1.用WinDLX模拟器执行下列三个程序: 求阶乘程序fact.s 求最大公倍数程序gcm.s 求素数程序prim.s 分别以步进、连续、设置断点的方式运行程序,观察程序在流水线中的执行情况,观察 CPU中寄存器和存储器的内容。熟练掌握WinDLX的操作和使用。 2. 用WinDLX运行程序structure_d.s,通过模拟找出存在资源相关的指令对以及导致资源相 关的部件;记录由资源相关引起的暂停时钟周期数,计算暂停时钟周期数占总执行周期数的 百分比;论述资源相关对CPU性能的影响,讨论解决资源相关的方法。 3. 在不采用定向技术的情况下(去掉Configuration菜单中Enable Forwarding选项前的勾选符),用WinDLX运行程序data_d.s。记录数据相关引起的暂停时钟周期数以及程序执行的 总时钟周期数,计算暂停时钟周期数占总执行周期数的百分比。 在采用定向技术的情况下(勾选Enable Forwarding),用WinDLX再次运行程序data_d.s。重复上述3中的工作,并计算采用定向技术后性能提高的倍数。 1. 求阶乘程序 用WinDLX模拟器执行求阶乘程序fact.s。这个程序说明浮点指令的使用。该程序从标准 输入读入一个整数,求其阶乘,然后将结果输出。 该程序中调用了input.s中的输入子程序,这个子程序用于读入正整数。 实验结果: 在载入fact.s和input.s之后,不设置任何断点运行。 a.不采用重新定向技术,我们得到的结果

计算机体系结构—— Cache模拟器实验 实验报告 姓名崔雪莹 学号 班级计科1202班 老师董岚 2015年 06月07日

一、阅读分析附件模拟器代码...............................错误!未定义书签。 1、关键参数.......................................错误!未定义书签。 2、关键算法.......................................错误!未定义书签。 二、课后习题.............................................错误!未定义书签。 1、习题内容.......................................错误!未定义书签。 2、题目分析.......................................错误!未定义书签。 3、计算及结果.....................................错误!未定义书签。 4、模拟器上实验结果检验...........................错误!未定义书签。 三、整体分析.............................................错误!未定义书签。 1、三种映射方式对Cache效率的的影响...............错误!未定义书签。 2、block块大小与Cache容量对Cache效率的影响 .....错误!未定义书签。 3、Cache容量与相连度对Cache效率的影响...........错误!未定义书签。 4、三种失效类型影响因素...........................错误!未定义书签。 四、实验思考和感受.......................................错误!未定义书签。 1、关于模拟器的思考...............................错误!未定义书签。 2、关于整个实验的思考.............................错误!未定义书签。

《计算机组成原理》模拟试题一 一、填空题 1、若[X]补=X0.X1X2X3X4则[X/4]补= ()。 2、局部性原理分为()局部性和()空间局部性。 3、六管静态存储单元利用()保存信息,动态 存储单元利用()保存信息。 4、冯诺依曼计算机的工作原理是() 5、动态存储器的刷新是以()方式进行的。 6、操作数在寄存器中是()寻址方式、操作数地址在内存中 是()寻址方式 7、128KX8位的RA M,不考虑电源线,还有()个引脚 二、名词解释 透明性、固件、存储体系、中断、寻址方式、接口 三、计算题 1、已知X= 0.1001 , Y= - 0.1011用变形补码计算X - Y ,并判断是否溢 出(5’写详细步骤) 2、设数的阶码为3位,尾数为6位(均不含符号位),按照计算机补码 浮点数运算步骤计算X+Y (写详细步骤) X= 2 -011X(-0.100100)Y= 2 - 010 X 0.011010 四、已知16位机需要1M的存储空间,使用16KX8位的静态存储器芯片构 造该计算机的存储器,并允许访问最大的存储空间,选用模板结构形式。 1.若每个摸板为128KX16位,构成该机的主存共需要多少摸板 2.上述每个摸板内有多少个16KX8位存储器芯片 3. 画出该存储器与CPU的连接,并计算每个摸板的全局地址范围 五、判断正误,并改正你认为错误的。 1、CACHE和虚拟存储器对系统程序员都是不透明的() 2、动态存储器的刷新是按行进行的,刷新地址由CPU给出() 3、多操作数指令可以是单字长指令() 4、从逻辑功能上看,硬件和软件的功能是等价的() 5、指令的功能是由操作码决定的()

桂林理工大学2013年春季学期 <<计算机组成原理X>>课程论文 题目:高速缓冲存储器Cache的工作原 理及技术实现 专业:网络工程 班级:网络11-2班 学号:3110757202 姓名:xxx 信息科学与工程学院 2013年7月

【内容摘要】 缓冲存储器用在两个工作速度不同的硬件之间,在交换信息过程中起到缓冲作用,它能提高计算机系统的工作效益。高速缓冲存储器Cache 是架设在CPU与内存之间的临时存储器,它的容量比内存小但交换速度快,主要用来提高CPU提取数据的速度,Cache作为PC系统中一个重要功能部件,已成为评价和选购P C系统的重要指标,下面主要谈谈Cache的原理、设计及发展趋势。 【关键词】Cache CPU 命中率映像局部性原理 【前言】 我们通常都认为计算机的速度是由CPU决定的, 虽然CPU主频的提升会带动系统性能的改善,但系统性能的提高不仅仅取决于CPU,还要有其它的硬件或软件来充分发挥它的速度,与系统架构、指令结构、信息在各个部件之间的传送速度及存储部件的存取速度等因素有关,特别是与CPU/内存之间的存取速度有关。我们知道要使用的软件都要通过主存储器(内存)才能运行,而主存储器的运行速度和CPU之间有一个数量级的差距,这就限制了CPU速度潜力的发挥,若CPU工作速度较高,但内存存取速度较低,则造成CPU等待,降低处理速度,浪费CPU的能力。如500MHz的PⅢ,一次指令执行时间为2ns,与其相配的内存(SDRAM)存取时间为10ns,比前者慢5倍,CPU和PC的性能怎么发挥出来? 如何减少CPU与内存之间的速度差异?有4种办法:一种是在基本总线周期中插入等待,这样会浪费CPU的能力。另一种方法是采用存取时

实验6 Cache 性能分析 6.1 实验目的 1. 加深对Cache 的基本概念、基本组织结构以及基本工作原理的理解; 2. 掌握Cache 的容量、相联度、块大小对Cache 性能的影响; 3. 掌握降低Cache 不命中率的各种方法,以及这些方法对Cache 性能提高的好处; 4. 理解LRU 与随机法的基本思想以及它们对Cache 性能的影响; 6.2 实验平台 实验平台采用Cache 模拟器My Cache 。 6.3 实验内容及步骤 首先要掌握My Cache 模拟器的使用方法。 6.3.1 Cache 的容量对不命中率的影响 1. 启动MyCache 模拟器。 2. 用鼠标单击“复位”按钮,把各参数设置为默认值。 3. 选择一个地址流文件。方法:选择“访问地址”→“地址流文件”选项,然后单击“浏 览”按钮,从本模拟器所在的文件夹下的“地址流”文件夹中选取。 4. 选择不同的Cache 容量,包括2KB 、4KB 、8KB 、16KB 、32KB 、64KB 、128KB 和256KB 。分 别执行模拟器(单击“执行到底”按钮即可执行),然后在表5.1中记录各种情况下的不命中率。 地址流文件名: E:\cjh\系统结构模拟器\MyCache 模拟器\地址流\all.din 5. 以容量为横坐标,画出不命中率随Cache 容量变化而变化的曲线,并指明地址流文件名。 不命中率随Cache容量变化图 0.00% 2.00%4.00%6.00%8.00%10.00%12.00%2 4 8 16 32 64 128 Cache容量(KB) 不命中率 6据结果,你能得出什么结论? 6.3.2 相联度对不命中率的影响 1. 用鼠标单击“复位”按钮,把各参数设置为默认值。此时的Cache 的容量为64KB 。 2. 选择一个地址流文件。方法:选择“访问地址”→“地址流文件”选项,然后单击“浏 览”按钮,从本模拟器所在的文件夹下的“地址流”文件夹中选取。 3. 选择不同的Cache 相联度,包括直接映像、2路、4路、8路、16路和32路。分别执行 模拟器(单击“执行到底”按钮即可执行),然后在表5.2中记录各种情况下的不命中