基于FPGA 的伪随机序列的生成方法及应用

- 格式:docx

- 大小:382.87 KB

- 文档页数:5

基于FPGA的伪随机序列的生成方法及应用

张金宝;李新阳;陈波

【期刊名称】《微计算机信息》

【年(卷),期】2009(025)029

【摘要】通过分析各种伪随机序列生成方法,提出了一种基于M序列的连续抽样方法,可以生成满足自适应光学系统SPGD控制算法要求的多路、相互独立以及服从伯努利分布的伪随机序列.该方法适合于用FPGA等超大规模集成电路实现,且具有占用硬件资源较少,实现方便等优点.用FPGA实现了用于61单元自适应光学系统SPGD控制算法的伪随机序列,并将此方法应用于基于SPGD控制算法的自适应光学系统实验中,实验表明,该方法能够满足自适应光学系统SPGD算法的需求,系统实现成功闭环.

【总页数】3页(P153-155)

【作者】张金宝;李新阳;陈波

【作者单位】610209,成都,中国科学院光电技术研究所;100039,北京,中国科学院研究生院;610209,成都,中国科学院光电技术研究所;610209,成都,中国科学院光电技术研究所;100039,北京,中国科学院研究生院

【正文语种】中文

【中图分类】TP301.6;TP331.1+1

【相关文献】

1.基于余数系统与置换多项式的高速长周期伪随机序列生成方法 [J], 马上;刘剑锋;杨泽国;张艳;胡剑浩

2.基于非规则二值化的伪随机序列生成方法 [J], 陈亚如;张雪锋

3.基于随机序列统计特性的伪随机序列生成方法 [J], 柏森;周龙福;郭辉;闫兵;

4.基于FPGA的Leap-forward型线性反馈移位寄存器在伪随机序列算法中的应用[J], 郝洪伟;

5.基于海绵函数的快速伪随机序列生成方法 [J], 赵磊; 郑东; 任方

因版权原因,仅展示原文概要,查看原文内容请购买。

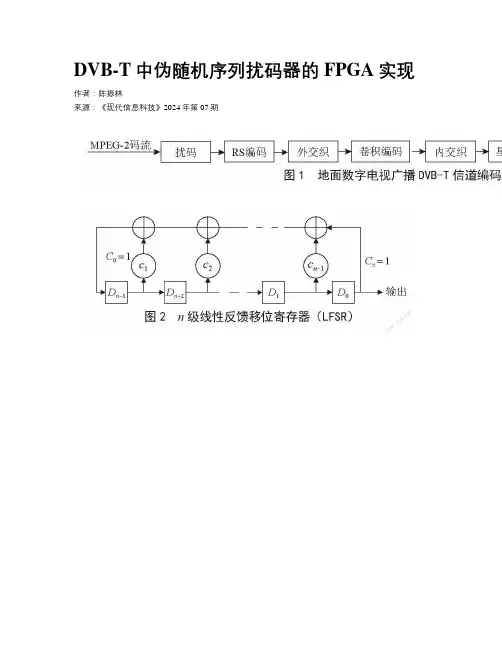

DVB-T中伪随机序列扰码器的FPGA实现作者:***来源:《现代信息科技》2024年第07期收稿日期:2023-07-20DOI:10.19850/ki.2096-4706.2024.07.003摘要:伪随机序列在伪码测距、导航、数字数据扰乱器、噪声产生器、通信加密中有着广泛的应用。

在这些实际应用中,常常利用现场可编程门阵列(FPGA)来产生伪随机序列,这便于系统设计和测试的实现。

针对数字地面电视广播(DVB-T)标准,以线性反馈移位寄存器电路为基础,设计了一种并行伪随机序列产生方法,该方法简单而高效地实现DVB-T系统码流数据的扰码。

实验结果表明,MATLAB扰码算法结果与FPGA扰码模块仿真结果和硬件实现结果一致,该设计方法切实可行。

关键词:伪随机序列;DVB-T;MATLAB;FPGA;Verilog中图分类号:TN914.3 文献标识码:A 文章编号:2096-4706(2024)07-0011-05FPGA Implementation of Pseudo-random Sequence Scrambler in DVB-TCHEN Zhenlin(Electronic Information School, Foshan Polytechnic, Foshan 528137, China)Abstract: Pseudo-random sequence is widely used in pseudo-code ranging, navigation,digital data scramblers, noise generators and communication encryption. In the practical application, the FPGA is usually used to generate pseudo-random sequences, which can bring great convenience to system design or testing. Aiming at the DVB-T standard, based on the linear feedback shift register circuit, a simple and efficient parallel pseudo-random sequence generation method is designed to realize the scrambling of DVB-T system code flow data. The experimental results show that the MATLAB scrambling algorithm results are consistent with the FPGA scrambling module simulation results and hardware implementation results, so the design method is feasible.Keywords: pseudo-random sequence; DVB-T; MATLAB; FPGA; Verilog0 引言目前,数字通信已经成为当代通信技术的主流,数字通信的应用越来越广泛,人们开始追求更高的通信质量。

fpga 伪随机二进制序列作用FPGA(现场可编程逻辑门阵列)是一种可重构的硬件平台,可以实现定制的数字逻辑电路功能。

FPGA在许多领域都有广泛应用,其中之一是生成伪随机二进制序列(Pseudo Random Binary Sequence,PRBS)。

伪随机二进制序列是一种特殊的数字序列,具有类似于随机序列的特征,但实际上是根据特定算法生成的。

在现实世界中,我们经常需要使用具有随机性质的序列,比如在通信系统中进行数据调制和解调、信号分析和测试等。

FPGA生成伪随机二进制序列的过程基于特定的算法和初始种子值。

常见的算法有线性反馈移位寄存器(Linear Feedback Shift Register,LFSR)和伪随机数发生器(Pseudo Random Number Generator,PRNG)。

下面,我们将探讨伪随机二进制序列在不同领域的应用。

首先,在通信系统中,伪随机二进制序列被广泛应用于数据调制和解调。

调制是将数字信号转换为模拟信号的过程,解调则是将模拟信号转换为数字信号的过程。

在数字调制中,我们需要将原始数据通过一系列的变换映射到不同的频率或相位上,以便在传输过程中提供更好的抗干扰性能。

伪随机二进制序列可以用作调制器和解调器之间的同步信号,确保数据在传输过程中正确地被解调。

其次,信号分析也是伪随机二进制序列的重要应用领域之一。

信号分析是指对特定信号进行检测、测量和解释的过程,以从中获得关键信息。

在通信和雷达领域,我们经常需要对信号进行频谱分析,以检测其中的频率成分和特征。

伪随机二进制序列可以用作信号激励源,通过将其与待分析信号混合,可以提取出待分析信号的频谱特征。

最后,在测试和验证领域,伪随机二进制序列发挥着至关重要的作用。

在芯片设计和电路板测试中,我们经常需要对电路进行功能测试和故障诊断。

伪随机二进制序列可以用作测试源,通过将其输入待测试电路,我们可以观察电路的输出响应,并判断电路是否正常工作。

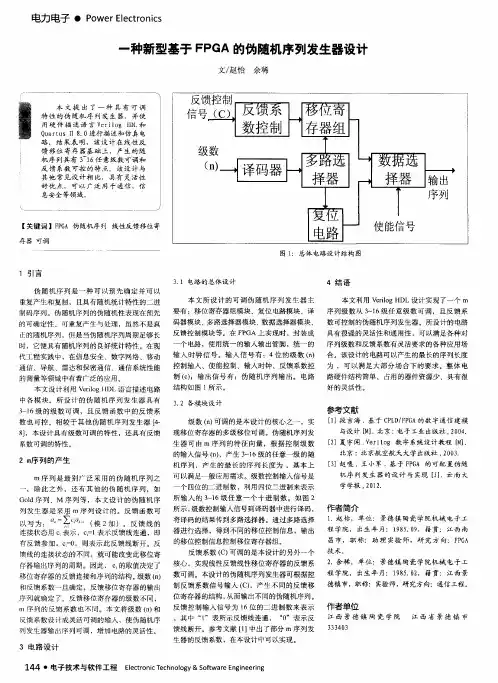

基于FPGA的伪随机序列发生器设计方案1基本概念与应用1)1FSR:线性反馈移位寄存器(1inear feedbackshiftregister,1FSR)是指给定前一状态的输出,将该输出的线性的薮再用作输入的移位寄存器。

异或运算是最常见的单比特线性函数:对寄存器的某些位进行异或操作后作为输入,再对寄存器中的各比特进行整体移位。

1FSR产生的两种形式为伽罗瓦(Ga1ois)和斐波那契(FibonaCCi)两种形式。

也有成为外部(Ex隹rna1)执行方式和内部(Interna1)执行方式。

(1)伽罗瓦方式(Interna1)X0X4X17! ! TepCount ,-Θ□□EF-Γ>4300000000Θ{3B0-*~*DaiaFtowW>)∙ι.x4.χ“(Ga1oisImp1ementation)Ga1ois方式特征数据的方向从左至右,反馈线路是从右至左。

其中XCo项(本原多项式里面的T'这一项)作为起始项。

按照本原多项式的指示确定异或门(XOR)在移位寄存器电路上的位置。

如上图所示XM。

因此Ga1ois方式也有人称作线内或模类型(M-型)1FSRo(2)斐波那契方式(Externa1)TapCountB*0;E3t3-⅛QEHIH30GHZHHDGIFSHpcivncrTMrig(M)-X14.X,>♦X n»1(Fibonacciimp1ementation)从图中我们可以看到Fibonacci方式的数学流向和反馈形式是恰好跟Ga1ois方式相反的,按照本原多项式,其中XCO这一项作为最后一项,这里需要一个XOR∏,将本原多项式中所给的taps来设定它的异或方式。

因此Fibonacci方式也被叫做线外或者简型(S-型)1FSR。

2)本原多项式本原多项式是近世代数中的一个概念,是唯一分解整环上满足所有系数的最大公因数为1的多项式。

本原多项式不等于零,与本原多项式相伴的多项式仍为本原多项式。

0 引言伪随机序列现已广泛应用于密码学、扩频通讯、导航、集成电路的可测性设计、现代战争中的电子对抗技术等许多重要领域。

伪随机序列的伪随机性表现在预先的可确定性、可重复产生与处理。

伪随机序列虽然不是真正的随机序列,但是当伪随机序列周期足够长时,它便具有随机序列的良好统计特性。

在已有的序列中,m序列的应用最为成熟和广泛,为此,本文给出线性m序列和基于m序列的非线性m子序列的FPGA实现方法。

由于FPGA的内部逻辑功能是通过向内部静态存储器单元加载配置数据来实现的,其配置文件决定了逻辑单元的逻辑功能以及模块间或与I/O间的连接,故可最终决定FPGA实现的功能。

FPGA的这种结构允许多次编程,并享有快速有效地对新设计进行优化的灵活性,为此,本文选用了altera 的cvclone系列FPGA芯片EPlC12-240PQFP,该芯片内部有12060个逻辑单元、239616 bit RAM、两个锁相环(PLL)。

本文应用移位寄存器理论来产生序列,其算法的关键是找到线性m序列和非线性m子序列移位寄存器的反馈逻辑式。

1 m序列的实现1.1 基于FPGA的m序列实现利用反馈移位寄存器产生0、1序列时,其n位反馈移位寄存器的逻辑功能如图1所示。

图中,xi蕾表示寄存器所处的状态,通常用0和1来代表两个可能的状态,并且把0和1看成是有限域GF(2)的两个元素。

f(x0,x1,…,xn-1)刻划了移位寄存器反馈逻辑的功能,它可以看成一个定义在GF(2)上并且在GF(2)中取值的n元函数,当f(x0,x1…,xn-1)可以表示成一线性齐次函数时。

即,相应的反馈移位寄存器是线性的,而由线性移位寄存器产生的序列就称为线性移位寄存器序列。

m序列就是线性移位寄存器序列。

对于一个n级m序列移位寄存器来说。

它在每一时刻的内部状态都可以看做有限域GF(2)上的一个n维向量,而反馈函数就是刻划了从每一时刻的状态到下一时刻状态的转移规律,或者说反馈函数定义了n维向量空间上的一个线性变换。

基于FPGA的m序列发生器摘要m序列广泛应用于密码学、通信、雷达、导航等多个领域,本文提出了一种基于FPGA的伪随机序列产生方法,应用移位寄存器理论从序列的本原多项式出发,获得产生该序列的移位寄存器反馈逻辑式,结合FPGA芯片结构特点,在序列算法实现中采用元件例化语句。

算法运用VHDL语言编程,以A1tera的QuartusⅡ软件为开发平台,给出了序列的仿真波形。

序列的统计特性分析表明:该方法产生的序列符合m序列的伪随机特性,验证了算法的正确性。

关键词:m序列;移位寄存器理论;VHDL语言1 m序列m序列是伪随机序列的一种 ,结构简单 ,实现方便。

在现代工程实践中 , m 序列在通讯、导航、雷达、通信系统性能的测量等领域中有着广泛的应用。

例如 , 在连续波雷达中可用作测距信号 , 在遥控系统中可用作遥控信号 , 在多址通信中可用作地址信号 , 在数字通信中可用作群同步信号 ,还可用作噪声源及在保密通信中起加密作用等。

伪噪声发生器在测距、通信等领域的应用日益受到人们重视。

目前,m序列产生实现方法主要有3种:(1)门电路实现该方法设计简单,但随移位寄存器级数的增长,电路装调困难,且占用的印制板面积较大。

(2)DSP编程实现该方法专业性过强,不适合一般用户。

(3)VHDL与CPLD实现由于CPLD的高集成度,而且VHDL语言编程较为方便,故可以大大减少电路的装调的困难。

文章提出VHDL语言实现,,l序列电路是周期、初相位可编程变化的,其应用较为灵活,通过微处理器对其进行适当的初始化,即可产生用户所需周期、初相位的m序列输出。

用软件方式构成的特点是采用灵活的数据查询方式可以获得任意级数 n 的本原多项式系数 ,从而实现 m 序列的产生 , 但速度受到单片机工作速度的限制。

而 FPGA 具有硬件电路实现的优点 , 又具有设计上的灵活性 , 并且由于FPGA 便于实现大规模的数字系统。

1.1 理论基础m 序列是最长线性反馈移位寄存器序列的简称,它是由带线性反馈的移位寄存器产生的周期最长的一种序列。

基于FPGA的伪随机序列发生器设计随着通信理论的发展,早在20世纪40年代末,香农(Shannon)就曾指出,在某些情况下,为了实现最有效的通信,应采用具有白噪声的统计特性的信号。

目前广泛应用的伪随机噪声由数字电路产生的周期序列(经滤波等处理后)得到的。

我们将这种周期序列称为伪随机序列。

伪随机序列概述伪随机序列发展及应用随着通信技术的发展,在某些情况下,为了实现最有效的通信应采用具有白噪声统计特性的信号;为了实现高可靠的保密通信,也希望利用随机噪声;另外在测试领域,大量的需要使用随机噪声来作为检测系统性能的测试信号。

然而,利用随机噪声的最大困难是它难以重复再生和处理。

伪随机序列的出现为人们解决了这一难题。

伪随机序列具有类似于随机噪声的一些统计特性,同时又便于重复产生和处理,有预先的可确定性和可重复性。

由于它的这些优点,在通信、雷达、导航以及密码学等重要的技术领域中伪随机序列获得了广泛的应用。

而在近年来的发展中,它的应用范围远远超出了上述的领域,如计算机系统模拟、数字系统中的误码测试、声学和光学测量、数值式跟踪和测距系统等也都有着广阔的使用。

伪随机序列通常由反馈移位寄存器产生,又可分为线性反馈移位寄存器和非线性反馈移位寄存器两类。

由线性反馈移位寄存器产生出的周期最长的二进制数字序列称为最大长度线性反馈移位寄存器,即为通常说的m序列,因其理论成熟,实现简单,应用较为广泛。

伪随机序列的特点决定了它有着重要并且广泛的应用,这里仅举出一些有代表性的用途。

误码率测量。

在数字通信中误码率是一项重要的质量指标,在实际测量数字通信系统的误码率时,一般来说,测量结果与信源发出信号的统计特性有关。

通常认为二进制信号0和1是以等概率随机出现的。

所以测量误码率时最理想的信源应是伪随机序列产生器。

这样测量的结果,我们认为是符合实际运用时的情况。

时延测量。

有时我们需要测量信号经过某一传输路径所收到的时间延迟,例如,需要测量某一延迟线的时间延迟。

1绪论近年来,以FPG为代表的可编程ASIC器件发展极快,从最初的数百个门发展到现今的数百万个门,系列品种增多,功能更强,速度更快,功耗更小,价格更低。

因此,愈来愈受到电子界的青睐,开发基于FPGA勺数字集成系统设计的新技术方法将逐渐成为主流。

FPG技术发展出现几个新动向:一是在FPG中嵌人处理器(包括CPU微处理器、微控制器);二是高速并行I/O 口;三是实现数字信号处理功能。

针对以上动态,本课题通过对FPG技术的研究,对在FPG中实现伪随机序列发生器做了有益的研究与实践,设计中充分运用了自上而下、结构化、模块化设计思想。

伪随机序列具有良好的随机性,它的相关函数接近白噪声的相关函数(函数),即有窄的高峰或宽的功率谱密度,使它易于从其他信号或干扰中分离出来。

伪随机序列的伪随机性表现在:预先的可确定性、可重复性,使它易于实现相关接收和匹配接收,故有良好的抗干扰性能。

伪随机序列(又称伪噪声序列)广泛应用于通信、雷达、导航等重要的技术领域。

近年来,在自动控制、计算机、声学、光学测量、数字式跟踪和测距系统,以及数字网络系统的故障分析检测也得到广泛的应用。

1.1课题背景在现代工程实践中,伪随机信号在移动通信、导航、雷达和保密通信、通信系统性能的测量等领域中有着广泛的应用。

例如,在连续波雷达中可用作测距信号,在遥控系统中可用作遥控信号,在多址通信中可用作地址信号,在扩频通信系统中,抗干扰、抗噪声、抗截获、信息数据隐蔽和保密、抗衰落、多址通信、实现同步与捕获等都与扩频码的设计密切相关。

在数字通信中可用作群同步信号,还可用作噪声源以及在保密通信中的加密作用等。

伪随机发生器在测距、通信等领域的应用日益受到人们重视。

EDA(电子设计自动化)技术就是以计算机为工具,在EDA软件平台上,对以硬件描述语言VHDL为系统逻辑描述手段完成的设计文件,自动的完成逻辑编译、逻辑化简、逻辑综合及优化、逻辑仿真,直至对特定目标芯片的适配编译、逻辑映像和编程下载等工作(本文选用的开发工具为Altera公司的Quartus H)。

基于FPGA的多路伪随机序列发生器的设计与实现引言伪随机序列生成器(Pseudorandom Number Generator,PRNG)在许多计算机应用中都是必不可少的工具。

PRNG通过输入一个种子(seed),然后根据一定的算法生成一个看似随机的序列。

然而,由于PRNG本质上是基于算法的,所以生成的序列实际上是可重复的、周期性的。

本文将介绍基于FPGA的多路伪随机序列发生器的设计与实现。

设计目标本设计的目标是实现一个多路的伪随机序列发生器,该发生器具有高速性能和可扩展性。

设计需满足以下要求:1.高速性能:PRNG需要生成大量的伪随机序列,因此需要具备较高的计算速度;2.可扩展性:PRNG需要同时生成多个伪随机序列,因此需要具备可扩展性,方便根据需求扩展生成的路数;3.随机性:生成的伪随机序列需要具备较高的随机性,能够满足实际应用的需求。

设计思路本设计采用LFSR(Linear Feedback Shift Register)算法来实现PRNG。

LFSR算法是一种经典的PRNG实现方式,可以通过移位寄存器和异或门来实现。

LFSR算法的优势在于其计算速度快、硬件实现简单。

具体实现步骤如下:1.设计LFSR模块:LFSR模块是PRNG的核心模块,通过移位寄存器和异或门来实现。

LFSR模块接收一个种子作为输入,并根据一定的生成多路伪随机序列的算法生成对应的伪随机序列。

2.设计控制模块:控制模块用于控制LFSR模块的生成和输出。

控制模块根据输入的控制信号来决定生成的路数和序列长度,并将生成的伪随机序列进行输出。

3.设计顶层模块:顶层模块对上述模块进行组合,实现多路伪随机序列发生器。

顶层模块接收输入的控制信号和种子,并将控制信号传递给控制模块,种子传递给LFSR模块。

最后将生成的伪随机序列输出。

实现与验证本设计实现采用FPGA开发板进行验证。

首先,搭建基本的开发板环境,包括连接FPGA开发板、安装相应的开发软件等。

基于FPGA的伪随机序列调频系统摘要:本文根据线性反馈寄存器可产生伪随机序列的原理,基于FPGA硬件电路平台以Quartus II为开发平台采取了自顶向下的设计方法设计了伪随机序列调频系统,将产生的伪随机序列作为调频码反馈回输入端,通过DDS的方法实现调频,用来控制正弦波形的输出频率。

关键词:伪随机序列FPGA 调频在通信领域,如果一种序列可以预先确定的,即可以重复地生产和复制,同时统计特性方面又具有随机序列的随机特性,我们便称这种序列为伪随机序列。

伪随机序列现已广泛地应用于许多重要领域,如密码学、扩频通讯、导航、现代战争中的电子对抗技术等等。

伪随机序列的伪随机性主要是指其预先的确定性以及可重复产生与处理,其发生器通常是通过算法实现的,由于算法是已经确定的,产生器并不能产生真正的随机序列,生成的序列都具有或长或短的周期,但是当所产生序列的周期足够大时,便具有了随机序列的良好统计特性,看起来是随机的。

伪随机序列具有良好的相关特性,可以作为雷达测距、同步或是线性系统测量的信号。

因为具有伪随机性,因而它也可用于加密系统和伪随机调频等场合,还可用来产生伪随机数,用来在数字系统中作为误码测试信号等。

1基于FPGA实现伪随机序列在很多实际应用场合中,直接利用FPGA产生伪随机序列的方法可以为系统设计带来极大的便利。

本文给出了一种简洁而又高效的伪随机序列产生方法,结合FPGA特有的结构,采用线性反馈寄存器的原理实现伪随机序列的方法,选用了altera的cyclone III系列FPGA 芯片EP3C25作为硬件平台,该芯片内部有246 24个逻辑单元、608256bit的RAM和4个锁相环。

开发的源程序如下:module m_sequence (clk, out),parameter level=3,parameter[level-l:0]initial state=3&acute; blll,input clk,output [1:0] out,reg[level-l:0] register;integer i,initial register<=initial_state,always @(posedge clk)begin register[Ol<=register[level-2] -register [level-l],//for (i=0, i<level-l, i=i+l) register [i+l]<=register [i],endassign out [1] =register [0], assign out [0]二register [2],endmodule生成的伪随机序列的结果可以从示波器观测到。

FPGA产生基于LFSR的伪随机数1.概念通过一定的算法对事先选定的随机种子(seed)做一定的运算可以得到一组人工生成的周期序列,在这组序列中以相同的概率选取其中一个数字,该数字称作伪随机数,由于所选数字并不具有完全的随机性,但是从实用的角度而言,其随机程度已足够了。

这里的“伪”的含义是,由于该随机数是按照一定算法模拟产生的,其结果是确定的,是可见的,因此并不是真正的随机数。

伪随机数的选择是从随机种子开始的,所以为了保证每次得到的伪随机数都足够地“随机”,随机种子的选择就显得非常重要,如果随机种子一样,那么同一个随机数发生器产生的随机数也会一样。

2.由LFSR引出的产生方法产生伪随机数的方法最常见的是利用一种线性反馈移位寄存器(LFSR),它是由n个D触发器和若干个异或门组成的,如下图:其中,gn为反馈系数,取值只能为0或1,取为0时表明不存在该反馈之路,取为1时表明存在该反馈之路;n个D触发器最多可以提供2^n-1个状态(不包括全0的状态),为了保证这些状态没有重复,gn的选择必须满足一定的条件。

下面以n=3,g0=1,g1=1,g2=0,g3=1为例,说明LFSR的特性,具有该参数的LFSR 结构如下图:假设在开始时,D2D1D0=111(seed),那么,当时钟到来时,有:D2=D1_OUT=1;D1=D0_OUT^D2_OUT=0;D0=D2_OUT=1;即D2D1D0=101;同理,又一个时钟到来时,可得D2D1D0=001. ………………画出状态转移图如下:从图可以看出,正好有2^3-1=7个状态,不包括全0;如果您理解了上图,至少可以得到三条结论:1)初始状态是由SEED提供的;2)当反馈系数不同时,得到的状态转移图也不同;必须保证g n===1,否则哪来的反馈?3)D触发器的个数越多,产生的状态就越多,也就越“随机”;3.verilog实现基于以上原理,下面用verilog产生一个n=8,反馈系数为g0g1g2g3g4g5g6g7g8=101110001的伪随机数发生器,它共有2^8=255个状态,该LFSR的结构如下:verilog源代码如下:module RanGen(input rst_n, /*rst_n is necessary to prevet locking up*/input clk, /*clock signal*/input load, /*load seed to rand_num,active high */input [7:0] seed,output reg [7:0] rand_num /*random number output*/ );always@(posedge clk or negedge rst_n)beginif(!rst_n)rand_num <=8'b0;else if(load)rand_num <=seed; /*load the initial value when load is active*/ elsebeginrand_num[0] <= rand_num[7];rand_num[1] <= rand_num[0];rand_num[2] <= rand_num[1];rand_num[3] <= rand_num[2];rand_num[4] <= rand_num[3]^rand_num[7];rand_num[5] <= rand_num[4]^rand_num[7];rand_num[6] <= rand_num[5]^rand_num[7];rand_num[7] <= rand_num[6];endendendmodule以1111 1111为种子,load信号置位后,开始在255个状态中循环,可将输出值255、143、111……作为伪随机数。

摘要:通过分析各种伪随机序列生成方法,提出了一种基于M 序列的连续抽样方法,可以生成满足自适应光学系统SPGD 控制算法要求的多路、相互独立以及服从伯努利分布的伪随机序列。

该方法适合于用FPGA等超大规模集成电路实现,且具有占用硬件资源较少,实现方便等优点。

用FPGA 实现了用于61 单元自适应光学系统SPGD 控制算法的伪随机序列,并将此方法应用于基于SPGD 控制算法的自适应光学系统实验中,实验表明,该方法能够满足自适应光学系统SPGD 算法的需求,系统实现成功闭环。

1 引言

随机序列是一组满足特定统计学规律的数据,在信号理论分析中应用非常普遍。

由于精确的随机序列生成方法较为复杂,产生的随机序列不具有可重复性等特点,在很多应用场合使用伪随机序列。

伪随机序列在扩频通信、信息加密和系统测试等诸多领域中都有着广泛的应用。

在自适应光学SPGD 算法中,伪随机序列亦有相当重要的作用。

Vorontsov 等人在1997 年将SPGD 算法引入到自适应光学领域[2]。

国内在近几年开始了对 SPGD 算法在自适应光学系统应用的研究,并且在计算机上用软件编程实现了算法,进行了自适应光学的系统实验[3]。

自适应光学SPGD 控制算法的研究趋势是使用专用的信号处理硬件电路作为算法的实现平台,以获得更高的迭代速度和更好的收敛效果。

Cauwenberghs等人设计了专用的模拟超大规模集成电路实现SPGD 控制算法,并且在一些应用领域进行了实验[5]。

目前自适应光学系统的规模普遍达到几十上百单元。

针对多单元自适应光学系统SPGD 控制算法的特殊要求,本文提出了一种适合于用FPGA 硬件电路产生满足算法要求的多路伪随机序列的生成方法,完成了FPGA 电路的硬件实现,并将其用于实现61 单元自适应光学SPGD控制算法,同时进行自适应光学的闭环实验。

2 自适应光学 SPGD 控制算法对伪随机序列的要求

SPGD(the Stochastic Parallel Gradient Descent algorithm)算法通过对多路的控制参数加入随机并行的扰动,使用性能指标测量值的变化量与控制参数的变化量进行控制参数的梯度估计,以迭代方式在梯度下降方向上进行控制参数的搜索。

在自适应光学SPGD 算法中,控制参数为变形镜的控制电压,随机并行的扰动通过多路伪随机序列模拟。

SPGD 算法中随机并行扰动的特性,对伪随机序列也提出了相应的要求[5]:

(1) 路数多。

路数等于变形镜单元数(即变形镜上驱动单元的数目)。

例如在一个61 单元的自适应光学系统中,就需要产生61 路的伪随机序列。

(2) 伪随机序列两两相互独立。

相互独立可避免变形镜各驱动单元间的相互耦合。

(3) 伪随机序列符合伯努利分布,两个样本值出现的概率各为0.5。

3 硬件电路实现伪随机序列的传统方法

传统的生成伪随机序列的方法较多,如线性反馈移位寄存器法(LFSR,可产生M 序列),乘同余法,线性同余法,Gold 序列等[6],[7]。

M 序列是一种常用的随机序列,符合SPGD 算法中单路随机序列伯努利分布的要求。

但使用M 序列作为SPGD 算法中多路随机序列在实现上存在难点:算法要求多路伪随机序列,用多个不同的LFSR 结构去生成多路的伪随机序列,需要耗费大量的硬件资源,并且构造多路不同的LFSR 结构需耗费巨大的工作量。

Gold 序列优点在于只由两个M 序列构造,能够节省资源;并且改变两个M 序列模二和的相对位置即可构成多个Gold 序列,从而满足SPGD 算法中多路伪随机序列的要求。

但在实际工程中如何方便改变两个M 序列的相对位置以产生多路的Gold 序列亦有难度。

同时,Gold 序列亦存在非平衡性问题,不完符合伯努利分布。

国外最早使用模拟超大规模集成电路(Analog VLSI)做出SPGD 控制算法的Vorontsov 等人设计的随机数发生器,其本质也是LFSR 结构,使用了抽头的方法从而可以用一个 LFSR 结构同时产生19 路的伪随机序列[8],[1]。

这种方法的缺陷是如果伪随机序列的路数序列超过19 路后,则用这个电路结构产生的各路伪随机数之间不是完全相互独立的。

4 连续抽样生成多路伪随机序列的方法

通过以上对M 序列,Gold 序列的分析,结合M 序列易于硬件实现,Gold 序列可生成多路序列的优点,以及基于时间抽样的思想,设计了如图1 所示硬件结构的68 路伪随机Gold 序列发生器。

图中所示结构包括两个时钟,两个相同的线性反馈移位寄存器,N 进制计数器,以及N 路伪随机序列的存取单元。

两个时钟有特殊的关系,即时钟1 是时钟2 的N 分频。

N 进制计数器的输出作为N 路伪随机序列存取单元的存储地址。

存取单元及地址译码器可视为一个整体,在实现时使用深度为N,宽度为1bit 的双端口RAM 代替(一个端口存数据,另一个端口取数据)。

此外,图中的“+”表示模二和。

结构中的N 值,为本原抽样数,即使用N 对M 序列抽样后,可得到另一同周期的M 序列。

上述结构产生多路Gold 序列的原理如下:

⑤将这N个不同相位的M2 序列与M1 序列模二和,生成N 个不同的Gold 序列。

该方法需要选定两个可构成Gold 序列的理想M 序列对,之后将能够从一个M 序列抽样出另一M 序列的本原抽样数N 预先计算出来。

由于是预先计算,不需在硬件内实现,不占用硬件资源。

因此该方法占用的资源较少,同时结构化的设计也适合于用硬件描述语言进行设计。

5 实验及结果分析

为验证上述伪随机序列生成方法的可行性,在FPGA 内对上述结构进行了硬件设计,并搭建了基于SPGD 控制算法的自适应光学系统平台。

自适应光学系统实验平台的结构如下图3 所示,主要由激光器和扩束系统、倾斜镜TM、变形镜DM、CCD 相机、基于FPGA 的SPGD 算法控制处理器、数字到模拟转换器DAC和高压放大器HVA 等组成。

光源从激光器发出后经TM 和DM 反射至CCD 相机,相机将图像数据传输给FPGA 板进行算法迭代,再输出电压至数模转换,最后经高压放大后控制61 单元的变形镜DM(驱动器的排布见图(3)和倾斜镜TM,完成闭环控制。

连续抽样法结构的主要参数: LFSR1 和LFSR2 对应的本原多项式为:

本原抽样数N 为68。

该设计可

产生68路,

周期为1023 的Gold 序列。

该参数设计主要以实验为主,本原多项式1F (x)的选取原则是反馈少,实现简单。

本原抽样数要比61 稍大,保证能产生足够多的Gold 序列,如果过大亦会造成资源的浪费。

SPGD 算法包括伪随机序列发生器都在Xilinx公司的VII3000 FPGA 内实现。

通过ChipScope 在线逻辑分析仪记录68 路Gold 序列,经计算验证这68 路Gold 满足相互独立的要求。

针对Gold 序列的非平衡性问题,根据序列的周期性及对偶性,实验运用了一个简单的方法加以解决:将偶数周期的两个样本值互相交换,即应该输出1 时输出0,应该输出0 时输出1。

因此每两个周期内的两个样本值出现的概率各为0.5,只要序列发生的时间足够长,长期统计平均,其概率亦各为0.5。

因此通过实验验证表明连续抽样方法能够满足自适应光学SPGD 算法的要求。

自适应光学系统实验方面,以均值半径作为本实验中SPGD 算法的性能指标[4],向极小的方向进行梯度搜索,性能指标的收敛曲线如图4(a)所示。

在迭代1000 次后,曲线就已接近极小值。

图4(b)和7(c)是进行校正前后,CCD 相机中获取的远场光斑的光强分布图。

校正前的峰值为96,校正后的峰值为230,校正后的远场光斑接近艾里斑,结果说明使用 SPGD 算法对静态的波前畸变达到了良好的效果,同时也验证了本方法所产生的伪随机序列能够在实际的SPGD 控制算法中正常工作。

6 结论

利用FPGA硬件电路生成了61单元自适应光学系统SPGD控制算法要求的68路伪随机序列。

开展了基于SPGD控制算法自适应光学系统实验,系统能够实时闭环,结果表明了该方法的实用性。

同时,该方法除了满足自适应光学系统SPGD控制算法的专用性外,也为生成大量的、任意多路的伪随机序列提供了一种通用的方法,在信号处理、信号加密等工程领域也具有一定的实际意义。

本文作者创新点:针对自适应光学系统的SPGD 控制算法对伪随机序列的要求,分析了两种适合于硬件实现的伪随机序列――M 序列及Gold 序列的特点,及直接用于SPGD 控制算法存在的问题。

在M 序列抽样方法的基础上,提出了一种连续抽样生成多路Gold 序列的方法。

该方法在对时间未要求的基础上,以时间来换取空间资源,减少了空间资源的占用,只需要两个LFSR 结构,解决了生成大量LFSR 结构的工作量问题,方便地实现了SPGD 控制算法要求的多路、独立伪随机序列的生成,并提出了解决了Gold 序列非平衡性问题的方法。