排队取号服务系统的VHDL程序实现

- 格式:pdf

- 大小:367.77 KB

- 文档页数:4

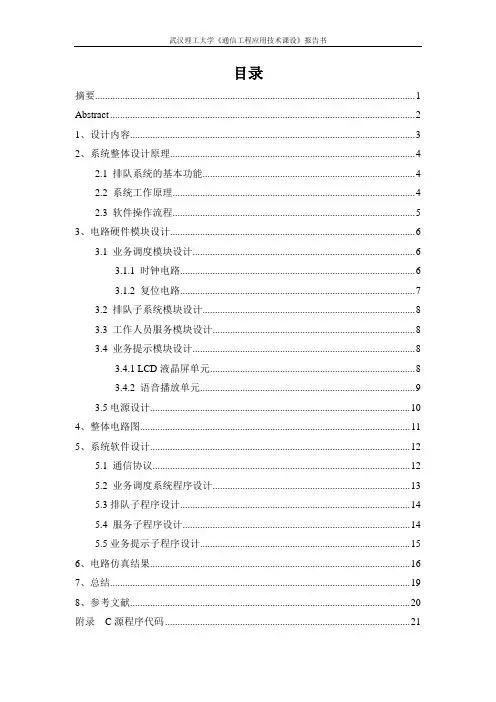

武汉理工大学《通信工程应用技术课设》报告书目录摘要 (1)Abstract (2)1、设计内容 (3)2、系统整体设计原理 (4)2.1 排队系统的基本功能 (4)2.2 系统工作原理 (4)2.3 软件操作流程 (5)3、电路硬件模块设计 (6)3.1 业务调度模块设计 (6)3.1.1 时钟电路 (6)3.1.2 复位电路 (7)3.2 排队子系统模块设计 (8)3.3 工作人员服务模块设计 (8)3.4 业务提示模块设计 (8)3.4.1 LCD液晶屏单元 (8)3.4.2 语音播放单元 (9)3.5电源设计 (10)4、整体电路图 (11)5、系统软件设计 (12)5.1 通信协议 (12)5.2 业务调度系统程序设计 (13)5.3排队子程序设计 (14)5.4 服务子程序设计 (14)5.5业务提示子程序设计 (15)6、电路仿真结果 (16)7、总结 (19)8、参考文献 (20)附录C源程序代码 (21)摘要目前,在以银行营业大厅为代表的窗口业务,大量客户的拥挤排队已成为了这些企事业单位改善服务品质、提升企业形象的主要障碍。

排队叫号系统的使用将成为改变这种情况的有力手段。

排队系统完全模拟了人群排队的全过程,通过取票进队。

排队等待、叫号服务等功能,很好的解决了客户在服务机构办理业务是所遇到的各种排队、拥挤和混乱现象,代替了人们站队的辛苦,把顾客等待的烦恼变成了一段难得的休闲时光,使客户拥有了一个自由的空间和一份美好的心情。

本次课程设计详细的介绍了设计的整过程,各个子系统的设计规则,而且还基于MATLAB做了简单的仿真。

关键字:窗口业务、排队等待、呼叫服务、设计、MATLABAbstractAt present, in the business hall of the bank as the representative of the window service, a large number of customers queuing has become the main obstacle to these enterprises to improve service quality, enhance corporate image. The use of queuing system will become a powerful means to change this situation. Queuing system is fully simulates the whole process of the crowd queuing, the ticket into the team. Queuing, queuing and service functions, is a very good solution to customers in the service business is encountered queuing, crowded and chaotic phenomena, instead of people line up hard, make customer waiting annoyance into a rare leisure time, so that customers have a free space and a good mood.Keywords: window service, waiting in line, call service, design, MATLAB1、设计内容由于嵌入式的电路板比较复杂,而次设计用单片机可以实现,所以相对来说用单片机设计比较简单,程序设计也比较方便。

排队叫号机的实现目录1.引言 (1)2.系统功能分析及设计要求 (2)3.系统框图 (4)4.主要应用器件及技术原理 (6)4.1 微处理器介绍 (6)4.1.1、MCS-51单片机的特点 (6)4.1 2、MCS-51 单片机的结构 (6)4.2液晶LCD1602的介绍 (7)4.2.1 字符型液晶显示器的显示原理 (7)4.2.2 液晶LCD1602的简介 (8)5.系统硬件电路设计 (11)5.1晶振电路 (12)5.2液晶显示电路 (13)5.3声音提示电路 (14)6.系统测试 (16)7.系统软件设计 (15)7.1系统软件流程图........................................................... 错误!未定义书签。

7.2系统程序设计............................................................... 错误!未定义书签。

7.2.1 主程序............................................................... 错误!未定义书签。

7.2.2 液晶LCD1602显示处理程序...................... 错误!未定义书签。

7.2.3 按键检测程序...........................................................................错误!未定义书签。

8.结束语 (19)9.致谢辞.................................................................................. 错误!未定义书签。

10.参考文献............................................................................ 错误!未定义书签。

单片机原理与应用技术课程设计设计题目:基于单片机银行排队叫号系统设计目录1 设计目的 (3)2 设计的任务与要求 (3)3 设计方案与论证 (3)3.2设计论证 (4)4 硬件电路设计 (5)4.1 单片机及外围电路 (5)4.2 显示电路 (6)4.3 按键电路 (8)4.4 蜂鸣器电路 (8)5 系统软件设计 (9)5.1 主程序设计 (9)5.2显示处理程序 (10)6 系统调试 (10)7 总结 (11)附录1:总体电路原理图 (14)附录2:元器件清单 (15)附录4:源程序 (17)附录4:源程序 ......................................................... 错误!未定义书签。

1设计目的近年来,随着科学技术的迅猛发展和人们生活水平的日益提高,各行各业特别是服务行业的竞争也逐渐激烈。

服务质量作为体现企业的公众形象、服务理念、管理水平的标准已越来越受到服务和被服务双方所关注,而营业窗口正是代表银行、医院、电信、税务、工商等企业服务质量的重要场所。

随着服务行业业务量的增长及业务种类的增加,排队等候已成为人们面临的实际问题。

长期以来,人们在银行、医院、电信、税务、工商等营业大厅里前拥后挤、杂乱无章地排队等候,有时一站就是一个多小时,这已是司空见惯的现象,极大地影响了服务质量。

员工坐着服务、客户站着等待的服务方式与“用户就是上帝”的服务宗旨完全背道而驰!改善服务质量、树立良好形象,解决劳累的排队现象、创造人性化服务环境已成为急需解决的问题。

设计一套排队抽号的服务系统,可以很好的解决因排队引起的种种问题,排队系统应运而生此系统完全模拟人群排队过程,通过取票进队、排队等待、叫号服务等功能,诠释了人性化的服务理念,舒缓顾客等待的急噪情绪,使人们在等候服务的过程中拥有一个相对自由的空间,是科技以人为本的真正体现。

本文基于单片机的排队叫号系统,由客户端和主机终端组成,有LCD大屏幕显示信息,让客户知道自己的队号,并有叫号提示音提醒客户,方便快捷,可以满足日常的服务行业排队叫号,所以非常有意义。

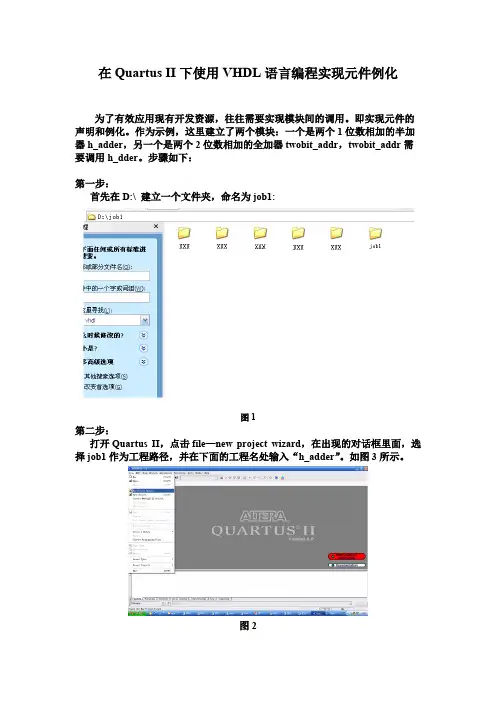

在Quartus II下使用VHDL语言编程实现元件例化为了有效应用现有开发资源,往往需要实现模块间的调用。

即实现元件的声明和例化。

作为示例,这里建立了两个模块:一个是两个1位数相加的半加器h_adder,另一个是两个2位数相加的全加器twobit_addr,twobit_addr需要调用h_dder。

步骤如下:第一步:首先在D:\ 建立一个文件夹,命名为job1:图1第二步:打开Quartus II,点击file—new project wizard,在出现的对话框里面,选择job1作为工程路径,并在下面的工程名处输入“h_adder”。

如图3所示。

图2图3第三步:点击file—new,在出现的对话框里面选择VHDL文件,如图4所示。

界面上将会出现一个空白的.vhd的文件,点击“保存按钮”,将该文件的文件名取为“h_adder”(必须与工程名一致)。

图4第四步:在h-adder.vhd文档中,键入如下程序(可复制粘贴):library ieee;use ieee.std_logic_1164.all;entity h_adder isport(X: in std_logic ;Y: in std_logic ;C_in: in std_logic;Sum : out std_logic ;C_out : out std_logic ) ;end h_adder ;-- The architecture body :architecture behav of h_dder isbeginprocess(X,Y,C_in)beginSum <= (X xor Y) xor C_in;C_out <= (X and Y)or (C_in and X) or (C_in and Y);end process;end Behav;上述程序主要是实现X与Y的相加,同时包括进位输入C_in、进位输出C_out、相加的和Sum。

地铁自动售票机一、设计要求1、功能描述用于模仿地铁售票自动售票,完成地铁售票的核心控制功能。

2、功能要求售票机有两个进币孔,一个是输入硬币,识别的范围是一元硬币;一个是纸币,识别的范围是一元、两元、五元、十元、二十元。

乘客可以连续多次投入钱币。

乘客一次只能选择一个出站口,购买车票时,乘客先选出站口,有六个出站口可供选择,再选择所需的票数,然后投币,投入的钱币达到或者超过所需金额时,售票机自动出票,并找零。

本次交易结束后,等待下一次交易。

在选择出站口、所需票数以及在投币期间,乘客可以按取消键取消操作,钱币自动退出。

二、实验分析1、买票时,乘客按下开始键,售票机进入站台选择程序,乘客选择出站口后,可以按取消键重新选择,否则售票机自动进入票数选择程序,同样这时可以按下取消键重新开始选择出站口以及票数。

2、当选择好出站口以及所需票数时,乘客可以投硬币或者用纸币,当所投的钱币总额大于或者等于票价时,售票机自动出票以及找零。

期间,可以按下取消键重新开始选择,并退出所有的钱币。

3、乘客若还没选择出站口或者票数,就投币或者使用纸币,售票机会自动退出所有的钱币。

4、有六个站台可供乘客选择,每个乘客最多可以买3张票,六个站台编号为1到6,票价从2元依次递增到7。

三、系统流程图四、程序源代码LIBRARY IEEE;USE IEEE.std_logic_1164.ALL;USE IEEE.std_logic_arith.ALL;USE IEEE.std_logic_unsigned.ALL;ENTITY metrosell ISPORT(clk:in std_logic; --set the clock signalstartselect:in std_logic; --start to select the platformsure:in std_logic; --this button is to save your forward step(s)coin1y:in std_logic; --1 yuan coinpmoney1y:in std_logic; --1 yuan paper moneypmoney2y:in std_logic; --2 yuan paper moneypmoney5y:in std_logic; --5 yuan paper moneypmoney10y:in std_logic; --10 yuan paper moneypmoney20y:in std_logic; --20 yuan paper moneycancel:in std_logic; --cancel the forward step(s)number:in std_logic_vector(3 downto 0); --choose the number of the ticketsplatform:in std_logic_vector(3 downto 0); --choose the platform you want to reachmoneystorage:out std_logic; --to store the moneyacceptmo:out std_logic; --accept the moneystamp:out std_logic; --stamp outgatecharge:out std_logic_vector(3 downto 0); --the mount of charge,up to 15 yuanchargegate:out std_logic --charge outgate);END metrosell;ARCHITECTURE sell OF metrosell IStype state_type is(initial_type,selectp_type,selectnum_type,insert_type,stamp_type,charge_type);--define six typessignal state:state_type; --define a shared state BEGINmain:process(clk,state,startselect,platform,number,coin1y,pmoney1y,pmoney2y,pmon ey5y,pmoney10y,pmoney20y,cancel,sure)variable univalence :integer range 0 to 7; --the univalence of the ticket variable total_money :integer range 0 to 21; --the price of the ticket(s)variable selectp_alr:std_logic; --the flag of select platform typevariable selectnum_alr:std_logic; --the flag of select number typevariable stamp_alr:std_logic; --the flag of the stamp gate variable charge_alr:std_logic; --the flag of the charge gatevariable money_reg:integer range 0 to 21; --the mount of money put in variable coin1y_f:std_logic; --the flag of one yuan coin variable pmoney1y_f:std_logic; --the flag of one yuan paper moneyvariable pmoney2y_f:std_logic; --the flag of two yuan paper moneyvariable pmoney10y_f:std_logic; --the flag of ten yuan paper moneyvariable pmoney20y_f:std_logic; --the flag of twelve yuan paper moneyvariable pmoney5y_f:std_logic; --the flag of five yuan paper moneyvariable charge_reg:integer range 0 to 15; --the register of chargebeginif(rising_edge(clk)) thencase state iswhen initial_type => --initialize some variablesunivalence:=0;selectp_alr:='0';selectnum_alr:='0';stamp_alr:='0';charge_alr:='0';money_reg:=0;total_money:=0;coin1y_f:='0';pmoney1y_f:='0';pmoney2y_f:='0';pmoney5y_f:='0';pmoney10y_f:='0';pmoney20y_f:='0';moneystorage<='0';stamp<='0';charge_reg:=0;charge<="0000";acceptmo<='0';chargegate<='0';if (startselect='1') thenstate<=selectp_type;end if;when selectp_type =>if(selectp_alr='0'and cancel='0') then --choose the platform if(platform="0001")then univalence:=2;selectp_alr:='1';elsif(platform="0010")then univalence:=3;selectp_alr:='1';elsif(platform="0011")then univalence:=4;selectp_alr:='1';elsif(platform="0100")then univalence:=5;selectp_alr:='1';elsif(platform="0101")then univalence:=6;selectp_alr:='1';elsif(platform="0110")then univalence:=7;selectp_alr:='1';elsif(platform="0000")then univalence:=0;selectp_alr:='0';else null;end if;elsif(selectp_alr='1'and cancel='1')then state<=initial_type;elsif(selectp_alr='1'and sure='1') then state<=selectnum_type;end if;when selectnum_type => --you can buy at most 3 ticketsif(selectnum_alr='0'and cancel='0')then--choose the number of ticketsif(number="0001")thenif(univalence=2)thentotal_money:=2;selectnum_alr:='1';elsif(univalence=3)thentotal_money:=3;selectnum_alr:='1';elsif(univalence=4)thentotal_money:=4;selectnum_alr:='1';elsif(univalence=5)thentotal_money:=5;selectnum_alr:='1';elsif(univalence=6)thentotal_money:=6;selectnum_alr:='1';elsif(univalence=7)thentotal_money:=7;selectnum_alr:='1';elsif(univalence=0)thentotal_money:=0;selectnum_alr:='0';else null;end if;end if;if(number="0010")thenif(univalence=2)thentotal_money:=4;selectnum_alr:='1';elsif(univalence=3)thentotal_money:=6;selectnum_alr:='1';elsif(univalence=4)then total_money:=8;selectnum_alr:='1';elsif(univalence=5)then total_money:=10;selectnum_alr:='1';elsif(univalence=6)then total_money:=12;selectnum_alr:='1';elsif(univalence=7)then total_money:=14;selectnum_alr:='1';elsif(univalence=0)then total_money:=0;selectnum_alr:='0';else null;end if;end if;if(number="0011")thenif(univalence=2)then total_money:=6;selectnum_alr:='1';elsif(univalence=3)then total_money:=9;selectnum_alr:='1';elsif(univalence=4)then total_money:=12;selectnum_alr:='1';elsif(univalence=5)then total_money:=15;selectnum_alr:='1';elsif(univalence=6)then total_money:=18;selectnum_alr:='1';elsif(univalence=7)then total_money:=21;selectnum_alr:='1';elsif(univalence=0)then total_money:=0;selectnum_alr:='0';else null;end if;end if;elsif(selectnum_alr='1'and cancel='1')then state<=initial_type;elsif(selectnum_alr='1'and sure='1') then state<=insert_type;end if;when insert_type =>moneystorage<='1';if(money_reg<total_money and cancel='0')then--receive the inserted moneyif(coin1y='1'andcoin1y_f='0')then money_reg:=money_reg+1;coin1y_f:='1';end if;if(coin1y='0'and coin1y_f='1')then coin1y_f:='0';end if;if(pmoney1y='1'and pmoney1y_f='0')thenmoney_reg:=money_reg+1;pmoney1y_f:='1';end if;if(pmoney1y='0'and pmoney1y_f='1')thenpmoney1y_f:='0';end if;if(pmoney2y='1'and pmoney2y_f='0')thenmoney_reg:=money_reg+2;pmoney2y_f:='1';end if;if(pmoney2y='0'and pmoney2y_f='1')thenpmoney2y_f:='0';end if;if(pmoney5y='1'and pmoney5y_f='0')thenmoney_reg:=money_reg+5;pmoney5y_f:='1';end if;if(pmoney5y='0'and pmoney5y_f='1')thenpmoney5y_f:='0';end if;if(pmoney10y='1'and pmoney10y_f='0')thenmoney_reg:=money_reg+10;pmoney10y_f:='1';end if;if(pmoney10y='0'and pmoney10y_f='1')then pmoney10y_f:='0';end if;if(pmoney20y='1'and pmoney20y_f='0')then money_reg:=money_reg+20;pmoney20y_f:='1';end if;if(pmoney20y='0'and pmoney20y_f='1')then pmoney20y_f:='0';end if;elsif(money_reg<total_money and cancel='1')thenstate<=initial_type;elsif(money_reg>=total_money) then state<=stamp_type;end if;when stamp_type => --put out the stampif(stamp_alr='0')thenacceptmo<='1';stamp<='1';stamp_alr:='1';else state<=charge_type;end if;when charge_type => --put out the chargecharge_reg:=money_reg - total_money;case charge_reg iswhen 0 => charge<="0000";when 1 => charge<="0001";when 2 => charge<="0010";when 3 => charge<="0011";when 4 => charge<="0100";when 5 => charge<="0101";when 6 => charge<="0110";when 7 => charge<="0111";when 8 => charge<="1000";when 9 => charge<="1001";when 10 => charge<="1010";when 11 => charge<="1011";when 12 => charge<="1100";when 13 => charge<="1101";when 14 => charge<="1110";when 15 => charge<="1111";when others => charge<="0000";end case;if(charge_reg>0 and charge_alr='0') thenchargegate<='1';charge_alr:='1';elsif(charge_reg=0 and charge_alr='0')thenchargegate<='0';charge_alr:='1';else state<=initial_type;end if;end case;end if;end process main;END sell;五、波形仿真1、乘客按下开始按钮,进入选站台模式,选择二号站台,按下确定键,再选择票数为2张,按下确定键,售票机钱箱关闭,投入一张两元和五元纸币(对顺序没有要求),此时钱币总额大于票价,出两张票并找零一元。

vhdl编程实例VHDL编程实例- 设计与实现一个4位的全加器在本篇文章中,我们将一步一步地回答如何设计和实现一个4位的全加器。

VHDL编程语言将是我们用于描述和模拟这个电路的工具。

第一步:理解全加器的原理在编写代码之前,我们首先需要理解全加器的原理。

全加器是一种用于对两个二进制数字进行相加的电路。

它接收三个输入信号:两个位的输入(A 和B)以及一个进位输入(C_in)。

全加器的输出结果为一个位的和(S)和一个进位输出(C_out)。

我们可以使用如下的真值表来描述全加器的输出结果:输入信号输出结果A B C_in S C_out0 0 0 0 00 0 1 1 00 1 0 1 00 1 1 0 11 0 0 1 01 0 1 0 11 1 0 0 11 1 1 1 1了解了全加器的工作原理后,我们可以开始编写代码了。

第二步:编写全加器的VHDL代码我们将使用VHDL语言来描述和模拟全加器。

下面是一个简单的4位全加器的VHDL代码实现:vhdlEntity声明entity full_adder isport (A, B : in std_logic_vector(3 downto 0);C_in : in std_logic;S : out std_logic_vector(3 downto 0);C_out : out std_logic);end full_adder;Architecture声明architecture Behavioral of full_adder isbeginprocess(A, B, C_in)variable carry : std_logic;begincarry := C_in;for i in 0 to 3 loopS(i) <= A(i) xor B(i) xor carry;carry := (A(i) and B(i)) or (carry and (A(i) xor B(i)));end loop;C_out <= carry;end process;end Behavioral;在此代码中,我们首先声明了一个实体(entity)和一个架构(architecture)。

基于STM32的嵌入式银行排队系统智能叫号终端设计摘要:本文基于STM32嵌入式系统设计了一款智能叫号终端,该终端可以连接银行排队系统,自动调度顾客,实现优化银行服务的目的。

设计中采用了多种传感器感知顾客状态、LCD显示屏呈现顾客信息、蜂鸣器提示顾客等硬件,结合STM32芯片的高性能和低功耗,实现了高效、稳定的智能叫号功能。

该终端可以广泛应用于银行等有排队需求的场所,提高银行服务质量,优化客户体验。

关键词:STM32、嵌入式系统、智能叫号、银行排队系统、优化服务正文:一、绪论在银行等场所中,排队是常见的现象。

面对人多,服务慢的情况,人们常常感到烦躁,而优化服务,则是银行等企业的共同目标之一。

为此,我们设计了一款智能叫号终端,通过连接银行排队系统,并利用多种感知器实现自动、高效的叫号功能,提高服务效率、优化客户体验。

二、设计方案1.硬件设计:智能叫号终端主板采用STM32F103芯片,该芯片具有较高的性能和低功耗,适用于嵌入式系统应用。

为了感知顾客的队列情况,我们利用了多款传感器,包括红外传感器、超声波传感器等,通过对应的信号线连接至主板。

我们还在主板上设置了LCD显示屏,用以展现顾客的叫号信息,并在终端上加装了蜂鸣器,用于提示正在排队的顾客。

2.软件设计:智能叫号终端的软件设计分为两部分:嵌入式系统程序设计和PC机端程序设计。

(1)嵌入式系统程序设计:嵌入式系统程序可以实现接收银行排队系统的信息,解码数据,进行感知器状态检测,进而计算当前队列状态,自动发送叫号指令等功能。

(2)PC机端程序设计:PC机端程序是终端的图形化管理界面,主要用于设置叫号规则、任务下发等管理工作,方便银行工作人员进行管理和维护工作。

三、实验及结果在实验中,我们将终端连接银行排队系统,并进行了多次叫号实验。

实验结果表明,该终端具有较高的叫号效率和较低的误叫率,并且其LCD显示屏等硬件设计,可以方便顾客查询和排队。

四、结论基于STM32嵌入式系统的智能叫号终端,实现了银行排队系统的自动调度、顾客叫号等智能功能,并在实验中得到了验证。

《排队取号模拟系统》作业设计方案(第一课时)一、作业目标本作业旨在帮助学生掌握使用编程语言设计和实现排队取号模拟系统的基本技能,提高他们的编程能力和问题解决能力。

二、作业内容1. 任务一:设计排队取号模拟系统的基本框架要求:学生使用编程语言(如Python)设计一个简单的排队取号模拟系统,包括用户登录、排队、取号、等待和结束等基本功能。

2. 任务二:实现排队规则和取号方式要求:学生根据实际情况,设计并实现合理的排队规则(如先到先得、随机分配等)和取号方式,确保模拟系统的公平性和准确性。

3. 任务三:添加用户交互和数据统计功能要求:学生添加用户界面,使系统能够接收用户输入,并实现数据统计和结果展示功能,方便用户查看排队情况和取号结果。

4. 任务四:优化和调试系统要求:学生不断优化和调试系统,确保程序的稳定性和准确性,并解决可能出现的问题和错误。

三、作业要求1. 独立完成:学生需独立完成上述任务,不得抄袭或借助他人完成作业。

2. 实践操作:学生需使用编程语言实现上述任务,并在实践中提高自己的编程能力。

3. 报告提交:学生需将完成的作品和报告以电子版形式提交,报告需包括设计思路、实现过程、遇到的问题及解决方案等。

四、作业评价1. 评价标准:根据学生提交的作品和报告,评价学生的设计思路、实现过程、问题解决能力和创新性。

2. 评价方式:采取教师评价和学生互评相结合的方式,确保评价的公正性和准确性。

3. 优秀作品:对优秀作品给予表彰和鼓励,以激励学生继续提高自己的信息技术水平和能力。

五、作业反馈1. 学生自评:学生需对自己的作业进行自我评价,总结自己在实现过程中的优点和不足,为以后的作业和学习提供参考。

2. 同学互评:同学之间可以互相评价彼此的作品,交流经验和心得,共同提高信息技术水平。

3. 教师反馈:教师根据学生的完成情况和提交的作品,给予反馈和指导,帮助学生更好地完成后续的作业和学习任务。

通过本次作业,学生可以进一步掌握使用编程语言设计和实现排队取号模拟系统的技能,提高自己的问题解决能力和编程能力。

《排队取号模拟系统》作业设计方案(第一课时)一、作业目标本次作业旨在帮助学生理解和掌握排队取号模拟系统的基本原理和技术,培养他们利用编程语言实现模拟系统的能力,并加深对信息技术在现实生活中的应用的理解。

二、作业内容1. 任务一:设计排队取号模拟系统的流程图学生需根据模拟系统的基本功能,绘制出系统的流程图。

要求详细描述各个步骤和逻辑关系,以便后续编程实现。

2. 任务二:编程实现排队取号模拟系统学生需使用适当的信息技术工具(如Python、Java等)编写程序,实现排队取号的模拟系统。

要求能够模拟排队、取号、分配任务等基本功能,并能够进行测试和调试。

3. 任务三:优化和完善模拟系统学生需根据实际情况和需求,对模拟系统进行优化和完善,提高系统的稳定性和效率。

三、作业要求1. 独立完成:学生需独立完成上述任务,不得抄袭或依赖他人。

2. 规范提交:学生需按照要求提交作业,包括但不限于流程图、代码和测试报告等。

3. 质量要求:要求程序代码规范、逻辑清晰、运行稳定,能够达到预期效果。

四、作业评价1. 评价标准:根据学生提交的作业质量、创新性和实用性等方面进行评价。

2. 评价方式:采取教师评价和学生互评相结合的方式,确保评价的公正性和客观性。

3. 评价结果:作业评价结果将作为学生平时成绩的参考之一,激励学生在信息技术课程中积极参与、勇于实践。

五、作业反馈1. 学生自评:学生需对自己的作业进行自我评价,总结优点和不足,以便在后续的学习中不断改进。

2. 教师反馈:教师将对学生在作业中存在的问题进行反馈,并提供指导和建议,帮助学生更好地理解和掌握相关知识。

3. 同学交流:学生之间可相互交流学习,分享经验和技巧,共同提高编程能力和信息技术应用水平。

通过本次作业,学生将能够加深对排队取号模拟系统的理解和掌握,提高编程能力和信息技术应用水平,为今后的学习和工作奠定坚实的基础。

作业设计方案(第二课时)一、作业目标本作业旨在巩固和提升学生对排队取号模拟系统的理解和应用能力,进一步掌握编程语言和相关软件工具,并培养其团队协作和问题解决能力。

单片机系统课程设计成绩评定表设计课题排队叫号系统设计学院名称:电气工程学院专业班级:学生姓名:学号:指导教师:设计地点 :设计时间:指导教师意见:成绩:签名:年月日单片机系统课程设计课程设计名称: 排队叫号系统设计专业班级:学生姓名:学号:指导教师:课程设计地点:课程设计时间:单片机系统课程设计任务书学生姓名专业班级学号题目课题性质工程设计课题来源选题指导教师主要内容(参数)利用排队叫号系统,实现以下功能:1、取票:顾客取一张号票吗,上面有号码、等候人数、时间等2、休息等待:持号票在休息区休息并留意显示屏音箱叫号3、按键叫号:工作人员办完一笔业务后按下叫号器上的下一位按钮4、前去办理:叫号时根据显示屏音箱的信息到指定位置享受一对一的服务。

任务要求(进度)第1-2天:熟悉课程设计任务及要求,查阅技术资料,确定设计方案.第3—4天:按照确定的方案设计单元电路。

要求画出单元电路图,元件及元件参数选择要有依据,各单元电路的设计要有详细论述.第5-6天:软件设计,编写程序。

第7—8天:实验室调试.第9—10天:撰写课程设计报告。

要求内容完整、图表清晰、文理流畅、格式规范、方案合理、设计正确,篇幅不少于6000字。

主要参考资料[1]康万新.毕业设计指导及案例剖析—应用电子技术方向[M].北京:清华大学出版社,2007.[2]杨连国。

医院智能排队叫号系统的设计与实现[D]。

南京:东南大学,2006.[3] 胡汉才.单片机原理及其接口技术[M]。

北京:清华大学出版社,2004。

审查意见系(教研室)主任签字: 年月日目录摘要.。

.。

..。

..。

.。

..。

.。

.。

.。

.。

..。

.。

....。

..。

.。

11、绪论.....。

.。

.。

..。

...。

.。

...。

.。

.。

..。

.。

.。

...。

..。

.。

21.1课题背景.。

.。

..。

..。

..。

.。

.。

.。

.。

.。

.。

.。

.。

.。

..。

21.2课题的研究内容与目标.。

..。

目录第一部分实验思路 (2)第二部分问题和解决方案 (3)第三部分技术的认识 (3)第四部分课程的建议 (4)第五部分程序源代码 (4)--实验二(8位可逆计数器) (4)--实验三(任意整数分频电路设计) (6)--实验四(多功能循环彩灯控制电路设计) (7)--实验五(8段数码管动态扫描显示控制) (9)--实验六(频率计设计) (13)--实验七(矩阵式键盘扫描与键码检测) (17)--实验八(LPM的使用) (20)--实验九(多功能电子钟设计) (20)--实验十(SPI总线时序模拟) (29)第一部分实验思路1.1实验二(8位可逆计数器)分两个进程,一个记录手动脉冲个数,另一个记录脉冲源脉冲个数,最后以方式选择开关决定显示哪个个数。

1.2实验三(任意整数分频电路设计)分两个进程,一个记录上升沿个数,另一个纪录下降沿个数,当计数总和等于预分频数时,两个进程的标识位取反,最后将两个标识位的异或送给输出。

1.3实验四(多功能循环彩灯控制电路设计)确定四种循环方式,分别为1、3、5、7,2、4、6、8,7、5、3、1,8、6、4、2。

用case,when语句,同时计数自动加一。

1.4实验五(8段数码管动态扫描显示控制)设置一个顶层文件,三个模块文件(分频模块,计数模块,显示模块)。

分频是将20Mhz分成周期为1/100s和100us的方波。

计数是记录有多少个1/100s。

显示是以100us为步调扫描数码管以显示计数。

1.5实验六(频率计设计)设置一个顶层文件,三个模块文件(分频模块,计数模块,显示模块)。

分频是将20Mhz分成周期为1s和1ms的方波。

计数是记录在1s内待测脉冲的周期数。

显示是以1ms为步调扫描数码管以显示计数。

1.6实验七(矩阵式键盘扫描与键码检测)设立四个进程,一个完成由20Mhz到周期为10ms,100us的转换(10ms用于扫描键盘,100us 用于扫描数码管以显示键码)。

排队电路VHDL程序设计library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity paidui isport(rst,clk:in std_logic;selout:out std_logic_vector(2 downto 0);Jin,chu:in bit;selbit:out std_logic_vector(7 downto 0);lednum:out std_logic_vector(6 downto 0));end paidui;architecture behav of paidui isSignal xinlai0,xinlai1,xinlai2,xinlai3:std_logic_vector(3 downto 0);signal dengdai0,dengdai1,dengdai2,dengdai3:std_logic_vector(3 downto 0);signal dandqian0,dandqian1,dandqian2,dandqian3:std_logic_vector(3 downto 0);signal duichang0,duichang1,duichang2,duichang3:std_logic_vector(3 downto 0);signal tm:std_logic_vector(3 downto 0);signal cnt4:integer range 0 to 10 ;signal sel:std_logic_vector(2 downto 0);signal cnt10:std_logic_vector(1 downto 0);signal tmpclk:std_logic;beginp1:process(clk,rst)beginif rst='0' thenxinlai0<="0000";xinlai1<="0000";xinlai2<="0000";xinlai3<="0000";dengdai0<="0000";dengdai1<="0000";dengdai2<="0000";dengdai3<="0000";elsif clk'event and clk='1' thenxinlai0<=xinlai0+1;if xinlai0<"1001" thenxinlai0<=xinlai0+1;elsif xinlai1<"1001" thenxinlai1<=xinlai1+1; xinlai0<="0000";elsif xinlai2<"1001" thenxinlai2<=xinlai2+1; xinlai1<="0000";elsif xinlai3<"1001" thenxinlai3<=xinlai3+1; xinlai2<="0000";Elsif (xinlai0<="1001"and xinlai1<="1001" and xinlai2<="1001"and xinlai3<="1001" )thendengdai0<=dengdai0+1;If dengdai0<"1001" thendengdai0<=dengdai0+1;xinlai0<="0000";xinlai1<="0000";xinlai2<="0000";xinlai3<="0000";elsif dengdai1<"1001" thendengdai1<=dengdai1+1;dengdai0<="0000";elsif dengdai2<"1001" thendengdai2<=dengdai2+1;dengdai1<="0000";elsif dengdai3<"1001" thendengdai3<=dengdai3+1;dengdai2<="0000";elsif(dengdai0<="1001"and dengdai1<="1001"and dengdai2<="1001"and dengdai3<="1001")thenxinlai0<="0000";xinlai1<="0000";xinlai2<="0000";xinlai3<="0000";dengdai0<="0000";dengdai1<="0000";dengdai2<="0000";dengdai3<="0000";end if;end if;end if;end process p1;p2:process(rst,clk,jin)beginif rst='0' then dandqian0<="0000";dandqian1<="0000";dandqian2<="0000";dandqian3<="0000";Elsif clk'event and clk='1' thenif jin<='0' thendandqian0<="0000";dandqian1<="0000";dandqian2<="0000";dandqian3<="0000";elsif jin<='1' then ---——柜台可以为客人服务;if dandqian0<"1001" thendandqian0<=dandqian0+1;elsif dandqian1<"1001" thendandqian1<=dandqian1+1;dandqian0<="0000";elsif dandqian2<"1001" thendandqian2<=dandqian2+1;dandqian1<="0000";elsif dandqian3<"1001" then ---——顾客的编号都小于9999,开始加1;dandqian3<=dandqian3+1;dandqian2<="0000";elsif (dandqian0<="1001" and dandqian1<="1001"and dandqian2<="1001" and dandqian3<="1001")thendandqian0<="0000";dandqian1<="0000";dandqian2<="0000";dandqian3<="0000";end if;---——当前顾客的编号都大于9999;全都至为0000;end if;end if;end process p2;p3:process(rst,tmpclk)beginif rst='0' then cnt4<=0; -- ——当复位rst=0时,cnt4=0;elsif tmpclk'event and tmpclk='1' then -- ——时钟上升沿;if cnt4<8 thencnt4<=cnt4+1; --——cnt4<8,cnt4的值为cnt4加1,一直加到7;Else cnt4<=0;end if;end if;end process p3;free_counter:blocksignal q:std_logic_vector(24 downto 0);beginp4:process(clk,rst)beginif rst='0' then q<=(OTHERS=>'0');elsif clk'event and clk='1' then q<=q+1;end if;end process p4;selout<=sel;sel<="000" when cnt4=0 else --——倒数第一个数码管cnt4=0;"001" when cnt4=1 else --——倒数第二个数码管cnt4=1;"010" when cnt4=2 else --——倒数第三个数码管cnt4=2;"011" when cnt4=3 else --——倒数第四个数码管cnt4=3;"100" when cnt4=4 else --——第四个数码管cnt4=4;"101" when cnt4=5 else --——第三个数码管cnt4=5;"110" when cnt4=6 else --——第二个数码管cnt4=6"111" when cnt4=7 else --——第一个数码管cnt4=7;"000";end block free_counter;P5:process(rst,clk)beginif rst='0' then cnt10<="00";elsif clk'event and clk='1' thenif cnt10<3 then cnt10<=cnt10+1;else cnt10<="00";end if;end if;end process p5;tmpclk<=cnt10(1);P6:process(rst,clk,chu)beginif rst='0' then -- ——复位为零,其他均设为零;duichang0<="0000";duichang1<="0000";duichang2<="0000";duichang2<="0000";elsif clk'event and clk='1' then --——上升沿到时,队长开始计算;if chu<='0' then duichang0<="0000";duichang1<="0000";duichang2<="0000";duichang2<="0000";elsif chu<='1' then --——柜台已经服务完上一任顾客,有空位时,四-- 位分别相减;duichang0<=xinlai0-dandqian0;duichang1<=xinlai1-dandqian1;duichang2<=xinlai2-dandqian2;Duichang3<=xinlai3-dandqian3;end if;end if;end process p6;P7:process(tmpclk,cnt4)beginif tmpclk'event and tmpclk='1' and cnt4<8 thencase cnt4 iswhen 0=> selbit <="11111110";tm<=dandqian0;when 1=> selbit <="11111101";tm<=dandqian1;when 2=> selbit <="11111011";tm<=dandqian2;when 3=> selbit <="11110111";tm<=dandqian3;when 4=> selbit <="11101111";tm<=duichang0;when 5=> selbit <="11011111";tm<=duichang1;when 6=> selbit <="10111111";tm<=duichang2;when 7=> selbit <="01111111";tm<=duichang3;when others=>selbit<="11111111";end case; -- ——给每个数码管赋值见图四;end if;end process p7;P8:process(tm)begincase tm iswhen "0000"=>lednum<="0111111"; -- ——段选位显示“0”的字样;when "0001"=>lednum<="0000110"; --——段选位显示“1”的字样;when "0010"=>lednum<="1011011"; --——段选位显示“2”的字样;when "0011"=>lednum<="1001111"; --——段选位显示“3”的字样;when "0100"=>lednum<="1100110"; --——段选位显示“4”的字样;when "0101"=>lednum<="1101101"; --——段选位显示“5”的字样;when "0110"=>lednum<="1111101"; --——段选位显示“6”的字样;when "0111"=>lednum<="0000111"; --——段选位显示“7”的字样;when "1000"=>lednum<="1111111"; --——段选位显示“8”的字样;when "1001"=>lednum<="1100111"; --——段选位显示“9”的字样;when others=>lednum<="0000000"; --——段选位无任何输出;end case;end process p8;end;。

武汉理工大学《通信工程应用技术课设》报告书(通信企业管理)通信工程技术用FPGA实现银行叫号系统目录摘要1Abstract21、设计内容32、系统整体设计原理42.1 排队系统的基本功能42.2 系统工作原理42.3 软件操作流程53、电路硬件模块设计63.1 业务调度模块设计63.1.1 时钟电路63.1.2 复位电路73.2 排队子系统模块设计83.3 工作人员服务模块设计83.4 业务提示模块设计83.4.1 LCD液晶屏单元83.4.2 语音播放单元93.5电源设计104、整体电路图115、系统软件设计125.1 通信协议125.2 业务调度系统程序设计135.3排队子程序设计145.4 服务子程序设计145.5业务提示子程序设计156、电路仿真结果167、总结198、参考文献20附录C源程序代码21摘要目前,于以银行营业大厅为代表的窗口业务,大量客户的拥挤排队已成为了这些企事业单位改善服务品质、提升企业形象的主要障碍。

排队叫号系统的使用将成为改变这种情况的有力手段。

排队系统完全模拟了人群排队的全过程,通过取票进队。

排队等待、叫号服务等功能,很好的解决了客户于服务机构办理业务是所遇到的各种排队、拥挤和混乱现象,代替了人们站队的辛苦,把顾客等待的烦恼变成了壹段难得的休闲时光,使客户拥有了壹个自由的空间和壹份美好的心情。

本次课程设计详细的介绍了设计的整过程,各个子系统的设计规则,而且仍基于MATLAB做了简单的仿真。

关键字:窗口业务、排队等待、呼叫服务、设计、MATLABAbstractAtpresent,inthebusinesshallofthebankastherepresentativeofthewindo wservice,alargenumberofcustomersqueuinghasbecomethemainobstacletotheseenterprisestoimproveservicequality,enhancecorporateimage.Theus eofqueuingsystemwillbecomeapowerfulmeanstochangethissituation.Que uingsystemisfullysimulatesthewholeprocessofthecrowdqueuing,theticketi ntotheteam.Queuing,queuingandservicefunctions,isaverygoodsolutionto customersintheservicebusinessisencounteredqueuing,crowdedandchaoti cphenomena,insteadofpeoplelineuphard,makecustomerwaitingannoyanc eintoarareleisuretime,sothatcustomershaveafreespaceandagoodmood. Keywords:windowservice,waitinginline,callservice,design,MATLAB1、设计内容由于嵌入式的电路板比较复杂,而次设计用单片机能够实现,所以相对来说用单片机设计比较简单,程序设计也比较方便。