DS12887是美国达拉斯半导体公司最新推出的时钟芯片,采用CMOS技术制成,把时钟芯片所需的晶振和外部锂电池相关电路集于芯片内部,同时它与目前 IBM AT计算机常用的时钟芯片

MC146818B和DS1287管脚兼容,可直接替换。采用DS12887芯片设计的时钟电路勿需任何外围电路并具有良好的微机接口。DS12887芯片具有微轼耗、外围接口简单、精度高、工作稳定可靠等优点,可广泛用于各种需要较高精度的实时时钟场合中。其主要功能如下:

(1)内含一个锂电池,断电情况运行十年以上不丢失数据。

(2)计秒、分、时、天、星期、日、月、年,并有闰年补偿功能。

(3)二进制数码或BCD码表示时间、日历和定闹。

(4)12小时或24小时制,12小时时钟模式带有PWM和AM指导,有夏令时功能。

(5)MOTOROLA5和INATAEL总线时序选择。

(6)有128个RAM单元与软件音响器,其中14个作为字节时钟和控制寄存器,114字节为通用RAM,所有ARAM单元数据都具有掉电保护功能。

(7)可编程方波信号输出。

(8)中断信号输出(IRQ)和总线兼容,定闹中断、周期性中断、时钟更新周期结束中断可分别由软件屏蔽,也可分别进行测试。

2. DS12887的原理及管脚说明

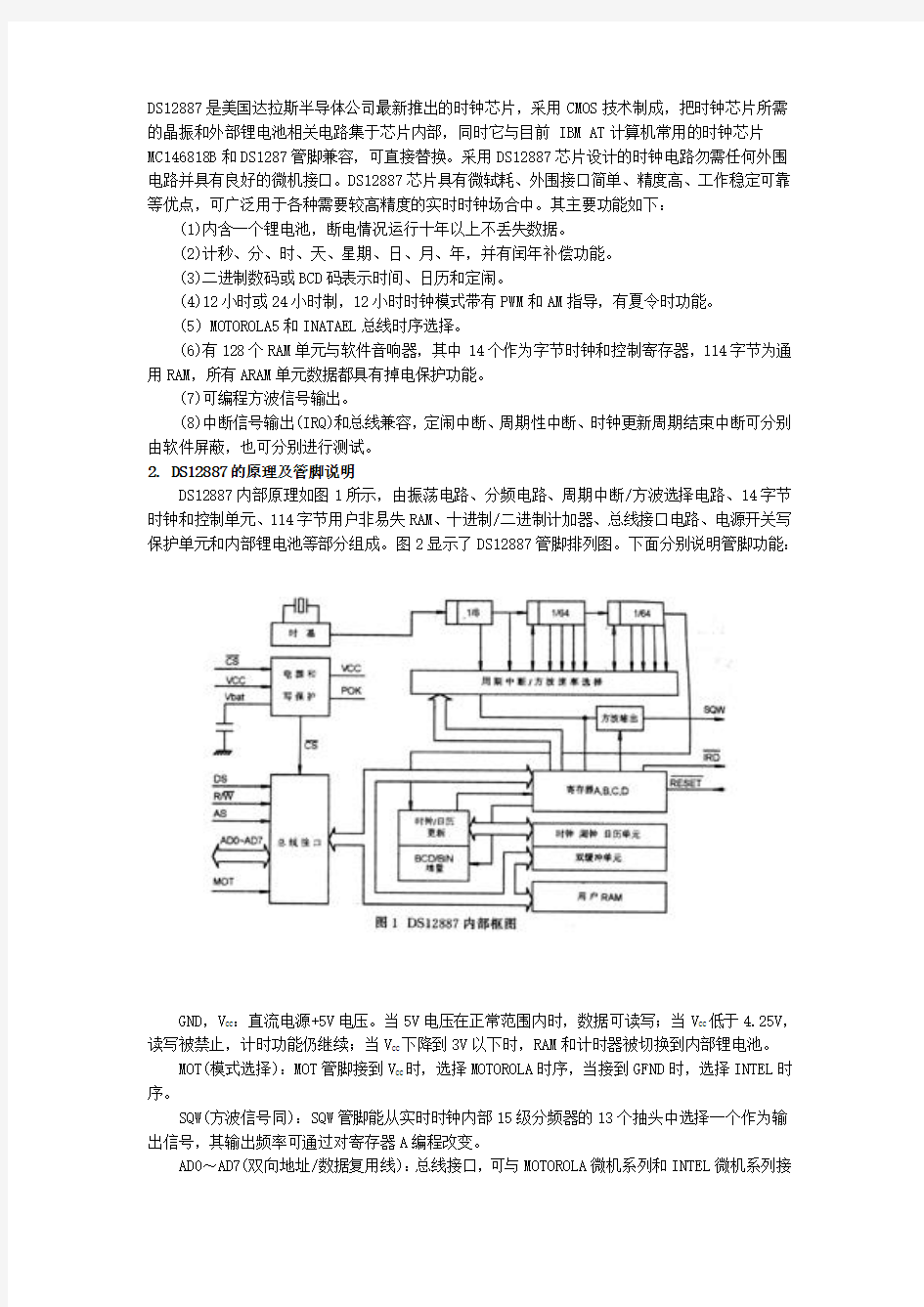

DS12887内部原理如图1所示,由振荡电路、分频电路、周期中断/方波选择电路、14字节时钟和控制单元、114字节用户非易失RAM、十进制/二进制计加器、总线接口电路、电源开关写保护单元和内部锂电池等部分组成。图2显示了DS12887管脚排列图。下面分别说明管脚功能:

GND,V CC:直流电源+5V电压。当5V电压在正常范围内时,数据可读写;当V CC低于4.25V,读写被禁止,计时功能仍继续;当V CC下降到3V以下时,RAM和计时器被切换到内部锂电池。

MOT(模式选择):MOT管脚接到V CC时,选择MOTOROLA时序,当接到GFND时,选择INTEL时序。

SQW(方波信号同):SQW管脚能从实时时钟内部15级分频器的13个抽头中选择一个作为输出信号,其输出频率可通过对寄存器A编程改变。

AD0~AD7(双向地址/数据复用线):总线接口,可与MOTOROLA微机系列和INTEL微机系列接

口。

AS(地址选通输入):用于实现信号分离,在AD/ALE的下降沿把地址锁入DS12887。

DS(数据选通或读输入):DS/RD客脚有两种操作模式,取决于MOT管脚的电平,当使用MOTOROLA时序时,DS是一正脉冲,出现在总线周期的后段,称为数据选通;在读周期,DS指示DS12887驱动双向总的时刻,在写周期,DS的后沿使DS12887锁存写数据。选择INTEL时序时,DS称作(RD),RD与典型存贮器的允许信号(OE)的定义相同。

R/W(读/写输入):R/W管脚也有两种操作模式。选MOTOROLA时序时,R/W是一电平信号,指示当前周期是读或写周期,DSO为高电平时,R/W高电平指示读周期,R/W低电平指示写周期;选INTEL时序,R/W信号是一低电平信号,称为WR。在此模式下,R/W管脚与通用RAM的写允许信号(WE)的含义相同。

CS(片选输入):在访问DS12887的总线周期内,片选信号必须保持为低。

IRQ(中断申请输入):低电平有效,可作微处理的中断输入。没有中断条件满足时,IRQ处于高阻态。IRQ线是漏极开路输入,要求外接上接电阻。

RESET(复位输出):当该脚保持低电平时间大于200ms,保证DS12887有效复位。

3. DS12887的内部功能

3.1 地址分配图

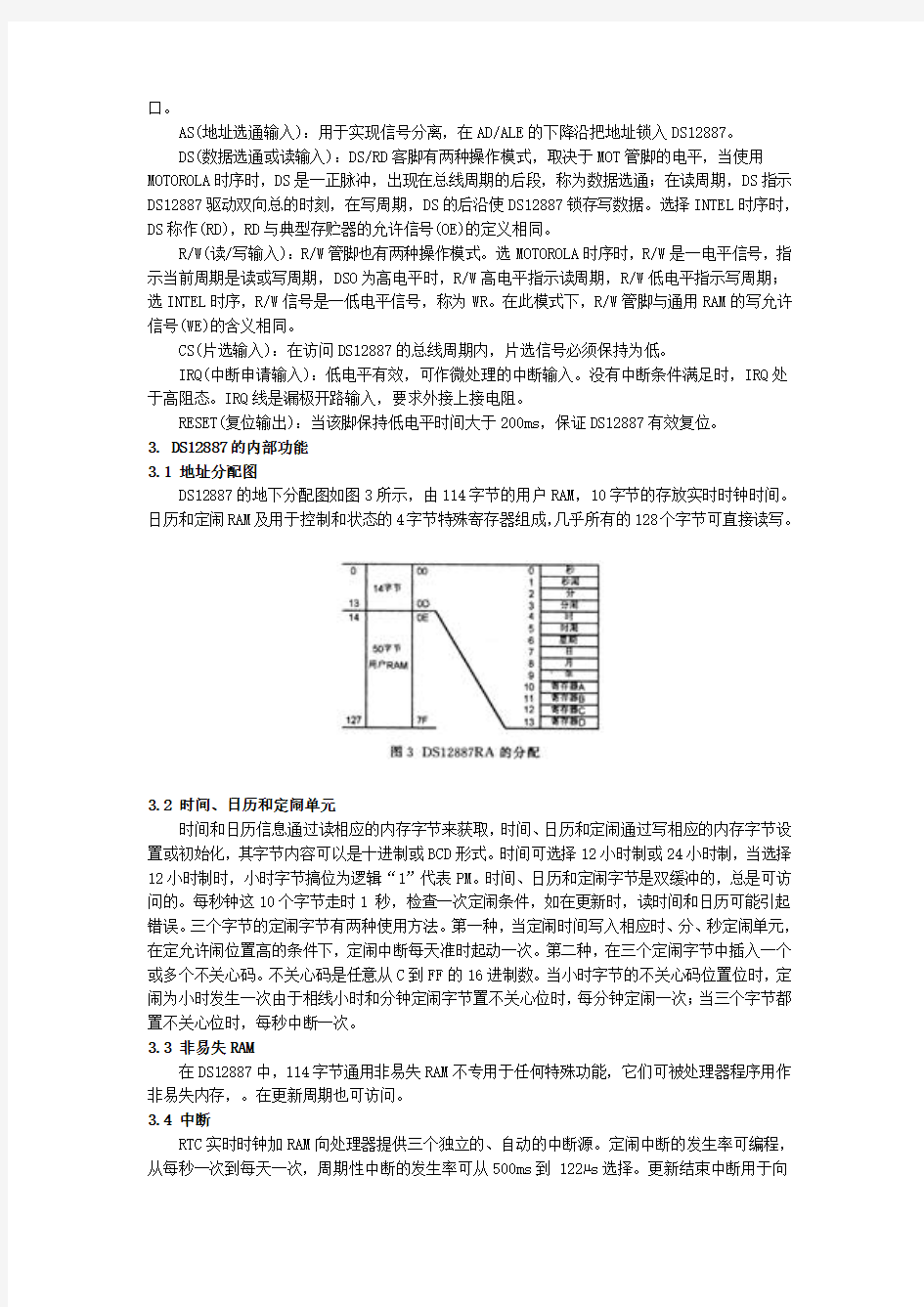

DS12887的地下分配图如图3所示,由114字节的用户RAM,10字节的存放实时时钟时间。日历和定闹RAM及用于控制和状态的4字节特殊寄存器组成,几乎所有的128个字节可直接读写。

3.2 时间、日历和定闹单元

时间和日历信息通过读相应的内存字节来获取,时间、日历和定闹通过写相应的内存字节设置或初始化,其字节内容可以是十进制或BCD形式。时间可选择12小时制或24小时制,当选择12小时制时,小时字节搞位为逻辑“1”代表PM。时间、日历和定闹字节是双缓冲的,总是可访问的。每秒钟这10个字节走时1 秒,检查一次定闹条件,如在更新时,读时间和日历可能引起错误。三个字节的定闹字节有两种使用方法。第一种,当定闹时间写入相应时、分、秒定闹单元,在定允许闹位置高的条件下,定闹中断每天准时起动一次。第二种,在三个定闹字节中插入一个或多个不关心码。不关心码是任意从C到FF的16进制数。当小时字节的不关心码位置位时,定闹为小时发生一次由于相线小时和分钟定闹字节置不关心位时,每分钟定闹一次;当三个字节都置不关心位时,每秒中断一次。

3.3 非易失RAM

在DS12887中,114字节通用非易失RAM不专用于任何特殊功能,它们可被处理器程序用作非易失内存,。在更新周期也可访问。

3.4 中断

RTC实时时钟加RAM向处理器提供三个独立的、自动的中断源。定闹中断的发生率可编程,从每秒一次到每天一次,周期性中断的发生率可从500ms到122μs选择。更新结束中断用于向

程序指示一个更新周期完成。中断控制和状态位在寄存器B和C中,本文的其它部分将详细描述每个中断发生条件。

3.5 晶振控制位

DS12887出厂时,其内部晶振被关掉,以防止锂电池在芯片装入系统前被消耗。寄存器A的BIT4~BIT6为010时打开晶振,分频链复位,BIT4~BIT6的其它组合都是使晶振关闭。

3.6 方波输出选择

如图1原理图所示,15级分步抽着中的13个可用于15选1选择器,选择分频器抽头的目的是在SQW管脚产生一个方波信号,其频率由寄存器A的 RS0~RS3位设置。SQW频率选择与周期中断发生器共离15选1选择器,一旦频率选择好,通过用程序控制方波输出允许位SWQE来控制SQW管脚输出的开关。

3.7 周期中断选择

周期中断可在IRQ脚产生500ms一次到每122μs一次的中断,中断频率同样由寄存A确定,它的控制位为寄存器B中的PIE位。

3.8 更新周期

DS12887每秒执行一次更新周期还比较每一定闹字节与相应的时间字节,如果匹配枵三个字节都是不关心码,则产生一次定闹中断。

4. DS12887状态控制寄存器

DS12887有4个控制寄存器,它们在任何时间都可访问,即使更新周期也不例外。

4.1 寄存器A

UIP:更新周期正在进行位。当UIP为1,更新转换将很快发生,当UIP为0,更新转换至少在244μs内不会发生。

DV0,DV1,DV2:用于开关晶振和复位分频链。这些位的010唯一组合将打开晶振并允许RTC 计时。

表1列了邮周期中断率和方波频率。

RS3,RS2,RS1,RS0:频率选择位,从15级频率器13个抽头中选一个,或禁止分频器输入,

选择好的抽头用于产生方波(SQW管脚)输出和周期中断,用户可以:

(1)用PIE位允许中断:

(2)用SQWE位允许SQAW输出;

(3)二者同时允许并用相同的频率;

(4)都不允许

4.2 寄存器B

SET:SET为0,时间更新正常进行,每秒计数走时一次,当SET位写入1,时间更新被禁止,程序可初始化时间和日历字节。

PIE:周期中断劲旅位,PIE为1,则允许以选定的频率拉低IRQ管脚,产和不足齿数民:PIE 为0,则禁止中断。

AIE:定闹中断允许位,PIE为1,允许中断,否则禁止中断。

SQWE:方波允许位,置1选定频率方波从SQW脚输出;为0-时,SQW脚为低。

DM:数据模式位,DM为1青蛙为十进制数据,而0表明是BCD码的数据。

24/12:小时格式位,1表明24小时械,而0表明12小时械。

DSE:P夏令时允许位,当DSE置1时允许两个特殊的更新,在四月份的第一时期日、时间从1:59:59AM时改变为1:00:00AM,当DSE位为0,这种特殊修正不发生。

4.3 寄存器C

IRQF:中断申请标志位。当下列表达式中一个或多个为真时,置1。

PF=PIE=1;AF=AIE=1;

UF=UIE=1;

即:IRQF=PF·PIE+AF·AIE+UF·UIE

只要IRQF为1,IRQ管脚输出低,程序读寄存器C以后或RESET管脚为低后,所有标志位清零。

AF:定闹中断标志位,只读,AF为1表明现在时间与定闹时间匹配。

VF:更新周期结束标志位。VF为1表明更新周期结束。

BIAT0~BIT3:未用状态位,读出总为0,不能写入。

4.4 寄存器D

VRT:内部锂电池状态位,平时应总读出1,如出现0,表明内部锂电池耗尽。

BIT0~BIT6:未用状态位,读出总为0,不能写入。

5. 硬件接口电路

DS12887时钟芯片和AT89C51单微机的接口电路如图4所示,选择DS12887时钟芯片的地址

总线及 AS端口和AT89C51单片微机的P0及ALE端直接相联;而DS、R/W读写控制线与单片机的RD、WAR控制线相连;DS12887的高位地址由 80C31半日片机的P2.7端口来片选,则DS12887的高8位地址定为7FH,而其低8侠地址则由芯片内部各单元的地址来决定(00H~3FH); DS12887的中断输出端IRQ和80C的外部INT0端相联,给单片机提供中断信号;DS12887的SQW端口可编程产生方波输出信号。

6. 接口软件

下面为DS12887时钟芯片和80C31单片机的接口软件,假定采用每天24小时制的非夏令时,时间数据格式为BCD码,初始化时间为1996年1月1 日9时00分00秒,1k方波输出。时钟芯片每一秒种向单片机申请中断一次,一方面让单片机修改一次时钟显示,另一方面也给单片微机系统提供时间基准。

(1)DS12887时钟芯片的初始化写入程序

MOV DPTR,#7F0AH;寄存器A地址

MOV A,#70H:DV2~DV0=111,分频复位

MOVX @ DPTR,AA

INC DPTR:到寄存器B地址

MOV A,#8AH:停止更新,允许更新中断,选BCD码,24小时制

MOVX @DPRT,A

MOV QPL,#00H,秒单元地址

CLR A:00秒

MOVX @DPTR,A

MOV DPL,#02H;分单元地址

CLR A:00分

MOVX @DPTR,A

MOV DPL,#04H;时单元地址

MOV A,#09H;9时

MOVX @DPTR,A

MOV DPL#07H;日单元地址

MOV A,@01H:1日

MOVX @DPTR,A

INC DPTR:到月单元地址

MOV A,#01H;1月

MOVX @DPTR,A

IC DPTR:到年单元地址

MOV A,#96H;1996年

MOVX @DPTR,A

INC DPTR;到寄存器A地址

MOV A,#26H;DV2~DV0=010 RS3~RS0=0110

MOVX @DPTR,A:选周期中断率为976.5625μs,允许方波输出,频率1kHz

INC DPTR:到寄存器B

MOV A,#1AH;每秒更新一次,允许方波输出,24小时制

MOVX @DPTR,A:时钟开始运行

(2)读取DS12887时钟日历数据程序

DS12887的日历时钟通常有中断和查询两种方法读出。但在读数据时,首先要判断数据是否更新结束,只有在数据更新结束时数据读出才有效。

①采用查询法读取数据:

查询寄存器A的UIP位,当UIP=0时,数据更新结束,可以读出。以下是采用查询方法,从秒至年单元的数据读出后存入80C31内部RAM的30~35H单元中,该部分程序如下:

MOV DPTR,#7F0AH;寄存器A地址

MOVX A,@DPTR

WAIT:JB ACC,7,WAIT:UIP=1则等待更新完毕

MOV DPL,@00H;秒地址

MOV R0,#30H;取目标首地址

MOVX A,@DPTR;取秒数据

MOV @R0,A:送入80C31的内部RAM缓冲区

IC DPTR:移指针

IC R0

;以下略

②采用中断法读取数据

当DS12887发出中断请示,单片微机可以响应中断而读取日历数据。对于更新结束中断,中断时更新结束,数据有效,可以直接读取日历数据;对于闹钟中断和周期中断也需查询寄存器A 的UIP位,当UIP=0时,数据更新结束,再读出日历时钟,具体指令这里不再列出

单片机玩到此时,很想玩TFT真彩屏,但如果不玩一玩汉显字符液晶屏,就总觉得少了些什么,说实话,我对时钟制作并不很感兴趣,因为家里走针的、蹦字的计时器、定时器大小有七八个,还不算手机和电脑的时钟,而要想玩汉显屏,则做时钟算是最合适的了,也难怪杜洋老师会在这上下功夫,毕竟没有那家公司会让咱初学者去搞工控或商品。前些时,在网上淘了一只LCD-12864模块,已经点亮并通过了简单的测试,准备做杜洋的时钟,准备技术资料时,在网上找到了一篇关于时钟芯片DS1302的应用文章,觉得不错,转帖于此以资共享。 时钟芯片DS1302可靠起振的方法 作者:不详出处:不详 DS1302是Dallas公司生产的一种实时时钟芯片。它通过串行方式与单片机进行数据传送,能够向单片机提供包括秒、分、时、日、月、年等在内的实时时间信息,并可对月末日期、闰年天数自动进行调整;它还拥有用于主电源和备份电源的双电源引脚,在主电源关闭的情况下,也能保持时钟的连续运行。另外,它还能提供31字节的用于高速数据暂存的RAM。鉴于上述特点,DS1302已在许多单片机系统中得到应用,为系统提供所需的实时时钟信息。 一、 DS1302的主要特性 1. 引脚排列 图1 DS1302引脚排列图(见附图) DS1302的引脚排列如图1所示,各引脚的功能如下: X1,X2——32768Hz晶振引脚端; RST——复位端; I/O——数据输入/输出端; SCLK——串行时钟端; GND——地; VCC2,VCC1——主电源与后备电源引脚端。 2. 主要功能: DS1302时钟芯片内主要包括移位寄存器、控制逻辑电路、振荡器、实时时钟电路以及用于高速暂存的31字节RAM。DS1302与单片机系统的数据传送依靠RST,I/O,SCLK三根端线即可完成。其工作过程可概括为:首先系统RST引脚驱动至高电平,然后在作用于SCLK时钟脉冲的作用下,通过I/O引脚向DS1302输入地址/命令字节,随后再在SCLK时钟脉冲的配合下,从I/O引脚写入或读出相应的数据字节。因此,其与单片机之间的数据传送是十分容易实现的。 二、时钟的产生及存在的问题 (1) 在实际使用中,我们发现DS1302的工作情况不够稳定,主要表现在实时时间的传送有时会出现误差,有时甚至整个芯片停止工作。我们对DS1302的工作电路进行了分析,其与单片机系统的连接如图2所示。从图中可以看出,DS1302的外部电路十分简单,惟一外接的元件是32768Hz 的晶振。通过实验我们发现:当外接晶振电路振荡时,DS1302计时正确;当外接晶振电路停振时,DS1302计时停止。因此,我们认为32768Hz晶振是造成DS1302工作不稳定的主要原因。 图2 DS1302与单片机系统的连接图(见附图) (2) DS1302时钟的产生基于外接的晶体振荡器,振荡器的频率为32768Hz。该晶振通过引脚X1、X2直接连接至DS1302,即DS1302是依靠外部晶振与其内部的电容配合来产生时钟脉冲的。

- - -. 目录 1 、课程设计目的 (2) 2 、课程设计和要求 (2) 2.1、设计内容 (2) 2.2、设计要求 (2) 3 、设计方案 (2) 3.1、设计思路 (2) 3.2、工作原理及硬件框图 (2) 3.3、硬件电路原理图 (8) 3.4、PCB版图设计 (8) 4 、课程设计总结 (9) 5 、参考文献 (11)

一、课程设计目的 (1)掌握电子电路的一般设计方法和设计流程; (2)学习简单电路系统设计,掌握Protel99的使用方法; (3)掌握8051单片机、实时时钟/日历芯片MC146818的应用; (4)学习掌握硬件电路设计的全过程。 二·课程设计内容和要求 2.1、设计内容:设计一个基于单片机实时时钟/日历 2.2、设计要求: (1)学习掌握8051单片机的工作原理及应用; (2)学习掌握实时时钟/日历芯片MC146818的工作原理及应用; (3)设计MC146818与8051的接口电路原理图及PCB版图; (4)整理设计内容,编写设计说明书。 三·设计方案 3.1、设计思路 数字时钟系统的组成: 硬件电路设计主要围绕时钟日历芯片MC146818的使用进行的,主要由8051单片机·MC146818时钟日历芯片·液晶显示屏·键盘组成。 3.2、工作原理及硬件框图 工作原理:

图(1)数字时钟系统框图 (3)电路设计 8051单片机: 单片机的40个引脚大致可分为4类:电源、时钟、控制和I/O引脚。 ⒈电源: ⑴ VCC - 芯片电源,接+5V; ⑵ VSS - 接地端;

⒉时钟: XTAL1、XTAL2 - 晶体振荡电路反相输入端和输出端。 ⒊控制线: 控制线共有4根, ⑴ ALE/PROG:地址锁存允许/片内EPROM编程脉冲 ① ALE功能:用来锁存P0口送出的低8位地址 ② PROG功能:片内有EPROM的芯片,在EPROM编程期间,此引脚输入编程脉冲。 ⑵ PSEN:外ROM读选通信号。 ⑶ RST/VPD:复位/备用电源。 ① RST(Reset)功能:复位信号输入端。 ② VPD功能:在Vcc掉电情况下,接备用电源。 ⑷ EA/Vpp:内外ROM选择/片内EPROM编程电源。 ① EA功能:内外ROM选择端。 ②Vpp功能:片内有EPROM的芯片,在EPROM编程期间,施加编程电源Vpp。 ⒋ I/O线 8051共有4个8位并行I/O端口:P0、P1、P2、P3口,共32个引脚。P3口还 具有第二功能,用于特殊信号输入输出和控制信号(属控制总线)。 (2)时钟日历芯片MC146818: MC146818是MOTOROLA公司生产的CMOS实时时钟/日历芯片,该芯片可

(用数码管显示实时日历时钟的应用设计)

摘要 本课题通过MCS-51单片机来设计电子时钟,采用汇编语言进行编程,可以实现以下一些功能:小时,分,秒和年,月,日的显示。本次设计的电子时钟系统由时钟电路,LED显示电路三部分组成。51单片机通过软件编程,在LED数码管上实现小时,分,秒和年,月,日的显示;利用时钟芯片DS1302来实现计时。本文详细介绍了DS1302 芯片的基本工作原理及其软件设计过程,运用PROTEUS软件进行电路连接和仿真,同时还介绍了74LS164,通过它来实现I|O口的扩展。 关键词:时钟芯片,仿真软件,74LS164 目录 前言 0.1设计思路 (8) 0.2研究意义 (8)

一、时钟芯片 1.1 了解时钟芯片……………………………………………….8-9 1.2 掌握时钟芯片的工作原理………………………………….10-11二、74LS164 2.1 了解74LS164........................................................11-12 2.2 掌握的74LS164工作原理. (12) 三、数码管 3.1 熟悉常用的LED数码管...........................................12-13 3.2 了解动态显示与静态显示. (13) 四、程序设计 4.0 程序流程图 (14) 4.1 DS1392的驱动.......................................................15-16 4.2 PROTUES实现电路连接. (17) 4.3 数码管的显示:小时;分;秒 (18) 4.4 数码管显示:年;月;日 (19) 五、总结…………………………………………………………………..20-21 六、附页程序………………………………………………………………22-31前言

目录 1题目设计的要求 (1) 2 系统硬件设计 (1) 2.1设计原理 (1) 2.2器件的功能与作用 (1) 2.2.1 MCS51单片机AT89C51 (1) 2.2.2 串行时钟日历片DS1302 (2) 2.2.3 液晶显示LCD1602 (3) 3 系统软件设计 (4) 3.1程序流程 (4) 3.2程序代码 (5) 4 系统仿真调试 (12) 4.1仿真原理图设计 (12) 4.2仿真运行过程 (12) 4.3仿真运行结果 (13) 5 总结 (13) 6 参考文献 (13)

1题目设计的要求 通过串行日历时钟芯片DS1302生成当前日期和是时间,通过IO口传输到AT89c52芯片中,然后再将AT89c52接收到的数据输出到LCD上。要求LCD上显示的日期和时间与当前系统时间保持一致。 2 系统硬件设计 2.1 设计原理 图3.1 电路原理图 2.2 器件的功能与作用 2.2.1 MCS51单片机AT89C51 XX AT89C51是一种带4K字节FLASH存储器(FPEROM—Flash Programmable and Erasable Read Only Memory)的低电压、高性能CMOS 8位微处理器,俗称单片机。AT89C2051是一种带2K字节闪存可编程可擦除只读存储器的单片机。单片机的可擦除只读存储器可以反复擦除1000次。该器件

采用ATMEL高密度非易失存储器制造技术制造,与工业标准的MCS-51指令集和输出管脚相兼容。 由于将多功能8位CPU和闪烁存储器组合在单个芯片中,ATMEL的AT89C51是一种高效微控制器。 AT89C51单片机为很多嵌入式控制系统提供了一种灵活性高且价廉的方案。 2.2.2 串行时钟日历片DS1302 系统的组成与工作原理: 系统由单片机AT89C52,串行日历时钟片DS1302,液晶显示模组LCD1602。 DS1302的CLOCK与AT89C52的P1.6相连,RST与P1.5相连,IO与P1.7相连。 LCD1602的D0~D7与AT89C51的P0.0~P.7相连,并接上拉电阻,RS与P2.0相连,RW与P2.1相连,E与P2.2相连。 DS1302是DALLAS公司拖出的涓流充电时钟芯片,内含有一个实时时钟/日历和31个季节静态RAM,通过简单地串行接口与单片机进行通信,实时时钟/日历电路提供秒、分、时、日、日期、月、年的信息,每月的天数和闰年的天数可自动调整,时钟操作可通过AM/PM指示决定采用24小时或12小时格式,DS1302与单片机之间能简单地采用同步串行方式进行通信,仅需用到RES复位、I/O 数据线、SCLK串行时钟3个口线。对时钟、RAM的读/写,可以改用单字节方式或多达31个字节的字符组方式。DS1302工作时功耗很低,保持数据和时钟信息是功率小于1mW。DS1302广泛应用于电话传真、便携式仪器及电池供电的仪器仪表等产品领域中。 RT-1602 字符型液晶模块是以两行16个子的5*7点阵吐信来显示字符的液晶显示器。 DS1302有8个引脚: X1、X2:32.768kHz晶振介入引脚。 GND:地。 RST:复位引脚,低电平有效。 I/O:数据输入/输出引脚,具有三态功能。 SCLK:串行时钟输入引脚。 Vcc1:工作电源引脚。 Vcc2:备用电源引脚。 DS1302有一个控制寄存器,12个日历,时钟寄存器和31个RAM。 控制寄存器 控制寄存器用于存放DS1302的控制命令字,DS1302的RST引脚回到高电平后写入的第一个字就为控制命令。它用于对DS1302读写过程进行控制,它的格式如下:

实时时钟芯片DS1302的结构,工作原理及应用(含源程序) 1.ds1302实时时钟简介 现在流行的串行时钟电路很多,如DS1302、DS1307、PCF8485等。这些电路的接口简单、价格低廉、使用方便,被广泛地采用。本文介绍的实时时钟电路DS1302是DALLAS公司的一种具有涓细电流充电能力的电路,主要特点是采用串行数据传输,可为掉电保护电源提供可编程的充电功能,并且可以关闭充电功能。采用普通32.768kHz晶振。 2 DS1302的结构及工作原理 DS1302是美国DALLAS公司推出的一种高性能、低功耗、带RAM的实时时钟电路,它可以对年、月、日、周日、时、分、秒进行计时,具有闰年补偿功能,工作电压为2.5V~5.5V。采用三线接口与CPU进行同步通信,并可采用突发方式一次传送多个字节的时钟信号或RAM数据。DS1302内部有一个31×8的用于临时性存放数据的RAM寄存器。DS1302是DS1202的升级产品,与DS1202兼容,但增加了主电源/后背电源双电源引脚,同时提供了对后背电源进行涓细电流充电的能力。 2.1 引脚功能及结构 图1示出DS1302的引脚排列,其中Vcc1为后备电源,VCC2为主电源。在主电源关闭的情况下,也能保持时钟的连续运行。DS1302由Vcc1或Vcc2两者中的较大者供电。当Vcc2大于Vcc1+0.2V时,Vcc2给DS1302供电。当Vcc2小于Vcc1时,DS1302由Vcc1供电。X1和X2是振荡源,外接32.768kHz晶振。RST是复位/片选线,通过把RST输入驱动置高电平来启动所有的数据传送。RST输入有两种功能:首先,RST接通控制逻辑,允许地址/命令序列送入移位寄存器;其次,RST提供终止单字节或多字节数据的传送手段。当RST 为高电平时,所有的数据传送被初始化,允许对DS1302进行操作。如果在传送过程中RST 置为低电平,则会终止此次数据传送,I/O引脚变为高阻态。上电运行时,在Vcc≥2.5V之前,RST必须保持低电平。只有在SCLK为低电平时,才能将RST置为高电平。I/O为串行数据输入输出端(双向),后面有详细说明。SCLK始终是输入端。 2.2 DS1302的控制字节

目录 摘要 一、引言 (1) 二、硬件电路设计 (2) 2.1 主要芯片 (2) 2.1.1 微处理器 (2) 2.1.2 DS1302简介 (4) 2.1.3 DS1302引脚说明 (5) 2.1.4 74ls245简介及引脚说明 (5) 2.2 时钟硬件电路设计 (6) 2.2.1 时钟电路设计 (7) 2.2.2 整点报时功能 (8) 2.2.3 硬件原理图 (9) 三、proteus和keil软件仿真及调试 (9) 3.1 电路的仿真 (9) 3.2 软件调试 (9) 四、C语言程序 (10) 五、参考文献 (13)

电子时钟主要是利用电子技术将时钟电子化、数字化,拥有时钟精确、体积小、界面友好、可扩展性能强等特点,被广泛应用于生活和工作当中。另外,在生活和工农业生产中,也常常需要温度,这就需要电子时钟具有多功能性。 本文对当前电子钟开发手段进行了比较和分析,最终确定了采用单片机技术实现多功能电子时钟。本设计应用AT89C52芯片作为核心,6位LED数码管显示,使用DS1302实时时钟日历芯片完成时钟/日历的基本功能。这种实现方法的优点是电路简单,性能可靠,实时性好,时间精确,操作简单,编程容易。 本设计主要为实现一款可正常显示时钟/日历、带有定时闹铃的多功能电子时钟。该电子时钟可以应用于一般的生活和工作中,也可通过改装,提高性能,增加新功能,从而给人们的生活和工作带来更多的方便。 关键词:电子钟;多功能;AT89C52;时钟芯片

一、引言 时间是人类生活必不可少的重要元素,如果没有时间的概念,社会将不会有所发展和进步。从古代的水漏、十二天干地支,到后来的机械钟表以及当今的石英钟,都充分显现出了时间的重要,同时也代表着科技的进步。致力于计时器的研究和充分发挥时钟的作用,将有着重要的意义。 1.1 多功能电子时钟研究的背景和意义 20世纪末,电子技术获得了飞速的发展。在其推动下,现代电子产品几乎渗透到了社会的各个领域,有力的推动和提高了社会生产力的发展与信息化程度,同时也使现代电子产品性能进一步提升,产品更新换代的节奏也越来越快。 时间对人们来说总是那么宝贵,工作的忙碌性和繁杂容易使人忘记当前的时间。然而遇到重大事情的时候,一旦忘记时间,就会给自己或他人造成很大麻烦。平时我们要求上班准时,约会或召开会议必然要提及时间;火车要准点到达,航班要准点起飞;工业生产中,很多环节都需要用时间来确定工序替换时刻。所以说能随时准确的知道时间并利用时间,是我们生活和工作中必不可少的[1]。 电子钟是采用电子电路实现对时、分、秒进行数字显示的计时装置,广泛应用于个人家庭,车站,码头办公室等公共场所,成为人们日常生活中不可少的必需品。由于数字集成电路的发展和石英晶体振荡器的广泛应用,使得数字钟的精度,远远超过老式钟表,钟表的数字化给人们生产生活带来了极大的方便,而且大大地扩展了钟表原先的报时功能。诸如定时自动报警、0按时自动打铃、定时广播、自动起闭路灯、定时开关烘箱、通断动力设备、甚至各种定时电气的自动启用等,所有这些,都是以钟表数字化为基础的。因此,研究数字钟及扩大其应用,有着非常现实的意义。

目录 1.题目设计要求 (1) 2.开发平台简介 (1) 3.系统硬件设计 (2) 3.1设计原理 (2) 3.2器件的功能与作用 (2) 3.2.1 MCS51单片机AT89C51 (2) 3.2.2复位电路 (3) 3.2.3晶振电路 (4) 3.2.4 DS1302时钟模块 (4) 3.2.5 引脚功能及结构 (4) 3.2.6 DS1302的控制字节 (5) 3.2.7 数据输入输出(I/O) (5) 3.2.8 DS1302的寄存器 (6) 3.2.9 液晶显示LCD1602 (6) 3.2.10 串行时钟日历片DS1302 (8) 4.系统软件设计 (10) 4.1程序流程 (10) 4.2程序代码 (10) 5.系统仿真调试 (20) 5.1仿真原理图设计 (20) 5.2仿真运行过程 (21) 5.3仿真运行结果 (21) 6.总结 (21) 7.参考文献 (22)

1.题目设计要求 通过串行日历时钟芯片DS1302生成当前日期和是时间,通过IO口传输到AT89c52芯片中,然后再将AT89c52接收到的数据输出到LCD上。要求LCD上显示的日期和时间与当前系统时间保持一致。 2.开发平台简介 2.1系统仿真平台Proteus Proteus软件是由英国Labcenter Electronics公司开发的EDA工具软件,已有近20年的历史,在全球得到了广泛应用。Proteus软件的功能强大,它集电路设计、制版及仿真等多种功能于一身,不仅能够对电工、电子技术学科涉及的电路进行设计,还能够对微处理器进行设计和仿真,并且功能齐全,界面多彩。和我们手头其他的电路设计仿真软件,他最大的不同即它的功能不是单一的。另外,它独特的单片机仿真功能是任何其他仿真软件都不具备的。 2.2软件开发平台Keil C Keil C51是美国Keil Software公司出品的51系列兼容单片机C语言软件开发系统,与汇编相比,C语言在功能上、结构性、可读性、可维护性上有明显的优势,因而易学易用。Keil提供了包括C编译器、宏汇编、连接器、库管理和一个功能强大的仿真调试器等在内的完整开发方案,通过一个集成开发环境(uVision)将这些部分组合在一起。Keil C51生成的目标代码效率之高,多数语句生成的汇编代码很紧凑,容易理解。在开发大型软件时更能体现高级语言的优势。

实时时钟芯片应用设计时必须要考虑的事项 总述 实时时钟芯片(RTC)允许一个系统能同步或记录事件,给用户一个易理解的时间参考。由于RTC的应用越来越广泛,为了避开设计时出现的问题,设计者应熟悉RTCs。 选择接口 RTC可用的总线接口范围很宽。串行接口包括2线(I2C),3线和串行外设接口(SPI)。并行接口包含多总线(多数据和地址线)和带单独地址及字节数据输入的设计。接口的选择通常由所用的处理器类型决定,很多处理器包括2线或SPI接口。其它的,如8051处理器及其派生的处理器支持多路地址和数据总线。时间保持非易失性(NV)RAM和SRAM用相同的控制信号,许多处理器都提供这种方便的接口,也包括各种不同的用电池组支持的RAM。最后,看不见的时钟隐藏电池供电的RAM中并可用64位的软件协议去访问时钟。 备用电池的功能 在有的应用中,例如VCRS,如果去掉电源,会丢失时间和日期信息,。许多新的应用中,即使主电源去掉了,要求时间和日期信息应保持有效。为了保持时钟晶振运行,要用到一个主电源或者备用电源,或者一个大容量的电容。在这种情况下,时钟芯片必须能够在两个电源之间进行切换。 如果有一个电池,例如钮扣型锂电池用作备用电源,当在用备用电源工作时RTC应设计成尽可能少的消耗功耗。电源切换电路,一般情况下由主电源供电,会使电源切换到电池供电,并使RTC进入低功耗模式。微处理器和RTC之间的通信通常锁定(称为写保护),用来使电池供电电流最小和防止数据损坏。 许多时钟芯片都包括一个晶振控制位,通常称之为时钟中断(CH)或是晶振使能位(/EOSC)。此位通常位于秒寄存器或控制寄存器的最高位(位7),几乎在有这位的所有时钟芯片中,初始电池上的首选状态对于晶振来说是无效的。这允许系统设计者提出制造流程,在安装和测试后,用Vbat进行供电,通常用个锂电池。此时晶振处于一个停止状

PCF8563 实时时钟日历芯片选型指南 1. 概述 PCF8563是低功耗的CMOS实时时钟日历芯片。它提供一个可编程时钟输出一个中断输出和掉电检测器所有的地址和数据,通过I2C总线接口串行传递最大总线速度为400Kbits/s,每次读写数据后内嵌的字地址寄存器会自动产生增量。 2. 特性 低工作电流典型值:0.25 A,VDD=3.0V Tamb=25 时; 世纪标志; 大工作电压范围:1.0V--5.5V; 低休眠电流典型值为:0.25 A(VDD=3.0V,Tamb=25 ); 400KHz 的I2C 总线接口:VDD=1.8 5.5V 时; 可编程时钟输出频率为:32.768KHz、1024Hz、32Hz、1Hz; 报警和定时器; 内部集成的振荡器电容片内电源复位功能掉电检测器; I2C 总线从地址:读0A3H 写0A2H; 开漏中断引脚。 3. 应用 复费率电度表IC、卡水表IC、卡煤气表 便携仪器 传真机移动电话 电池电源产品 4.简明参考数据

8.功能描述 PCF8563内有16个8位的地址递增寄存器,一个32.768 kHz片上集成电容振荡器,一个实时时钟源(RTC)的分频器,可编程的时钟输出,一个定时器,报警器,一个低压检测器和400KHz的I2C接口。 所有16个寄存器被设计成可寻址的8位并行寄存器,虽然不是所有的位都有效。前两个寄存器(内存地址00H和01H),用于控制与/或状态寄存器。内存地址02H至08H是时钟功能的计数器,用于(秒、分、时、日、月、年计数器)。内存地址09H至0CH包含定义报警的条件的报警寄存器。内存地址0DH控制CLKOUT的输出频率。0EH和0FH分别是定时控制器和定时器。 秒、分钟、小时、天、月、年、以及每分钟报警、小时报警、日报警寄存器都以BCD 格式编码。平日和星期报警寄存器不以BCD格式编码。 当一个RTC寄存器被读取,所有的寄存器的内容被冻结。因此可以避免在读指令跳转期间,读取时钟/日历时发生错误。 8.1 报警功能模式 通过清除一个或多个报警寄存器最高有效位(位AE=报警启用),相应的报警条件将被激活。这种方式可以产生从每分钟至每周一次的报警。报警条件设置报警标志,AF(控制/状态寄存器2的第3位),AF可用于产生一个中断(INT),AF只能通过软件清零。 8.2 定时器模式 8位减数计时器(地址0FH)由定时控制寄存器(地址0EH,参见表25)控制。定时控制寄存器可以选择定时器的时钟源频率(4096,64,1,或1/60Hz)和启用/禁用计时器。从软件加载的8位二进制值的倒计时,在每个倒计时结束时,定时器设置的定时器标志TF(见表7)。定时器标志位TF只能由软件清零。根据定时器标志位TF可以产生一个中断(INT)。每个倒计时阶段都可能会产生中断脉冲信号,作为一个永久的积极信号,如TF条件下。TI/ TP(见表7)用于控制这种模式的选择。当读取定时器,当前的倒计时数值作为返回值。 8.3 CLKOUT输出 CLKOUT引脚有可编程方波。由CLKOUT频率寄存器(地址0DH;见表23)控制操作。时钟频率32.768KHz(默认),1024,32和1Hz的频率可以作为系统时钟,单片机的时钟,输入到电荷泵,或校准振荡器。CLKOUT开漏输出,上电时启用。如果禁用它变为高阻抗。8.4 复位低电压检测器和时钟监视器 PCF8563的包括内部复位电路,振荡器停止时,复位电路激活。在复位状态下,I2C总线初始化,所有寄存器和地址指针被清零,VL、TD1、TD0、TESTC和AE被设置为逻辑1。8.5 低电压检测器和时钟监视器 PCF8563芯片的低电压探测器。当VDD低于Vlow,VL位(秒寄存器第7位)设置表明可靠的时钟/日历信息将不再保证。VL标志只能由软件清零。 位VL用于检测在电池供电情况下,VDD慢慢降低到Vlow的情况。在VDD低于Vlow之前应该把VDD从新拉高。这种情况下,时间可能被损坏。 8.6 寄存器结构

RTC实时时钟芯片 RTC实时时钟芯片是一种计时器,可以由硬件集成电路来完成,也可以由单片机加程序来完成。实时时钟可以对秒、分、时、星期、日、月和年进行准确计时,具有闰年补偿功能,能够计时到2100年。

消费类电子(机顶盒、VCR),手持式装置(GPS、POS终端),医疗设备,办公设备,电信(路由器、交换机、服务器),电器设备,汽车,消费类电子,嵌入式时标,工业,电表。 DS3231集成了温度补偿晶体振荡器(TCXO)和晶体,电池备份输入用于支持连续计时,可编程方波输出,低电平有效复位输出。关键参数: 工作温度商业级:0°C至+70°C,具有2ppm精度; 工业级:40°C至+85°C,具有3.5pmm精度。 DS3231M是业内首款内置MEMS、带温度补偿的RTC,允许器件用于强烈震动的场合,不会由于晶体失效而导致产品故障。 DS3232相比较于DS3231将32kHz输出驱动器更改为推挽输出,省去一个外部上拉电阻,节省空间,够加快时钟的边沿速度,降低器件功耗。电池切换时,可通过32kHz位选择使能/禁止32kHz输出。DS3232的32kHz输出在关闭状态下驱动至低电平,DS3231的32kHz输出在关闭状态下为高阻输出。DS3232内部可通过2个CRATE位控制温度转换速率,这些位用于控制器件的采样率。采样率决定了对温度传感器进行数字转换的频率,以及补偿振荡器的时间间隔。降低采样率则降低了温度传感器的工作频率,从而降低整体功耗。此外,DS3232具有236字节的SRAM。

压检测功能和振荡停止检测功能,内置定时器可以产生周期性的定时中断信号,警报器用于定时报警,可设定天、日期、小时、分钟。工作电压范围:1.70V-5.5V。计时保持电压:1.15V-5.5V。此外,采用IIC接口,支持低功耗模式。 RX6110 频率输出功能:能选择输出频率,有32.768kHz, 1024Hz, 1Hz。 接口类型:IIC总线接口和SPI总线接口。 自动电源切换功能:当VDD低于1.6V失效时,内部电源自动切换到VBAT. 内置128位的RAM。 定时器功能:当事件出现时,定时器可以自动记录到TF-bit,并能通过/IRQ1 或/IRQ2引脚输出。 报警功能:当事件出现时,定时器可以自动记录到AF-bit,并能通过/IRQ1引脚输出。 工作电压范围:1.6V-5.5V。 计时保持电压:1.1V-5.5V。

DS12887是美国达拉斯半导体公司最新推出的时钟芯片,采用CMOS技术制成,把时钟芯片所需的晶振和外部锂电池相关电路集于芯片内部,同时它与目前 IBM AT计算机常用的时钟芯片 MC146818B和DS1287管脚兼容,可直接替换。采用DS12887芯片设计的时钟电路勿需任何外围电路并具有良好的微机接口。DS12887芯片具有微轼耗、外围接口简单、精度高、工作稳定可靠等优点,可广泛用于各种需要较高精度的实时时钟场合中。其主要功能如下: (1)内含一个锂电池,断电情况运行十年以上不丢失数据。 (2)计秒、分、时、天、星期、日、月、年,并有闰年补偿功能。 (3)二进制数码或BCD码表示时间、日历和定闹。 (4)12小时或24小时制,12小时时钟模式带有PWM和AM指导,有夏令时功能。 (5)MOTOROLA5和INATAEL总线时序选择。 (6)有128个RAM单元与软件音响器,其中14个作为字节时钟和控制寄存器,114字节为通用RAM,所有ARAM单元数据都具有掉电保护功能。 (7)可编程方波信号输出。 (8)中断信号输出(IRQ)和总线兼容,定闹中断、周期性中断、时钟更新周期结束中断可分别由软件屏蔽,也可分别进行测试。 2. DS12887的原理及管脚说明 DS12887内部原理如图1所示,由振荡电路、分频电路、周期中断/方波选择电路、14字节时钟和控制单元、114字节用户非易失RAM、十进制/二进制计加器、总线接口电路、电源开关写保护单元和内部锂电池等部分组成。图2显示了DS12887管脚排列图。下面分别说明管脚功能: GND,V CC:直流电源+5V电压。当5V电压在正常范围内时,数据可读写;当V CC低于4.25V,读写被禁止,计时功能仍继续;当V CC下降到3V以下时,RAM和计时器被切换到内部锂电池。 MOT(模式选择):MOT管脚接到V CC时,选择MOTOROLA时序,当接到GFND时,选择INTEL时序。 SQW(方波信号同):SQW管脚能从实时时钟内部15级分频器的13个抽头中选择一个作为输出信号,其输出频率可通过对寄存器A编程改变。 AD0~AD7(双向地址/数据复用线):总线接口,可与MOTOROLA微机系列和INTEL微机系列接

Integrated Circuit Systems, Inc. ICS954119 Advance Information Pin Configuration Recommended Application:CK410 compliant clock Output Features:? 2 - 0.7V current-mode differential CPU pairs ? 1 - 0.7V current-mode differential SRC pair ? 6 - PCI (33MHz)? 3 - PCICLK_F , (33MHz) free-running ? 1 - USB, 48MHz ? 1 - 24/48 MHz ? 1 - DOT, 96MHz, 0.7V current differential pair ? 2 - REF , 14.318MHz ? 5 - PCI-Express 0.7V current differential pairs Key Specifications:?CPU/SRC outputs cycle-cycle jitter < 85ps ?PCI outputs cycle-cycle jitter < 250ps ?+/- 300ppm frequency accuracy on CPU & SRC clocks Programmable Timing Control Hub? for Next Gen P 4? processor Functionality Features/Benefits:?Programmable output frequencies ?Programmable output skew.?Programmable spread percentage for EMI control.?Programmable watch dog safe frequency.?Supports tight ppm accuracy clocks for Serial-ATA ?Supports spread spectrum modulation, 0 to -0.5% down spread, ±0.25% center spread, and ±0.3%center spread ?Uses external 14.318MHz crystal, external crystal load caps are required for frequency tuning ? Supports undriven differential CPU, SRC pair in PD#for power management. GND 156VDDPCI PCICLK3255PCICLK2PCICLK4354PCICLK1PCICLK5 453PCICLK0GND 552Reset# VDDPCI 651REF0/FS L C PCICLK_F0750REF1FS L A/PCICLK_F1849GND FS L B/PCICLK_F2 948X1VDD48 1047X2 **SEL24_48#/24_48MHz 1146VDDREF USB_48MHz 1245SCLK GND 1344SDATA DOTT_ 96MHz 1443CPUCLKT0DOTC_96MHz 1542CPUCLKC0Vtt_PwrGd#/PD 1641VDDCPU PCIEXT01740CPUCLKT1PCIEXC01839CPUCLKC1VDDPCIEX 1938GND GND 2037IREF PCIEXT12136GNDA PCIEXC12235VDDA PCIEXT22334VDDPCIEX PCIEXC2 2433PCIEXT4GND 2532PCIEXC4SRCCLKT 2631PCIEXT3SRCCLKC 2730PCIEXC3VDDSRC 2829GND I C S 954119 56-Pin SSOP * Internal Pull-Up Resistor

单片机 课程设计报告 课程名称单片机课程设计 专业电气工程及其自动化班级 姓名 学号 指导教师 2012年3 月9 日

DS12887日历时钟课程设计 目录 一前言.............................................................................................. 4 1.1 设计任务及要求........................................................................ 4 1.2 设计应用意义............................................................................ 4 二方案的论证................................................................................. 4 三总体设计..................................................................................... 4 3.1基本工作原理.................................................................................. 4 3.2、硬件总体设计............................................................................... 5 3.3、软件总体设计.............................................................................. 5 四硬件设计................................................................................... 5

51单片机第二十三课实时时钟芯片DS1302的读写 所属类别:课程代码发布日期:2011-03-05 点击量:385 #include

解读无时钟芯片技术 本文作者:大宝 英特尔每推出一颗芯片,除了标出价格外,还会亮出另一个更重要指标,这就是时 钟速度。英特尔总是将芯片速度作为最大的市场卖点,对种种“功能过剩”的预言置若 罔闻,坚持不懈地推出速度越来越快的芯片,从而稳坐芯片制造业头把交椅。与此同时,时钟速度还在芯片设计工程师们的工作起着至关重要的作用,因为他们考虑的第一件事情,就是如何在下一次“钟摆”(Clock Tick)之前,将某项任务执行完毕。所以, 对大多数芯片设计师来说,没有时钟是不可思议的。 但是,美国硅谷的一些新兴公司、大学和企业实验室却正在从事一种无时钟芯片(Clockless Chip)的研发,对这里的研究人员而言,时钟速度和时钟都不重要。他们的 信念是,带时钟的芯片已经山穷水尽,而这种又名“异步设计”或“自计时电路”(Se lf-timed Circuit)的芯片却有不同凡响之处。他们深信,芯片业除了最终接受它之外 ,将别无选择。 其实,传统芯片设计师已经发现,随着系统变得越来越复杂,用时钟来统领整个系 统已变得越来越困难。现在的芯片时钟需要协调几百万个晶体管的工作,因此随着芯片的复杂化,时钟自身消耗的能量在芯片的全部能耗中所占的比例越来越大。 异步(无时钟)芯片放弃时钟,省却了这一部分能耗,从而拥有了很多优势。其中 之一是它大大地提高了电能利用效率,直接延长了电池寿命。此外它还具有计算速度方面的优势。在Sun、英特尔和IBM等公司的实验室里,无时钟芯片提高了高端处理器的工作速度。英特尔在1997年开发了一颗与奔腾系统兼容的异步测试芯片,其运行速度是同等同步芯片的三倍,而能耗却只有后者的一半。硅谷新兴公司特修斯逻辑(Theseus Lo gic)公司的创始人和首席技术官卡尔·范特还发现并关注着异步芯片的另一大优势:由 于这些芯片不像带时钟的电路那样,有规律地发出时间信号,所以它们能执行一种更加难以辨识和攻破的加密算法。加密性的提高,将使异步芯片成为智能卡的当然之选。 那么,无时钟芯片的拥护者们是不是走对了路呢?坦率地说,答案是肯定的。只不过,尽管这种技术的优势是显而易见的,但无时钟芯片在更大程度上还停留在理论层面上,至今尚未步入实用阶段。 一条早年放弃的路线 早在1946年,现代计算机技术的创始者们就考虑过异步设计。不过这些早期的计算 机工程师还是选择了时钟。因为在他们当时的设计环境里,使用的是真空管和中继电路,没有时钟来控制全局,就无法开发出可靠的计算机。而通过使用时钟,工程师们可以找到一种防故障的方法,即使在部件不可靠的情况下,也能保证计算机的稳定可靠。 做了这种选择后,产生了摩尔定律,带来了开天辟地的效应,使得半导体业里的所 有研究、开发和生产活动都将目光集中到带时钟的芯片上。到20世纪60年代,除了在从大学里冒出的一、两篇深奥论文中还有一点身影之外,无时钟芯片的概念基本上消失了。因此,在今天的芯片中,时钟仍然是一个关键部分。在这些芯片中,当微处理器执行指定的操作时,电子信号沿着细微的金属线路前进-分流、交汇、进入逻辑门-直到最后将结果积存到叫做寄存器的临时内存条中。在计算过程中,寄存器里的值是变化的。这是因为执行某操作的信号在到达寄存器之前,沿着不同的路径行进,只有全部信号都走完了自己的路程后,寄存器才将正确的值确定下来。时钟的作用就是保证在指定的时间内得出结果。这样设计出来的芯片能保证电路中最慢的那条路径(线路最长、逻辑门路最多的路径)中的信号在一次钟摆内到达寄存器。 有中央时钟来控制操作,工程师就无需担心几百万条无穷小线路的长度不等了。信 号也可以按任意次序到达寄存器,只要在时钟进行下一次摆动之前全部到达寄存器即可

以DS1302实时时钟芯片和液晶显示屏CD1602为基础设计的电子钟

实验目的: 1、能够以DS1302实时时钟芯片和液晶显示屏CD1602为基础设计一款电子钟 2、熟悉DS1302芯片的工作过程 3、熟悉CD1602芯片的工作过程 4、可以进行必要的扩展,如用第三DS18B20新品进行温度采集和显示 5、熟悉掌握51的c程序的编写 6、掌握用Proteus进行系统设计仿真验证 实验仪器、仪表目录 1、DS1302实时时钟芯片1片 2、LCD1602液晶显示屏1个, 3、80C52芯片1片 5、DS18B20芯片一片 6、晶振、电容、电阻、开关各若干等 7、proteus仿真软件 8、KeilC51、PC机 实验设计任务 以DS1302实时时钟芯片和液晶显示屏LCD1602为基础设计一个电子钟,要求:时间和日期可调整,按键采用3个按键;至少在Proteus上调试通过。扩展:闹钟和重要日期提醒功能(增加蜂鸣器),闹铃音乐功能

实验步骤 1、打开Keil软件,新建一个工程文件,选择好芯片,并记得在“OptionsforTarget1”的Output 选项中,将CreateHEXFil选项勾起来。 2、将编写的程序保存成“.C”的形式 3、编译保存好的C文件,并根据提示修改程序中的错误,直到编译成功为止 4、打开proteus软件,画出实验电路图 5、在89C52中,载入原来已生成的HEX文档 6、按下运行键,对Proteus进行软件仿真,观察运行结果 原理、结果及分析 一、设计方案原理与设计特点分析 电子钟总的设计模块: 1、DS1302时钟采集模块: 1.1电路原理图: 1.2DS1302分析: 首先DS1302是DALLAS公司推出的涓流充电时钟芯片。内含有一个实时时钟/日历和31字节静态RAM通过简单的串行接口与单片机进行通信实时时钟/日历电路提供秒分时日日期月年的信息每月的天数和闰年的天数可自动调整时钟操作。 DS1302芯片广脚介绍:X1、X2为32.768KHz晶振管脚。GND为地。RST复位脚。I/O