PCB零件封装的创建 孙海峰零件封装是安装半导体集成电路芯片的外壳,主要起到安装、固定、密封、保护芯片和增强电热性能的作用,它是芯片内部电路与外部电路的桥梁。随着电子技术飞速发展,集成电路封装技术也越来越先进,使得芯片内部电路越来越复杂的情况下,芯片性能不但没受影响,反而越来越强。 在Cadence软件中,设计者要将绘制好的原理图正确完整的导入PCB Editor 中,并对电路板进行布局布线,就必须首先确定原理图中每个元件符号都有相应的零件封装(PCB Footprint)。虽然软件自带强大的元件及封装库,但对于设计者而言,往往都需要设计自己的元件库和对应的零件封装库。在Cadence中主要使用Allegro Package封装编辑器来创建和编辑新的零件封装。 一、进入封装编辑器 要创建和编辑零件封装,先要进入Allegro Package封装编辑器界面,步骤如下: 1、执行“开始/Cadence/Release 16.3/PCB Editor”命令,弹出产品选择对话框,如下图, 点击Allegro PCB Design GXL即可进入PCB设计。 2、在PCB设计系统中,执行File/New将弹出New Drawing对话框如下图, 该对话框中,在Drawing Name中填入新建设计名称,并可点击后面Browse 改变设计存储路径;在Template栏中可选择所需设计模板;在Drawing Type 栏中,选择设计的类型。这里可以用以设计电路板(Board)、创建模型(Module),还可以用以创建以下各类封装: (1)封装符号(Package Symbol) 一般元件的封装符号, 后缀名为*.psm。PCB 中所有元件像电阻、电容、电感、IC 等的封装类型都是Package Symbol; (2)机械符号(Mechanical Symbol) 由板外框及螺丝孔所组成的机构符号, 后缀名为*.bsm。有时设计PCB 的外框及螺丝孔位置都是一样的, 比如显卡, 电脑主板, 每次设计PCB时要画一次板外框及确定螺丝孔位置, 显得较麻烦。这时我们可以将PCB的外框及螺丝孔建

Allegro元件封装(焊盘)制作方法总结 ARM+Linux底层驱动 2009-02-27 21:00 阅读77 评论0 字号:大中小 https://www.doczj.com/doc/311014997.html,/html/PCBjishu/2008/0805/3289.html 在Allegro系统中,建立一个零件(Symbol)之前,必须先建立零件的管脚(Pin)。元件封装大体上分两种,表贴和直插。针对不同的封装,需要制 作不同的Padstack。 Allegro中Padstack主要包括以下部分。 1、PAD即元件的物理焊盘 pad有三种: 1. Regular Pad,规则焊盘(正片中)。可以是:Circle 圆型、S quare 方型、Oblong 拉长圆型、Rectangle 矩型、Octagon 八 边型、Shape形状(可以是任意形状)。 2. Thermal relief 热风焊盘(正负片中都可能存在)。可以是: Null(没有)、Circle 圆型、Square 方型、Oblong 拉长圆型、 Rectangle 矩型、Octagon 八边型、flash形状(可以是任意形 状)。 3. Anti pad 抗电边距(负片中使用),用于防止管脚与其他的网 络相连。可以是:Null(没有)、Circle 圆型、Square 方型、 Oblong 拉长圆型、Rectangle 矩型、Octagon 八边型、Shape形 状(可以是任意形状)。 2、SOLDERMASK:阻焊层,使铜箔裸露而可以镀涂。 3、PASTEMASK:胶贴或钢网。 4、FILMMASK:预留层,用于添加用户需要添加的相应信息,根据需要使用。 表贴元件的封装焊盘,需要设置的层面及尺寸: Regular Pad: 具体尺寸根据实际封装的大小进行相应调整后得到。推荐使用《IPC-SM-78 2A Surface Mount Design and Land Pattern Standard》中推荐的尺寸进行尺寸设计。同时推荐使用IPC-7351A LP Viewer。该软件包括目前常用的大多数S

Cadence 封装尺寸总结 1、 表贴IC a )焊盘 表贴IC 的焊盘取决于四个参数:脚趾长度W ,脚趾宽度Z ,脚趾指尖与芯片中心的距离D ,引脚间距P ,如下图: 焊盘尺寸及位置计算:X=W+48 S=D+24 Y=P/2+1,当P<=26mil 时 Y=Z+8,当P>26mil 时 b )silkscreen 丝印框与引脚内边间距>=10mil ,线宽6mil ,矩形即可。对于sop 等两侧引脚的封装,长度边界取IC 的非引脚边界即可。丝印框内靠近第一脚打点标记,丝印框外,第一脚附近打点标记,打点线宽视元件大小而定,合适即可。对于QFP 和BGA 封装(引脚在芯片底部的封装),一般在丝印框上切角表示第一脚的位置。 c )place bound 该区域是为防止元件重叠而设置的,大小可取元件焊盘外边缘以及元件体外侧+20mil 即可,线宽不用设置,矩形即可。即,沿元件体以及元件焊盘的外侧画一矩形,然后将矩形的长宽分别+20mil 。 d )assembly 该区域可比silkscreen 小10mil ,线宽不用设置,矩形即可。对于外形不规则的器件,assembly 指的是器件体的区域(一般也是矩形),切不可粗略的以一个几乎覆盖整个封装区域的矩形代替。 PS :对于比较确定的封装类型,可应用LP Wizard 来计算详细的焊盘尺寸和位置,再得到焊盘尺寸和位置的同时还会得到silkscreen 和place bound 的相关数据,对于后两个数据,可以采纳,也可以不采纳。

2、通孔IC a)焊盘 对于通孔元件,需要设置常规焊盘,热焊盘,阻焊盘,最好把begin层,internal层,bottom 层都设置好上述三种焊盘。因为顶层和底层也可能是阴片,也可能被作为内层使用。 通孔直径:比针脚直径大8-20mil,通常可取10mil。 常规焊盘直径:一般要求常规焊盘宽度不得小于10mil,通常可取比通孔直径大20mil (此时常规焊盘的大小正好和花焊盘的内径相同)。这个数值可变,通孔大则大些,比如+20mil,通孔小则小些,比如+12mil。 花焊盘直径:花焊盘内径一般比通孔直径大20mil。花焊盘外径一般比常规焊盘大20mil (如果常规焊盘取比通孔大20mil,则花焊盘外径比花焊盘内径大20mil)。这两个数值也是可以变化的,依据通孔大小灵活选择,通孔小时可取+10-12mil。 阻焊盘直径:一般比常规焊盘大20mil,即应该与花焊盘外径一致。这个数值也可以根据通孔大小调整为+10-12mil。注意需要与花盘外径一致。 对于插件IC,第一引脚的TOP(begin)焊盘需要设置成方形。 b) Silkscreen 与表贴IC的画法相同。 c) Place bound 与表贴IC的画法相同。 d) Assembly 与表贴IC的画法相同。 3、表贴分立元件 分立元件一般包括电阻、电容、电感、二极管、三极管等。 对于贴片分立元件,封装规则如下: a)焊盘 表贴分立元件,主要对于电阻电容,焊盘尺寸计算如下:

1. Allegro 零件库封装制作的流程步骤。 2. 规则形状的smd 焊盘制作方法。 3. 表贴元件封装制作方法。 4. 0805贴片电容的封装制作实例。 先创建焊盘,再创建封装 一、先制作焊盘 制作焊盘软件路径:candence\Release 16.6\PCB Editor Utilities\Pad Designer Pad Designer 界面 solderMask_top 比其它层大0.1mm,焊盘数据可以用复制、粘贴来完成。 当前层

Null:空; Circle:圆形; Square: 正方形; Oblong:椭圆形; Rectangle:长方形; Octagon: 八边形; Shape:形状; 封装制作完成后,选择路径,命名后进行保存Rect_x1_15y1_45 二、制作封装 操作步骤:打开Allegro 软件(allegro PCB design GXL ) file(new) OK 进入零件封装编辑界面。 设置图纸的尺寸(元件尺寸太小,所以图纸的尺寸也要设置小) 单位:毫米 X \Y:坐标原点绝对坐标设置 精度: 4 封装类型 线(机械)设置 栅格点设置,setup--Grid

第20讲 一、正式绘制元件封装 操作步骤: layout Pins 如果要把焊盘放在原点(0,0),选择好焊盘后,在命令(command )行输入x 0 0 ,然后回车,这样焊盘就自动跳到坐标原点(0,0)上啦。 二、盘放置好后,绘制零件的框。步骤如下: Add Line 输入坐标的方式输入,用命令(command )输入 如下图 表示具有电气连接的焊盘 表示没有电气连接的焊盘或引脚 选择路径,找到需要的焊盘 Rectangular:焊盘直线排列 Polar:焊盘弧形排列 Qty:表示直线排列数量; Spacing:两个焊盘中心 点之间的距离; Order:排列方向 旋转角度 Pin#:焊盘编号1 Inc:表示增量为1 Text block:表示字符的大小 OffsetX:表示字符放在焊盘中心 Class 与subclass 要选好 单独显示这一层的效果

Cadence封装制作实例 这是因为本人现在在学习PCB layout,而网上没有很多的实例来讲解,如果有大师愿意教我那有多好啊,嘿嘿!这里本人把学习cadence封装后的方法通过实例给其他的初学者更好的理解,因为本人也是初学者,不足或错误的地方请包涵,谢谢! 一. M12_8芯航空插座封装制作 1.阅读M12_8芯航空插座的Datasheet了解相关参数; 根据Datasheet可知: a.航空插座的通孔焊盘Drill尺寸为 1.2mm≈50mil,我们可以设计其焊盘为 P65C50(焊盘设计会涉及到); b.航空插座的直径为 5.5mm=21 6.53mil,以5.5/2mm为半径; 2.根据参数设计该航空插座的焊盘; a.已知钻孔直径Drill_size≈50mil可知:Regular Pad=Drill_size+16mil 通孔焊盘尺寸计算规则: 设元器件直插引脚直径为M,则 1)钻孔直径Drill_size=M+12mil,M≤40

=M+16mil,40<M≤80 =M+20mil,M>80 2)规则焊盘Regular Pad=Drill_size+16mil,Drill_size<50mil =Drill_size+30mil,Drill_size≥50mil =Drill_size+40mil,Drill_size为矩形或椭圆形 3)阻焊盘Anti-Pad=Regular Pad+20mil 4)热风焊盘Drill_size<10mil,内径ID=Drill_size+10mil,外径 OD=Drill_size+20mil; Drill_size>10mil,内径ID= Drill_size+20mil 外径OD= Regular Pad+20mil = Drill_size+36mil,Drill_size<50mil = Drill_size+50mil,Drill_size≥50mil = Drill_size+60mil,Drill_size为矩形或椭圆b.按照通孔焊盘计算方式我们命名为P65C50,打开Pad_Designer; File\NEW,点击Browse,选择文件所放路径,新建P65C50.pad文件 新建好文件后,设置相关参数:

Cadence Allegro元件封装制作流程 1.引言 一个元件封装的制作过程如下图所示。简单来说,首先用户需要制作自己的焊盘库Pads,包括普通焊盘形状Shape Symbol和花焊盘形状Flash Symbol;然后根据元件的引脚Pins选择合适的焊盘;接着选择合适的位置放置焊盘,再放置封装各层的外形(如Assembly_Top、Silkscreen_Top、Place_Bound_Top等),添加各层的标示符Labels,还可以设定元件的高度Height,从而最终完成一个元件封装的制作。 下面将分表贴分立元件,通孔分立元件,表贴IC及通孔IC四个方面来详细分述元件封装的制作流程。 2.表贴分立元件 分立元件一般包括电阻、电容、电感、二极管、三极管等。 对于贴片分立元件,以0805封装为例,其封装制作流程如下: 2.1.焊盘设计 2.1.1.尺寸计算 表贴分立元件,主要对于电阻电容,焊盘尺寸计算如下:

其中,K 为元件引脚宽度,H 为元件引脚高度,W 为引脚长度,P 为两引脚之间距离(边距离,非中心距离),L 为元件长度。X 为焊盘长度,Y 为焊盘宽度,R 为焊盘间边距离,G 为封装总长度。则封装的各尺寸可按下述规则: 1) X=Wmax+2/3*Hmax+8 mil 2) Y=L ,当L<50 mil ;Y=L+ (6~10) mil ,当L>=50 mil 时 3) R=P-8=L-2*Wmax-8 mil ;或者G=L+X 。这两条选一个即可。个人觉得后者更容易理 解,相当于元件引脚外边沿处于焊盘中点,这在元件尺寸较小时很适合(尤其是当Wmax 标得不准时,第一个原则对封装影响很大),但若元件尺寸较大(比如说钽电容的封装)则会使得焊盘间距过大,不利于机器焊接,这时候就可以选用第一条原则。本文介绍中统一使用第二个。 注:实际选择尺寸时多选用整数值,如果手工焊接,尺寸多或少几个mil 影响均不大,可视具体情况自由选择;若是机器焊接,最好联系工厂得到其推荐的尺寸。例如需要紧凑的封装则可以选择小一点尺寸;反之亦然。 另外,还有以下三种方法可以得到PCB 的封装尺寸: ◆ 通过LP Wizard 等软件来获得符合IPC 标准的焊盘数据。 ◆ 直接使用IPC-SM-782A 协议上的封装数据(据初步了解,协议上的尺寸一般偏大)。 ◆ 如果是机器焊接,可以直接联系厂商给出推荐的封装尺寸。 2.1.2. 焊盘制作 Cadence 制作焊盘的工具为Pad_designer 。 打开后选上Single layer mode ,填写以下三个层: 1) 顶层(BEGIN LAYER ):选矩形,长宽为X*Y ; 2) 阻焊层(SOLDERMASK_TOP ):是为了把焊盘露出来用的,也就是通常说的绿油层 实际上就是在绿油层上挖孔,把焊盘等不需要绿油盖住的地方露出来。其大小为Solder Mask=Regular Pad+4~20 mil (随着焊盘尺寸增大,该值可酌情增大),包括X 和Y 。 3) 助焊层(PASTEMASK_TOP ):业内俗称“钢网”或“钢板”。这一层并不存在于印制板上, 而是单独的一张钢网,上面有SMD 焊盘的位置上镂空。这张钢网是在SMD 自动装配焊接工艺中,用来在SMD 焊盘上涂锡浆膏用的。其大小一般与SMD 焊盘一样,尺寸略小。 其他层可以不考虑。 侧视图 底视图 封装底视图 K H K P X R Y W G L

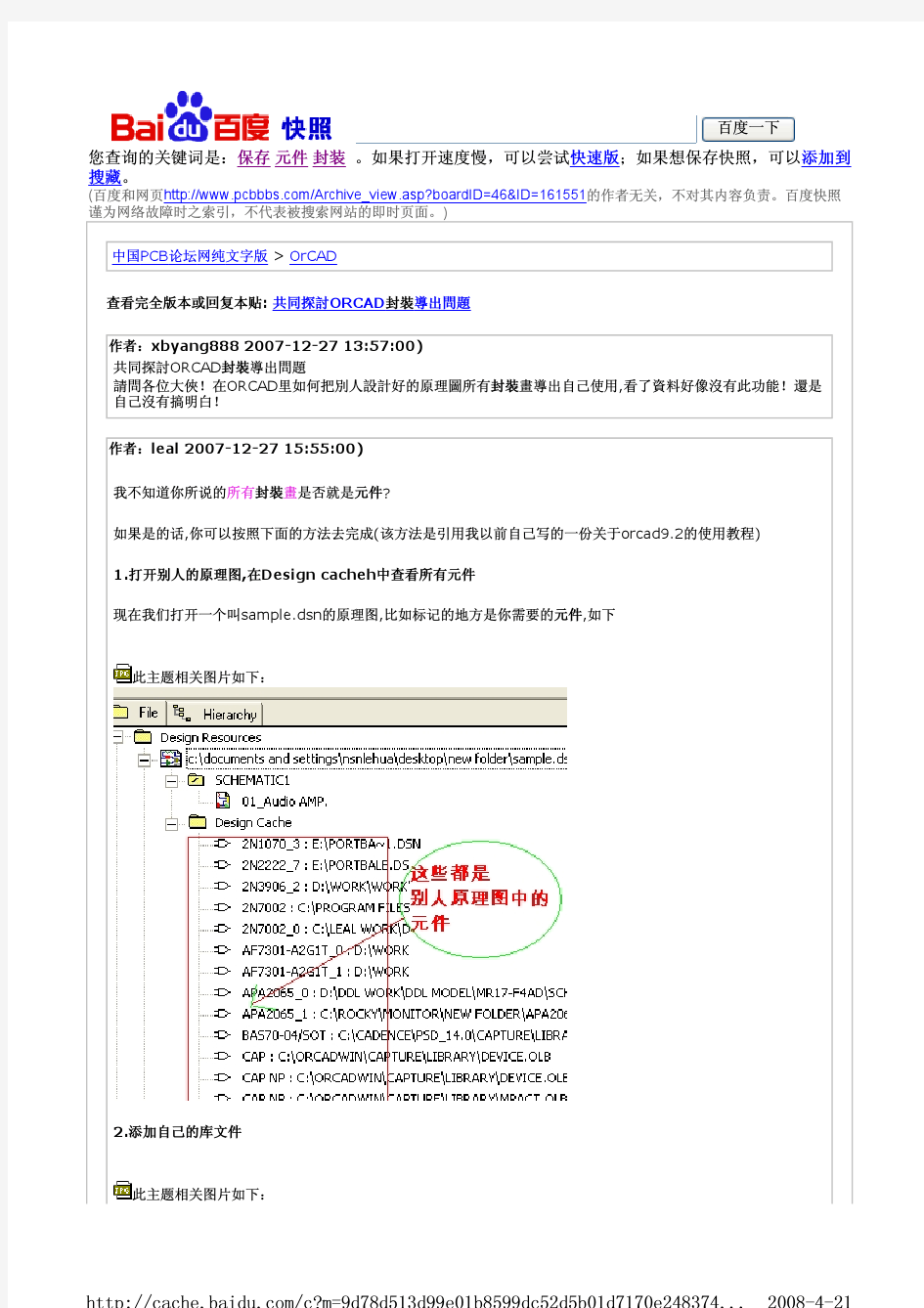

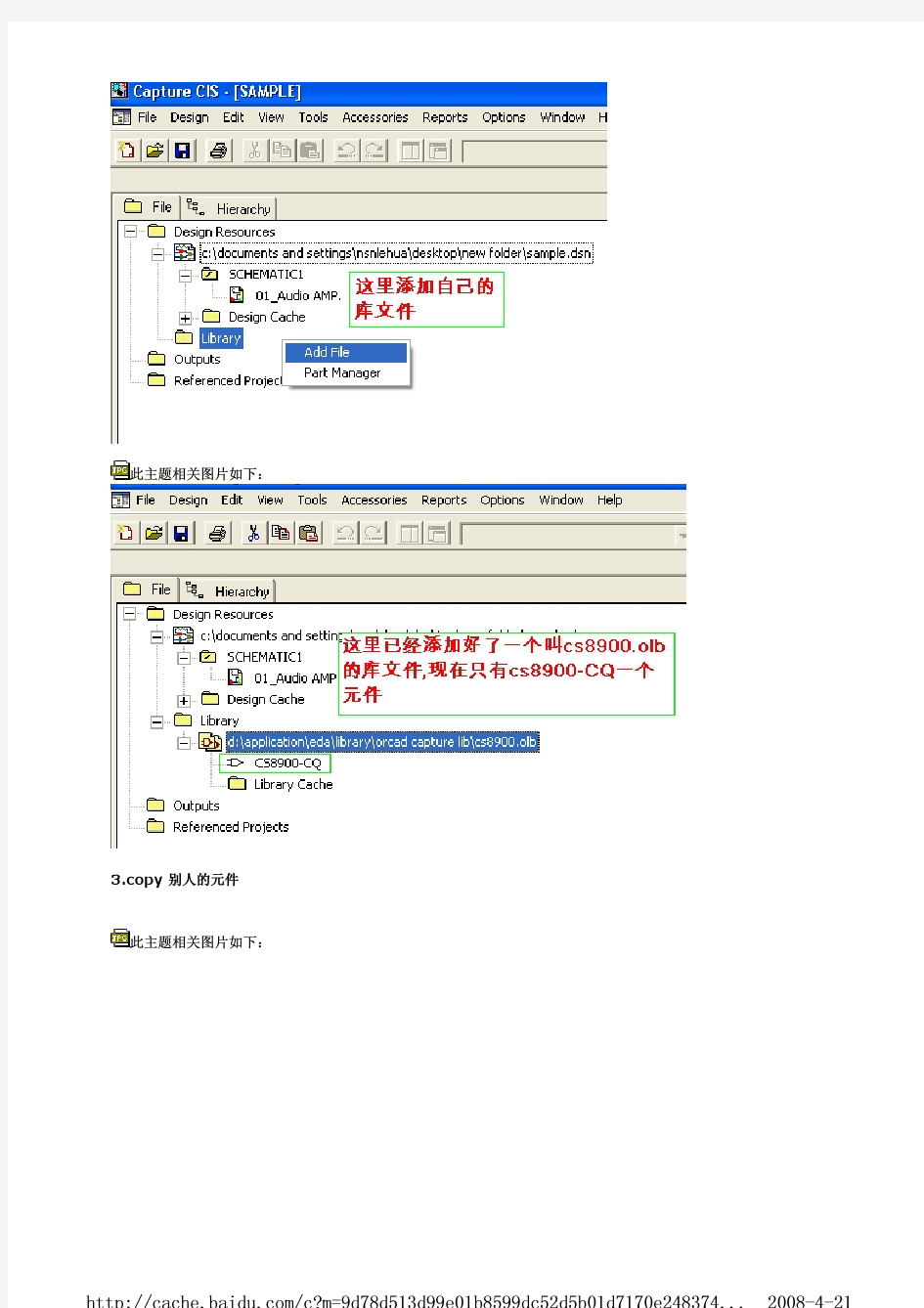

Cadence总结 一、Capture设计过程 二、新建Project(create a design project) Capture的Project是用来管理相关文件及属性的。新建Project的同时,Capture会自动创建相关的文件,如DSN、OPJ文件等,根据创建的Project类型的不同,生成的文件也不尽相同。 根据不同后续处理的要求,新建Project时必须选择相应的类型。Capture支持四种不同的Project类型。 1、创建工程 首先启动OrCAD CaptureCIS选design entry CIS,如图 然后启动后弹出对话框,对话窗中有很多程序组件,不要选OrCAD Capture,这个组件和OrCAD Capture CIS相比少了很多东西,对元件的管理不方便。选OrCAD Capture CIS,如图:

打开程序界面,这时界面中是空的,只有左下角有一个session log最小化窗口。现在我们可以开始建立工程project。选主菜单file->new->project,弹出project wizard对话框,如图: 在这里选择要建立的工程的类型。因为我们要用它进行原理图设计,所以选schematic 选项。在name对话框中为你的工程起一个名字,最好由清一色的小写字母及数字组成,别加其他符号,如myproject。下面location对话框是你的工程放置在那个文件夹,可以用右边的browse按钮选择位置或在某个位置建立新的文件夹, 在程序主界面走侧的工程管理框中会出现和工程同名的数据库文件。Myproject.dsn是数据库文件,下面包括SCHEMA TIC1和design cache两个文件夹。SCHEMATIC1文件夹中存放原理图的各个页面。当原理图界面上放置元件后,design cache文件夹下会出现该元件的名字路径等信息,这时数据库中的元件缓存,该功能使设计非常方便, 2、工程管理器介绍 界面左侧是工程管理器,用于管理设计中用到的所有资源。包含两个标签File和

第六章Cadence PCB封装库的制作及使用 封装库是进行PCB设计时使用的元件图形库,本章主要介绍使用Cadence 软件进行PCB封装库制作的方法及封装库的使用方法。 一、创建焊盘 在设计中,每个器件的封装引脚都是由与之相关的焊盘构成的,焊盘描述了器件引脚如何与设计中所涉及的每个物理层发生关系,每个焊盘包含以下信息: ●焊盘尺寸大小和焊盘形状; ●钻孔尺寸和显示符号。 焊盘还描述了引脚在表层(顶层和底层)的SOLDERMASK、PASTEMASK 和FILMMASK等相关信息。同时,焊盘还包含有数控钻孔数据,Allegro用此数据产生钻孔符号和钻带文件。 1.焊盘设计器 Allegro在创建器件封装前必须先建立焊盘,建立的焊盘放在焊盘库里,在做器件封装时从焊盘库里调用。Allegro创建的焊盘文件名后缀为.pad。Allegro 用Pad Designer创建并编辑焊盘。 在Allegro中,一个器件封装的每个引脚必须有一个与之相联系的焊盘名。在创建器件封装时,将引脚添加到所画的封装中。在添加每一个引脚时,Allegro 找到库中的焊盘,将焊盘的定义拷贝到封装图中,并显示焊盘的图示。基于这个原因,必须在创建器件封装前先设计出库中要用到的焊盘。 在创建器件封装符号时,Allegro存储每一个引脚对应的焊盘名而不是焊盘数据,在将器件封装符号加到设计中时,Allegro从焊盘库拷贝焊盘数据,同时从器件封装库拷贝器件封装数据。 Allegro用在全局或本地环境文件定义的焊盘库路径指针(PADPATH)和器件封装库路径指针(PSMPATH)查找焊盘库和器件封装库。一旦一个焊盘在某个设计中出现一次,Allegro使其他所有相同的焊盘参考于那个焊盘而不是参考库中的焊盘。 有两种方法可以启动焊盘设计器:1、选择【开始】/【程序】/【Cadence SPB 16.6】/【PCB Editor Utilities】/【Pad Designer】命令,即可启动焊盘设计器;2、按照前面章节所述,创建一个库项目,库项目界面如图6_1所示,点击界面中的“Pad Stack Editor”按钮,也可以启动焊盘设计器。焊盘设计器界面如图6_2所示。

Cadence 使用及注意事项 目录 1 PCB工艺规则...................................................................................... 错误!未定义书签。 2 Cadence的软件模块 .......................................................................... 错误!未定义书签。 Cadence的软件模块--- Pad Designer ............................................. 错误!未定义书签。 Pad的制作....................................................................................... 错误!未定义书签。 PAD物理焊盘介绍 .......................................................................... 错误!未定义书签。 3 Allegro中元件封装的制作................................................................. 错误!未定义书签。 PCB 元件(Symbol)必要的CLASS/SUBCLASS ................................. 错误!未定义书签。 PCB 元件(Symbol)位号的常用定义 ............................................... 错误!未定义书签。 PCB 元件(Symbol)字符的字号和尺寸 ......................................... 错误!未定义书签。 根据Allegro Board (wizard)向导制作元件封装........................... 错误!未定义书签。 制作symbol时常遇见的问题及解决方法 .................................... 错误!未定义书签。 4 Cadence易见错误总结 ...................................................................... 错误!未定义书签。 1 PCB工艺规则 以下规则可能随中国国内加工工艺提高而变化 (1)不同元件间的焊盘间隙:大于等于40mil(1mm),以保证各种批量在线焊板的需要。 (2)焊盘尺寸:粘锡部分的宽度保证大于等于10mil,如果焊脚(pin)较高,应修剪;如果不能修剪的,相应焊盘应增大….. (3)机械过孔最小孔径:大于等于6mil。小于此尺寸将使用激光打孔,为国内大多数PCB厂家所不能接受。 (4)最小线宽和线间距:大于等于4mil。小于此尺寸,为国内大多数PCB 厂家所不能接受,并且不能保证成品率! (5)PCB 板厚:通常指成品板厚度,常见的是:、1mm、、、;材质为FR-4。当然也有其它类型的,比如:陶瓷基板的… (6)丝印字符尺寸:高度大于30mil,线条宽大于6mil,高与宽比例3:2 (7)最小孔径与板厚关系:目前国内加工能力为:板厚是最小孔径的8~15倍,大多数多层板PCB 厂家是:8~10倍。举例:假如板内最小孔径(如:VIA)6mil,那么你不能要求厂家给你做厚的PCB 板,但可以要求或以下的。 (8)定位基准点:用于给贴片机、插件机等自动设备取基准点,用20mil直径的表贴实心圆盘(需要被SOLDERMASK,以便铜裸露或镀锡而反光)。分布于顶层(TOP) 的板边对脚线、底层(BOTTOM)的板边对脚线,

建立元件封装 总起来说,元件封装制作步骤: ◆添加管脚,可用 x 0 0 命令来定义第一个点的位置; ◆添加装配外形,设置栅格25mil,选择ADD->Line class和subclass 为 PACKAGE GEOMETRY/ASSEMBLY_TOP; 添加丝印 class/subclass为PACKAGE GEOMETRY/SILKSCREEN_TOP; ◆添加标号RefDes class和subclass 为 REFDES/ASSEMBLY_TOP;输入U*;放在器件的中央; class和subclass 为 Device Type/ASSEMBLY_TOP;输入DEV;放在器件的中央; class和subclass 为 REFDES/SILKSCREEN_TOP;输入U*;放在器件的上侧中央; class和subclass 为 Device Type/SILKSCREEN_TOP;输入DEV;放在器件的上侧中央; ◆生成封装边界,点击SHAPE ADD;画出封装的边界。可以检测器件没有放重叠; class和subclass 为 PACKAGE GEOMETRY/PLACE_BOUND_TOP; ◆定义封装高度(可以选择) 选择Setup->Areas->Package Boundary Height; class和subclass 为 PACKAGE GEOMETRY/PLACE_BOUND_TOP; 点击刚才画的封装边界,输入高度; ◆添加测试点不能添加的区域(可以选择),点击SHAPE ADD;添加阻止测试点放置的区域; class和subclass 为 Manufacturing/No_Probe_TOP; 详细过程如下所示: 1、打开程序Cadence SPB 16.2 PCB Editor,File—New打开新建对话框。 在Drawing Type选择Package symbol,然后点击Browse,浏览选择保存路径并填写文件名字。

Cad ence Allegro 封装尺寸总结 1、 表贴IC a )焊盘 表贴IC 的焊盘取决于四个参数:脚趾长度W ,脚趾宽度Z ,脚趾指尖与芯片中心的距离D ,引脚间距P ,如下图: 焊盘尺寸及位置计算:X=W+48 S=D+24 Y=P/2+1,当P<=26mil 时 Y=Z+8,当P>26mil 时 b )silkscreen 丝印框与引脚内边间距>=10mil ,线宽6mil ,矩形即可。对于sop 等两侧引脚的封装,长度边界取IC 的非引脚边界即可。丝印框内靠近第一脚打点标记,丝印框外,第一脚附近打点标记,打点线宽视元件大小而定,合适即可。对于QFP 和BGA 封装(引脚在芯片底部的封装),一般在丝印框上切角表示第一脚的位置。 c )place bound 该区域是为防止元件重叠而设置的,大小可取元件焊盘外边缘以及元件体外侧+20mil 即可,线宽不用设置,矩形即可。即,沿元件体以及元件焊盘的外侧画一矩形,然后将矩形的长宽分别+20mil 。 d )assembly 该区域可比silkscreen 小10mil ,线宽不用设置,矩形即可。对于外形不规则的器件,assembly 指的是器件体的区域(一般也是矩形),切不可粗略的以一个几乎覆盖整个封装区域的矩形代替。 PS :对于比较确定的封装类型,可应用LP Wizard 来计算详细的焊盘尺寸和位置,再得到焊盘尺寸和位置的同时还会得到silkscreen 和place bound 的相关数据,对于后两个数据,可以采纳,也可以不采纳。

2、通孔IC a)焊盘 对于通孔元件,需要设置常规焊盘,热焊盘,阻焊盘,最好把begin层,internal层,bottom 层都设置好上述三种焊盘。因为顶层和底层也可能是阴片,也可能被作为内层使用。 通孔直径:比针脚直径大8-20mil,通常可取10mil。 常规焊盘直径:一般要求常规焊盘宽度不得小于10mil,通常可取比通孔直径大20mil (此时常规焊盘的大小正好和花焊盘的内径相同)。这个数值可变,通孔大则大些,比如+20mil,通孔小则小些,比如+12mil。 花焊盘直径:花焊盘内径一般比通孔直径大20mil。花焊盘外径一般比常规焊盘大20mil (如果常规焊盘取比通孔大20mil,则花焊盘外径比花焊盘内径大20mil)。这两个数值也是可以变化的,依据通孔大小灵活选择,通孔小时可取+10-12mil。 阻焊盘直径:一般比常规焊盘大20mil,即应该与花焊盘外径一致。这个数值也可以根据通孔大小调整为+10-12mil。注意需要与花盘外径一致。 对于插件IC,第一引脚的TOP(begin)焊盘需要设置成方形。 b) Silkscreen 与表贴IC的画法相同。 c) Place bound 与表贴IC的画法相同。 d) Assembly 与表贴IC的画法相同。 3、表贴分立元件 分立元件一般包括电阻、电容、电感、二极管、三极管等。 对于贴片分立元件,封装规则如下: a)焊盘 表贴分立元件,主要对于电阻电容,焊盘尺寸计算如下:

Cadence学习笔记3__封装 IPC软件计算后导出 下面是STM32F103RCT6(64脚QFP封装)数据手册的封装尺寸: STM32F103xC, STM32F103xD, STM32F103xE Package characteristics Figure 71. LQFP64 – 10 x 10 mm 64 pin low-profile Figure 72. Recommended footprint

然后打开IPC,在Calculate中打开SMD Calculator,选择QFP封装,双击或者点击ok,出现计算界面,如下图: 此时在左侧窗口填上相应的数据,然后光标停在任意一个数据中回车,就可以计算出其余的尺寸了。注意到这里的单位是毫米Millimeters,所以应该对应数据手册中的毫米而不是英尺。Pitch(P)在图中是引脚中心的间距,对应于数据手册中的e,值为0.5。A和B分别是两个方向上的引脚数量,都是16,下面给出了提示,如果是矩形芯片的话,A应该小于B。Pin Count(for search)是引脚总数,填64。L1和L2表示包括引脚的芯片宽度和长度,对应芯片手册的D和E,最小值是11.8,最大值是12.2。T是引脚长度,对应于数据手册中的L,最小值为0.45,最大值为0.75。W表示焊盘的宽度,对应于数据手册中的b,最小值为0.17,最大值为0.27。A和B表示不包括引脚的芯片宽度和长度,对应芯片手册的D1和E1,最小值为9.8,最大值为10.2。H表示芯片的高度,对应于芯片手册中的A,最大值为1.6,不用填最小值。K表

示芯片离PCB板的高度,对应于芯片手册中的A1,最小值为0.05,不用填最大值。填完之后光标放在任意一个框中回车,就可以计算出其余的数据了。可以看见IPC软件自动给这个封装命名了,打开Land Pattern就可以看到装配边框、丝印边框、Place_Bound_Top等的数据,如下图左。 点击Wizard图标,可以导出这个封装。导出封装前需要进行一些选项设置,可以每次都设置一下,也可以在工具栏“Preferences”里面统一设置一下,点击下面的“Preferences”图标后,会出现一个设置的窗口,在Wizard CAD Tools下面选择自己的工具,这里选择Allegro,对应右边选择软件版本,Version选择16.3,设置好封装的输出路径,其余默认即可。

Cadence 使用及注意事项 1 2 目录 3 1 PCB工艺规则 (1) 2 Cadence的软件模块 (3) 4 5 2.1 Cadence的软件模块--- Pad Designer (4) 6 2.2 Pad的制作 (5) 7 2.2.1 PAD物理焊盘介绍 (6) 8 3 Allegro中元件封装的制作 (9) 9 3.1 PCB 元件(Symbol)必要的 CLASS/SUBCLASS (9) 3.2 PCB 元件(Symbol)位号的常用定义 (13) 10 11 3.3 PCB 元件(Symbol)字符的字号和尺寸 (14) 12 3.4 根据Allegro Board (wizard)向导制作元件封装 (15) 13 3.5 制作symbol时常遇见的问题及解决方法 (23) 14 4 Cadence易见错误总结 (24) 15 16 1 PCB工艺规则 以下规则可能随中国国内加工工艺提高而变化 17 1

(1)不同元件间的焊盘间隙:大于等于 40mil(1mm),以保证各种批量在 18 19 线焊板的需要。 20 (2)焊盘尺寸:粘锡部分的宽度保证大于等于 10mil(0.254mm),如果焊脚(pin)较高,应修剪;如果不能修剪的,相应焊盘应增大….. 21 22 (3)机械过孔最小孔径:大于等于 6mil(0.15mm)。小于此尺寸将使用激23 光打孔,为国内大多数PCB厂家所不能接受。 24 (4)最小线宽和线间距:大于等于 4mil(0.10mm)。小于此尺寸,为国内25 大多数 PCB 厂家所不能接受,并且不能保证成品率! 26 (5)PCB 板厚:通常指成品板厚度,常见的是:0.8mm、1mm、1.2mm、1.6mm、 2.0mm;材质为 FR-4。当然也有其它类型的,比如:陶瓷基板的… 27 28 (6)丝印字符尺寸:高度大于 30mil(0.75mm),线条宽大于 6mil(0.15mm),29 高与宽比例3:2 (7)最小孔径与板厚关系:目前国内加工能力为:板厚是最小孔径的 8~15 30 31 倍,大多数多层板 PCB 厂家是:8~10倍。举例:假如板内最小孔径(如:VIA)32 6mil,那么你不能要求厂家给你做 1.6mm厚的 PCB 板,但可以要求 1.2mm或33 以下的。 34 (8)定位基准点:用于给贴片机、插件机等自动设备取基准点,用35 20mil(0.5mm)直径的表贴实心圆盘(需要被SOLDERMASK,以便铜裸露或镀锡而反光)。分布于顶层(TOP) 的板边对脚线、底层(BOTTOM)的板边对脚线,每面最少 36 37 2 个;另外无引脚封装的贴片元件也需要在 pin1附近放一个(不能被元件遮盖,38 可以在做这些元件封装时做好),这些元件可能是:BGA、LQFN 等…. (9)成品板铜薄厚度:大于等于 35um,强制 PCB 板厂执行,以保证质量! 39 2

Allegro 软件是 Cadence 公司出品的面向中高端企业用户的 PCB 设计软件,主要针对高速、高密度电路板设计,尤其在通讯等领域被广泛应用,目前最新版本号是 16.0。Allegro 软件导出坐标数据步骤. ①Design Entry CIS绘制原理图。 ②*HDL:芯片开发时的扳机设计 ③PCB Editor:PCB板布局布线的工具 ④PCB Router:自动布线的工具。 ⑤PCB SI:电路板完整性仿真。 ⑥ ⑦设置模版Options--Design Template ⑧原理图背景设置,设置跳转:options-preferences ⑨修改原理图属性:options-Schematic page properties ⑩封装的一些设置在:options-user properties 11多个部分的元器件显示在一页:view-package 12---第一个多个模块功能相同 13第二个功能不同 14多个部分之间切换:ctrl+n; 15同时看多个部分:View--package.

16放置期间:place--part 17取消所有标注; 18自动生成编号: 19多个部分冲突,给封装添加一个属性,根据不同修改属性。 20放置的时候,按R按键,可以旋转放置的封装。 21画线快捷键:按W 22画线到了终点(终端悬空),双击,如果单击还会继续画。 23画之前,按住shift按键,可以绘制任意角度的线条。 24删除节点,按住S,才能选中焦点。 25放置网络名字,按n 26总线的命名:名字一定是英文。 27总线和信号线的要求: 28 29连接到其他页。 30浏览工程中用到的软件,选中工程中的dns---菜单edit---browse---parts(可以查看有没有忘记编号那些) 31电气规则检查: 32查看所有网络:dns---edit---browse---nets(双击表格中的网络,可以查看此网络) 33查看页面之间互联的网络:dns---EDIT---browse---off_page(原理图检查非常重要,或者用pans检查也行)。

第六章Cadence PCB封装库的制作及使用封装库是进行PCB设计时使用的元件图形库,本章主要介绍使用Cadence 软件进行PCB封装库制作的方法及封装库的使用方法。 一、创建焊盘 在设计中,每个器件的封装引脚都是由与之相关的焊盘构成的,焊盘描述了器件引脚如何与设计中所涉及的每个物理层发生关系,每个焊盘包含以下信息: ●焊盘尺寸大小和焊盘形状; ●钻孔尺寸和显示符号。 焊盘还描述了引脚在表层(顶层和底层)的SOLDERMASK、PASTEMASK 和FILMMASK等相关信息。同时,焊盘还包含有数控钻孔数据,Allegro用此数据产生钻孔符号和钻带文件。 1.焊盘设计器 Allegro在创建器件封装前必须先建立焊盘,建立的焊盘放在焊盘库里,在做器件封装时从焊盘库里调用。Allegro创建的焊盘文件名后缀为.pad。Allegro用Pad Designer创建并编辑焊盘。 在Allegro中,一个器件封装的每个引脚必须有一个与之相联系的焊盘名。在创建器件封装时,将引脚添加到所画的封装中。在添加每一个引脚时,Allegro 找到库中的焊盘,将焊盘的定义拷贝到封装图中,并显示焊盘的图示。基于这个原因,必须在创建器件封装前先设计出库中要用到的焊盘。 在创建器件封装符号时,Allegro存储每一个引脚对应的焊盘名而不是焊盘数据,在将器件封装符号加到设计中时,Allegro从焊盘库拷贝焊盘数据,同时从器

件封装库拷贝器件封装数据。 Allegro用在全局或本地环境文件定义的焊盘库路径指针(PADPATH)和器件封装库路径指针(PSMPATH)查找焊盘库和器件封装库。一旦一个焊盘在某个设计中出现一次,Allegro使其他所有相同的焊盘参考于那个焊盘而不是参考库中的焊盘。 有两种方法可以启动焊盘设计器:1、选择【开始】/【程序】/【Cadence SPB 15.5.1】/【PCB Editor Utilities】/【Pad Designer】命令,即可启动焊盘设计器;2、按照前面章节所述,创建一个库项目,库项目界面如图6_1所示,点击界面中的“Pad Stack Editor”按钮,也可以启动焊盘设计器。焊盘设计器界面如图6_2所示。 6_1

在Allegro系统中,建立一个零件(Symbol)之前,必须先建立零件的管脚(Pin)。元件封装大体上分两种,表贴和直插。针对不同的封装,需要制作不同的Padstack。 Allegro中Padstack主要包括以下部分。 1、PAD即元件的物理焊盘 pad有三种: Regular Pad,规则焊盘(正片中)。可以是:Circle 圆型、Square 方型、Oblong 拉长圆型、Rectangle 矩型、Octagon 八边型、Shape形状(可以是任意形状)。 Thermal relief热风焊盘(正负片中都可能存在)。可以是:Null(没有)、Circle 圆型、Square 方型、Oblong 拉长圆型、Rectangle 矩型、Octagon 八边型、flash形状(可以是任意形状)。 Anti pad抗电边距(负片中使用),用于防止管脚与其他的网络相连。可以是:Null(没有)、Circle 圆型、Square 方型、Oblong 拉长圆型、Rectangle 矩型、Octagon 八边型、Shape 形状(可以是任意形状)。 2、SOLDERMASK:阻焊层,使铜箔裸露而可以镀涂。 3、PASTEMASK:胶贴或钢网。 4、FILMMASK:预留层,用于添加用户需要添加的相应信息,根据需要使用。 表贴元件的封装焊盘,需要设置的层面及尺寸: Regular Pad: 具体尺寸根据实际封装的大小进行相应调整后得到。推荐使用《IPC-SM-782A Surface Mount Design and Land Pattern Standard》中推荐的尺寸进行尺寸设计。同时推荐使用IPC-7351A LP Viewer。该软件包括目前常用的大多数SMD元件的封装。并给出其尺寸及焊盘设计尺寸。可以从https://www.doczj.com/doc/311014997.html,免费下载。 Thermal Relief: 通常比Regular pad尺寸大20mil,如果Regular Pad尺寸小于40mil,根据需要适当减小。 Anti pad: 通常比Regular pad尺寸大20mil,如果Regular Pad尺寸小于40mil,根据需要适当减小。 SOLDERMASK: 通常比Regular Pad尺寸大4mil。

Cadence元件圭寸装设计 、进入封装编辑器 要创建和编辑零件封装,先要进入Allegro P ackage封装编辑器界面,步骤如 下: 1、执行“开始/Cadence/Release 16.3/PCB Editor ”命令,弹出产品选择对 话框,如下图, 点击Allegro PCB Design GXL 即可进入PCB设计。 .. .... —. . . , . . 4 匕fd 巨" ?■■■--U 2、在PCB设计系统中,执行File/New 将弹出New Drawing对话框如下图, 该对话框中,在Drawing Name中填入新建设计名称,并可点击后面Browse改 变设计存储路径;在Temp late栏中可选择所需设计模板;在Drawi ng Type栏中,选

择设计的类型。这里可以用以设计电路板(Board) 、创建模型(Module) ,还可以用以创建以下各类封装: (1) 封装符号(Package Symbol) 一般元件的封装符号, 后缀名为*.psm。PCB 中所有元件像电阻、电容、电感、IC等的圭寸装类型都是Package Symbol; (2) 机械符号(Mechanical Symbol) 由板外框及螺丝孔所组成的机构符号,后缀名为*.bsm。有时设计PCB的外框及螺丝孔位置都是一样的,比如显卡,电脑主板,每次设计PCB时要画一次板外框及确定螺丝孔位置,显得较麻烦。这时我们可以将PCB的外框及螺丝孔建成一个 Mechanical Symbol, 设计PCB时,调用Mechanical Symbol 即可。 (3) 格式符号(Format Symbol) 由图框和说明所组成的元件符号,后缀名为*.osm。 (4) 形状符号(Shape Symbol) 用以建立特殊形状的焊盘用,后缀为*.ssm。像金手指封装的焊盘即为一个不规则形状的焊盘, 在建立此焊盘时要先将不规则形状焊 盘的形状建成一个Shape Symbol, 然后在建立焊盘中调用此Shape Symbol。 (5) 嚗光符号(Flash Symbol) 焊盘连接铜皮导通符号, 后缀名为*.fsm 。在PCB 设计中, 焊盘与其周围的铜皮相连, 可以全包含, 也可以采用梅花辨的形式连接, 我们可以将此梅花辨建成一个Flash Symbol, 在建立焊盘时调用此Flash Symbol 。 其中Package symbol即是有电气特性的零件圭寸装,其中Pad是Package symbol 构成的基础。 3、选定设计路径和名称,而后选择Package Symbol,点击OK则进入 Allegro Package 工作界面如下图。