allegro焊盘总结

- 格式:doc

- 大小:73.00 KB

- 文档页数:5

26、非电气引脚零件的制作1、建圆形钻孔:(1)、parameter:没有电器属性(non-plated)(2)、layer:只需要设置顶层和底层的regular pad,中间层以及阻焊层和加焊层都是null。

注意:regular pad要比drill hole大一点27、Allegro建立电路板板框步骤:1、设置绘图区参数,包括单位,大小。

2、定义outline区域3、定义route keepin区域(可使用Z-copy操作)4、定义package keepin区域5、添加定位孔28、Allegro定义层叠结构对于最简单的四层板,只需要添加电源层和底层,步骤如下:1、Setup –> cross-section2、添加层,电源层和地层都要设置为plane,同时还要在电气层之间加入电介质,一般为FR-43、指定电源层和地层都为负片(negtive)4、设置完成可以再Visibility看到多出了两层:GND和POWER5、铺铜(可以放到布局后再做)6、z-copy –> find面板选shape(因为铺铜是shape)–> option面板的copy to class/subclass选择ETCH/GND(注意选择create dynamic shape)完成GND层覆铜7、相同的方法完成POWER层覆铜Allegro生成网表1、重新生成索引编号:tools –> annotate2、DRC检查:tools –> Design Rules Check,查看session log。

3、生成网表:tools –> create netlist,产生的网表会保存到allegro文件夹,可以看一下session log内容。

29、Allegro导入网表1、file –> import –> logic –> design entry CIS(这里有一些选项可以设置导入网表对当前设计的影响)2、选择网表路径,在allegro文件夹。

allegro常见问题解答allegro常见问题解答allegro是Cadence 推出的先进 PCB 设计布线工具,下面店铺准备了关于allegro常见问题解答,欢迎大家参考!1 无论哪个版本都经常出现自动退出,提示为非法操作,然后不能存盘,自动退出。

(ALLEGRO)(出现这种情况,主要是操作系统方面的原因,ALLEGRO要求在英文NT或WINDOWS 2000下使用.在中文WINDOWS 2000下,出错概略提高许多。

事实上,设计人员应充分使用Allegro的Autosave 功能,以避免各种情况下引起的数据丢失。

提示:Allegro在异常退出时,会在当前设计目录下产生一个后缀为sav的文件。

用Allegro打开该文件,另存为brd文件即可)2在ALLEGRO中,编辑焊盘时,经常会出现“执行程序错误”而退出程序,且没有备份文件,导致之前的工作白费。

(此问题14.1已经解决,而且同样与操作系统有关)3 在从自动布线器(SPECCTRA)建军回到ALLEGRO后,输出表层的线、孔就与器件成为一个整体,移动器件时,线、孔就附在上面一起移动。

(实际上,这个功能是Cadence应大多数用户要求而添加上的,主要是为了方便移动器件的时候fanout后的引腿和via能跟着一起移动。

如果你实在不愿意这么做,可以执行下面这个Skill程序解决,以后版本将会有选项供用户选择:; The following Skill routine will remove invisible; properties from CLINES and VIAS.; The intent of this Skill program is to provide; users with the ability of deleting the invisible; properties that SPECCTRA/SPIF puts on. This will allow the moving; of symbols without the attached clines/vias once the; design is returned from SPECCTRA if the fanouts were originally; put in during an Allegro session.;; To install: Copy del_cline_prop.il to any directory defined; within your setSkillPath in your; allegro.ilinit. Add a "load("del_cline_prop.il")"; statement to your allegro.ilinit.;; To execute: Within the Allegro editor type "dprop" or; "del cline props". This routine should; only take seconds to complete.;; Deficiencies: This routine does not allow for Window or; Group selection.;; WARRANTIES: NONE. THIS PROGRAM WAS WRITTEN AS "SHAREWARE" AND IS AVAILABLE AS IS; AND MAY NOT WORK AS ADVERTISED IN ALL ENVIRONMENTS. THERE IS NO; SUPPORT FOR THIS PROGRAM.;; Delete invisible cline/via properties.;axlCmdRegister( "dprop" 'delete_cline_prop)axlCmdRegister( "del cline props" 'delete_cline_prop)(defun delete_cline_prop ();; Set the Find Filter to Select only clines(axlSetFindFilter ?enabled (list "CLINES" "VIAS")onButtons (list "CLINES" "VIAS"));; Select all clines(axlClearSelSet)(axlAddSelectAll) ;select all clines and vias(setq clineSet (axlGetSelSet))(axlDBDeleteProp clineSet "SYMBOL_ETCH") ;Remove the property(axlClearSelSet) ;unselect everything4.用贴片焊盘(type=single)做成的package,用toolspadstackmodify design padstack...编辑,发现type变成了blind/buried。

根据个人经验总结一些方法做板子的步骤1.拿到板子.什么都不管.先看要求!2.规则设置(过孔通道要大!铜的设置也要大)3.同信号打开来(via和Pin)4.打开drc5.特别关注下配对(差分)6.格点改为57.贴片型的用满铜:通孔用十字架去铺铜!8.检查要仔细啊!9.插件器件不要在里面打VIA(特别是扩版的)10.注意电影打孔!11.建pad 我们注意尺寸.线宽.丝印部要画到焊盘上!12.分割电源和地的时候注意参考平面!(28v 28V—gnd)快捷键设置alias Pgup zoom in 放大alias Pgdown zoom out 缩小alias Home add connect 拉线alias end slide 移线alias Insert reject 换线alias Del delete 删除alias F12 swap pins swap功能funckey 1 'delete;pop cut' 剪线funckey 2 'slide;pop cut' 剪小段funckey 4 assign color 高亮颜色funckey 5 dehilight 删除颜色funckey 6 angle 90 旋转90度funckey 7 copy 复制funckey 8 move 移动(元件、丝印)funckey 9 mirror 元件换层funckey ~K show measure 测量间距funckey ~O show element show功能强大(线、元件、丝印、铜箔….)funckey ~P show measure 测量间距alias Left ix -1 微调左移动alia alias Right ix 1 微调右移动alias uy iy 1 微调上移动alias down iy -1 微调下移动1.如何添加层面和删除层面setup->cross section->鼠标右键->delete2.原色透明度设置display->colour/visibility->display->OpenGL->Global transparency->transparen t3同信号DRCSetup---constraints---modes4.怎么使用swap功能Place—swap—pins设置快捷键alias按键swap pins5 .BGA怎么自动fanoutRoute---create fanout—过滤器要选择6把BUA线居中VIA&VIA居中Rout—resize\respace—选择你所要的层面7.怎么改变格点Setup—grids—更改参数8如果不小心关了过滤器怎么打打开来View—windows—后面就是窗口了9. 怎么消掉VS(1),shape—manual vold—element-点击铜箔—via(2). --点击铜箔----静铜变动铜10.如何导坐标-分图有移动元件(剪线贴线)导出(1)file—export—sub-drawing—剪线—clp (2) file—export—plaxement—symbol..-txt导入补充下!我们为了防止信号网络贴图被吸走我们剪图和贴图把这给勾选起来(如图)11.怎么改变字体大小(丝印和位号)Setup—design parameters—text12. 如何查找多余线段和via Tools—quick reports—dangling lines report13.如何改变叠层设置;板宽厚度先定义材料定义材料14.如何设置线宽,间距,同信号1.setup—constraints—….2.直接点击图标就可以了A线宽B.间距15.如何添加差分(配对)Logic —assign differential pair —加线Edit—properties—加误差Shape—polygon—割铜铜箔割好了在给它赋予网络名字补充一点怎么合并同信号铜箔掏空铜箔怎么去修铜箔呢?怎么设置自动避铜箔和线呢?A.在还没设置自动避铜之前参数是0(参考B打开)B. shape—global dynamic shape parameters--clearances我们有时候把板子打开线和铜箔都有眼睛看了会很花也很不舒服,怎么隐藏铜箔呢A.我们可以在颜色哪里设置透明度B.stupe—user preferences..-display--shape-fill—no_shape_fill17.如何添加BUSa.在添加BUS前我们要先看下什么线归类一组BUSB.在高亮这组线C.添加BUS选线小技巧(比较分散的线怎么抓)Edit—properties-右键temp group—选线—右键—complete—BUS name18.自动保存Setup—user-preferences..—filemanagener--autosave19.如何设置份割图注.分图打开也要勾选右键画一个区域或者多个区域注:合图时!要放到同个目录下面!20.怎么让元器件原点旋转Sdit—spin—body-center21.怎么在via添加测试点(TP)Manufacture—testprep—manual--add显示TP这两个要勾选起来22.边走线.边显示线的长度?23.去铺一块完整的铜皮?补充下(多个电源的!我们可以画anti etch)24.怎么自动fanout?(特别适用于BGA)快捷图标()25.命令栏的快捷图标丢失,或者不小心删了,怎么找回来?26.怎么自由设置添加快捷图标?27.不小心控制版面删了或者丢失了,怎么这么找回来?28.怎么自动避螺丝孔的铜(TOP.20mil:BOT.40mil)右键右键这样就可以自动避铜了29. 怎么显示孤铜呢?(有的时候板子看没孤铜)在打开颜色就可以看到其他的孤铜了!我们可以一个一个层面删!30.怎么把线闭合(outline)把线变为铜?我们也可以把铜变为线!补充下!要变为静态铜!31.怎么给差分添加误差(dp)32.怎么沿着半边内扩60米勒画anti each?看来这个只能用skill 输入; load("outline_anti_create.il" "") 板子打开够直接输入:anti_create33.怎么把DRC实体化!setup –> user preferences –> display 里面搜索display_drcfill34.怎么设置Xnet35.。

为了便于大家察看pcb 版,我将Allegro 中遇到的一些细微的东西在此跟大家分享:1、焊盘空心、实心的显示经常每个人都有自己视觉的习惯,有些人习惯空心焊盘而有些人则习惯实心的,当面对的板子和你自己的习惯矛盾时,可以用以下的方法来改变:在菜单中选SetupÆDrawing Options….,会弹出一个对话框:在Display 下的Filled pad 前面打勾,显示的就是实心焊盘,反之就是空心的。

在16.3中则在display菜单下参数设置,display选项卡中2、Highlight这个如果没有设定好的话,当我们高亮一个网络或者零件的时候,显示为虚线条,这样当放大屏幕的时候很难看清点亮的东西。

没有设定好的话,当我们高亮一个网络或者零件的时候,显示为虚线条,这样当缩小屏幕的时候很难看清点亮的东西。

按照如下的方法可以加以设定:在菜单中选SetupÆUser Preferences…,点选Display,在右侧的Display_nohilitefont 前面打勾,则高亮的物体显示为实心颜色,否则为虚线。

这一点实际做一下对比就可以体会到。

3、显示平面层花盘这点跟第1 点类似,在图一中的Thermal pads 中打勾即可;另外要想显示钻孔,只需选中Display drill holes。

4、DRC 显示为填充以及改变大小显示填充:同样在图二的对话框中,选中右侧Display_drcfill 即显示填充的drc,否则为空心。

改变大小:在参数设置中显示的对话框中点开drc 则出现对话框:我们就可以更改drc 的大小,或者开、关drc。

5、改变光标的形状(大十字、小十字等)用惯PowerPCB 的人可能比较习惯光标是大十字,充满整个屏幕,可以作如下设定:在图二中,选中左侧Ui,在右侧Pcb_cursor 的下拉菜单中选不同的项,则可以实现不同的设定,其中Cross 是小光标,infinite 是大光标。

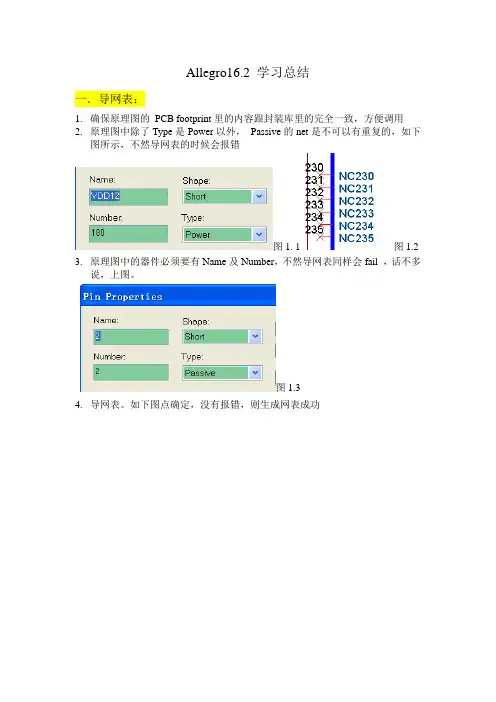

Allegro16.2 学习总结一.导网表:1.确保原理图的PCB footprint里的内容跟封装库里的完全一致,方便调用2.原理图中除了Type是Power以外,Passive的net是不可以有重复的,如下图所示,不然导网表的时候会报错图1. 1图1.2 3.原理图中的器件必须要有Name及Number,不然导网表同样会fail ,话不多说,上图。

图1.34.导网表。

如下图点确定,没有报错,则生成网表成功二.建立焊盘:Allegro的封装必须先建立相对应的PAD.2.1插播一下PAD的基本知识:一个物理焊盘包含三个pad,即:Regular Pad:正规焊盘,在正片中看到的焊盘,也是通孔焊盘的基本焊盘。

Thermal Relief:热风焊盘,也叫花焊盘,在负片中有效。

用于在负片中焊盘与敷铜的接连方式。

Anti Pad:隔离焊盘,也是在负片中有效,用于在负片中焊盘与敷铜的隔离。

SOLDEMASK:阻焊层,使铜皮裸露出来,需要焊接的地方。

PASTEMASK:钢网开窗大小。

表贴元件封装的焊盘名层面尺寸的选取:1.BEGINLAYERRegular Pad:根据器件的数据手册提供的焊盘大小或者自测得的器件引脚尺寸来定。

Thermal Relief:通常比Regular Pad 大20mil,如果Regular Pad 的尺寸小于40mil,根据需要适当减小。

Anti Pad:通常比Regular Pad 大20mil,如果Regular Pad 的尺寸小于40mil,根据需要适当减小2. SOLDEMASK:通常比Regular Pad 大4mil(0.1mm)。

3. PASTEMASK:与SOLDEMASK 一样。

直插元件封装焊盘各层面尺寸的选取:1. BEGINLAYERRegular Pad:根据器件的数据手册提供的焊盘大小或者自测得的器件引脚尺寸来定。

Thermal Relief:通常比Regular Pad 大20mil。

allegro总结根据个人经验总结一些方法做板子的步骤1.拿到板子.什么都不管.先看要求!2.规则设置(过孔通道要大!铜的设置也要大)3.同信号打开来(via和Pin)4.打开drc5.特别关注下配对(差分)6.格点改为57.贴片型的用满铜:通孔用十字架去铺铜!8.检查要仔细啊!9.插件器件不要在里面打VIA(特别是扩版的)10.注意电影打孔!11.建pad 我们注意尺寸.线宽.丝印部要画到焊盘上!12.分割电源和地的时候注意参考平面!(28v 28V—gnd)快捷键设置alias Pgup zoom in 放大alias Pgdown zoom out 缩小alias Home add connect 拉线alias end slide 移线alias Insert reject 换线alias Del delete 删除alias F12 swap pins swap功能funckey 1 'delete;pop cut' 剪线funckey 2 'slide;pop cut' 剪小段funckey 4 assign color 高亮颜色funckey 5 dehilight 删除颜色funckey 6 angle 90 旋转90度funckey 7 copy 复制funckey 8 move 移动(元件、丝印)funckey 9 mirror 元件换层funckey ~K show measure 测量间距funckey ~O show element show功能强大(线、元件、丝印、铜箔….)funckey ~P show measure 测量间距alias Left ix -1 微调左移动alia alias Right ix 1 微调右移动alias uy iy 1 微调上移动alias down iy -1 微调下移动1.如何添加层面和删除层面setup->cross section->鼠标右键->delete2.原色透明度设置display->colour/visibility->display->OpenGL->Global transparency->transparen t3同信号DRCSetup---constraints---modes4.怎么使用swap功能Place—swap—pins 设置快捷键alias按键swap pins5 .BGA怎么自动fanoutRoute---create fanout—过滤器要选择6把BUA线居中VIA&VIA居中Rout—resize\respace—选择你所要的层面7.怎么改变格点Setup—grids—更改参数8如果不小心关了过滤器怎么打打开来View—windows—后面就是窗口了9. 怎么消掉VS(1),shape—manual vold—element-点击铜箔—via(2). --点击铜箔----静铜变动铜10.如何导坐标-分图有移动元件(剪线贴线)导出(1)file—export—sub-drawing—剪线—clp (2) file—export—plaxement—symbol..-txt导入补充下!我们为了防止信号网络贴图被吸走我们剪图和贴图把这给勾选起来(如图)11.怎么改变字体大小(丝印和位号)Setup—design parameters—text12. 如何查找多余线段和via Tools—quick reports—dangling lines report13.如何改变叠层设置;板宽厚度先定义材料定义材料14.如何设置线宽,间距,同信号1.setup—constraints—….2.直接点击图标就可以了A线宽B.间距15.如何添加差分(配对)Logic —assign differential pair —加线Edit—properties—加误差Shape—polygon—割铜铜箔割好了在给它赋予网络名字补充一点怎么合并同信号铜箔掏空铜箔怎么去修铜箔呢?怎么设置自动避铜箔和线呢?A.在还没设置自动避铜之前参数是0(参考B打开)B. shape—global dynamic shape parameters--clearances我们有时候把板子打开线和铜箔都有眼睛看了会很花也很不舒服,怎么隐藏铜箔呢A.我们可以在颜色哪里设置透明度。

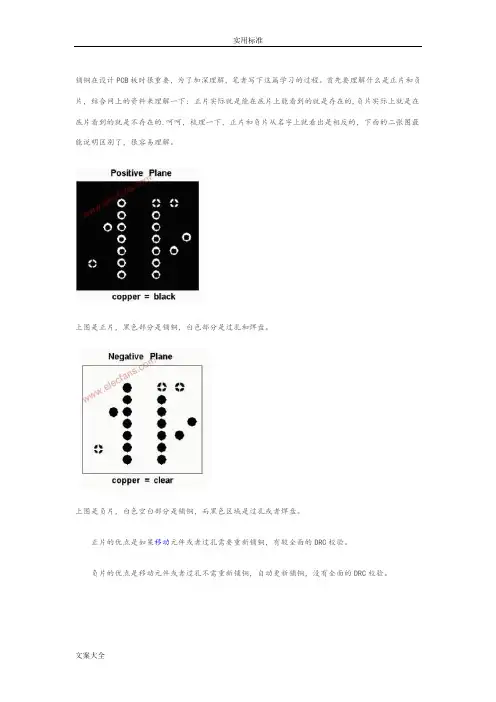

铺铜在设计PCB板时很重要,为了加深理解,笔者写下这篇学习的过程。

首先要理解什么是正片和负片,结合网上的资料来理解一下:正片实际就是能在底片上能看到的就是存在的,负片实际上就是在底片看到的就是不存在的.呵呵,梳理一下,正片和负片从名字上就看出是相反的,下面的二张图最能说明区别了,很容易理解。

上图是正片,黑色部分是铺铜,白色部分是过孔和焊盘。

上图是负片,白色空白部分是铺铜,而黑色区域是过孔或者焊盘。

正片的优点是如果移动元件或者过孔需要重新铺铜,有较全面的DRC校验。

负片的优点是移动元件或者过孔不需重新铺铜,自动更新铺铜,没有全面的DRC校验。

可以在上图看到热风焊盘,分为正热风焊盘和负热风焊盘这二种焊盘是针对内层中的正片或者负片的。

也可以在选择焊盘时预览。

接着要理解动态铜箔和静态铜箔的概念和区别所谓动态就是能自动避让元件或者过孔,所谓静态就是要手动避让,其实他们有不同的设置主要是对动态铜箔的设置,可以通过shape->Global Dynamic Params来设置铜箔的参数。

铺铜的主要步骤是建立Shape.我们先学习一下如何建立Shape,可以在菜单栏上看到Shape下面根据Cadence的一本书中的实例来看看,如何为平面层建立Shape。

使用Shape的菜单项为VCC电源层建立Shape点击Shape->Polygon命令,并在options选项中设置为下。

注意Assign net name我们设置新建的Shape的网络名为Vcc并且为静态的Static solid,然后在Route Keepin区域中沿着边缘绘制出这个Shape形状。

使用Z-copy命令为GND地层建立Shape20-080100-106002在Edit-Z-Copy命令修改Options如图然后点击刚才设置的VCC的Shape创建完毕。

选择Shape菜单中的Select Shape or Void,然后用鼠标选中刚才创建的GND shape并右键选中Assign Net为复制成的GND Shape创建网络名,具体的Options为至此我们使用二种方法制作了VCC和GND的Shape 。

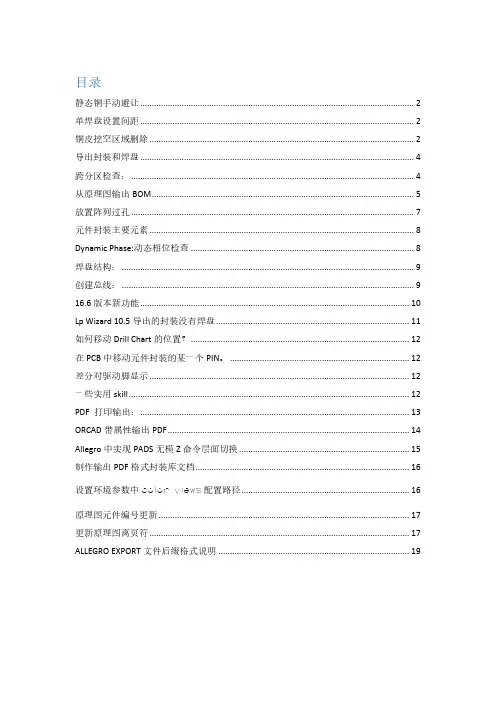

目录静态铜手动避让 (2)单焊盘设置间距 (2)铜皮挖空区域删除 (2)导出封装和焊盘 (4)跨分区检查: (4)从原理图输出BOM (5)放置阵列过孔 (7)元件封装主要元素 (8)Dynamic Phase:动态相位检查 (8)焊盘结构: (9)创建总线: (9)16.6版本新功能 (10)Lp Wizard 10.5导出的封装没有焊盘 (11)如何移动Drill Chart的位置? (12)在PCB中移动元件封装的某一个PIN。

(12)差分对驱动脚显示 (12)一些实用skill (12)PDF 打印输出: (13)ORCAD带属性输出PDF (14)Allegro中实现PADS无模Z命令层面切换 (15)制作输出PDF格式封装库文档 (16)设置环境参数中color views配置路径 (16)原理图元件编号更新 (17)更新原理图离页符 (17)ALLEGRO EXPORT文件后缀格式说明 (19)静态铜手动避让1、选中静态铜图标,右键Parameters设置参数。

铜皮挖空区域删除单焊盘设置间距选属性菜单,点焊盘编辑增加间距属性。

导出封装和焊盘跨分区检查:运行命令Highlight SOV,取消高亮用Dehilight。

设置参数:sov_active_only打勾(只检查当前层),sov_spacing(检查间隙值)。

只检查一条或几条网络从原理图输出BOMK eyed用于设置合并相同的元件,例如一个电路中有10个0.1uF的电容,如果不设置key,则会按标号列出10行来。

如果把“值”、“封装”,这两项设为key,就会把这两项相同的电容认为是同一个元件,其他没设置为key的属性会被统一成一个,例如如果有C1~C9的属性“器件名称”叫“电容”,C10的属性“器件名称”叫“陶瓷电容”,则会按照出现的顺序把“器件名称”这个属性统一为电容,列写到同一行。

然后调整上下顺序,实现自己要的BOM表。

Allegro 中SYMBOL 种类在Allegro 中, Symbol 有五种, 它们分别是Package Symbol 、Mechanical Symbol、Format Symbol、Shape Symbol、Flash Symbol。

每种Symbol 均有一个Symbol Drawing File(符号绘图文件), 后缀名均为*.dra。

此绘图文件只供编辑用, 不能给Allegro 数据库调用。

Allegro 能调用的Symbol 如下:一、Package Symbol一般元件的封装符号, 后缀名为*.psm。

PCB 中所有元件像电阻、电容、电感、IC 等的封装类型即为Package Symbol。

二、Mechanical Symbol由板外框及螺丝孔所组成的机构符号, 后缀名为*.bsm。

有时我们设计PCB 的外框及螺丝孔位置都是一样的, 比如显卡, 电脑主板, 每次设计PCB 时要画一次板外框及确定螺丝孔位置, 显得较麻烦。

这时我们可以将PCB 的外框及螺丝孔建成一个Mechanical Symbol, 在设计PCB 时, 将此Mechanical Symbol 调出即可。

三、Format Symbol由图框和说明所组成的元件符号, 后缀名为*.osm。

比较少用。

四、Shape Symbol供建立特殊形状的焊盘用, 后缀为*.ssm。

像显卡上金手指封装的焊盘即为一个不规则形状的焊盘, 在建立此焊盘时要先将不规则形状焊盘的形状建成一个Shape Symbol, 然后在建立焊盘中调用此Shape Symbol。

五、Flash Symbol焊盘连接铜皮导通符号, 后缀名为*.fsm。

在PCB 设计中, 焊盘与其周围的铜皮相连, 可以全包含, 也可以采用梅花辨的形式连接, 我们可以将此梅花辨建成一个Flash Symbol, 在建立焊盘时调用此Flash Symbol。

PCB命名规则—allegro一、焊盘命名规则1、贴片矩形焊盘命名规则:SMD+长(L)+宽(W)(mil)举例:SMD90X602、贴片圆焊盘命名规则:SMDC+焊盘直径(D)(mil)举例:SMDC503、贴片手指焊盘命名规则:SMDF+长(L)+宽(W)(mil)举例:SMDF30X104、通孔圆焊盘命名规则:PAD+焊盘外径(mil)+C+孔径(mil)+D举例:PAD80C50D注:D代表金属化孔,没有D代表非金属化过孔5、通孔方焊盘命名规则:PAD+焊盘外径(mil)+SQ+孔径(mil)+D举例:PAD45SQ20D注:D代表金属化孔,没有D代表非金属化过孔6、通孔矩形焊盘命名规则:PAD+长X宽+REC+孔径(mil)+D举例:PAD50X30REC20D注:D代表金属化孔,没有D代表非金属化过孔二、分离元件封装的命名规则SMD1、电阻命名规则:元件类型简称+元件尺寸举例:R0805注:06代表英制0.06英寸2、阻排命名规则:元件类型简称+元件尺寸举例:RA08053、电容命名规则:元件类型简称+元件尺寸举例:C08054、钽电容命名规则:元件类型简称+元件尺寸举例:TC32165、发光二极管命名规则:元件类型简称+元件尺寸举例:LED08056、其它分立命名规则:元件封装代号+管脚数举例:SOT23—5三、表贴IC封装的命名规则1、小外形封装IC命名规则:外形封装简称+管脚数—管脚间距(mil)举例:SO8—502、J引线小外形封装SOJ命名规则:SOJ+引脚数—管脚间距(mil)举例:SOJ14—1003、PLCC命名规则:PLCC+引脚数—管脚间距(mil)举例:SOJ14—1004、BGA命名规则:BGA+引脚数—管脚间距(mil)举例:BGA258-105、四方扁平IC命名规则:封装简称+引脚数—管脚间距(mil)举例:QFP44—50四、插装元件封装的命名规则1、无极性电容CAP命名规则:CAP-管脚间距(mil)举例:CAP-2002、有极性柱状电容命名规则:CAPC—管脚间距(mil)举例:CAPC—2003、二极管命名规则:DIODE—管脚间距(mil)举例:DIODE-2004、插装电感器命名规则:IN+形状C/R—管脚间距(mil)举例:INDC-400注:C代表圆形,R代表方形5、插装电阻器命名规则:REC—管脚间距(mil)举例:REC—2006、插装电位器命名规则:POT—管脚间距(mil)举例:POT—2007、插装振荡器命名规则:OSC+管脚数-元件尺寸(mil)举例:OSC4-20X208、单列直插SIP命名规则:SIP+管脚数—管脚间距(mil)举例:SIP6-1009、双列直插DIP命名规则:DIP+管脚数-管脚间距(mil)举例:SIP6—10010、插装晶体管命名规则:TO+封装代号—管脚数举例:TO92—311、测试点命名规则:TP五、连接器封装的命名规则1、D型连接器命名规则:DB+管脚数—类型M/F举例:DB9—M注:M代表针,F代表孔2、贴片双边缘连接器命名规则:SED+管脚数—管脚间距(mm)+类型M/F举例:SED50-10F六、热风焊盘(thermal relief)和隔离盘(anti pad)通常比规则焊盘尺寸大20MIL,如果盘小于40MIL,可以适当减小七、阻焊层一般比焊盘的尺寸大5MIL。

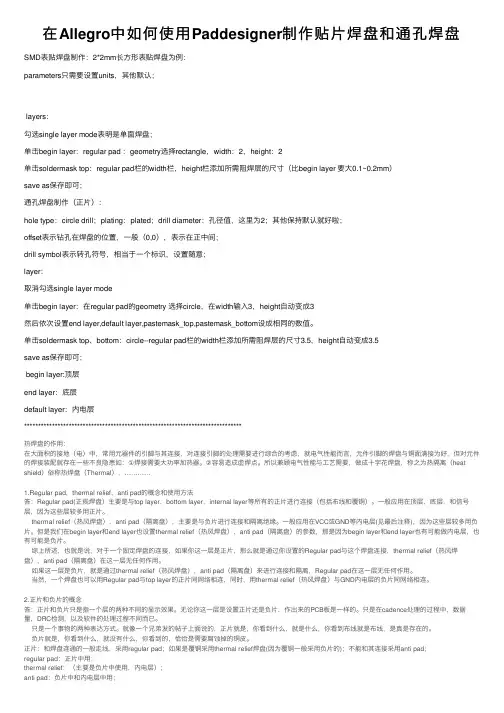

在Allegro中如何使⽤Paddesigner制作贴⽚焊盘和通孔焊盘SMD表贴焊盘制作:2*2mm长⽅形表贴焊盘为例:parameters只需要设置units,其他默认;layers:勾选single layer mode表明是单⾯焊盘;单击begin layer:regular pad :geometry选择rectangle,width:2,height:2单击soldermask top:regular pad栏的width栏,height栏添加所需阻焊层的尺⼨(⽐begin layer 要⼤0.1~0.2mm)save as保存即可;通孔焊盘制作(正⽚):hole type:circle drill;plating:plated;drill diameter:孔径值,这⾥为2;其他保持默认就好啦;offset表⽰钻孔在焊盘的位置,⼀般(0,0),表⽰在正中间;drill symbol表⽰转孔符号,相当于⼀个标识,设置随意;layer:取消勾选single layer mode单击begin layer:在regular pad的geometry 选择circle,在width输⼊3,height⾃动变成3然后依次设置end layer,default layer,pastemask_top,pastemask_bottom设成相同的数值。

单击soldermask top、bottom:circle--regular pad栏的width栏添加所需阻焊层的尺⼨3.5,height⾃动变成3.5save as保存即可;begin layer:顶层end layer:底层default layer:内电层******************************************************************************热焊盘的作⽤:在⼤⾯积的接地(电)中,常⽤元器件的引脚与其连接,对连接引脚的处理需要进⾏综合的考虑,就电⽓性能⽽⾔,元件引脚的焊盘与铜⾯满接为好,但对元件的焊接装配就存在⼀些不良隐患如:①焊接需要⼤功率加热器。

Unable to load flash symbol 170 (Check PSMPATH setting for this symbol).W-(SPMHUT-127): Could not find padstack PAD220CIR140D.PAD220CIR140D缺少热风焊盘的flash symbol,导出库的时候没有问题,但是该库缺少170.dra、170.fsm文件,软件自带的也没有(如下图)此时需要自己建一个flash symbol,这是可以自己搜索具体的步骤,下面不一定对,仅做参考,1、打开软件,新建2、setup-----design parameters..3、ADD----FLASH(注:里面的设置没有改,根据自己的实际要求来)Inner diameter(内径):选择20(同Regular Pad大小)Outer diameter(外径):选择36(同Anti Pad大小)Spoke width(开口大小):选择1012 (当DRILL_SIZE = 10MIL以下)15 (当DRILL_SIZE = 11~40MIL)20 (当DRILL_SIZE = 41~70MIL)30 (当DRILL_SIZE = 71~170 MIL)40 (当DRILL_SIZE = 171 MIL以上)也有这种说法:至于flash的开口宽度,则要根据圆周率计算一下,保证连接处的宽度不小于10mil。

公式为:Regular Pad ×Sin30°﹙正弦函数30度﹚Number of spokes(开口个数):选择4 表示有4个开口Spoke angle(开口角度):选择45,表示开口角度为45°Center Dot Option:不填注:第三步中文字这些全是网上抄的,不对请谅解(热风焊盘的内径(ID)等于钻孔直径+20mil,外径(OD)等于Anti-pad的直径,通常是比焊盘的直径大20mil。

Cadence学习笔记2__焊盘一、焊盘前期准备在Allegro系统中,建立一个零件(Symbol)之前,必须先建立零件的管脚(Pin)。

元件封装大体上分两种,表贴和直插。

针对不同的封装,需要制作不同的Padstack。

名词解释不同层的名词解释:Begin Layer:最上面的铜Default Internal:中间层End Layer:最下面的铜Solder Mask:阻焊层、绿油层。

是反显,有就是没有。

等于是开了个小孔不涂绿油,是为了把焊盘或是过孔露出来,不涂绿油就是亮晶晶的铜,也就是在板子上看到的焊盘,或者是一个个的孔,其它的部分都上阻焊剂,也就是绿油,其实不光是绿色的,还有红色的、黑色的、蓝色的等等。

Paste Mask:助焊层、钢网层、锡膏防护层、锡膏层,也叫胶贴、钢网、钢板。

是正显,有就是有。

等于是钢网开了个窗,过波峰焊时机器就在此窗口内喷上焊锡了。

这一层是针对表面贴装(SMD)元件的,其实不光是表贴,通孔也要用到,因为通孔的表面上也有个焊盘,该层用来制作钢板﹐而钢板上的孔就对应着电路板上的SMD器件的焊点。

在表面贴装(SMD)器件焊接时﹐先将钢板盖在电路板上(与实际焊盘对应)﹐然后将锡膏涂上﹐用刮片将多余的锡膏刮去﹐移除钢板﹐这样SMD器件的焊盘就加上了锡膏,之后将SMD器件贴附到锡膏上面去(手工或贴片机)﹐最后通过回流焊机完成SMD器件的焊接。

通常钢板上孔径的大小会比电路板上实际的焊盘小一些。

Film Mask:预留层,用于添加用户自定义信息,根据需要使用。

不同焊盘的名词解释:Regular Pad:实际焊盘、规则焊盘,正片中使用,也是通孔焊盘的基本焊盘。

可以是:Null、Circle 圆型、Square 方型、Oblong 拉长圆型、Rectangle 矩型、Octagon 八边型、Shape形状(可以是任意形状)。

Thermal Relief:热焊盘、热风焊盘、花焊盘、防散热焊盘。

Allegro中焊盘结构及制作方法在Allegro中焊盘的结构如下图:Soldermask_TOP EDA365论坛$ L) y) N( w% D% m5 s1 xSoldermask _BOTTOM是指阻焊层我们常说的绿油层(不过阻焊层的颜色,不只是绿色的,还有红色、蓝色、黑色和白色的等等),是电路板的非布线层,用于制成丝网漏印板,将不需要焊接的地方涂上阻焊剂。

由于焊接电路板时焊锡在高温下的流动性,所以必须在不需要焊接的地方涂一层阻焊物质,防止焊锡流动、溢出引起短路。

在阻焊层上预留的焊盘大小,要比实际焊盘大一些,其差值一般为10~20mil,在Pad_Design 工具中可以进行设定。

Pastemask_TOPPastemask _BOTTOM锡膏防护层(Paste Mask):为非布线层,该层用来制作钢膜(片),而钢膜上的孔就对应着电路板上的SMD 器件的焊点。

在表面贴装(SMD)器件焊接时,先将钢膜盖在电路板上(与实际焊盘对应),然后将锡膏涂上,用刮片将多余的锡膏刮去,移除钢膜,这样SMD 器件的焊盘就加上了锡膏,之后将SMD 器件贴附到锡膏上去(手工或贴片机),最后通过回流焊机完成SMD 器件的焊接。

通常钢膜上孔径的大小会比电路板上实际的焊点小一些,这个差值在Pad_Design 工具中可以进行设定。

Thermal relief(花焊盘/热风焊盘):也叫热风焊盘,防散热热分焊盘。

热风焊盘有以下两个作用:(1)防止散热。

由于电路板上电源和地是由大片的铜箔提供的,所以为了防止因为散热太快而造成虚焊,故电源和接地过孔采用热风焊盘形式;(2)防止大片铜箔由于热胀冷缩作用而造成对过孔及孔壁的挤压,导致孔壁变形。

Thermal relief(热风焊盘)建立(1)启动Allegro PCB Design 610—>选择“File”—>“New…”—>弹出“New Drarwing”对话框—>在“ Drawing Type”中选择“Flash symbol”,再确定热风焊盘的名字“f20-36-10”(内径20mil,外径36mil,开口10mil)。

Allegro SPB 软件操作学习之第一难关------建立PCB封装: 学习allegro首先就要学会建PCB封装,要会做PCB封装首先就要会建焊盘!很多人都说allegro难学,其实就是被一开始的做封装给难住了, 根源就在于对焊盘结构不了解,甚至有些教材有误导人之处, 很多教材你看了也是一头雾水! 在这里我尽所能帮初学者、有需之士描述一些东东,看看对你有帮助不喽?一.认识通孔焊盘结构,让脑子里有个清晰正确的焊盘概念,今后做焊盘才不会出错.做起来也比较顺手。

如上图, 最表层(顶层)为soldermask ,就是我们通常说的绿油层了, 但是注意了, 我们以后做焊盘时所填的soldermask参数是其开窗大小参数, 也就是不上绿油(阻焊层)的地方.通常还有蓝油,红油,黑油,不管什么油都是起阻焊作用.接下来为表面的常规焊盘regular pad, 这个就是实际焊接的焊盘了,这个很好理解,就不多说了.再接下来就是内层了分别为thermal relief 和anti pad,内层结构默认做各做一层就够了,以后调用它会随你定的板层数自动增加, thermal relief我就把它译为防散热结构片,其作用就是为防止内电层覆铜与镀锡的钻孔完全接通。

因为完全接通将造成对焊接温度散热过快造成焊接温度不够影响焊接。

(很多人或教材把它叫散热焊盘,有点难理解,它真正目的是防散热.)Anti pad我就把它译成防连接结构片, 实际上它就是没有被覆铜的面积大小参数,它的作用(意思)就是为防止内电层与镀锡的钻孔连接短路.因为这层的逻辑上是不需要跟这个焊盘钻孔连接的,从上图中我们不难看出.thermal relief和anti pad这两个说它是焊盘嘛也不适合,很多教材都译成带有“焊盘”字样的名称,我认为有点误导人, 所以总有些人搞不清楚这些概念故而说allegro太难学!接下来就是最底层,其结构跟最顶层是一样的概念,这里就不多说了.接下来再来加深一下理解, 比如一块四层板,内电层分别为VCC(正电)和GND(负电) 两层,那么一个通孔焊盘就要穿过这两层, 如果这个通孔焊盘电气逻辑上都没有连接这两个内电层, 那么这个通孔焊盘在这个设计里就自动用上两个anti pad,这样通孔焊盘就都不连接内电层了. 反过来理解,如果要接内电层(四层板的通常只接其中一内电层啦) 那它就自动用上thermal relief来进行连接. 多层板有多个层要接,它就自动产生多个thermal relief来连接相应的层. 注意,从下下图中我们还看出内层有真正叫焊盘的,那就是用于多层板中的内布线层。

不规则焊盘制作流程一.引言在此介绍不规则贴片焊盘和不规则通孔焊盘(椭圆例)的制作流程。

二.焊盘制作a)不规则贴片焊盘1.开启软件,File->new打开如下对话框,设置如下:2.点击setup->Design parameter Editor设置好单位及其相关,Drawingtype->package(务必设置)3.Shape->polygon画如下图形:4.点击shape->merge shape 合并shape,点击需要合并的图形得如下:5.点击setup->Design parameter Editor 设置Drawing type ->shape 后保存;(暂不关闭编辑器)6.Soldermask 一般比regular pad 要大0.1mm ,故还需要再制作一个相对大0.1mm的shape;点击 setup->Design parameter Editor 设置Drawing type ->package7.点击Editor->Z_copy shape 并设置Options->Size ->contract(放大)->offset->0.1,得到图形如下:8.删除原shape,并点击setup->Design parameter Editor 设置Drawing type ->shape 并保存命名其他名字9.打开可直接调用先前设计的shape,设计好的PAD做封装如下:以此方法,可以设计任意你需要图形的贴片PAD.b)不规则通孔焊盘的制作(椭圆例)1.在制作通孔焊盘前先制作一个椭圆的热风焊盘,打开,new填写设计flash名称和设置如下:2.点击ADD->FLASH并设置以椭圆的直径算得到的热风焊盘的尺寸,并设置Spokeangle 为90度如下:3.点击setup->Design parameter Editor 设置Drawing type -> shape(此步骤很重要),如下图所示:4.设置Find 勾选Shapes 如下图,选择需要移动的半边球形->右键->move->命令栏中输入ix -1 (即沿着X轴反方向移动1mm):5.分别在相应的位置加上椭圆的长的一半,如下图所示:6.点击shape->Merge Shape->点击需要合并的图形,得到如下图形:7.点击Setup->Design parameter Editor->Drawing type->flash,并保存flash.1.调用椭圆Shape和flash,制作Pad,得到如下:。

Allegro元件封装(焊盘)制作方法总结 时间:2008-08-05 来源: 作者:BabyKing 点击:7526 字体大小:【大 中 小】 在Allegro系统中,建立一个零件(Symbol)之前,必须先建立零件的管脚(Pin)。元件封

装大体上分两种,表贴和直插。针对不同的封装,需要制作不同的Padstack。

Allegro中Padstack主要包括以下部分。 1、PAD即元件的物理焊盘 pad有三种:

1. Regular Pad,规则焊盘(正片中)。可以是:Circle 圆型、Square 方型、Oblong 拉长圆型、Rectangle 矩型、Octagon 八边型、Shape形状(可以是任意形状)。 2. Thermal relief 热风焊盘(正负片中都可能存在)。可以是:Null(没有)、Circle 圆型、Square 方型、Oblong 拉长圆型、Rectangle 矩型、Octagon 八边型、flash形状(可以是任意形状)。 3. Anti pad 抗电边距(负片中使用),用于防止管脚与其他的网络相连。可以是:Null(没有)、Circle 圆型、Square 方型、Oblong 拉长圆型、Rectangle 矩型、Octagon 八边型、Shape形状(可以是任意形状)。

2、SOLDERMASK:阻焊层,使铜箔裸露而可以镀涂。 3、PASTEMASK:胶贴或钢网。 4、FILMMASK:预留层,用于添加用户需要添加的相应信息,根据需要使用。

表贴元件的封装焊盘,需要设置的层面及尺寸: Regular Pad: 具体尺寸根据实际封装的大小进行相应调整后得到。推荐使用《IPC-SM-782A Surface Mount Design and Land Pattern Standard》中推荐的尺寸进行尺寸设计。同时推荐使用IPC-7351A LP Viewer。该软件包括目前常用的大多数SMD元件的封装。并给出其尺寸及焊盘设计尺寸。可以从www.pcblibraries.com免费下载。

Thermal Relief: 通常比Regular pad尺寸大20mil,如果Regular Pad尺寸小于40mil,根据需要适当减小。

Anti pad: 通常比Regular pad尺寸大20mil,如果Regular Pad尺寸小于40mil,根据需要适当减小。

SOLDERMASK: 通常比Regular Pad尺寸大4mil。

PASTEMASK: 通常比Regular Pad尺寸大4mil。

FILMMASK: 似乎很少用到,暂时与SOLDERMASK 直径一样。 直插元件的封装焊盘,需要设置的层面及尺寸: 所需要层面:

Regular Pad

Thermal Relief

Anti pad

SOLDERMASK

PASTEMASK

FILMMASK

1)BEGIN LAYER-----Thermal Relief Pad和Anti Pad比实际焊盘做大0.5mm 2)END LAYER与BEGIN LAYER一样设置 2)DEFAULT INTERNAL尺寸如下 其中尺寸如下: DRILL_SIZE >= PHYSICAL_PIN_SIZE + 10MIL Regular Pad >= DRILL_SIZE + 16MIL (DRILL_SIZE<50)(0.4mm 1.27) Regular Pad >= DRILL_SIZE + 30MIL (DRILL_SIZE>=50)(0.76mm 1.27) Regular Pad >= DRILL_SIZE + 40MIL (钻孔为矩形或椭圆形时)(1mm) Thermal Pad = TRaXbXc-d其中TRaXbXc-d为Flash的名称(后面有介绍) Anti Pad = DRILL_SIZE + 30MIL 0.76mm SOLDERMASK = Regular_Pad + 6MIL 0.15mm PASTEMASK = Regular Pad (可以不要)

•Flash Name: TRaXbXc-d 其中: a. Inner Diameter: Drill Size + 16MIL b. Outer Diameter: Drill Size + 30MIL c. Wed Open: 12 (当DRILL_SIZE = 10MIL以下) 15 (当DRILL_SIZE = 11~40MIL) 20 (当DRILL_SIZE = 41~70MIL) 30 (当DRILL_SIZE = 71~170 MIL) 40 (当DRILL_SIZE = 171 MIL以上) 也有这种说法:至于flash的开口宽度,则要根据圆周率计算一下,保证连接处的宽度不小于10mil。公式为: DRILL SIZE × Sin30°﹙正弦函数30度﹚批注[B.K.1]:那不就是1/2?有待商榷 d.Angle:45 图 1 通孔焊盘(图中的Thermal Relief使用Flash)

PCB 元件(Symbol)的必要的 CLASS/SUBCLASS *这些层在添加pad时已经添加,无需额外添加。其他层需要在Allegro中建立封装时添加。 **对于PLACE_BOUND_TOP,DIP元件要比零件框大1mm SMD的话是0.2mm 注:这些层除标明必要外,其他的层可以不包括在内。另外其他层可以视情况添加进来。

序号 CLASS SUBCLASS 元件要素 备注

1* Eth Top Pad/PIN(通孔或表贴孔) Shape(贴片IC 下的散热铜箔) 必要、有导电性

2* Eth Bottom Pad/PIN(通孔或盲孔) 视需要而定、有导电性

3* Package Geometry Pin_Number 映射原理图元件的 pin 号。 如果 PAD没标号,表示原理图不关心这个 pin 或是机械孔。 必要

4 Ref Des Silkscreen_Top 元件的位号。 必要 5 Component Value Silkscreen_Top 元件型号或元件值。 必要 6 Package Geometry Silkscreen_Top 元件外形和说明:线条、弧、字、Shape 等。 必要

7 Package Geometry Place_Bound_Top** 元件占地区域和高度。 必要 8 Route Keepout Top 禁止布线区 视需要而定 9 Via Keepout Top 禁止放过孔区 视需要而定

备注: 1.Regular pad,thermal relief,anti pad的概念和使用方法 答:Regular pad(正规焊盘)主要是与top layer,bottom layer,internal layer等所有的正片进行连接(包括布线和覆铜)。一般应用在顶层,底层,和信号层,因为这些层较多用正片。 thermal relief(热风焊盘),anti pad(隔离盘),主要是与负片进行连接和隔离绝缘。一般应用在VCC或GND等内电层,因为这些层较多用负片。但是我们在begin layer和end layer也设置thermal relief(热风焊盘),anti pad(隔离盘)的参数,那是因为begin layer和end layer也有可能做内电层,也有可能是负片。 综上所述,也就是说,对于一个固定焊盘的连接,如果你这一层是正片,那么就是通过你设置的Regular pad与这个焊盘连接,thermal relief(热风焊盘),anti pad(隔离盘)在这一层无任何作用。 如果这一层是负片,就是通过thermal relief(热风焊盘),anti pad(隔离盘)来进行连接和隔离,Regular pad在这一层无任何作用。 当然,一个焊盘也可以用Regular pad与top layer的正片同网络相连,同时,用thermal relief(热风焊盘)与GND内电层的负片同网络相连。

2.正片和负片的概念 答:正片和负片只是指一个层的两种不同的显示效果。无论你这一层是设置正片还是负片,作出来的PCB板是一样的。只是在cadence处理的过程中,数据量,DRC检测,以及软件的处理过程不同而已。 只是一个事物的两种表达方式。就像一个兄弟发的帖子上面说的,正片就是,你看到什么,就是什么,你看到布线就是布线,是真是存在的。 负片就是,你看到什么,就没有什么,你看到的,恰恰是需要腐蚀掉的铜皮。

3.正片和负片时,应如何使用和设置(Regular pad,thermal relief,anti pad)这三种焊盘 答:我们在制作pad时,最好把flash做好,把三个参数全部设置上,无论你做正片还是负片,都是一劳永逸。如果不用负片,那么,恭喜你,你可以和flash说拜拜了。 如果在做焊盘的时候,你内层不做花焊盘,那么在多层板的如果电源层是负片的话就不会有花焊盘出现,必须前期做了才会有.如果反过来,前期做了,但出图的时候不想要花焊盘,可以直接在art work负片中设置去掉花焊盘。 当然你电源层也可以采用正片直接铺铜的方式,铺洞时设置孔的连着方式等参数,也可达到花焊盘的效果,这样在做焊盘的时候不做花焊盘也可以通过设置孔的连接方式达到花焊盘的效果。设置方法:shape—global dynamic parameter-Thermal relief connects里进行相应设置。 每个管脚可以拥有所有类型的pad(Regular, thermal relief, anti-pad and custom shapes),这些pad将应用于设计中的各个走线层。对于artwork层中的负片,allegro将使用thermal relief和anti-pad。而对于正片,allegro只使用Regular pad。这些工作是allegro在生成光绘文件时,自动选择的。