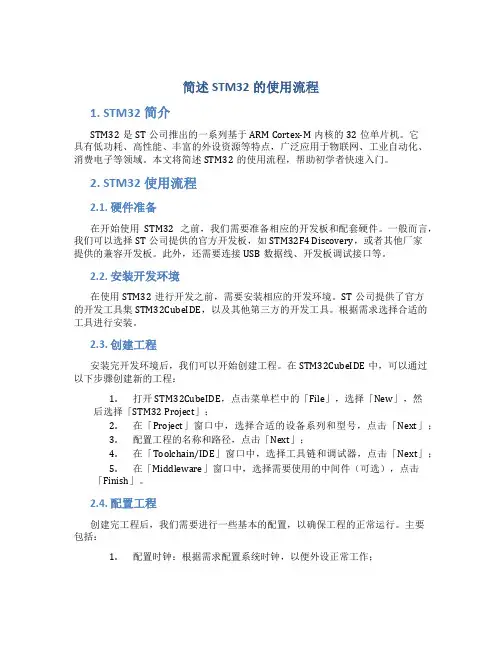

STM32L1xxx硬件开发快速入门

- 格式:pdf

- 大小:430.36 KB

- 文档页数:31

STM32学习之开发流程STM32是一种基于ARM Cortex-M内核的微控制器系列,具有高性能、低功耗和丰富的外设功能。

在学习STM32之前,我们需要了解一些基础知识。

首先,需要具备C语言的基础知识,因为STM32开发使用的是C语言编程。

其次,需要了解一些电子电路和嵌入式系统的知识,以便能够使用外设和驱动相应的硬件。

在掌握了这些基础知识之后,我们可以开始学习STM32的开发流程。

1.硬件准备2.开发环境搭建为了进行STM32的开发,我们需要搭建相应的开发环境。

常见的开发环境包括Keil MDK、IAR Embedded Workbench和STM32CubeIDE等。

这些开发环境都提供了丰富的开发工具和库函数,方便我们进行开发。

在选择开发环境时,可以根据自己的需求和操作习惯进行选择。

3.编写代码在开始编写代码之前,我们需要先了解硬件的特性和功能。

可以通过查阅STM32的参考手册和数据手册来了解各个外设的使用方法和寄存器配置等。

然后,我们可以通过开发环境提供的模板或者自己编写代码来实现相应的功能。

在编写代码时,需要注意使用合适的编程规范和风格,使得代码易于阅读和维护。

5.调试和测试6.优化和测试在程序调试和测试完成后,我们可以对程序进行优化,提高其性能和效率。

通过优化可以减小程序的体积,提高运行速度。

此外,还可以进行一些性能测试,如功耗测试、性能测试和稳定性测试等,以保证程序的质量和可靠性。

7.文档撰写和总结在开发流程结束之后,我们可以撰写相应的文档,记录开发过程和结果。

文档应包括代码注释、电路图、实验结果以及遇到的问题等。

此外,还可以对整个开发过程进行总结,总结经验和教训,为以后的开发提供参考。

STM32快速入门教程STM32是一种微控制器系列,由意法半导体(STMicroelectronics)公司推出。

它具有高性能、低功耗和丰富的外设功能,非常适合用于各种嵌入式应用。

本文将介绍STM32的快速入门教程,帮助读者快速上手使用STM32进行开发。

准备好硬件和软件环境后,我们可以开始编写程序了。

首先,我们需要创建一个新工程。

在Keil中,选择“Project”->“New uVision Project”,然后选择STM32的型号和储存路径。

在STM32CubeIDE中,选择“File”->“New”->“STM32 Project”,然后按照向导创建新工程。

接下来,我们需要配置工程的设置。

包括选择编译器、指定目标芯片型号、选择运行频率等。

在Keil中,选择“Options”->“Device”,然后选择目标芯片型号。

在STM32CubeIDE中,选择“Project”->“Properties”,然后选择目标芯片型号和运行频率。

配置完成后,我们需要编写代码。

在Keil中,选择“Project”->“Add New Item”,然后选择一个空白文件。

在STM32CubeIDE中,选择“File”->“New”->“Source File”,然后输入文件名。

编写代码时,我们可以使用STM32固件库提供的函数库,简化了底层驱动的编写。

编写代码的时候,我们需要定义引脚的用途和功能。

在Keil中,选择“Project”->“Manage”->“Board Selector”,然后选择目标芯片和功能。

在STM32CubeIDE中,选择“Pinout & Configuration”,然后选择功能和引脚。

接下来,我们可以测试编写的代码了。

我们可以使用串口输出、LED 闪烁等方式进行测试。

在Keil中,选择“View”->“Serial Window”,然后选择波特率和串口号。

stm32开发板学习计划引言:STM32开发板是一款基于ARM Cortex-M处理器的微控制器开发工具,它具有处理器高性能、低功耗、丰富的外设以及丰富的应用程序库等特点,被广泛应用于嵌入式系统开发中。

在学习STM32开发板的过程中,一定要对其硬件和软件进行深入的了解,掌握其应用方法和开发流程,这样才能更好地发挥其功能和潜力。

本文将介绍一份完整的STM32开发板学习计划,帮助初学者更好地入门和掌握STM32开发板的使用。

一、学习前的准备1. 硬件准备:- 一款STM32开发板,如STM32F103C8T6、STM32F407VGT6等- 一台计算机,安装有Windows、Linux或者MacOS操作系统- 一根MicroUSB数据线- 一块面包板- 一些基础的电子元件,如LED、电阻、电容等2. 软件准备:- 安装并配置好Keil、IAR、GCC等开发工具- 安装并配置好ST-Link、J-Link等调试工具- 下载并安装好STM32CubeMX和相关的库文件- 掌握C/C++语言的基础知识- 学习并熟悉STM32开发板的数据手册和参考手册以上准备工作完成后,就可以开始进行STM32开发板的学习了。

二、学习目标1. 了解STM32开发板的基本介绍,如型号、外设、引脚定义等2. 掌握STM32开发板的硬件连接和调试方法3. 学习STM32开发板的软件开发环境搭建和使用4. 熟悉STM32开发板的程序设计和调试流程5. 掌握STM32开发板与外围电路的连接方式和应用方法6. 完成一些基础的STM32开发板实验和项目三、学习内容和学习计划1. 学习STM32开发板的基础知识- 了解STM32开发板的基本介绍和特点- 学习STM32开发板的硬件结构、外设和引脚定义- 掌握STM32开发板的主频设置和时钟配置2. 学习STM32开发板的硬件连接和调试方法- 掌握STM32开发板的软件和硬件调试环境搭建- 学习STM32开发板与调试工具的连接和使用方法- 熟悉STM32开发板的固件升级和调试流程3. 学习STM32开发板的软件开发环境搭建和使用- 学习并掌握Keil、IAR、GCC等开发工具的安装和配置- 下载安装并配置好STM32CubeMX和相关的库文件- 掌握STM32开发板的程序编辑、编译和下载方法4. 熟悉STM32开发板的程序设计和调试流程- 学习并掌握C/C++语言在STM32开发板上的应用- 掌握STM32开发板的程序调试和仿真方法- 学习STM32开发板的程序下载和调试技巧5. 掌握STM32开发板与外围电路的连接方式和应用方法- 了解STM32开发板与外围电路的连接方式- 学习并掌握STM32开发板的GPIO、UART、SPI、I2C等外设的应用方法- 完成一些基础的STM32开发板在外围电路上的实验和项目6. 完成一些基础的STM32开发板实验和项目- 完成一些基础的STM32开发板实验,如LED控制、按键检测、PWM输出等- 完成一些简单的STM32开发板项目,如温湿度检测、无线通信等四、学习方法和总结1. 学习方法- 多参考STM32开发板的数据手册和参考手册- 多查阅相关的学习资料和教程- 多与其他学习者、开发者交流和讨论2. 总结- 在学习和实践的过程中,要及时总结和归纳所学知识- 对出现的问题和困难要及时进行分析和解决- 不断地完善和提升自己的 STM32 开发技能通过以上的学习计划,相信初学者可以更好地入门和掌握 STM32开发板的使用。

简述STM32的使用流程1. STM32简介STM32是ST公司推出的一系列基于ARM Cortex-M内核的32位单片机。

它具有低功耗、高性能、丰富的外设资源等特点,广泛应用于物联网、工业自动化、消费电子等领域。

本文将简述STM32的使用流程,帮助初学者快速入门。

2. STM32使用流程2.1. 硬件准备在开始使用STM32之前,我们需要准备相应的开发板和配套硬件。

一般而言,我们可以选择ST公司提供的官方开发板,如STM32F4 Discovery,或者其他厂家提供的兼容开发板。

此外,还需要连接USB数据线、开发板调试接口等。

2.2. 安装开发环境在使用STM32进行开发之前,需要安装相应的开发环境。

ST公司提供了官方的开发工具集STM32CubeIDE,以及其他第三方的开发工具。

根据需求选择合适的工具进行安装。

2.3. 创建工程安装完开发环境后,我们可以开始创建工程。

在STM32CubeIDE中,可以通过以下步骤创建新的工程:1.打开STM32CubeIDE,点击菜单栏中的「File」,选择「New」,然后选择「STM32 Project」;2.在「Project」窗口中,选择合适的设备系列和型号,点击「Next」;3.配置工程的名称和路径,点击「Next」;4.在「Toolchain/IDE」窗口中,选择工具链和调试器,点击「Next」;5.在「Middleware」窗口中,选择需要使用的中间件(可选),点击「Finish」。

2.4. 配置工程创建完工程后,我们需要进行一些基本的配置,以确保工程的正常运行。

主要包括:1.配置时钟:根据需求配置系统时钟,以便外设正常工作;2.配置引脚:根据实际需求配置引脚的功能和模式,如GPIO、USART、SPI等;3.配置中断:根据需要配置中断服务程序,以实现特定功能的响应;4.配置外设:根据需求初始化和配置需要使用的外设,如定时器、ADC、DAC等。

2.5. 编写代码完成工程配置后,我们可以开始编写代码了。

STM32快速入门教程本文将介绍STM32的快速入门教程,帮助你迅速上手使用STM32进行开发。

第一步:准备开发工具首先,你需要准备相应的开发工具。

在使用STM32进行开发时,通常需要以下几个工具:1.STM32开发板:选择一款合适的STM32开发板作为开发平台。

市面上有很多不同型号的STM32开发板可供选择,你可以根据自己的需求和预算作出选择。

2. 开发环境:STM32可使用多种开发环境进行开发,包括Keil MDK、IAR Embedded Workbench、STM32CubeIDE等。

你可以根据自己的习惯和需求选择适合的开发环境。

准备好以上开发工具后,我们可以开始进行STM32的快速入门教程。

第二步:熟悉开发环境在开始开发之前,我们需要先熟悉所选用的开发环境。

以Keil MDK为例,你需要了解如何创建一个新的工程、配置工程的属性和选项、添加源文件等。

这些基本的开发环境的操作将对后续的开发工作起到关键作用。

第三步:编写第一个程序学习STM32的第一步是编写一个简单的程序,将其烧录到开发板上运行。

这个程序通常是一个LED闪烁的示例程序,通过控制开发板上的LED 灯,检查开发环境是否配置正确。

在Keil MDK中,你可以创建一个新的C文件,编写如下代码:```#include "stm32f4xx.h"int main(void)//初始化LED灯RCC_AHB1PeriphClockCmd(RCC_AHB1Periph_GPIOA, ENABLE); GPIO_InitTypeDef GPIO_InitStruct;GPIO_InitStruct.GPIO_Pin = GPIO_Pin_1;GPIO_InitStruct.GPIO_Mode = GPIO_Mode_OUT;GPIO_InitStruct.GPIO_OType = GPIO_OType_PP;GPIO_InitStruct.GPIO_Speed = GPIO_Speed_50MHz;GPIO_InitStruct.GPIO_PuPd = GPIO_PuPd_NOPULL;GPIO_Init(GPIOA, &GPIO_InitStruct);while (1)//控制LED灯的状态GPIO_ToggleBits(GPIOA, GPIO_Pin_1);}```上述代码通过GPIO控制LED的亮灭,通过轮询的方式实现LED闪烁的效果。

STM32初学者必用——类似的教程如果你是一位STM32的初学者,那么以下的教程绝对会帮助你快速入门并理解如何使用STM32微控制器进行开发。

1.学习基本知识首先,你应该了解STM32是什么以及它的基本原理。

它是一款由STMicroelectronics公司生产的32位ARM Cortex-M系列微控制器。

你需要了解一些关键术语和概念,例如GPIO(通用输入输出)、引脚映射和寄存器等。

2.安装工具链在开始使用STM32微控制器进行开发之前,你需要安装一些工具。

这些工具包括STM32CubeMX,它是一款用于配置STM32微控制器的图形化配置工具。

你还需要安装Keil或者IAR Embedded Workbench等编译器和调试工具。

3.配置工程使用STM32CubeMX配置你的工程非常重要。

你可以选择适合你项目的STM32微控制器型号,并且配置外设,例如UART串口、SPI接口和I2C总线等。

配置完成后,STM32CubeMX将自动生成工程文件。

4.编写代码在编写代码之前,你需要了解一些基本的编程知识,例如C语言和嵌入式系统编程。

你可以通过阅读相关书籍或者参加在线课程学习这些知识。

接下来,你需要根据项目要求编写代码,并将其添加到生成的工程文件中。

5.调试和测试在你的代码编写完成后,你需要进行调试和测试。

你可以使用Keil 或者IAR Embedded Workbench等调试工具来单步调试代码,检查变量的值以及程序的执行路径。

你还可以使用示波器或者逻辑分析仪来测试硬件接口和通信协议的正确性。

6.参考文档和资源作为一位STM32初学者,你应该熟悉STMicroelectronics官方网站上的文档和资源。

他们提供了很多有关STM32微控制器的技术说明书、应用笔记和参考设计。

你还可以加入STM32的开发者社区,并与其他开发者分享经验和获取帮助。

总结起来,学习STM32微控制器需要对基本知识有一定的了解,并掌握相关的工具和技术。

STM32入门教程STM32是一款由意法半导体(STMicroelectronics)开发的32位微控制器系列。

它是一种广泛应用于嵌入式系统设计的芯片,具有高性能、低功耗、丰富的外设接口以及可编程的特点。

对于初学者来说,入门STM32可能会有一定的难度。

本篇教程将逐步介绍STM32的基本知识和入门方法,帮助初学者快速上手。

第一部分:STM32简介在入门STM32之前,我们首先了解一些基本的背景知识。

STM32系列采用了ARM Cortex-M内核,具有不同的系列和型号,例如STM32F1xx、STM32F4xx等。

不同的系列和型号拥有不同的性能和外设接口,所以在选型时需要根据具体需求进行选择。

第二部分:开发环境搭建第三部分:编写第一个程序第四部分:外设的使用STM32拥有丰富的外设接口,包括GPIO、UART、SPI、I2C等。

在这一部分,我们将详细介绍如何使用这些外设。

以GPIO为例,我们将学习如何配置GPIO引脚的输入输出模式,如何控制GPIO引脚的高低电平,以及如何使用外部中断功能。

类似地,我们还将介绍UART、SPI和I2C等外设的使用方法。

第五部分:中断的处理中断是STM32中一个非常重要的特性。

它可以让我们在程序运行的同时,对外部事件做出及时的响应。

本节我们将学习如何配置和使用中断。

首先,我们需要了解中断向量表和中断优先级的概念。

然后,学习如何编写中断处理函数,并配置和启用中断。

最后,通过一个例子,演示如何使用中断来处理外部事件,例如按键的按下和释放。

第六部分:时钟和定时器时钟和定时器是嵌入式系统中非常重要的功能模块。

STM32提供了多个时钟源和定时器模块,可以用于各种定时任务和时序要求。

在这一部分,我们将学习如何配置时钟源和时钟分频器,以及如何配置和使用定时器。

通过一个实例,我们将学习如何使用定时器来产生精确的延时和周期性的中断信号。

第七部分:存储器和编程方法STM32拥有多种存储器类型,包括闪存、RAM和EEPROM等。

stm32教程

以下是一份 STM32 的基础教程,无标题且文中没有重复的文字。

STM32 是一系列由意法半导体(STMicroelectronics)公司推

出的 32 位单片机系列产品。

它基于 ARM Cortex-M 内核,提

供了强大的计算能力和丰富的外设功能。

本教程将介绍如何开始使用 STM32,并带领你逐步了解其基

本使用方法。

首先,你需要准备以下材料:

1. 一块 STM32 开发板

2. 一根 USB 数据线

3. 一台计算机

接下来,我们将逐步进行以下步骤:

1. 安装 STM32 相关软件开发工具,如 Keil MDK 或者

STM32Cube IDE。

2. 连接开发板和计算机,使用 USB 数据线将它们连接起来。

3. 打开开发工具,并创建一个新的工程。

4. 设置工程的参数,包括选择正确的目标芯片型号和调试接口。

5. 在工程中编写并调试代码,以实现你想要的功能。

在编写代码的过程中,你可以调用 STM32 提供的丰富的函数

库,如 GPIO 控制、串口通信、定时器和中断等。

这些函数库

可以帮助你更快速地实现你的应用需求。

在实际应用中,你可以根据具体需求,使用外部传感器、执行器等硬件组件。

通过 STM32 的外设功能,你可以方便地与这

些硬件组件进行通信和控制。

总结起来,STM32 是一款功能强大的 32 位单片机,它的灵活

性和丰富的外设功能使得它成为了嵌入式系统开发的理想选择。

通过本教程,你将能够快速上手 STM32 开发,并能够独立完

成自己的项目。

STM32 开发入门教程(一 ) 开发环境建立及其应用入门准备:我们常用的STM32开发编译环境为和 IAR公司的EWARM.Keil 公司的MDK(Microcontroller Development Kit)在这里我们提供了比较稳定的新版本编译软件下载: MDK4.10限于篇幅 , 在我们的教程里面将先以MDK下的一个例子来介绍如何使用式应用开发 .MDK 进行嵌入MDK 安装与配置 :基于MDK下的开发中基本的过程:(1)创建工程 ;(2)配置工程 ;(3)用 C/C++ 或者汇编语言编写源文件 ;(4)编译目标应用程序(5)修改源程序中的错误(6)测试链接应用程序----------------------------------------------------------------(1)创建一个工程 :在 uVision 3 主界面中选择 "Project" -> "New uVision Project" 菜单项 , 打开一个标准对话框选择好你电脑中的保存目录后名字叫 "NewProject" 的工程, 输入一个你的工程名字后点确认..我们的工程中建了一个从设备库中选择目标芯片选中STMicrocontroller, 我们的MINI-STM32下对应的芯片:开发板使用的是STM32F103V8T6, 因此ARM 32-bit Cortex-M3 Microcontroller, 72MHz, 64kB Flash, 20kB SRAM, PLL, Embedded Internal RC 8MHz and 32kHz, Real-Time Clock, Nested Interrupt Controller, Power Saving Modes, JTAG and SWD,3 Synch. 16-bit Timers with Input Capture, Output Compare and PWM, 16-bit 6-ch Advanced Timer, 2 16-bit Watchdog Timers, SysTick Timer,2 SPI, 2 I2C,3 USART, USB 2.0 Full Speed Interface, CAN 2.0B Active, 2 12-bit 16-ch A/D Converter, Fast I/O Ports选择完芯片型号后会提示是否在目标工程中加入CPU的相关的启动代码,如下图所示启动代码是用来初始化目标设备的配置,完成运行的系统初始化工作,因此我们选择" " ,这会使系统的启动代码编写工作量大大减少.. 是----------------------------------------------------------------(2)配置工程 :选择菜单中"Project" -> "Option for Target"或者选择快捷菜单中的图标:因为 MINI-STM32开发板上使用的就是8M 的晶振且是使用的片内的RAM 和 ROM 因此"taget"下我们都可以使用默认的配置;在"Output"菜单下我们需要选中"Creat Hex File"来生成编译好的工程代码,此工程可以通过仿真器或者串口ISP烧录进开发板中.注: ISP 烧录过程我们将在入门教程二中给大家介绍."Listing" "User"菜单中我们保持默认即可."C/C++"菜单为我们常用的菜单,这里简单的介绍下他们的具体功能:PreProcesser Symbols 中的 Define, Undefine菜单表示是工程的宏定义中的变量,我们将在今后的教程中详细介绍这个功能.Optimization为优化选项 , Level0为不优化,这种模式最适合调试,因为不会优化掉代码, 基本每个用到的变量都可以打断点 . Level3 为优化等级最高 , 最适合生产过程中下载到芯片中的代码 .Include Path为工程中的包含路径,一般需将.h文件或者库文件的地址配置进去."Asm" 和 "Link"将在今后的高级教程中介绍."Debug" 为我们调试使用的配置选项, "Use Simulator" 为使用软件仿真. 这里根据大家手里的仿真器来选择配置环境.如果你使用的是Ulink,那么就选择"Ulink 就选择 " Cotex M3 Jlink",如果你使用的是就选择 "ST-Link Debug". Cotex Debug",如果你选择的是JLINK,ST公司出的简易仿真器ST-Link ,那么那么你注意 : main 右边当中的选项"Run to main{}"函数 ,如果没有选上就会进入初始地址选项如果勾上就表示仿真时进入了就会进入到,你需要自己打断点运行到你的主程序main处.当插上仿真器后选择上面右图中的Setting后会跳出一个仿真器的配置菜单.左边会自动识别出你的仿真器的信息.如下图为ULINK2 的信息 :对于 SWJ 选项为三线制调试右下方有两个选项:, 将在后面的高级教程中介绍."Verify Code Download" : "Download to flash":表示下载后校验数据表示当仿真的时候先将目标代码下载到Flash 中 .Trace 菜单为跟踪配置, 可以实时的将一些变量使用曲线的形式实时表示出来, 我们将在今后的高级教程中介绍这一项功能注意 :市面上目前的盗版Ulink2 能. .不支持这项功能, 正版的支持, Jlink 也不支持这项功"Flash Download"菜单用来配置使用仿真器程序下载的配置选项芯片配套的选项.如果你是使用的别人模板下修改为你的工程果不正确将不能将你的代码下载到芯片中. ,,大家务必选择好和你这个选项请注意一下, 如配置好 "Debug"后,那么如果你使用的是仿真器仿真择正确的仿真器进行配置. "Utilities"可以不用配置.,在你已经正确得将目标板和仿真器建立了物理连接后, 请选(二 ) ISP 在线下载程序ISP :in system programming简介 :ISP:用写入器将code 烧入 , 不过 , 芯片可以在目标板上, 不用取出来 , 在设计目标板的时候就将接口设计在上面, 所以叫 " 在系统编程 ", 即不用脱离系统;应用场合 : 1,ISP 程序升级需要到现场解决 , 不过好一点的是不必拆机器了 ; ISP 的实现一般需要很少的外部电路辅助实现,通常可利用单片机的串行口接到计算机的 RS232口,通过专门设计的固件程序来编程内部存储器。

STM32学习笔记(初学者快速入门STM32 学习笔记从51 开始单片机玩了很长时间了有51PICAVR 等等早就想跟潮流玩玩ARM 但一直没有开始原因-----不知道玩了ARM 可以做什么对我自己而言如果为学习而学习肯定学不好然后cortex-m3 出来了据说这东西可以替代单片机于是马上开始关注也在第一时间开始学习可惜一开始就有点站错了队选错了型仍是对我自己而言我希望这种芯片应该是满大街都是随便哪里都可以买得到但我选的第一种显然做不到为此大概浪费了一年多时间吧现在回到对我来说是正确的道路上来啦边学边写点东西这里写的是我的学习的过程显然很多时候会是不全面的不系统的感悟式的甚至有时会是错误的有些做法会是不专业的那么为什么我还要写呢这是一个有趣的问题它甚至涉及到博客为什么要存在的问题显然博客里面的写的东西其正确性权威性大多没法和书比可为什么博客会存在呢理由很多我非专家只说我的感慨我们读武侠小说总会有一些创出独门功夫的宗师功夫极高然后他的弟子则基本上无法超越他我在想这位宗师在创造他自己的独门功夫时必然会有很多的次的曲折弯路甚至失败会浪费他的很多时间而他教给弟子时则已去掉了这些曲折和弯路当然更不会把失败教给弟子按理说效率应该更高可是没用弟子大都不如师为什么呢也许知识本身并不是最重要的获取知识的过程才是最重要的也许所谓的知识并不仅仅是一条条的结论而是附带着很多说不清道不明的东西如植物的根一条主根上必带有大量的小小的触须闲话多了些就权当前言了下面准备开始一条件的准备我的习惯第一步是先搭建一个学习的平台原来学51PICAVR 时都是想方设法自己做些工具实验板之类现在人懒了直接购买成品了硬件电路板火牛板软件有keil 和iar 可供选择网上的口水仗不少我选keil理由很简单这个我熟目前要学的知识中软硬件我都不熟所以找一个我有点熟的东西就很重要在我相当熟练之前肯定不会用到IAR如果真的有一天不得不用IAR 相信学起来也很容易因为这个时候硬件部分我肯定很熟了再加上有keil 的基础所以应该很容易学会了调试工具JLINK V8 这个不多说了价格便宜又好用就是它了二热身网上选购的付了款就是等了拿到包裹端详良久起身沐浴更衣焚香总得先吃晚饭洗澡再点个电蚊香什么的吧拆包细细端详做工精良尤其那上面的32 吋屏越看越喜欢接下来就是一阵折腾了装JLINK 软件给板子通电先试试JLINK 能不能与电脑和板子通信上了真顺一点问题也没有于是准备将附带的程序一个一个地写进去试一试一检查大部分例子的HEX 文件并没有给出这要下一步自己生成但是几个大工程的例子都有HEX 文件如MP3如UCCGI 测试等写完以后观察程序运行的效果因为之前也做过彩屏的东西知道那玩艺代码量很大要流畅地显示并不容当时是用AVR 做的在18 吋屏上显示一幅画要有一段时间现在看起来用STM32 做的驱动显示出来的画面还是很快的不过这里显示的大部分是自画图并没有完整地显示一整幅的照片所以到底快到什么程度还不好说看来不久以后这可以作为一个学习点的一个晚上过去了下一篇就是要开始keil 软件的学习了STM32 学习笔记2本想着偷点懒的没想到竞被加了精没办法啦只能勤快点啦硬件调通后就要开始编程了编程的方法有两种一种是用st 提供的库另一种是从最底层开始编程网上关于使用哪种方法编程的讨论很多据说用库的效率要低一些但是用库编程非常方便所以我还是从库开始啦库是ST 提供的怎么说也不会差到哪里再说了用32 位ARM 的话开发的观念也要随之改变一点了说说我怎么学的吧找个例子如GPIO可以看到其结构如下SOURCE 文件夹- APP 文件夹-CMSIS 文件夹-STM32F10x_StdPeriph_Driver 文件夹Lis 文件夹OBJ 文件夹其中SOURCE 中保存的是应用程序其中又有好多子文件夹而CMSIS 文件夹中和STM32F10x_StdPeriph_Driver 文件夹中是ST 提供的库这样如果要做新的工程只要将这个文件夹整个复制过来就行其中APP 中保存自己的代码因为我们用51 单片机时一般比较简单有时就一个文件所以通常不设置专门的输出文件夹而这里做开发通常会有很多个文件加入一个工程中编译过程中会产生很多中间文件因此设置专门的文件夹LIS 和OBJ 用来保存中间文件下面就将设置简单描述一下将复到过来的GPIO 根目录下的所有文件删除因为我们要学着自己建立工程用菜单Project-- New uVision Porject建立新的工程选择目标器件为STM32103VC这个过程与建立51 单片机的工程没有什么区别这里就偷点懒不上图了接下来看一看怎么设置点那个品字形打开对话框这里就给个图了相信有一定操作基础的人应该会用顺便提一下原来用VC或者IAR 时总觉得它们的一个功能就是建立一个是Debug 组和Release 组这个功能挺好的从这个图可在Keil 里也是一样可以建的将刚才那个文件夹图中CMSIS 中的文件加入CMSIS 组一共3 个其中\Source\CMSIS\Core\CM3 有两个C 语言源程序文件全部加入另外还有一个在\Source\CMSIS\Core\CM3\startup\arm 文件夹中这个文件夹中有4 个s 文件我们选择其中的startup_stm32f10x_hds 文件这是根据项目所用CPU 来选择的我们用的CPU 是103VC 的属于高密度的芯片所以选这个至于LIB 中的文件就在这儿\Source\STM32F10x_StdPeriph_Driver\src 啦这里有很多个文件把什么文件加进去呢怕麻烦的话把所有文件全部加进去这并不会增加编译后的代码量但会增加很多的编译时间接下来设定目标输出文件夹上面这个图怎么出来的就不说啦单击Select Foler for Objects在弹出来的对话框中选择OBJ 文件夹同样方法选择List 文件的输出文件夹设置好后如果直接编译是不行的会出错还需要提供头文件所在位置单击cC标签页第一次进入时Include Paths 文本框中是空白的点击其后的按钮打开对话框增加相应的路径这样路径就设好了单击OK回到上一界面然后再单击OK退出设置即可编译链接下一会要试一试新的312 版的库效果如何了STM32 学习笔记3升级库光盘中所带的例子是310 的另外还有一个312 的我试着将312 的库替代原来的库还真有问题下面就简述问题及解决方法1将库文件解压库文件名是stm32f10x_stdperiph_libzip解压后放在任意一个文件夹中2 由于原作者做了很好的规划每一个项目中都分成三个文件夹并且在source 文件夹中又做了3 个文件夹其中APP 文件夹是放自己写的文件的其他的两个是从库中复制过来的因此想当com 版本中相同的两个文件夹CMSIS 和STM32F10x_StdPeriph_Driver 直接复制过来以为一切OK结果一编译出来一堆错误其中有错误Source\App\mainc 7 error 20 identifier "GPIO_InitTypeDef" is undefined还有大量的警告Source\STM32F10x_StdPeriph_Driver\src\stm32f10x_flashc 130 warning 223-D function "assert_param" declared implicitly看了看在APP 文件夹中还有一些不属于自己的东西stm32f10x_confhstm32f10x_ithstm32f10x_itc打开一看果然是310版本的没说的换找到STM32F10x_StdPeriph_Licom\Project\Template 文件夹用里面的同样的文件替换掉这几个文件这回应该万事大吉了吧再一看依然如故没办法了只好细细研究了通过观察发现原来可以编译通过的工程在mainc 下面挂满了h 文件而这个通不过的则少得很这是编译能通过的工程这是编译通不过的工程显然有些文件没有被包含进来一点一点跟踪发现大部分的头文件都包含在stm32f10x_confh 中而这个文件又出现在stm32f10xh 中其中有这样的一行ifdef USE_STDPERIPH_DRIVERinclude "stm32f10x_confh"endif看来是这个USE_STDPERIPH_DRIVER 没有被定义啊于是人为地去掉条件ifdef USE_STDPERIPH_DRIVERinclude "stm32f10x_confh"endif再次编译果然就OK 了可是可是也不能就这么去掉啊怎么办呢万能的网啊一搜果然就有了到设置 CC页面在那个define 中加入USE_STDPERIPH_DRIVERSTM32F10X_HD当然去掉条件编译前面的注释回到原样再次编译一切顺利可是原来的工程例子也没有加这个啊怎么回事呢再次打开原来的例子找到stm32f10xh可以看到有这么一行而新的stm32f10xh 中则是这样的原com 版的stm32f10xh 被人为地修改了一下所以不在define 中定义也不要紧而新com 则不行了至此简单的升级搞定本文见于好多地方但查询后未能确定其原始出处及作者故这里说明是转贴但作者和原始出处信息就无法提供了如果原作者看到请跟贴说明知情者也请跟贴说明ARM 中的RORW 和ZI DATA一直以来对于ARM 体系中所描述的RORW 和ZI 数据存在似是而非的理解这段时间对其仔细了解了一番发现了一些规律理解了一些以前书本上有的但是不理解的东西我想应该有不少人也有和我同样的困惑因此将我的一些关于RORW 和ZI 的理解写出来希望能对大家有所帮助要了解RORW 和ZI 需要首先了解以下知识ARM 程序的组成此处所说的ARM 程序是指在ARM 系统中正在执行的程序而非保存在ROM中的bin 映像image文件这一点清注意区别一个ARM 程序包含3 部分RORW 和ZIRO 是程序中的指令和常量RW 是程序中的已初始化变量ZI 是程序中的未初始化的变量由以上3 点说明可以理解为RO 就是readonlyRW 就是readwriteZI 就是zeroARM 映像文件的组成所谓ARM 映像文件就是指烧录到ROM 中的bin 文件也称为image 文件以下用Image 文件来称呼它Image 文件包含了RO 和RW 数据之所以Image 文件不包含ZI 数据是因为ZI 数据都是0没必要包含只要程序运行之前将ZI 数据所在的区域一律清零即可包含进去反而浪费存储空间Q为什么Image 中必须包含RO 和RWA 因为RO 中的指令和常量以及RW 中初始化过的变量是不能像ZI 那样无中生有的ARM 程序的执行过程从以上两点可以知道烧录到ROM 中的image 文件与实际运行时的ARM 程序之间并不是完全一样的因此就有必要了解ARM 程序是如何从ROM 中的image到达实际运行状态的实际上RO 中的指令至少应该有这样的功能1 将RW 从ROM 中搬到RAM 中因为RW 是变量变量不能存在ROM 中2 将ZI 所在的RAM 区域全部清零因为ZI 区域并不在Image 中所以需要程序根据编译器给出的ZI 地址及大小来将相应得RAM 区域清零ZI 中也是变量同理变量不能存在ROM 中在程序运行的最初阶段RO 中的指令完成了这两项工作后 C 程序才能正常访问变量否则只能运行不含变量的代码说了上面的可能还是有些迷糊RORW 和ZI 到底是什么下面我将给出几个例子最直观的来说明RORWZI 在C 中是什么意思1 RO看下面两段程序他们之间差了一条语句这条语句就是声明一个字符常量因此按照我们之前说的他们之间应该只会在RO 数据中相差一个字节字符常量为1 字节Prog1includevoid main voidProg2includeconst char a 5 void main voidProg1 编译出来后的信息如下Code RO Data RW Data ZI Data Debug948 60 0 96 0 Grand TotalsTotal RO Size Code RO Data1008 098kBTotal RW Size RW Data ZI Data 96 009kBTotal ROM Size Code RO Data RW Data 1008098kBProg2 编译出来后的信息如下Code RO Data RW Data ZI Data Debug948 61 0 96 0Grand TotalsTotal RO Size Code RO Data 1009 099kBTotal RW Size RW Data ZI Data 96 009kBTotal ROM Size Code RO Data RW Data 1009 099kB以上两个程序编译出来后的信息可以看出Prog1 和Prog2 的RO 包含了Code 和RO Data 两类数据他们的唯一区别就是Prog2 的RO Data 比Prog1 多了1 个字节这正和之前的推测一致如果增加的是一条指令而不是一个常量则结果应该是Code 数据大小有差别2 RW同样再看两个程序他们之间只相差一个已初始化的变量按照之前所讲的已初始化的变量应该是算在RW 中的所以两个程序之间应该是RW 大小有区别Prog3includevoid main voidProg4includechar a 5 void main voidProg3 编译出来后的信息如下Code RO Data RW Data ZI DataDebug948 60 0 96 0 Grand TotalsTotal RO Size Code RO Data 1008 098kBTotal RW Size RW Data ZI Data 96009kBTotal ROM Size Code RO Data RW Data 1008098kBProg4 编译出来后的信息如下Code RO Data RW Data ZI Data Debug948 60 1 96 0 GrandTotalsTotal RO Size Code RO Data 1008 098kBTotal RW Size RW Data ZI Data 97 009kBTotal ROM Size Code RO Data RW Data 1009 099kB可以看出Prog3 和Prog4 之间确实只有RW Data 之间相差了1个字节这个字节正是被初始化过的一个字符型变量a所引起的3 ZI再看两个程序他们之间的差别是一个未初始化的变量a从之前的了解中应该可以推测这两个程序之间应该只有ZI 大小有差别Prog3includevoid main voidProg4includevoid main voidProg3 编译出来后的信息如下Code RO Data RW Data ZI Data Debug948 60 0 96 0 GrandTotal RO Size Code RO Data 1008 098kBTotal RW Size RW Data ZI Data 96 009kBTotal ROM Size Code RO Data RW Data 1008 098kBProg4 编译出来后的信息如下Code RO Data RW Data ZI Data Debug948 60 0 97 0 GrandTotalsTotal RO Size Code RO Data 1008 098kBTotal RW Size RW Data ZI Data 97009kBTotal ROM Size Code RO Data RW Data 1008098kB编译的结果完全符合推测只有ZI 数据相差了1 个字节这个字节正是未初始化的一个字符型变量a所引起的注意如果一个变量被初始化为0则该变量的处理方法与未初始化华变量一样放在ZI 区域即ARM C 程序中所有的未初始化变量都会被自动初始化为0总结1 C 中的指令以及常量被编译后是RO 类型数据2 C 中的未被初始化或初始化为0 的变量编译后是ZI 类型数据3 C 中的已被初始化成非0 值的变量编译后市RW 类型数据附程序的编译命令假定C 程序名为tstcarmcc -c -o tsto tstcarmlink -noremove -elf -nodebug -info totals -info sizes -map -list aamap-o tstelf tsto编译后的信息就在aamap 文件中ROM 主要指NAND FlashNor FlashRAM 主要指PSRAMSDRAMSRAMDDRAM继续学习中先把开发板自带一个例子做了些精简以免看得吓人就是这个让PORTD 上接的4 个LED 分别点亮开始研究代码int main voidInit_All_Periph看到这一行开始跟踪于是又看到了下面的内容void Init_All_Periph voidRCC_Configuration继续跟踪void RCC_Configuration voidSystemInit这行代码在system_stm32f10xc 中找到了void SystemInit voidReset the RCC clock configuration to the default reset state fordebug purposeSet HSION bitRCC- CR uint32_t 0x00000001Reset SW HPRE PPRE1 PPRE2 ADCPRE and MCO bits ifndef STM32F10X_CLRCC- CFGR uint32_t 0xF8FF0000elseRCC- CFGR uint32_t 0xF0FF0000endif STM32F10X_CLReset HSEON CSSON and PLLON bitsRCC- CR uint32_t 0xFEF6FFFFReset HSEBYP bitRCC- CR uint32_t 0xFFFBFFFFReset PLLSRC PLLXTPRE PLLMUL and USBPREOTGFSPRE bits RCC- CFGR uint32_t 0xFF80FFFFifndef STM32F10X_CLDisable all interrupts and clear pending bits RCC- CIR 0x009F0000elseReset PLL2ON and PLL3ON bitsRCC- CR uint32_t 0xEBFFFFFFDisable all interrupts and clear pending bits RCC- CIR 0x00FF0000Reset CFGR2 registerRCC- CFGR2 0x00000000endif STM32F10X_CLConfigure the System clock frequency HCLK PCLK2 and PCLK1 prescalersConfigure the Flash Latency cycles and enable prefetch bufferSetSysClock这一长串的又是什么如何来用呢看来偷懒是不成的了只能回过头去研究STM32 的时钟构成了相当的复杂系统的时钟可以有3 个来源内部时钟HSI外部时钟HSE或者PLL 锁相环模块的输出它们由RCC_CFGR 寄存器中的SW 来选择SW 10系统时钟切换由软件置1或清0来选择系统时钟源在从停止或待机模式中返回时或直接或间接作为系统时钟的HSE 出现故障时由硬件强制选择HSI 作为系统时钟如果时钟安全系统已经启动00HSI 作为系统时钟01HSE 作为系统时钟10PLL 输出作为系统时钟11不可用PLL 的输出直接送到USB 模块经过适当的分频后得到48M 的频率供USB 模块使用系统时钟的一路被直接送到I2S 模块另一路经过AHB 分频后送出送往各个系统其中直接送往SDIFMSCAHB 总线8 分频后作为系统定时器时钟经过APB1 分频分别控制PLK1定时器TIM2TIM7经过APB2 分频分别控制PLK2定时器TIM1TIM8再经分频控制ADC由此可知STM32F10x 芯片的时钟比之于51AVRPIC 等8 位机要复杂复多因此我们立足于对着芯片手册来解读程序力求知道这些程序代码如何使用为何这么样使用如果自己要改可以修改哪些部分以便自己使用时可以得心应手单步执行看一看哪些代码被执行了Reset the RCC clock configuration to the default reset state fordebug purposeSet HSION bitRCC- CR uint32_t 0x00000001这是RCC_CR 寄存器由图可见HSION 是其bit 0 位HSION内部高速时钟使能由软件置1或清零当从待机和停止模式返回或用作系统时钟的外部4-25MHz 时钟发生故障时该位由硬件置1来启动内部8MHz 的RC 振荡器当内部8MHz 时钟被直接或间接地用作或被选择将要作为系统时钟时该位不能被清零0内部8MHz 时钟关闭1内部8MHz 时钟开启Reset SW HPRE PPRE1 PPRE2 ADCPRE and MCO bitsifndef STM32F10X_CLRCC- CFGR uint32_t 0xF8FF0000这是RCC_CFGR 寄存器该行程序清零了MC0[20]这三位和ADCPRE[10]ppre2[20]PPRE1 〔20〕HPRE 〔30〕SWS 〔10〕和SW 〔10〕这16 位MCO 微控制器时钟输出由软件置1或清零0xx没有时钟输出100系统时钟 SYSCLK 输出101内部8MHz 的RC 振荡器时钟输出110外部4-25MHz 振荡器时钟输出111PLL 时钟2 分频后输出Reset HSEON CSSON and PLLON bitsRCC- CR uint32_t 0xFEF6FFFF清零了PLLONHSEBYPHSERDY 这3 位Reset HSEBYP bitRCC- CR uint32_t 0xFFFBFFFF清零了HSEBYP 位为什么不一次写HSEBYP外部高速时钟旁路在调试模式下由软件置1或清零来旁路外部晶体振荡器只有在外部4-25MHz 振荡器关闭的情况下才能写入该位0外部4-25MHz 振荡器没有旁路1外部4-25MHz 外部晶体振荡器被旁路所以要先清HSEON 位再清该位Reset PLLSRC PLLXTPRE PLLMUL and USBPREOTGFSPRE bitsRCC- CFGR uint32_t 0xFF80FFFF清零了USBPREPLLMULPLLXTPRPLLSRC 共7 位Disable all interrupts and clear pending bitsRCC- CIR 0x009F0000这个暂不解读SetSysClock跟踪进入该函数可见一连串的条件编译单步运行执行的是elif defined SYSCLK_FREQ_72MHzSetSysClockTo72为何执行该行呢找到SYSCLK_PREQ_的相关定义如下图所示这样就得到了我们所要的一个结论如果要更改系统工作频率只需要在这里更改就可以了可以继续跟踪进入这个函数来观察如何将工作频率设定为72MHz 的static void SetSysClockTo72 void。

STM32入门简易教程首先,我们需要一块STM32开发板。

ST公司有多种型号可供选择,其中比较常用的是STM32F4系列和STM32F7系列。

这些开发板通常配有USB接口和一些基本的外设,如LED、按钮和串口通信。

安装完开发环境后,我们就可以开始编写代码了。

首先,我们需要创建一个新的工程。

在STM32CubeIDE中,我们可以选择创建一个基于单片机型号的模板工程。

然后,我们可以命名工程,并选择要使用的板级支持软件包。

一旦工程创建完成,我们就可以添加源文件并开始编写代码了。

在STM32CubeIDE中,我们可以使用C语言或C++语言来编写代码。

我们可以使用标准的C库或者ST提供的HAL库来操作单片机的外设。

在编写代码之前,我们需要了解一些基本概念。

每个STM32单片机都有一些寄存器,用于控制和配置外设。

我们可以使用这些寄存器来读取和写入寄存器的值,以控制外设的行为。

一般来说,我们需要完成以下几个步骤来编写STM32的代码:1.配置时钟:STM32单片机有多个时钟源和时钟分频器,我们需要配置它们以满足我们的需求。

2.配置外设:根据我们的需求,我们需要配置STM32的外设,如GPIO、USART、SPI等。

我们可以使用寄存器来配置和控制外设。

3.编写主程序:我们可以编写一个循环主程序,在其中处理一些任务。

这可能包括读取和写入外设、处理中断等。

以上就是一个简单的STM32入门教程。

当然,STM32的功能非常丰富,这只是一个入门的起点。

如果想深入学习STM32,我们可以继续学习更多的外设和高级特性。

stm32正点原子入门基础例程正点原子(OneLed)是一款基于STM32微控制器的嵌入式开发板,其入门基础例程旨在帮助新手快速了解和上手STM32开发。

本文将详细介绍STM32正点原子入门基础例程的相关内容,包括硬件架构、软件开发环境、基础例程的实现原理和具体案例。

一、硬件架构正点原子开发板采用了STM32系列微控制器作为核心处理器,具有丰富的外设资源和强大的性能。

它采用了新一代的ARM Cortex-M内核,具有32位宽、高性能和低功耗的特点。

开发板上还集成了多种外设,如LED、按键、蜂鸣器、LCD等,用于演示各种基础例程的功能。

二、软件开发环境正点原子开发板的软件开发环境主要包括Keil MDK和STM32CubeMX。

Keil MDK是一款专业的ARM开发工具,其中包含了ARM编译器、调试器和集成开发环境,是开发STM32的常用工具。

而STM32CubeMX是ST官方提供的一款快速开发工具,用于配置STM32微控制器的外设和时钟等参数,并生成相应的初始化代码。

三、基础例程实现原理基础例程主要涵盖了GPIO输入输出、定时器、中断等常用技术。

下面以GPIO 输入输出为例,简要介绍基础例程的实现原理。

1. 硬件连接需要将正点原子开发板的GPIO口与其他外设连接起来。

例如,将LED连接到某个GPIO输出引脚上,将按键连接到某个GPIO输入引脚上。

2. 配置GPIO口使用STM32CubeMX工具,配置开发板上对应的GPIO口。

选择GPIO口的方向(输入/输出)、推挽输出或开漏输出、上拉电阻或下拉电阻等。

3. 生成初始化代码在STM32CubeMX中进行配置后,生成对应的初始化代码。

该初始化代码会包含设置时钟、使能外设时钟、配置GPIO口等操作。

4. 编写应用程序在Keil MDK中创建一个新的工程,并将STM32CubeMX生成的初始化代码导入到工程中。

在应用程序中,可以使用相关的库函数来操作GPIO口,实现LED的闪烁或读取按键状态等功能。

STM32开发入门教程(一) 开发环境建立及其应用入门准备:我们常用的STM32开发编译环境为Keil 公司的MDK (Microc ontro llerDevelo pment Kit) 和IAR 公司的EWARM.在这里我们提供了比较稳定的新版本编译软件下载: MDK4.10限于篇幅, 在我们的教程里面将先以MDK 下的一个例子来介绍如何使用MDK 进行嵌入式应用开发.MDK 安装与配置:基于MDK 下的开发中基本的过程:(1) 创建工程;(2) 配置工程;(3) 用C/C++ 或者汇编语言编写源文件;(4) 编译目标应用程序(5) 修改源程序中的错误(6) 测试链接应用程序----------------------------------------------------------------(1) 创建一个工程:在uVisio n 3 主界面中选择"Projec t" -> "New uVisio n Projec t" 菜单项, 打开一个标准对话框选择好你电脑中的保存目录后, 输入一个你的工程名字后点确认.我们的工程中建了一个名字叫"NewPro ject"的工程.从设备库中选择目标芯片, 我们的MINI-STM32开发板使用的是STM32F103V8T6, 因此选中STMicr ocont rolle r 下对应的芯片:ARM 32-bit Cortex-M3 Microc ontro ller, 72MHz, 64kB Flash, 20kB SRAM,PLL, Embedd ed Intern al RC 8MHz and 32kHz, Real-Time Clock,Nested Interr upt Contro ller, PowerSaving Modes, JTAG and SWD,3 Synch. 16-bit Timers with InputCaptur e, Output Compar e and PWM,16-bit 6-ch Advanc ed Timer, 2 16-bit Watchd og Timers, SysTic k Timer,2 SPI, 2 I2C,3 USART, USB 2.0 Full SpeedInterf ace, CAN 2.0B Active,2 12-bit 16-ch A/D Conver ter, Fast I/O Ports选择完芯片型号后会提示是否在目标工程中加入 CPU 的相关的启动代码, 如下图所示.启动代码是用来初始化目标设备的配置, 完成运行的系统初始化工作, 因此我们选择 "是" , 这会使系统的启动代码编写工作量大大减少.----------------------------------------------------------------(2) 配置工程:选择菜单中"Projec t" -> "Option for Target" 或者选择快捷菜单中的图标:因为 MINI-STM32开发板上使用的就是 8M 的晶振且是使用的片内的 RAM 和 ROM 因此"taget"下我们都可以使用默认的配置;在"Output"菜单下我们需要选中 "CreatHex File" 来生成编译好的工程代码, 此工程可以通过仿真器或者串口 ISP 烧录进开发板中.注: ISP 烧录过程我们将在入门教程二中给大家介绍."Listin g" "User" 菜单中我们保持默认即可."C/C++" 菜单为我们常用的菜单,这里简单的介绍下他们的具体功能:PrePro cesse r Symbol s 中的 Define, Undefi ne 菜单表示是工程的宏定义中的变量,我们将在今后的教程中详细介绍这个功能.Optimi zatio n 为优化选项, Level0为不优化, 这种模式最适合调试, 因为不会优化掉代码, 基本每个用到的变量都可以打断点. Level3为优化等级最高, 最适合生产过程中下载到芯片中的代码.Includ e Path 为工程中的包含路径, 一般需将 .h 文件或者库文件的地址配置进去."Asm" 和 "Link" 将在今后的高级教程中介绍."Debug"为我们调试使用的配置选项, "Use Simula tor" 为使用软件仿真. 这里根据大家手里的仿真器来选择配置环境.如果你使用的是 Ulink,那么就选择"UlinkCotexDebug", 如果你选择的是 JLINK,那么就选择" CotexM3 Jlink", 如果你使用的是 ST 公司出的简易仿真器 ST-Link , 那么你就选择 "ST-Link Debug".注意: 右边当中的选项 "Run to main{}" 选项如果勾上就表示仿真时进入了就会进入到main 函数, 如果没有选上就会进入初始地址, 你需要自己打断点运行到你的主程序 main 处.当插上仿真器后选择上面右图中的Settin g 后会跳出一个仿真器的配置菜单. 左边会自动识别出你的仿真器的信息.如下图为 ULINK2的信息:对于 SWJ 选项为三线制调试, 将在后面的高级教程中介绍.右下方有两个选项:"Verify Code Downlo ad" : 表示下载后校验数据"Downlo ad to flash": 表示当仿真的时候先将目标代码下载到 Flash中.Trace菜单为跟踪配置, 可以实时的将一些变量使用曲线的形式实时表示出来, 我们将在今后的高级教程中介绍这一项功能.注意: 市面上目前的盗版 Ulink2不支持这项功能, 正版的支持, Jlink也不支持这项功能."FlashDownlo ad" 菜单用来配置使用仿真器程序下载的配置选项,大家务必选择好和你芯片配套的选项. 如果你是使用的别人模板下修改为你的工程, 这个选项请注意一下, 如果不正确将不能将你的代码下载到芯片中.配置好 "Debug"后, 那么 "Utilit ies" 可以不用配置.如果你使用的是仿真器仿真, 在你已经正确得将目标板和仿真器建立了物理连接后, 请选择正确的仿真器进行配置.(二) ISP 在线下载程序ISP:in system progra mming简介:ISP: 用写入器将c ode烧入,不过,芯片可以在目标板上,不用取出来,在设计目标板的时候就将接口设计在上面,所以叫"在系统编程",即不用脱离系统;应用场合: 1,ISP 程序升级需要到现场解决,不过好一点的是不必拆机器了;ISP的实现一般需要很少的外部电路辅助实现,通常可利用单片机的串行口接到计算机的RS232口,通过专门设计的固件程序来编程内部存储器。

嵌入式STM32入门总结及学习步骤一、入门总结1. STM32是一款基于ARM Cortex-M内核的嵌入式微控制器,具有高性能、低功耗、丰富的外设等特点。

2.学习嵌入式STM32需要掌握C语言、汇编语言以及微控制器的相关知识。

3.学习嵌入式STM32的过程中,最好选择一款开发板,如STM32F407VET6开发板,作为学习的实验平台。

4.学习嵌入式STM32需要动手实践,通过编写代码并在开发板上运行,来理解嵌入式系统的工作原理。

5. 学习嵌入式STM32可以参考ST官方提供的开发工具和资料,如STM32CubeMX、STM32Cube软件包等。

二、学习步骤1.准备工作a.学习C语言和计算机基础知识,包括变量、数据类型、运算符等基本概念。

b.学习汇编语言,了解汇编指令、寄存器、内存等相关知识。

c.了解嵌入式系统的基本概念,包括处理器、存储器、外设等。

d.购买一款合适的开发板,如STM32F407VET6开发板。

f.确定学习的目标,如掌握GPIO、UART、SPI、I2C等常用外设的使用。

2.环境搭建a. 打开STM32CubeMX,根据开发板的型号,选择合适的芯片,并配置时钟、外设等。

b. 生成项目代码,并导入Keil MDK。

3.实验练习a.学习GPIO的使用,包括输入和输出模式的配置、输入和输出的控制。

b.学习中断的使用,包括外部中断和定时器中断等。

c.学习串口通信的使用,包括配置串口参数、发送和接收数据。

d.学习SPI和I2C总线的使用,包括配置外设参数、发送和接收数据。

4.深入学习a.学习时序控制,包括定时器和PWM的使用。

b.学习模拟输入输出,包括ADC和DAC的使用。

c. 学习通信协议,如CAN和Ethernet等。

d. 学习操作系统的使用,如FreeRTOS等。

e.学习低功耗和节能技术,如休眠模式和时钟管理等。

5.实战项目a.根据自己的兴趣和需求,选择一个具体的项目,如小型智能家居控制器、智能车、温湿度监测器等。

STM32初学者教程STM32是意法半导体(STMicroelectronics)推出的一款32位微控制器系列。

它具有强大的处理能力、丰富的外设和灵活的可编程性,广泛应用于各种领域,如工业控制、汽车电子、物联网设备等。

对于初学者来说,掌握STM32的基础知识和编程技巧是非常重要的。

下面是一份适用于STM32初学者的教程,帮助你快速上手STM32开发。

第一步:了解STM32系列首先,你需要了解STM32系列的基本信息。

该系列微控制器以其精简的体积和低功耗而闻名,有多个型号可供选择。

每个型号都具有不同的处理能力和外设集成。

你可以根据项目需求选择适合的型号。

第二步:搭建开发环境要开始使用STM32,你需要搭建一个适合的开发环境。

首先,你需要一台计算机,并安装STM32开发工具。

STMicroelectronics提供了免费的开发工具STM32CubeIDE,它集成了多个开发工具,如编译器、调试器等。

同时,你还需要购买一块开发板,比如ST官方提供的Discovery系列开发板。

将开发板连接到计算机上,确保能够识别到设备。

第三步:学习基本操作第四步:学习开发工具的使用学习如何使用STM32开发工具是非常重要的。

你需要掌握编译、调试、烧录等操作。

STM32CubeIDE提供了一套强大的调试工具,如单步调试、断点调试等。

你可以利用这些工具来调试你的代码,查找错误。

此外,你还需要学会如何使用外设库函数,这些函数可以简化你的开发过程。

第五步:学习编程技巧掌握编程技巧对于STM32开发来说也是非常重要的。

你可以学习如何使用中断、定时器等功能来优化你的代码。

此外,你还可以学习如何使用DMA来提高数据传输效率。

通过学习这些编程技巧,你可以更好地利用STM32的功能。

第六步:参考文档和教程在学习STM32的过程中,你可以参考一些官方文档和教程。

STMicroelectronics提供了丰富的文档和教程,包括编程手册、应用笔记等。

STM32⼊门教程前⾔⼀天⼊门STM32,仅⼀天的时间,是否有真的这么快。

不同的⼈对⼊门的理解不⼀样,这篇⼀天⼊门STM32的教程,我们先对⼊门达成⼀个共识,如果你有异议,⼀天⼊门不了,请不要较真,不要骂街,保持⼀个⼯程师该有的修养,默默潜⼼学习,因为你还有很⼤的上升空间。

我眼中的⼊门:(前提是你学过51单⽚机和C语⾔)1、知道参考官⽅的什么资料来学习,⽽不是陷⼊⼀⼤堆资料中⽆从下⼿。

2、知道如何参考官⽅的⼿册和官⽅的代码来独⽴写⾃⼰的程序,⽽不是⼀味的看到⼈家写的代码就觉得⼈家很⽜逼。

3、消除对STM32的恐惧,消除对库开发的恐惧,学习是⼀个快乐⽽富有成就感的过程。

第1章⼀天⼊门STM32本章参考资料:《STM32中⽂参考⼿册》《CM3权威指南CnR2》学习本章时,配合《STM32中⽂参考⼿册》GPIO章节⼀起阅读,效果会更佳,特别是涉及到寄存器说明的部分。

1.151与STM32简介51是嵌⼊式学习中⼀款⼊门级的精典MCU,因其结构简单,易于教学,且可以通过串⼝编程⽽不需要额外的仿真器,所以在教学时被⼤量采⽤,⾄今很多⼤学在嵌⼊式教学中⽤的还是51。

51诞⽣于70年代,属于传统的8位单⽚机,如今,久经岁⽉的洗礼,既有其辉煌⼜有其不⾜。

现在的市场产品竞争激烈,对成本极其敏感,相应地对MCU的要求也更苛刻:功能更多,功耗更低,易⽤界⾯和多任务。

⾯对这些要求,51现有的资源就显得得抓襟见肘了。

所以⽆论是⾼校教学还是市场需求,都急需⼀款新的MCU来为这个领域注⼊新的活⼒。

基于这市场的需求,ARM公司推出了其全新的基于ARMv7架构的32位Cortex-M3微控制器内核。

紧随其后,ST(意法半导体)公司就推出了基于Cortex-M3内核的MCU—STM32。

STM32凭借其产品线的多样化、极⾼的性价⽐、简单易⽤的库开发⽅式,迅速在众多Cortex-M3MCU中脱颖⽽出,成为最闪亮的⼀颗新星。

STM32⼀上市就迅速占领了中低端MCU市场,受到了市场和⼯程师的⽆⽐青睐,颇有星⽕燎原之势。

菜鸟如何开始学习STM32单片机软件编程学习STM32单片机软件编程对于菜鸟来说可能是一个有些困难的任务,但只要你掌握正确的学习方法和资源,就能够轻松入门。

下面我将提供一些建议,帮助你开始学习STM32单片机软件编程。

1.了解单片机基础知识:在开始学习STM32之前,你需要先了解一些基础的单片机知识和编程概念。

你可以通过阅读相关书籍、参加在线课程或观看教学视频来学习这些基础知识。

重要的概念包括数字电子学、微控制器的工作原理、寄存器编程等。

2.准备学习工具和硬件:学习STM32单片机编程需要一些必要的工具和硬件。

你需要一台计算机来编写、编译和烧录代码。

另外,你还需要购买一块STM32开发板,例如常用的STM32F103系列的开发板。

这样你才能够将自己的代码运行在实际的硬件上,进行调试和测试。

3. 选择合适的编程语言和开发环境:STM32单片机支持许多不同的编程语言,包括C语言、C++、Python等。

然而,C语言是最常用的编程语言,也是大部分开发人员的首选。

你可以选择使用Keil、IAR或者STM32CubeIDE等集成开发环境(IDE)来编写和烧录代码,这些IDE都支持C语言编程。

4.学习编程语言和STM32库函数:一旦你确定了编程语言和开发环境,就需要开始学习编程语言和STM32库函数的使用。

在C语言方面,你可以学习控制语句、变量和数据类型、函数、指针等基本概念。

对于STM32库函数,你需要学习如何初始化和配置GPIO口、定时器、中断等,以及如何使用串口、SPI、I2C等外设。

你可以通过阅读官方文档、参考书籍或查找在线教程来学习这些内容。

5.实践和练习:学习STM32单片机软件编程最重要的一步是进行实践和练习。

你可以编写一些简单的程序来控制LED灯的亮灭,或者学习如何读取与外设连接的传感器数据。

通过反复实践,你将更好地掌握并理解编程语言和STM32库函数的使用。

6.参与社区和论坛:加入STM32单片机的学习社区和论坛,与其他学习者和专业人士交流和分享经验。

AN3216Application note Getting started with STM32L1xxx hardware developmentIntroductionThis application note is intended for system designers who require a hardwareimplementation overview of the development board features such as the power supply, theclock management, the reset control, the boot mode settings and the debug management. Itshows how to use STM32L1xxx product families and describes the minimum hardwareresources required to develop an STM32L1xxx application.Detailed reference design schematics are also contained in this document with descriptionsof the main components, interfaces and modes.Table 1.Applicable productsType Product sub-classMicrocontroller STM32L1xxxMay 2012Doc ID 17496 Rev 61/31Contents AN3216Contents1Power supplies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61.1Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61.1.1Independent A/D converter supply and reference voltage . . . . . . . . . . . . 71.1.2Independent LCD supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81.1.3Voltage regulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81.2Power supply schemes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91.3Reset and power supply supervisor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91.3.1Power-on reset (POR)/power-down reset (PDR),brownout reset (BOR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111.3.2Programmable voltage detector (PVD) . . . . . . . . . . . . . . . . . . . . . . . . . 111.3.3Brownout reset (BOR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121.3.4System reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132Clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142.1MSI clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142.2HSE OSC clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152.2.1External source (HSE bypass) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152.2.2External crystal/ceramic resonator (HSE crystal) . . . . . . . . . . . . . . . . . 152.3LSE OSC clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162.3.1External source (LSE bypass) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162.3.2External crystal/ceramic resonator (LSE crystal) . . . . . . . . . . . . . . . . . . 162.4Clock security system (CSS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173Boot configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 183.1Boot mode selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 183.2Boot pin connection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 183.3Embedded boot loader mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 194Debug management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 204.1Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 204.2SWJ debug port (serial wire and JTAG) . . . . . . . . . . . . . . . . . . . . . . . . . . 204.3Pinout and debug port pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 204.3.1SWJ debug port pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 2/10Doc ID 17496 Rev 1AN3216Contents4.3.2Flexible SWJ-DP pin assignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 214.3.3Internal pull-up and pull-down resistors on JT AG pins . . . . . . . . . . . . . . 224.3.4SWJ debug port connection with standard JTAG connector . . . . . . . . . 225Recommendations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 235.1Printed circuit board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 235.2Component position . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 235.3Ground and power supply (V SS, V DD) . . . . . . . . . . . . . . . . . . . . . . . . . . . 235.4Decoupling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 235.5Other signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 245.6Unused I/Os and features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 246Reference design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 256.1Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 256.1.1Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 256.1.2Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 256.1.3Boot mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 256.1.4SWJ interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 256.1.5Power supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 256.2Component references . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26 7Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30Doc ID 17496 Rev 13/10List of tables AN3216 List of tablesTable 1.Applicable products . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Table 2.Boot modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 Table 3.Debug port pin assignment. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 Table 4.SWJ I/O pin availability. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 Table 5.Mandatory components . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26 Table 6.Optional components . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26 Table 7.Reference connection for all packages. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28 Table 8.Document revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 4/4Doc ID 17496 Rev 6AN3216List of figures List of figuresFigure 1.Power supply overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 Figure 2.Power supply scheme. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Figure 3.Power supply supervisors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Figure 4.Power on reset/power down reset waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Figure 5.PVD thresholds. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Figure 6.Reset circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Figure 7.External clock. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 Figure 8.Crystal/ceramic resonators. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 Figure 9.External clock. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 Figure 10.Crystal/ceramic resonators(2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 Figure 11.Boot mode selection implementation example. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 Figure 12.Host-to-board connection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20 Figure 13.JTAG connector implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22 Figure 14.Typical layout for V DD/V SS pair . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24 Figure 15.STM32L152VB(T6) microcontroller reference schematic. . . . . . . . . . . . . . . . . . . . . . . . . . 27Doc ID 17496 Rev 15/10Power supplies AN32166/10Doc ID 17496 Rev 61 Power supplies1.1 IntroductionThe device requires a 2.0 V to 3.6 V operating voltage supply (V DD ), to be fully functional atfull speed. This maximum frequency is only achieved when the digital power voltage V COREis equal to 1.8 V (product voltage range 1).Product voltage range 2 (V CORE = 1.5 V) and 3 (V CORE = 1.2 V) can be selected when theV DD operates from 1.65 V to 3.6 V . Frequency is limited to 16 MHz and 4 MHz when thedevice is in product voltage range 2 and 3 respectively.When the ADC and brownout reset (BOR) are not used, the device can operate at powervoltages below 1.8 V down to 1.65 V .Digital power voltage (V CORE ) is provided with an embedded linear voltage regulator withthree different programmable ranges from 1.2 to 1.8 V (typical).Note:V DDA and V SSA must be connected to V DD and V SS , respectively.AN3216Power supplies1.1.1 Independent A/D converter supply and reference voltageTo improve conversion accuracy, the ADC and the DAC have an independent power supplythat can be filtered separately, and shielded from noise on the PCB.●The ADC voltage supply input is available on a separate V DDA pin●An isolated supply ground connection is provided on the V SSA pinV DDA and V REF require a stable voltage. The consumption on V DDA can reach several mA(see I DD(ADCx), I DD(DAC), I DD(COMPx), I VDDA, and I VREF in the product datasheets forfurther information).When available (depending on the package), V REF¨ must be tied to V SSA.On BGA 64-pin and all 100-pin or more packagesTo ensure a better accuracy on low-voltage inputs and outputs, the user can connect toV REF+, a separate external reference voltage which is lower than V DD. V REF+ is the highestvoltage, represented by the full scale value, for an analog input (ADC) or output (DAC)signal.●For ADC– 2.4 V ≤V REF+ = V DDA for full speed (ADCCLK = 16 MHz, 1 Msps)– 1.8 V ≤V REF+ = V DDA for medium speed (ADCCLK = 8 MHz, 500 Ksps)– 2.4 V ≤V REF+ ≠ V DDA for medium speed (ADCCLK = 8 MHz, 500 Ksps)– 1.8 V ≤V REF+ < V DDA for low speed (ADCCLK = 4 MHz, 250 Ksps)–When product voltage range 3 is selected (V CORE = 1.2 V), the ADC is low speed (ADCCLK = 4 MHz, 250 Ksps)●For DAC– 1.8 V≤ V REF+ < V DDAOn packages with 64 pins or less (except BGA package)V REF+ and V REF- pins are not available. They are internally connected to the ADC voltagesupply (V DDA) and ground (V SSA).Doc ID 17496 Rev 67/10Power supplies AN32168/10Doc ID 17496 Rev 61.1.2 Independent L CD supplyThe V LCD pin is provided to control the contrast of the glass LCD. This pin can be used intwo ways:●It can receive, from an external circuitry, the desired maximum voltage that is provided on the segment and common lines to the glass LCD by the microcontroller.●It can also be used to connect an external capacitor that is used by the microcontroller for its voltage step-up converter. This step-up converter is controlled by software toprovide the desired voltage to the segment and common lines of the glass LCD.The voltage provided to the segment and common lines defines the contrast of the glassLCD pixels. This contrast can be reduced when the dead time between frames isconfigured.●When an external power supply is provided to the V LCD pin, it should range from 2.5 V to 3.6 V . It does not depend on V DD .●When the LCD is based on the internal step-up converter, the V LCD pin should beconnected to a capacitor (see the product datasheets for further information).1.1.3 Voltage regulatorThe internal voltage regulator is always enabled after reset. It can be configured to providethe core with three different voltage ranges. Choosing a range with low V core reduces theconsumption but lowers the maximum acceptable core speed. Consumption ranges indecreasing consumption order are as follows:●Range 1, available only for V DD above 2.0 V , allows maximum speed ●Range 2 allows CPU frequency up to 16 MHz ●Range 3 allows CPU frequency up to 4 MHzVoltage regulator works in three different modes depending on the application modes.●In Run mode, the regulator supplies full power to the V core domain (core, memories anddigital peripherals).●In Stop mode, Low power run and Low power wait modes, the regulator supplies low power to the V core domain, preserving the contents of the registers and SRAM.●In Standby mode, the regulator is powered off. The contents of the registers and SRAM are lost except for those concerned with the Standby circuitry.AN3216Power suppliesDoc ID 17496 Rev 69/101.2 Power supply schemesThe circuit is powered by a stabilized power supply, V DD .●The V DD pins must be connected to V DD with external decoupling capacitors; onesingle Tantalum or Ceramic capacitor (minimum 4.7µF typical 10µF) for the package +one 100nF Ceramic capacitor for each V DD pin).●The V DDA pin must be connected to two external decoupling capacitors (100 nFCeramic capacitor + 1 µF Tantalum or Ceramic capacitor).●The V REF+ pin can be connected to the V DDA external power supply. If a separate,external reference voltage is applied on V REF+, a 100 nF and a 1 µF capacitor must beconnected on this pin. To compensate peak consumption on Vref, the 1 µF capacitormay be increased up to 10µF when the sampling speed is low. When ADC or DAC isused, VREF+ must remain between 1.8V and VDDA. VREF+ can be grounded whenADC and DAC are not active; this enables the user to power down an external voltagereference.●Additional precautions can be taken to filter analog noise: V DDA can be connected toV DD through a ferrite bead.1.Optional. If a separate, external reference voltage is connected on V REF+, the two capacitors (100 nF and 1 µF) must be connected.2.V REF + is either connected to V DDA or to V REF .3.N is the number of V DD and V SS inputs.1.3 Reset and power supply supervisorThe input supply to the main and low power regulators is monitored by a power-on/power-down/brownout reset circuit. Power-on/power-down reset are a null power monitoring withfixed threshold voltages, whereas brownout reset gives the choice between severalthresholds with a very low, but not null, power consumption.In addition, the STM32L1xxx embeds a programmable voltage detector that compares thepower supply with the programmable threshold. An interrupt can be generated when thepower supply drops below the V PVD threshold and/or when the power supply is higher thanthe V PVD threshold. The interrupt service routine then generates a warning message and/orputs the MCU into a safe state.Power supplies AN321610/10Doc ID 17496 Rev 6Figure 3.Power supply supervisors1.The PVD is available on all STM32L devices and it is enabled or disabled by software.2.The BOR is available only on devices operating from 1.8 to3.6 V, and unless disabled by option byte it masks the POR/PDR threshold.3.When the BOR is disabled by option byte, the reset is asserted when V DD goes below PDR level.4.For devices operating from 1.65 to 3.6 V, there is no BOR and the reset is released when V DD goes above POR level and asserted when V DD goes below PDR level.V D D /V D DA PVD o u tp u t100 mV hy s tere s i sV PVD V BOR hy s te re s i s100 mVIT en ab ledBOR re s et(NR S T)POR/PDR re s et(NR S T)PVDBOR a lw a y s a ctivePOR/PDR (BOR not a v a il ab le)a i17211bPOR V /PDRV BOR/PDR re s et(NR S T)BOR di sab led b y option b yte(Note 1)(Note 2)(Note 3)(Note 4)AN3216Power suppliesDoc ID 17496 Rev 611/101.3.1 Power-on reset (POR)/power-down reset (PDR),brownout reset (BOR)The monitoring voltage begins at 0.7 V .During power-on, for devices operating between 1.8 and 3.6 V , the BOR keeps the deviceunder reset until the supply voltages (V DD and V DDIO ) come close to the lowest acceptablevoltage (1.8 V). At power-up this internal reset is maintained during ~1 ms to wait for thesupply to reach its final value and stabilize.At power-down the reset is activated as soon as the power drops below the lowest limit(1.65 V).At power-on, a defined reset should be maintained below 0.7 V . The upper threshold for areset release is defined in the electrical characteristics section of the product datasheets.Figure 4.Power on reset/power down reset waveformIf you want to run the cpu at full speed the threshold should be raised to 2.0 V . For aprogrammable threshold above the chip lowest limit, a brownout reset can be configured tothe desired value. The BOR can also be used to detect a power voltage drop earlier. Thethreshold values of the BOR can be configured through the FLASH_OBR option byte.1.3.2 Programmable voltage detector (PVD)The device features an embedded programmable voltage detector (PVD) that monitors theV DD /V DDA power supply and compares it to the V PVD threshold. Seven different PVD levelscan be selected by software between 1.85 V and 3.05 V , with a 200 mV step. An interruptcan be generated when V DD /V DDA drops below the V PVD threshold and/or when V DD /V DDAis higher than the V PVD threshold. The interrupt service routine then generates a warningmessage and/or puts the MCU into a safe state. The PVD is enabled by softwareconfiguration. As an example, the service routine can perform emergency shutdown tasks.V DD /V DDAResetPORPDRTemporizationt RSTTEMPOPower supplies AN321612/10Doc ID 17496 Rev 6Figure 5.PVD thresholds1.3.3 Brownout reset (BOR)During power on, the brownout reset (BOR) keeps the device under reset until the supplyvoltage reaches the specified V BOR threshold.For devices operating from 1.65 to 3.6 V , the BOR option is not available and the powersupply is monitored by the POR/PDR. As the POR/PDR thresholds are at 1.5 V , a “greyzone” exists between the V POR /V PDR thresholds and the minimum product operating voltage1.65 V.For devices operating from 1.8 to 3.6 V , the BOR is always active at power on and itsthreshold is 1.8 V .When the system reset is released, the BOR level can be reconfigured or disabled by optionbyte loading.If the BOR level is kept at the lowest level, 1.8 V at power-on and 1.65 V at power down, thesystem reset is fully managed by the BOR and the product operating voltages are withinsafe ranges.When the BOR option is disabled by option byte, the power down reset is controlled by thePDR and a “grey zone” exists between the 1.65 V and V PDR .V BOR is configured through device option bytes. By default, level 4 threshold is activated.Five programmable V BOR thresholds can be selected (see product datasheets for actualV BOR0 to V BOR4 thresholds).When the supply voltage (V DD ) drops below the selected V BOR threshold, a device reset isgenerated. When the V DD is above the V BOR upper limit the device reset is released and thesystem can start.BOR can be disabled by programming the device option bytes. T o disable the BOR function,V DD must have been higher than V BOR0 to start the device option byte programmingsequence. The power-on and power-down is then monitored by the POR and PDR (seepower-on reset (POR)/power-down reset (PDR) section in the product datasheets).The BOR threshold hysteresis is ~100 mV (between the rising and the falling edge of thesupply voltage).V DD /V DDA PVD output100 mVhysteresisPVD thresholdAN3216Power suppliesDoc ID 17496 Rev 613/101.3.4 System resetA system reset sets all registers to their reset values except for the RTC, backup registersand RCC control/status register, RCC_CSR.A system reset is generated when one of the following events occurs:1.A low level on the NRST pin (external reset)2.Window watchdog end-of-count condition (WWDG reset)3.Independent watchdog end-of-count condition (IWDG reset)4.A reset bit set by software (SWreset)5.Entering Standby or Stop mode configured to generate a reset (Low-power management reset)6.Option byte loader reset 7. Exiting Standby modeThe reset source can be identified by checking the reset flags in the Control/Status register,RCC_CSR.The STM32L does not require an external reset circuit to power-up correctly. Only a pull-down capacitor is recommended to improve EMS performance by protecting the deviceagainst parasitic resets (see Figure 6).Charging/discharging the pull-down capacitor thru the internal resistor adds to the devicepower consumption. The recommended value of 100 nF for the capacitor can be reduced to10 nF to limit this power consumption.Clocks AN321614/10Doc ID 17496 Rev 62 ClocksFour different clock sources can be used to drive the system clock (SYSCLK). They are:●HSI ((high-speed internal) oscillator clock ●HSE (high-speed external) oscillator clock ●PLL clock ●MSI (multispeed internal) oscillator clockThe MSI is used as a system clock source after startup from reset, wake-up from Stop orStandby low power modes.The devices have the following two secondary clock sources:●37 kHz low speed internal RC (LSI RC) which drives the independent watchdog and optionally the RTC used for auto-wakeup from Stop/Standby mode.●32.768 kHz low speed external crystal (LSE crystal) which optionally drives the real-time clock (RTCCLK)Each clock source can be switched on or off independently when it is not used, to optimizepower consumption.Refer to the STM32L15xxx reference manual (RM0038) for a description of the clock tree.2.1 MSI clockThe MSI clock signal is generated from an internal RC oscillator. Its frequency range can beadjusted by software through the RCC_ICSCR register. Seven frequency ranges areavailable: 65.5 kHz, 131 kHz, 262 kHz, 524 kHz, 1.05 MHz, 2.1 MHz (default value) and4.2MHz. Those frequencies are multiple values of 32.768kHz.The MSI clock is used as a system clock after a restart from reset.The MSI RC oscillator has the advantage of providing a low-cost (no external components)low-power clock source. It is used as a wakeup clock in low power modes to reduce powerconsumption and wakeup time.The MSIRDY flag in the RCC_CR register indicates wether the MSI RC is stable or not. Atstartup, the MSI RC output clock is not released until this bit is set by hardware.The MSI RC can be switched on and off through the RCC_CR register (default is on).If the application is subject to voltage or temperature variations, this may affect the RCoscillator speed. Y ou can trim the MSI frequency in the application through the RCC_ICSCRregister. Typically, this uses the HSE as reference (see RM0038 for details on clockmeasurement with TIM9/TIM10/TIM11). For more information refer to AN3300 “How tocalibrate an STM32L1xx internal RC oscillator”.AN3216ClocksDoc ID 17496 Rev 615/102.2 HSE OSC clockThe high-speed external clock signal (HSE) can be generated from two possible clocksources:●HSE user external clock (see Figure 7)●HSE external crystal/ceramic resonator (see Figure 8)1.The value of R EXT depends on the crystal characteristics. A typical value is in the range of 5 to 6 R S (resonator series resistance).2.Load capacitance, C L , has the following formula: C L = C L1 x C L2 / (C L1 + C L2) + C stray where: C stray is the pin capacitance and board or trace PCB-related capacitance. Typically, it is between 2 pF and 7 pF. Please refer to Section 5: Recommendations on page 23 to minimize its value.2.2.1 External source (HSE bypass)In this mode, an external clock source must be provided. It can have a frequency of up to32 MHz.The external clock signal (square, sine or triangle) with a duty cycle of about 50%, has todrive the OSC_IN pin while the OSC_OUT pin must be left in the high impedance state (seeFigure 7 and Figure 8).2.2.2 External crystal/ceramic resonator (HSE crystal)The external oscillator frequency ranges from 1 to 24 MHz.The external oscillator has the advantage of producing a very accurate rate on the mainclock. The associated hardware configuration is shown in Figure 8.The resonator and the load capacitors have to be connected as close as possible to theoscillator pins in order to minimize output distortion and startup stabilization time. The loadcapacitance values must be adjusted according to the selected oscillator.For C L1 and C L2 it is recommended to use high-quality ceramic capacitors in the 5 pF to 25pF range (typical), designed for high-frequency applications and selected to meet therequirements of the crystal or resonator. C L1 and C L2, are usually the same value. Thecrystal manufacturer typically specifies a load capacitance that is the series combination ofC L1 and C L2. The PCB and MCU pin capacitances must be included when sizing C L1 andC L2 (10 pF can be used as a rough estimate of the combined pin and board capacitance).Refer to the electrical characteristics sections in the datasheet of your product for moredetails.Clocks AN321616/10Doc ID 17496 Rev 62.3 L SE OSC clockThe low-speed external clock signal (LSE) can be generated from two possible clocksources:●LSE user external clock (see Figure 9)●LSE external crystal/ceramic resonator (see Figure 10)3.The value of R EXT depends on the crystal characteristics. A 0Ω resistor works but, is not optimal. A typical value is in the range of 5 to 6 R S (resonator series resistance). T o fine tune the R S value refer to AN2867 (Oscillator design guide for ST microcontrollers).2.3.1 External source (LSE bypass)In this mode, an external clock source must be provided. It must have a frequency of32.768 kHz. The external clock signal (square, sine or triangle) with a duty cycle of about50% has to drive the OSC32_IN pin while the OSC32_OUT pin must be left high impedance(see Figure 9).2.3.2 External crystal/ceramic resonator (LSE crystal)The LSE crystal is a 32.768 kHz low-speed external crystal or ceramic resonator. It has theadvantage of providing a low-power, but highly accurate clock source to the real-time clockperipheral (RTC) for clock/calendar or other timing functions.The oscillator can be switched on and off by software (default is off). When switched on, theoscillator is not stable immediately. A bit is set in the RCC_CSR register when the oscillatorbecomes stable and an interrupt can be generated if enabled in the RCC_CIR register.The resonator and the load capacitors have to be connected as close as possible to theoscillator pins in order to minimize output distortion and startup stabilization time. The loadcapacitance values must be adjusted according to the selected oscillator (see Figure 10).(1)(2)1.To avoid exceeding the maximum value of C L1 and C L2 (15 pF), it is strongly recommended to use a resonator with a load capacitance C L ≤ 7 pF. Never use a resonator with a load capacitance of 12.5 pF.2.OSC32_IN and OSC_OUT pins can be also used as GPIOs, but it is recommended not to use them as both RTC and GPIO pins in the same application.(2)。