第4,5章 触发器,时序逻辑电路习题答案...

- 格式:doc

- 大小:2.46 MB

- 文档页数:14

第12章时序逻辑电路自测题一、填空题1.时序逻辑电路按状态转换情况可分为时序电路和时序电路两大类。

2.按计数进制的不同,可将计数器分为、和N进制计数器等类型。

3.用来累计和寄存输入脉冲个数的电路称为。

4.时序逻辑电路在结构方面的特点是:由具有控制作用的电路和具记忆作用电路组成。

、5.、寄存器的作用是用于、、数码指令等信息。

6.按计数过程中数值的增减来分,可将计数器分为为、和三种。

二、选择题1.如题图12.1所示电路为某寄存器的一位,该寄存器为。

A、单拍接收数码寄存器;B、双拍接收数码寄存器;C、单向移位寄存器;D、双向移位寄存器。

2.下列电路不属于时序逻辑电路的是。

A、数码寄存器;B、编码器;C、触发器;D、可逆计数器。

3.下列逻辑电路不具有记忆功能的是。

A、译码器;B、RS触发器;C、寄存器;D、计数器。

4.时序逻辑电路特点中,下列叙述正确的是。

A、电路任一时刻的输出只与当时输入信号有关;B、电路任一时刻的输出只与电路原来状态有关;C、电路任一时刻的输出与输入信号和电路原来状态均有关;D、电路任一时刻的输出与输入信号和电路原来状态均无关。

5.具有记忆功能的逻辑电路是。

A、加法器;B、显示器;C、译码器;D、计数器。

6.数码寄存器采用的输入输出方式为。

A、并行输入、并行输出;B、串行输入、串行输出;C、并行输入、串行输出;D、并行输出、串行输入。

三、判断下面说法是否正确,用“√"或“×"表示在括号1.寄存器具有存储数码和信号的功能。

( )2.构成计数电路的器件必须有记忆能力。

( )3.移位寄存器只能串行输出。

( )4.移位寄存器就是数码寄存器,它们没有区别。

( )5.同步时序电路的工作速度高于异步时序电路。

( )6.移位寄存器有接收、暂存、清除和数码移位等作用。

()思考与练习题12.1.1 时序逻辑电路的特点是什么?12.1.2 时序逻辑电路与组合电路有何区别?12.3.1 在图12.1电路作用下,数码寄存器的原始状态Q3Q2Q1Q0=1001,而输入数码D3D2D1D0=0110时,在CP的作用下,Q3Q2Q1Q0状态如何变化?12.3.2 题图12.2所示移位寄存器的初始状态为111,画出连续3个C P脉冲作用下Q2Q1Q0各端的波形和状态表。

第12章时序逻辑电路自测题一、填空题1.时序逻辑电路按状态转换情况可分为时序电路和时序电路两大类。

2.按计数进制的不同,可将计数器分为、和N进制计数器等类型。

3.用来累计和寄存输入脉冲个数的电路称为。

4.时序逻辑电路在结构方面的特点是:由具有控制作用的电路和具记忆作用电路组成。

、5.、寄存器的作用是用于、、数码指令等信息。

6.按计数过程中数值的增减来分,可将计数器分为为、和三种。

二、选择题1.如题图12.1所示电路为某寄存器的一位,该寄存器为。

A、单拍接收数码寄存器;B、双拍接收数码寄存器;C、单向移位寄存器;D、双向移位寄存器。

2.下列电路不属于时序逻辑电路的是。

A、数码寄存器;B、编码器;C、触发器;D、可逆计数器。

3.下列逻辑电路不具有记忆功能的是。

A、译码器;B、RS触发器;C、寄存器;D、计数器。

4.时序逻辑电路特点中,下列叙述正确的是。

A、电路任一时刻的输出只与当时输入信号有关;B、电路任一时刻的输出只与电路原来状态有关;C、电路任一时刻的输出与输入信号和电路原来状态均有关;D、电路任一时刻的输出与输入信号和电路原来状态均无关。

5.具有记忆功能的逻辑电路是。

A、加法器;B、显示器;C、译码器;D、计数器。

6.数码寄存器采用的输入输出方式为。

A、并行输入、并行输出;B、串行输入、串行输出;C、并行输入、串行输出;D、并行输出、串行输入。

三、判断下面说法是否正确,用“√"或“×"表示在括号1.寄存器具有存储数码和信号的功能。

( )2.构成计数电路的器件必须有记忆能力。

( )3.移位寄存器只能串行输出。

( )4.移位寄存器就是数码寄存器,它们没有区别。

( )5.同步时序电路的工作速度高于异步时序电路。

( )6.移位寄存器有接收、暂存、清除和数码移位等作用。

()思考与练习题时序逻辑电路的特点是什么?时序逻辑电路与组合电路有何区别?在图12.1电路作用下,数码寄存器的原始状态Q3Q2Q1Q0=1001,而输入数码D3D2D1D0=0110时,在CP的作用下,Q3Q2Q1Q0状态如何变化?题图12.2所示移位寄存器的初始状态为111,画出连续3个C P脉冲作用下Q2Q1Q0各端的波形和状态表。

第五章触发器5.1画出如题图5.1所示的基本RS触发器输出端Q、Q的电压波形图。

宁和★的电压波形如图5.1(b) 所示。

解:波形如图:5.2或门组成的基本RS触发器电路如题图5.2(a)所示,己知S和R的波形如题图5.2(b)所示。

试画出Q、3的波形图。

设触发器的初态Q = 0。

题图解:波形如图:5.3题图5.3所示为一个防抖动输出开关电路。

当拨动开关K 时,由于开关接通瞬间发生振颤,R 和S 的波形如图中所示,请画出Q 和Q 端的对应波形。

解:波形如图: 5.4有一时钟RS 触发器如题图5.4所示,试画出它的输出端。

的波形。

初态Q =0-解:波形如图:(b题图(a) (b)题图5.45.5设具有异步端的主从JK 触发器的初始状态Q =0,输入波形如题图5.5所示,试画出输出端Q 的波形。

CLKk题图5.5解:波形如图:CLK5.6设题图5.6的初始状态为0 21 Qo =000,在脉冲CLK 作用下,画出0、0、0的波形(所用 器件都是CD4013)o S D 、R D 分别是CD4013高电平有效的异步置1端,置。

端。

题图5.6解:波形如图:I II I I II I I I(-1__L-. I I --I_L-I I —I__L-1 1 1 1 1 1 0 1 1 1 Illi 1 -J_L- 1 Illi Illi —r i i H — i i i 1(-J__L- 1 1 1 1 1 1 -Hi i /III K I 1 1 1 1 1 1 1 1 o : | | IIII IIII i -i―i - i IIII i i i U_ i i i i i ii -i —i — i i i i i i t; ; 1 1 1 1 1 01 I IIII i [ i i i i —i i—i i ii i.1 1」 1 1 1 IIII IIII IIII1 1 11 1 1 1 1 1 oljiiii i i i i iiiii i ! i i i , 1 1 1——1tnmjwwi.,r -: ~: ~: : ~: ~: ~: ~: ~: ~: ~: ~: ~: ~~: ~: t5.7设题图5.7电路两触发器初态均为0,试画出0、0波形图。

第8章 触发器和时序逻辑电路及其应用习题解答8.1 已知基本RS 触发器的两输入端D S 和D R 的波形如图8-33所示,试画出当基本RS 触发器初始状态分别为0和1两种情况下,输出端Q的波形图。

图8-33 习题8.1图解:根据基本RS 触发器的真值表可得:初始状态为0和1两种情况下,Q的输出波形分别如下图所示:习题8.1输出端Q的波形图8.2 已知同步RS 触发器的初态为0,当S 、R 和CP 的波形如图8-34所示时,试画出输出端Q的波形图。

图8-34 题8.2图解:根据同步RS 触发器的真值表可得:初始状态为0时,Q的输出波形分别如下图所示:习题8.2输出端Q的波形图8.3 已知主从JK触发器的输入端CP、J和K的波形如图8-35所示,试画出触发器初始状态分别为0时,输出端Q的波形图。

图8-35 习题8.3图解:根据主从JK触发器的真值表可得:初始状态为0情况下,Q的输出波形分别如下图所示:习题8.3输出端Q的波形图8.4 已知各触发器和它的输入脉冲CP的波形如图8-36所示,当各触发器初始状态均为1时,试画出各触发器输出Q端和Q端的波形。

图8-36 习题8.4图解:根据逻辑图及触发器的真值表或特性方程,且将驱动方程代入特性方程可得状态方程。

即:(a )J =K =1;Qn +1=n Q,上升沿触发 (b)J =K =1;Qn +1=n Q, 下降沿触发 (c)K =0,J =1;Qn +1=J n Q+K Qn =1,上升沿触发 (d)K =1,J =n Q;Qn +1=J n Q+K Qn =n Qn Q+0·Qn =n Q,上升沿触发 (e)K =Qn ,J =n Q;Qn +1=J n Q+K Qn =n Qn Q+0=n Q,上升沿触发 (f)K =Qn ,J =n Q;Qn +1=J n Q+K Qn =n Qn Q+0=n Q,下降沿触发, 再根据边沿触发器的触发翻转时刻,可得当初始状态为1时,各个电路输出端Q的波形分别如图(a )、(b )、(c )、(d )、(e )和(f )所示,其中具有计数功能的是:(a )、(b )、(d )、(e )和(f )。

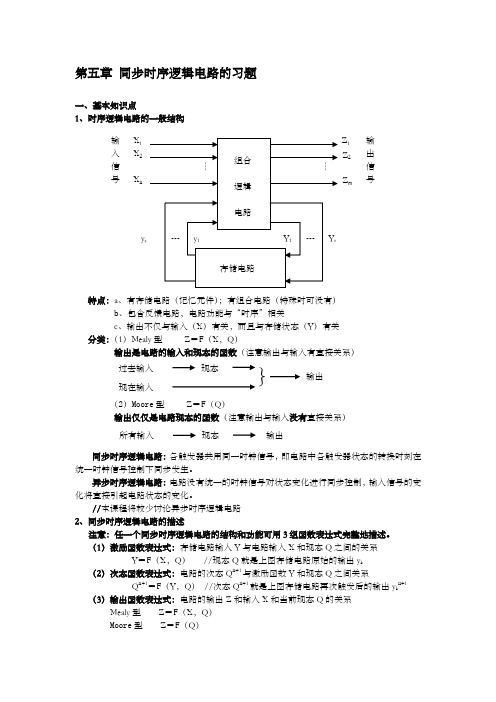

第五章 同步时序逻辑电路的习题一、基本知识点1、时序逻辑电路的一般结构特点:a 、有存储电路(记忆元件);有组合电路(特殊时可没有) b 、包含反馈电路,电路功能与“时序”相关c 、输出不仅与输入(X )有关,而且与存储状态(Y )有关 分类:(1)Mealy 型 Z =F (X ,Q )输出是电路的输入和现态的函数(注意输出与输入有直接关系)(2)Moore 型 Z =F (Q )输出仅仅是电路现态的函数(注意输出与输入没有直接关系)同步时序逻辑电路:各触发器共用同一时钟信号,即电路中各触发器状态的转换时刻在统一时钟信号控制下同步发生。

异步时序逻辑电路:电路没有统一的时钟信号对状态变化进行同步控制,输入信号的变化将直接引起电路状态的变化。

//本课程将较少讨论异步时序逻辑电路 2、同步时序逻辑电路的描述注意:任一个同步时序逻辑电路的结构和功能可用3组函数表达式完整地描述。

(1)激励函数表达式:存储电路输入Y 与电路输入X 和现态Q 之间的关系 Y =F (X ,Q ) //现态Q 就是上图存储电路原始的输出y k (2)次态函数表达式:电路的次态Q n+1与激励函数Y 和现态Q 之间关系Q n+1=F (Y ,Q ) //次态Q n+1就是上图存储电路再次触发后的输出y k n+1 (3)输出函数表达式:电路的输出Z 和输入X 和当前现态Q 的关系 Mealy 型 Z =F (X ,Q ) Moore 型 Z =F (Q )输入信号 输出信号X 1 X 2 X n Z 1 Z 2 Z m y s 过去输入 现态现在输入 }输出 输出所有输入 现态状态表的格式Mealy 型 Moore 型状态图的画法 Mealy 型Moore 型3、同步时序逻辑电路分析 (1)表格法的分析步骤a 、根据电路写出输出表达式和激励函数表达式b 、列出各自的激励矩阵,确定电路相应的次态c 、作出给定电路的状态表和状态图d 、拟定一个典型输入序列,画出时间图,描述此电路的功能 (2)代数法的分析步骤a 、根据电路写出输出表达式和激励函数表达式b 、把激励函数代入次态方程,导出次态方程组c 、根据此方程组,作出状态表和状态图d 、拟定一个典型输入序列,画出时间图,描述此电路的功能 注意:上述两种分析方法的b 、c 两步骤不同 4、同步时序逻辑电路设计 步骤:(1)形成原始的状态图和状态表y n+1/ y输入X 次态 / 输出 现 态 次 态现 态 Zy n+1y输入X输 出y n+1yx / Zy n+1 Zy n+1 / x(2)对原始的状态进行化简,变成最简状态,降低电路复杂度和成本 (3)把状态与二进制代码相对应,即决定触发器的个数(4)确定激励函数(对应触发器的种类)和输出函数(对应逻辑电路的种类),并画出逻辑电路图5、常用的时序电路(1)计数器 周期性的状态循环按进制可分为:二进制计数器、BCD 码计数器、任意进制计数器(楼两种存在无效状态) 按时钟输入方式:同步计数器、异步计数器 按趋势可分为:加“1”计数器、减“1”计数器 * 同步二进制计数器(3位数值,即3个触发器)用3个JK 触发器实现,电路图如下所示(输入端悬空为信号“1”)驱动方程 J 0 = K 0 =1 (Q 0触发器的输入控制) J 1 = K 1 =Q 0 (Q 1触发器的输入控制) J 2 = K 2 =Q 0 Q 1 (Q 2触发器的输入控制)输出方程 Z =(Q 2 Q 1 Q 0) 三个触发器的输出端原相直接输出 输出波形如下所示说明:Q 0触发器按时钟Cp 触发,每一个时钟Q 0触发器翻转一次Q 1触发器接收Q 0触发器的原相输出,当Q 0原相输出为1后才翻转一次Q 2触发器接收Q 0和Q 1原相输出相与之后的结果,只有前两者输出均为1后才翻转一次Cp Q 0 Q 1 Q 2 001 010 011 100 101 110 111 000* 异步二进制计数器也用3个JK 触发器实现,CR 为清零端,电路图如下所示(3个JK 触发器的输入端均悬空)驱动方程同上(略)输出波形如下所示(对比同步计数器,看看异同)注意:如反向输出则为加“1”计数(1)寄存器 多个触发器的并行操作,可以暂存数据信息* 数据寄存器(4位数值,即4个触发器)用D 触发器来实现,电路图如下所示* 移位寄存器(输入可并行亦可串行,输出可并行亦可串行)各位之间存在传递关系Cp Q 0 Q 1 Q 2 111 110 101 100 011 010 001CpCp数据输入端(存储4位数据)Cp数据输入端(存储4位数据)* 移位寄存器(各位之间存在传递关系,且首位和末位也存在传递关系)注意:前面示意的均为左移位,如右移位,传递关系相反二、相关习题**填空题 1、时序逻辑电路按其状态改变是否受统一定时信号控制,可分为( )和( )两种类型。

数字电路第四章答案【篇一:数字电路答案第四章时序逻辑电路2】p=1,输入信号d被封锁,锁存器的输出状态保持不变;当锁存命令cp=0,锁存器输出q?d,q=d;当锁存命令cp出现上升沿,输入信号d被封锁。

根据上述分析,画出锁存器输出q及 q的波形如习题4.3图(c)所示。

习题4.4 习题图4.4是作用于某主从jk触发器cp、j、k、 rd及 sd 端的信号波形图,试绘出q端的波形图。

解:主从jk触发器的 rd、且为低有效。

只有当rd?sd?1 sd端为异步清零和复位端,时,在cp下降沿的作用下,j、k决定输出q状态的变化。

q端的波形如习题4.4图所示。

习题4.5 习题4.5图(a)是由一个主从jk触发器及三个非门构成的“冲息电路”,习题4.5图(b)是时钟cp的波形,假定触发器及各个门的平均延迟时间都是10ns,试绘出输出f的波形。

cpf cp100ns10nsq(a)f30ns10ns(b)(c)习题4.5图解:由习题4.5图(a)所示的电路连接可知:sd?j?k?1,rd?f。

当rd?1时,在cp下降沿的作用下,且经过10 ns,状态q发生翻转,再经过30ns,f发生状态的改变,f?q。

rd?0时,经过10ns,状态q=0。

根据上述对电路功能的分析,得到q和f的波形如习题4.5图(c)所示。

习题4.6 习题4.6图(a)是一个1检出电路,图(b)是cp及j端的输入波形图,试绘出 rd端及q端的波形图(注:触发器是主从触发器,分析时序逻辑图时,要注意cp=1时主触发器的存储作用)。

cpj(a)qd(c)cp j(b)习题图解:分析习题4.6图(a)的电路连接:sd?1,k?0,rd?cp?q;分段分析习题4.6图(b)所示cp及j端信号波形。

(1)cp=1时,设q端初态为0,则rd?1。

j信号出现一次1信号,即一次变化的干扰,且k=0,此时q端状态不会改变;(2)cp下降沿到来,q端状态变为1,rd?cp,此时cp=0,异步清零信号无效;(3)cp出现上升沿,产生异步清零信号,使q由1变为0,在很短的时间里 rd又恢复到1;(4)同理,在第2个cp=1期间,由于j信号出现1信号,在cp下降沿以及上升沿到来后,电路q端和 rd端的变化与(2)、(3)过程的分析相同,其波形如习题4.6图(c)所示。

第一章逻辑门电路§1-1 基本门电路一、填空题1.与逻辑;Y=A·B2.或逻辑;Y=A+B3.非逻辑;Y=4.与;或;非二、选择题1. A2. C3. D三、综合题1.2.真值表逻辑函数式Y=ABC§1-2 复合门电路一、填空题1.输入逻辑变量的各种可能取值;相应的函数值排列在一起2.两输入信号在它们;异或门电路3.并;外接电阻R;线与;线与;电平4.高电平;低电平;高阻态二、选择题1. C2. B3. C4. D5. B三、综合题1.2.真值表逻辑表达式Y1=ABY2=Y3==A+B 逻辑符号3.第二章组合逻辑电路§2-1 组合逻辑电路的分析和设计一、填空题1.代数;卡诺图2.n;n;原变量;反变量;一;一3.与或式;1;04.组合逻辑电路;组合电路;时序逻辑电路;时序电路5.该时刻的输入信号;先前的状态二、选择题1. D2. C3. C4. A5. A三、判断题1. ×2. √3. √4. √5. ×6. √四、综合题1.略2.(1)Y=A+B(2)Y=A B+A B(3) Y=ABC+A+B+C+D=A+B+C+D3. (1) Y=A B C+A B C+ A B C + ABC=A C+AC(2) Y=A CD+A B D+AB D+AC D(3) Y=C+A B+ A B4. (a)逻辑函数式Y= Y=AB+A B真值表逻辑功能:相同出1,不同出0 (b)逻辑函数式Y=AB+BC+AC真值表逻辑功能:三人表决器5.状态表逻辑功能:相同出1,不同出0逻辑图1. 6.Y=A ABC+B ABC+C ABC判不一致电路,输入不同,输出为1,;输入相同,输出为0。

§2-2 加法器一、填空题1.加数与被加数;低位产生的进位2.加数与被加数;低位产生的进位3.加法运算二、选择题1. A2. C三、综合题1.略2.略3.§2-3 编码器与比较器一、填空题1. 编码2. 101011;010000113. 十;二;八;十六4. 0;1;逢二进一;10;逢十进一5. 二进制编码器;二—十进制编码器6. 两个数大小或相等7. 高位二、选择题1. A2. B3. C4. B三、综合题1.略2.(1)10111;00100011(2)00011001;19(3)583. (1)三位二进制(2)1,1,0(3)1,1,14.§2-4 译码器与显示器一、填空题1. 编码器;特定含意的二进制代码按其原意;输出信号;电位;解码器2. 二进制译码器;二—十进制译码器;显示译码器3. LED数字显示器;液晶显示器;荧光数码管显示器4. 1.5~3;10mA/段左右5. 共阴极显示译码器;共阳极显示译码器;液晶显示译码器二、选择题1. A;D2. A三、判断题1.√2.×3.×4.√5.√四、综合题七段显示译码器真值表f=D C B A +D C B A +D C B A+D CB A +D C B A +D C B A =D+B A +C A +C B =DB AC AC B§2-5 数据选择器与分配器一、填空题1.多路调制器;一只单刀多掷选择开关;地址输入;数字信息;输出端2.从四路数据中,选择一路进行传输的数据选择器3.地址选择;输出端二、选择题1. D2. A;C三、判断题1. √2. ×四、综合题1.略2. Y=A B D0+A BD1+A B D2+ABD3第三章触发器§3-1 基本RS触发器与同步RS触发器一、填空题1.两个;已转换的稳定状态2.R S+RSQ n;R+S=13. R S Q n+ R S;RS=04.置0;置15.相同;低电平;高电平6.时钟信号CP7.D触发器8.空翻二、选择题1.D2.B3.A4.B5.B6.D三、判断题1. ×2. ×3. √4. ×5. ×6. ×四、综合题1.略2.3.4.5.略§3-2主从触发器与边沿触发器一、填空题1.空翻2.置0、置1、保持、翻转3.D、J Q n+K Q n4.保持、置1、清0、翻转5.电平、主从6.一次变化7.边沿触发器8.不同、做成9.置0、置1、时钟脉冲二、选择题1.A2.A3.D4.B5.A6.C7.D8.B9.A10.D三、判断题1. √2. ×3. ×4. ×5. √6. ×7. √8. √四、综合题1.2.3.4.略5.略6.§3-3触发器的分类与转换一、填空题1.T、T'2. T Q n+ T Q n、Q n3.1、04. Q n、Q n5. 16. T'7. T8. T'二、选择题1.D2.D3.D4.B5.B三、判断题1. ×2. ×3. ×4. ×四、分析解答题1.2.3.略4.略5.略第四章时序逻辑电路§4-1 寄存器一、填空题1.输入信号;锁存信号2.接收;暂存;传递;数码;移位二、选择题1. C2. B;A三、判断题1. √2. ×3. √四、综合题1.JK触发器构成D触发器,即Q n+1= D。

第五章时序逻辑电路练习题及答案[]分析图时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,说明电路能否自启动。

图[解]驱动方程:丿广心=2, 状态方程:Q;J00" +型0 =型㊉G:厶=©=©, er = +Q-Q"=0 ㊉er ;、=Q、QJ 电Q;Q:l人=G0,K输出方程:Y = Q^由状态方程可得状态转换表,如表所示;由状态转换表可得状态转换图,如图所示。

电路可以自启动。

表Q3Q2Q1/YRpi(00 _»_(110)Vo/I J图电路的逻辑功能:是一个五进制计数器,计数顺序是从0到4循[]试分析图时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出 电路的状态转换图。

A 为输入逻辑变量。

>C1il 1D |y >ci p-1CP1Q2图[解]_驱动方程:D] = AQ 2, D 2 = AQ.Q 2 状态方程:ft"1=,0广=4議=4(0;'+0")由状态方程可得状态转换表,如表所示;由状态转换表町得 状态转换图,如图所示。

电路的逻辑功能是:判断A 是否连续输入四个和四个以上“1” 信号,是则Y=l,否则Y=0。

Q2Q1 A/Y佗0Y0 0 0 0 10 0 0 1 1 0 0 0 1 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 1 1 1 1 1 0 0 1 1 00 1 0 1 0 10 0[] 试分析图时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画 出电路的状态转换图,检查电路能否自启动。

r-0Q1TF1^=O->C1 1KCP[解]J严殛3, K 严1;J 2=Q lt K 严玆;=巫・g ; er 1= ae 2+me 2;丿3 = Q1Q29 位=Q 2Qr=Q.QA^QAY= O2O3电路的状态转换图如图所示,电路能够自启动。

第4,5章触发器,时序逻辑电路习题答案...第4章触发器4.3 若在图4.5电路中的CP、S、R输入端,加入如图4.27所示波形的信号,试画出其Q和Q 端波形,设初态Q=0。

CPSR图4.27 题4.3图解:图4.5电路为同步RS触发器,分析作图如下:CPSRQ4.5 设图4.28中各触发器的初始状态皆为Q=0,画出在CP脉冲连续作用下个各触发器输出端的波形图。

Q 11J 1C11KCP●Q 3>CP1T C11J C11KCPQ 2●>>1D C1Q 61JC11K>●Q 4CP1S 1RQ 5C1●●CP图4.28 题4.5图解:Q Q nn 111=+ Q Q n n 212=+ Q Q nn 313=+Q Q n n 414=+Q Q nn 515=+Q Q n n 616=+Q 1CP Q 2Q 3Q 4Q 5Q 64.6 试写出 图4.29(a)中各触发器的次态函数(即Q 1 n+1 、 Q 2 n+1与现态和输入变量之间的函数式),并画出在图4.29(b )给定信号的作用下Q 1 、Q 2的波形。

假定各触发器的初始状态均为Q =0。

1&≥1CPA B 1S C11R>CP>1D C1=1A BQ 1Q 2Q 2(a)BA(b)图4.29 题4.6图解:由图可见:Q B A AB Q n n 111)(++=+ B A Q n ⊕=+12B A Q 2Q 14.7 图4.30(a )、(b )分别示出了触发器和逻辑门构成的脉冲分频电路,CP 脉冲如图4.30(c )所示,设各触发器的初始状态均为0。

(1)试画出图(a )中的Q 1、Q 2和F 的波形。

(2)试画出图(b )中的Q 3、Q 4和Y 的波形。

≥111D>C11D>C1Y(b )(c )CP=1>1D >1D RC1Q 1Q 2F (a )C1Q Q Q 4Q 3Q Q图4.30 题4.7图解: (a )Q Q nn 211=+ Q Q nn 112=+ Q F 1CP ⊕= R 2 = Q 1低电平有效CPQ 1Q 2F(b )Q Q Q n n n 4313=+ Q Q Q n n n 4314=+ Q Q Y n n 43=CP 3= CP 上降沿触发 CP 4= CP 下降沿触发CPQ 3Q 4Y4.8 电路如图4.31所示,设各触发器的初始状态均为0。

已知CP 和A 的波形,试分别画出Q 1、Q 2的波形。

>1J >1J 1KC1CPC1Q Q =1Q 2Q 11KA 1ACP图4.31 题4.8图解:由图可见Q Q n n 111=+Q Q A Q n n n 2112⊕⊕=+ACPQ 1Q 24.9 电路如图4.32所示,设各触发器的初始状态均为0。

已知CP 1、CP 2的波形如图示,试分别画出Q 1、Q 2的波形。

1D >C11D >C1CP 1Q 2QQ 1R 1RQ 1CP 2QCP 1CP 2图4.32 题4.9图解:111=+Q n 112=+Q n Q R D 21= Q R D 12=CP 1CP 2Q 1Q 2第5章 时序逻辑电路5.1 分析图5.39时序电路的逻辑功能,写出电路的驱动方程、状态方程,设各触发器的初始状态为0,画出电路的状态转换图,说明电路能否自启动。

FF 0FF 11J C11K1J C11K 1J C11K ●●CP1●FF 2Q 0Q 1Q 2●图5.39 题5.1图解: 驱动方程:J 0=K 0=1, J 1=K 1=Q 0, J 2=K 2=Q 0Q 1状态方程:Q Q n n 010=+,Q Q Q Q Qn n n n n 101011+=+,Q Q Q Q Q Q Q n n n n n n n 2121012+=+状态转换图:110111101010001000Q 0Q 2Q 1100功能:同步三位二进制加法计数器,可自启动 。

5.5 用JK 触发器和门电路设计满足图5.43所示要求的两相脉冲发生电路。

图5.43 题5.5图解: 分析所给波形,可分为4个状态,00、01、11、01、00,由于有2个状态相同但次态不同,在实现途径上采用设计一个4进制计数器,再通过译码实现。

计数器采用同步二进制加法计数器,其状态方程如下:Q Q n n 010=+ Q Q QQ Q nn n 101011+=+采用JK 触发器,把上述状态方程与其特性方程比较系数,可见J 0=K 0=1,J 1=K 1= Q 0,设计电路如下:11JC11K1JC11KFF1 FF0CP 1Q0Q1>1&Y01分析图示电路,可得其工作波形如下所示,可见满足题目要求。

CPQQ1YY15.6 试用双向移位寄存器74194构成6位扭环计数器。

解:作状态转换图如下:用74194实现,首先扩展成8位移位寄存器;其次反馈形成扭环形计数器;解决启动的方法可采用清零或者置数法。

此处采用清零法。

5.7 由74290构成的计数器如图5.44所示,分析它们各为几进制计数器。

图5.44 题5.7图解:CP1=CP, S91= S92=0,R01= R02= Q3。

电路的基本连接形式是5进制计数器,采用反馈清零法形成4进制计数器。

其状态转换图如下:C P1=CP, S91= S92=0,R01= Q1 ,R02=Q2。

电路的基本连接形式是5进制计数器,采用反馈清零法形成3进制计数器。

其状态转换图如下:C P0=CP, CP1= Q0,S91= S92=0,R01=R02= Q3。

电路的基本连接形式是10进制计数器,采用反馈清零法形成8进制计数器。

其状态转换图如下:C P0=CP, CP1= Q0,S91= S92=0,R01= Q0,R02= Q3。

电路的基本连接形式是10进制计数器,采用反馈清零法形成9进制计数器。

其状态转换图如下:5.8 试画出图5.45所示电路的完整状态换图。

图5.45 题5.8图解:EP=ET= 1,RD=1,LD= Q2,DCBA=Q3100。

电路采用反馈置数法,且2次所置的数不同。

采用反馈置数法形成10进制计数器。

其状态转换图如下:试用74161设计一个计数器,其计数状态为0111~1111。

解: 作状态转换图,并作电路图如下:5.10 试分析图5.46所示电路,画出它的状态图,说明它是几进制计数器。

图5.46 题5.10图解: 分析图示电路,可见采用反馈清零法实现10进制计数器,其状态转换图如下:5.11 试用74160构成二十四进制计数器,要求采用两种不同的方法。

解:74160为同步10进制加法计数器,功能表及管脚与74161相同。

实现24进制计数器的途径是:先用2片74160扩展为100进制计数器,然后采用反馈清零法或者反馈置数法实现24进制计数器。

反馈清零法:LD=1,反馈置数法:RD=1,DCBA=0000讨论:也可用74160分别实现4进制和6进制计数器,然后级联;或者分别实现3进制和8进制计数器,然后级联。

5.12 试设计一个能产生011100111001110的序列脉冲发生器。

解:采用计数器+数据选择器的实现途径。

按题意应有一个15进制计数器和一个16选1数据选择器。

计数器采用74161通过反馈置数法实现,数据选择器采用2片74151扩展构成。

电路图如下:5.13 设计一个灯光控制逻辑电路。

要求红、绿、黄三种颜色的灯在时钟信号作用下按表5.14规定的顺序转换状态。

表中的1表示灯“亮”,0表示灯“灭”。

解:分析题目要求,方案一可用8进制计数器和3个数据选择器实现;方案二用计数器和门电路实现。

此处采用方案二设计电路如下。

5.14 试用JK触发器和与非门设计一个11进制加计数器。

解:作状态转换表如下:K0=15.15 试用JK触发器(具有异步清零功能)和门电路采用反馈清零法设计一个9进制计数器。

解:依据题意,先用4个JK触发器组成4位二进制计数器,然后利用反馈清零法实现9进制计数器。

上述电路存在的问题是:如果FF0或者FF3先清零,则RD端的清零信号消失,FF1、FF2可能达不到清零的目的。

改进的电路如下图所示,电路中利用了基本RS触发器的记忆功能。