Better External Memory Suffix Array Construction

- 格式:pdf

- 大小:204.13 KB

- 文档页数:12

人工智能是一门新兴的具有挑战力的学科。

自人工智能诞生以来,发展迅速,产生了许多分支。

诸如强化学习、模拟环境、智能硬件、机器学习等。

但是,在当前人工智能技术迅猛发展,为人们的生活带来许多便利。

下面是搜索整理的人工智能英文参考文献的分享,供大家借鉴参考。

人工智能英文参考文献一:[1]Lars Egevad,Peter Str?m,Kimmo Kartasalo,Henrik Olsson,Hemamali Samaratunga,Brett Delahunt,Martin Eklund. The utility of artificial intelligence in the assessment of prostate pathology[J]. Histopathology,2020,76(6).[2]Rudy van Belkom. The Impact of Artificial Intelligence on the Activities ofa Futurist[J]. World Futures Review,2020,12(2).[3]Reza Hafezi. How Artificial Intelligence Can Improve Understanding in Challenging Chaotic Environments[J]. World Futures Review,2020,12(2).[4]Alejandro Díaz-Domínguez. How Futures Studies and Foresight Could Address Ethical Dilemmas of Machine Learning and Artificial Intelligence[J]. World Futures Review,2020,12(2).[5]Russell T. Warne,Jared Z. Burton. Beliefs About Human Intelligence in a Sample of Teachers and Nonteachers[J]. Journal for the Education of the Gifted,2020,43(2).[6]Russell Belk,Mariam Humayun,Ahir Gopaldas. Artificial Life[J]. Journal of Macromarketing,2020,40(2).[7]Walter Kehl,Mike Jackson,Alessandro Fergnani. Natural Language Processing and Futures Studies[J]. World Futures Review,2020,12(2).[8]Anne Boysen. Mine the Gap: Augmenting Foresight Methodologies with Data Analytics[J]. World Futures Review,2020,12(2).[9]Marco Bevolo,Filiberto Amati. The Potential Role of AI in Anticipating Futures from a Design Process Perspective: From the Reflexive Description of “Design” to a Discussion of Influences by the Inclusion of AI in the Futures Research Process[J]. World Futures Review,2020,12(2).[10]Lan Xu,Paul Tu,Qian Tang,Dan Seli?teanu. Contract Design for Cloud Logistics (CL) Based on Blockchain Technology (BT)[J]. Complexity,2020,2020.[11]L. Grant,X. Xue,Z. Vajihi,A. Azuelos,S. Rosenthal,D. Hopkins,R. Aroutiunian,B. Unger,A. Guttman,M. Afilalo. LO32: Artificial intelligence to predict disposition to improve flow in the emergency department[J]. CJEM,2020,22(S1).[12]A. Kirubarajan,A. Taher,S. Khan,S. Masood. P071: Artificial intelligence in emergency medicine: A scoping review[J]. CJEM,2020,22(S1).[13]L. Grant,P. Joo,B. Eng,A. Carrington,M. Nemnom,V. Thiruganasambandamoorthy. LO22: Risk-stratification of emergency department syncope by artificial intelligence using machine learning: human, statistics or machine[J]. CJEM,2020,22(S1).[14]Riva Giuseppe,Riva Eleonora. OS for Ind Robots: Manufacturing Robots Get Smarter Thanks to Artificial Intelligence.[J]. Cyberpsychology, behavior and social networking,2020,23(5).[15]Markus M. Obmann,Aurelio Cosentino,Joshy Cyriac,Verena Hofmann,Bram Stieltjes,Daniel T. Boll,Benjamin M. Yeh,Matthias R. Benz. Quantitative enhancement thresholds and machine learning algorithms for the evaluation of renal lesions using single-phase split-filter dual-energy CT[J]. Abdominal Radiology,2020,45(1).[16]Haytham H. Elmousalami,Mahmoud Elaskary. Drilling stuck pipe classification and mitigation in the Gulf of Suez oil fields using artificial intelligence[J]. Journal of Petroleum Exploration and Production Technology,2020,10(10).[17]Rüdiger Schulz-Wendtland,Karin Bock. Bildgebung in der Mammadiagnostik –Ein Ausblick <trans-title xml:lang="en">Imaging in breast diagnostics—an outlook [J]. Der Gyn?kologe,2020,53(6).</trans-title>[18]Nowakowski Piotr,Szwarc Krzysztof,Boryczka Urszula. Combining an artificial intelligence algorithm and a novel vehicle for sustainable e-waste collection[J]. Science of the Total Environment,2020,730.[19]Wang Huaizhi,Liu Yangyang,Zhou Bin,Li Canbing,Cao Guangzhong,Voropai Nikolai,Barakhtenko Evgeny. Taxonomy research of artificial intelligence for deterministic solar power forecasting[J]. Energy Conversion and Management,2020,214.[20]Kagemoto Hiroshi. Forecasting a water-surface wave train with artificial intelligence- A case study[J]. Ocean Engineering,2020,207.[21]Tomonori Aoki,Atsuo Yamada,Kazuharu Aoyama,Hiroaki Saito,Gota Fujisawa,Nariaki Odawara,Ryo Kondo,Akiyoshi Tsuboi,Rei Ishibashi,Ayako Nakada,Ryota Niikura,Mitsuhiro Fujishiro,Shiro Oka,Soichiro Ishihara,Tomoki Matsuda,Masato Nakahori,Shinji Tanaka,Kazuhiko Koike,Tomohiro Tada. Clinical usefulness of a deep learning‐based system as the first screening on small‐bowel capsule endoscopy reading[J]. Digestive Endoscopy,2020,32(4).[22]Masashi Fujii,Hajime Isomoto. Next generation of endoscopy: Harmony with artificial intelligence and robotic‐assisted devices[J]. Digestive Endoscopy,2020,32(4).[23]Roberto Verganti,Luca Vendraminelli,Marco Iansiti. Innovation and Design in the Age of Artificial Intelligence[J]. Journal of Product Innovation Management,2020,37(3).[24]Yuval Elbaz,David Furman,Maytal Caspary Toroker. Modeling Diffusion in Functional Materials: From Density Functional Theory to Artificial Intelligence[J]. Advanced Functional Materials,2020,30(18).[25]Dinesh Visva Gunasekeran,Tien Yin Wong. Artificial Intelligence in Ophthalmology in 2020: A Technology on the Cusp for Translation and Implementation[J]. Asia-Pacific Journal of Ophthalmology,2020,9(2).[26]Fu-Neng Jiang,Li-Jun Dai,Yong-Ding Wu,Sheng-Bang Yang,Yu-Xiang Liang,Xin Zhang,Cui-Yun Zou,Ren-Qiang He,Xiao-Ming Xu,Wei-De Zhong. The study of multiple diagnosis models of human prostate cancer based on Taylor database by artificial neural networks[J]. Journal of the Chinese Medical Association,2020,83(5).[27]Matheus Calil Faleiros,Marcello Henrique Nogueira-Barbosa,Vitor Faeda Dalto,JoséRaniery Ferreira Júnior,Ariane Priscilla Magalh?es Tenório,Rodrigo Luppino-Assad,Paulo Louzada-Junior,Rangaraj Mandayam Rangayyan,Paulo Mazzoncini de Azevedo-Marques. Machine learning techniques for computer-aided classification of active inflammatory sacroiliitis in magnetic resonance imaging[J]. Advances in Rheumatology,2020,60(1078).[28]Balamurugan Balakreshnan,Grant Richards,Gaurav Nanda,Huachao Mao,Ragu Athinarayanan,Joseph Zaccaria. PPE Compliance Detection using Artificial Intelligence in Learning Factories[J]. Procedia Manufacturing,2020,45.[29]M. Stévenin,V. Avisse,N. Ducarme,A. de Broca. Qui est responsable si un robot autonome vient à entra?ner un dommage ?[J]. Ethique et Santé,2020.[30]Fatemeh Barzegari Banadkooki,Mohammad Ehteram,Fatemeh Panahi,Saad Sh. Sammen,Faridah Binti Othman,Ahmed EL-Shafie. Estimation of Total Dissolved Solids (TDS) using New Hybrid Machine Learning Models[J]. Journal of Hydrology,2020.[31]Adam J. Schwartz,Henry D. Clarke,Mark J. Spangehl,Joshua S. Bingham,DavidA. Etzioni,Matthew R. Neville. Can a Convolutional Neural Network Classify Knee Osteoarthritis on Plain Radiographs as Accurately as Fellowship-Trained Knee Arthroplasty Surgeons?[J]. The Journal of Arthroplasty,2020.[32]Ivana Nizetic Kosovic,Toni Mastelic,Damir Ivankovic. Using Artificial Intelligence on environmental data from Internet of Things for estimating solar radiation: Comprehensive analysis[J]. Journal of Cleaner Production,2020.[33]Lauren Fried,Andrea Tan,Shirin Bajaj,Tracey N. Liebman,David Polsky,Jennifer A. Stein. Technological advances for the detection of melanoma: Part I. Advances in diagnostic techniques[J]. Journal of the American Academy of Dermatology,2020.[34]Mohammed Amoon,Torki Altameem,Ayman Altameem. Internet of things Sensor Assisted Security and Quality Analysis for Health Care Data Sets Using Artificial Intelligent Based Heuristic Health Management System[J]. Measurement,2020.[35]E. Lotan,C. Tschider,D.K. Sodickson,A. Caplan,M. Bruno,B. Zhang,Yvonne W. Lui. Medical Imaging and Privacy in the Era of Artificial Intelligence: Myth, Fallacy, and the Future[J]. Journal of the American College of Radiology,2020.[36]Fabien Lareyre,Cédric Adam,Marion Carrier,Juliette Raffort. Artificial Intelligence in Vascular Surgery: moving from Big Data to Smart Data[J]. Annals of Vascular Surgery,2020.[37]Ilesanmi Daniyan,Khumbulani Mpofu,Moses Oyesola,Boitumelo Ramatsetse,Adefemi Adeodu. Artificial intelligence for predictive maintenance in the railcar learning factories[J]. Procedia Manufacturing,2020,45.[38]Janet L. McCauley,Anthony E. Swartz. Reframing Telehealth[J]. Obstetrics and Gynecology Clinics of North America,2020.[39]Jean-Emmanuel Bibault,Lei Xing. Screening for chronic obstructive pulmonary disease with artificial intelligence[J]. The Lancet Digital Health,2020,2(5).[40]Andrea Laghi. Cautions about radiologic diagnosis of COVID-19 infection driven by artificial intelligence[J]. The Lancet Digital Health,2020,2(5).人工智能英文参考文献二:[41]K. Orhan,I. S. Bayrakdar,M. Ezhov,A. Kravtsov,T. ?zyürek. Evaluation of artificial intelligence for detecting periapical pathosis on cone‐beam computed tomography scans[J]. International Endodontic Journal,2020,53(5).[42]Avila A M,Mezi? I. Data-driven analysis and forecasting of highway traffic dynamics.[J]. Nature communications,2020,11(1).[43]Neri Emanuele,Miele Vittorio,Coppola Francesca,Grassi Roberto. Use of CT andartificial intelligence in suspected or COVID-19 positive patients: statement of the Italian Society of Medical and Interventional Radiology.[J]. La Radiologia medica,2020.[44]Tau Noam,Stundzia Audrius,Yasufuku Kazuhiro,Hussey Douglas,Metser Ur. Convolutional Neural Networks in Predicting Nodal and Distant Metastatic Potential of Newly Diagnosed Non-Small Cell Lung Cancer on FDG PET Images.[J]. AJR. American journal of roentgenology,2020.[45]Coppola Francesca,Faggioni Lorenzo,Regge Daniele,Giovagnoni Andrea,Golfieri Rita,Bibbolino Corrado,Miele Vittorio,Neri Emanuele,Grassi Roberto. Artificial intelligence: radiologists' expectations and opinions gleaned from a nationwide online survey.[J]. La Radiologia medica,2020.[46]?. ? ? ? ? [J]. ,2020,25(4).[47]Savage Rock H,van Assen Marly,Martin Simon S,Sahbaee Pooyan,Griffith Lewis P,Giovagnoli Dante,Sperl Jonathan I,Hopfgartner Christian,K?rgel Rainer,Schoepf U Joseph. Utilizing Artificial Intelligence to Determine Bone Mineral Density Via Chest Computed Tomography.[J]. Journal of thoracic imaging,2020,35 Suppl 1.[48]Brzezicki Maksymilian A,Bridger Nicholas E,Kobeti? Matthew D,Ostrowski Maciej,Grabowski Waldemar,Gill Simran S,Neumann Sandra. Artificial intelligence outperforms human students in conducting neurosurgical audits.[J]. Clinical neurology and neurosurgery,2020,192.[49]Lockhart Mark E,Smith Andrew D. Fatty Liver Disease: Artificial Intelligence Takes on the Challenge.[J]. Radiology,2020,295(2).[50]Wood Edward H,Korot Edward,Storey Philip P,Muscat Stephanie,Williams George A,Drenser Kimberly A. The retina revolution: signaling pathway therapies, genetic therapies, mitochondrial therapies, artificial intelligence.[J]. Current opinion in ophthalmology,2020,31(3).[51]Ho Dean,Quake Stephen R,McCabe Edward R B,Chng Wee Joo,Chow Edward K,Ding Xianting,Gelb Bruce D,Ginsburg Geoffrey S,Hassenstab Jason,Ho Chih-Ming,Mobley William C,Nolan Garry P,Rosen Steven T,Tan Patrick,Yen Yun,Zarrinpar Ali. Enabling Technologies for Personalized and Precision Medicine.[J]. Trends in biotechnology,2020,38(5).[52]Fischer Andreas M,Varga-Szemes Akos,van Assen Marly,Griffith L Parkwood,Sahbaee Pooyan,Sperl Jonathan I,Nance John W,Schoepf U Joseph. Comparison of Artificial Intelligence-Based Fully Automatic Chest CT Emphysema Quantification to Pulmonary Function Testing.[J]. AJR. American journal ofroentgenology,2020,214(5).[53]Moore William,Ko Jane,Gozansky Elliott. Artificial Intelligence Pertaining to Cardiothoracic Imaging and Patient Care: Beyond Image Interpretation.[J]. Journal of thoracic imaging,2020,35(3).[54]Hwang Eui Jin,Park Chang Min. Clinical Implementation of Deep Learning in Thoracic Radiology: Potential Applications and Challenges.[J]. Korean journal of radiology,2020,21(5).[55]Mateen Bilal A,David Anna L,Denaxas Spiros. Electronic Health Records to Predict Gestational Diabetes Risk.[J]. Trends in pharmacological sciences,2020,41(5).[56]Yao Xiang,Mao Ling,Lv Shunli,Ren Zhenghong,Li Wentao,Ren Ke. CT radiomics features as a diagnostic tool for classifying basal ganglia infarction onset time.[J]. Journal of the neurological sciences,2020,412.[57]van Assen Marly,Banerjee Imon,De Cecco Carlo N. Beyond the Artificial Intelligence Hype: What Lies Behind the Algorithms and What We Can Achieve.[J]. Journal of thoracic imaging,2020,35 Suppl 1.[58]Guzik Tomasz J,Fuster Valentin. Leaders in Cardiovascular Research: Valentin Fuster.[J]. Cardiovascular research,2020,116(6).[59]Fischer Andreas M,Eid Marwen,De Cecco Carlo N,Gulsun Mehmet A,van Assen Marly,Nance John W,Sahbaee Pooyan,De Santis Domenico,Bauer Maximilian J,Jacobs Brian E,Varga-Szemes Akos,Kabakus Ismail M,Sharma Puneet,Jackson Logan J,Schoepf U Joseph. Accuracy of an Artificial Intelligence Deep Learning Algorithm Implementing a Recurrent Neural Network With Long Short-term Memory for the Automated Detection of Calcified Plaques From Coronary Computed Tomography Angiography.[J]. Journal of thoracic imaging,2020,35 Suppl 1.[60]Ghosh Adarsh,Kandasamy Devasenathipathy. Interpretable Artificial Intelligence: Why and When.[J]. AJR. American journal of roentgenology,2020,214(5).[61]M.Rosario González-Rodríguez,M.Carmen Díaz-Fernández,Carmen Pacheco Gómez. Facial-expression recognition: An emergent approach to the measurement of tourist satisfaction through emotions[J]. Telematics and Informatics,2020,51.[62]Ru-Xi Ding,Iván Palomares,Xueqing Wang,Guo-Rui Yang,Bingsheng Liu,Yucheng Dong,Enrique Herrera-Viedma,Francisco Herrera. Large-Scale decision-making: Characterization, taxonomy, challenges and future directions from an Artificial Intelligence and applications perspective[J]. Information Fusion,2020,59.[63]Abdulrhman H. Al-Jebrni,Brendan Chwyl,Xiao Yu Wang,Alexander Wong,Bechara J. Saab. AI-enabled remote and objective quantification of stress at scale[J]. Biomedical Signal Processing and Control,2020,59.[64]Gillian Thomas,Elizabeth Eisenhauer,Robert G. Bristow,Cai Grau,Coen Hurkmans,Piet Ost,Matthias Guckenberger,Eric Deutsch,Denis Lacombe,Damien C. Weber. The European Organisation for Research and Treatment of Cancer, State of Science in radiation oncology and priorities for clinical trials meeting report[J]. European Journal of Cancer,2020,131.[65]Muhammad Asif. Are QM models aligned with Industry 4.0? A perspective on current practices[J]. Journal of Cleaner Production,2020,258.[66]Siva Teja Kakileti,Himanshu J. Madhu,Geetha Manjunath,Leonard Wee,Andre Dekker,Sudhakar Sampangi. Personalized risk prediction for breast cancer pre-screening using artificial intelligence and thermal radiomics[J]. Artificial Intelligence In Medicine,2020,105.[67]. Evaluation of Payer Budget Impact Associated with the Use of Artificial Intelligence in Vitro Diagnostic, Kidneyintelx, to Modify DKD Progression:[J]. American Journal of Kidney Diseases,2020,75(5).[68]Rohit Nishant,Mike Kennedy,Jacqueline Corbett. Artificial intelligence for sustainability: Challenges, opportunities, and a research agenda[J]. International Journal of Information Management,2020,53.[69]Hoang Nguyen,Xuan-Nam Bui. Soft computing models for predicting blast-induced air over-pressure: A novel artificial intelligence approach[J]. Applied Soft Computing Journal,2020,92.[70]Benjamin S. Hopkins,Aditya Mazmudar,Conor Driscoll,Mark Svet,Jack Goergen,Max Kelsten,Nathan A. Shlobin,Kartik Kesavabhotla,Zachary A Smith,Nader S Dahdaleh. Using artificial intelligence (AI) to predict postoperative surgical site infection: A retrospective cohort of 4046 posterior spinal fusions[J]. Clinical Neurology and Neurosurgery,2020,192.[71]Mei Yang,Runze Zhou,Xiangjun Qiu,Xiangfei Feng,Jian Sun,Qunshan Wang,Qiufen Lu,Pengpai Zhang,Bo Liu,Wei Li,Mu Chen,Yan Zhao,Binfeng Mo,Xin Zhou,Xi Zhang,Yingxue Hua,Jin Guo,Fangfang Bi,Yajun Cao,Feng Ling,Shengming Shi,Yi-Gang Li. Artificial intelligence-assisted analysis on the association between exposure to ambient fine particulate matter and incidence of arrhythmias in outpatients of Shanghai community hospitals[J]. Environment International,2020,139.[72]Fatemehalsadat Madaeni,Rachid Lhissou,Karem Chokmani,Sebastien Raymond,Yves Gauthier. Ice jam formation, breakup and prediction methods based on hydroclimatic data using artificial intelligence: A review[J]. Cold Regions Science and Technology,2020,174.[73]Steve Chukwuebuka Arum,David Grace,Paul Daniel Mitchell. A review of wireless communication using high-altitude platforms for extended coverage and capacity[J]. Computer Communications,2020,157.[74]Yong-Hong Kuo,Nicholas B. Chan,Janny M.Y. Leung,Helen Meng,Anthony Man-Cho So,Kelvin K.F. Tsoi,Colin A. Graham. An Integrated Approach of Machine Learning and Systems Thinking for Waiting Time Prediction in an Emergency Department[J]. International Journal of Medical Informatics,2020,139.[75]Matteo Terzi,Gian Antonio Susto,Pratik Chaudhari. Directional adversarial training for cost sensitive deep learning classification applications[J]. Engineering Applications of Artificial Intelligence,2020,91.[76]Arman Kilic. Artificial Intelligence and Machine Learning in Cardiovascular Health Care[J]. The Annals of Thoracic Surgery,2020,109(5).[77]Hossein Azarmdel,Ahmad Jahanbakhshi,Seyed Saeid Mohtasebi,Alfredo Rosado Mu?oz. Evaluation of image processing technique as an expert system in mulberry fruit grading based on ripeness level using artificial neural networks (ANNs) and support vector machine (SVM)[J]. Postharvest Biology and Technology,2020,166.[78]Wafaa Wardah,Abdollah Dehzangi,Ghazaleh Taherzadeh,Mahmood A. Rashid,M.G.M. Khan,Tatsuhiko Tsunoda,Alok Sharma. Predicting protein-peptide binding sites with a deep convolutional neural network[J]. Journal of Theoretical Biology,2020,496.[79]Francisco F.X. Vasconcelos,Róger M. Sarmento,Pedro P. Rebou?as Filho,Victor Hugo C. de Albuquerque. Artificial intelligence techniques empowered edge-cloud architecture for brain CT image analysis[J]. Engineering Applications of Artificial Intelligence,2020,91.[80]Masaaki Konishi. Bioethanol production estimated from volatile compositions in hydrolysates of lignocellulosic biomass by deep learning[J]. Journal of Bioscience and Bioengineering,2020,129(6).人工智能英文参考文献三:[81]J. Kwon,K. Kim. Artificial Intelligence for Early Prediction of Pulmonary Hypertension Using Electrocardiography[J]. Journal of Heart and Lung Transplantation,2020,39(4).[82]C. Maathuis,W. Pieters,J. van den Berg. Decision support model for effects estimation and proportionality assessment for targeting in cyber operations[J]. Defence Technology,2020.[83]Samer Ellahham. Artificial Intelligence in Diabetes Care[J]. The American Journal of Medicine,2020.[84]Yi-Ting Hsieh,Lee-Ming Chuang,Yi-Der Jiang,Tien-Jyun Chang,Chung-May Yang,Chang-Hao Yang,Li-Wei Chan,Tzu-Yun Kao,Ta-Ching Chen,Hsuan-Chieh Lin,Chin-Han Tsai,Mingke Chen. Application of deep learning image assessment software VeriSee? for diabetic retinopathy screening[J]. Journal of the Formosan Medical Association,2020.[85]Emre ARTUN,Burak KULGA. Selection of candidate wells for re-fracturing in tight gas sand reservoirs using fuzzy inference[J]. Petroleum Exploration and Development Online,2020,47(2).[86]Alberto Arenal,Cristina Armu?a,Claudio Feijoo,Sergio Ramos,Zimu Xu,Ana Moreno. Innovation ecosystems theory revisited: The case of artificial intelligence in China[J]. Telecommunications Policy,2020.[87]T. Som,M. Dwivedi,C. Dubey,A. Sharma. Parametric Studies on Artificial Intelligence Techniques for Battery SOC Management and Optimization of Renewable Power[J]. Procedia Computer Science,2020,167.[88]Bushra Kidwai,Nadesh RK. Design and Development of Diagnostic Chabot for supporting Primary Health Care Systems[J]. Procedia Computer Science,2020,167.[89]Asl? Bozda?,Ye?im Dokuz,?znur Begüm G?k?ek. Spatial prediction of PM 10 concentration using machine learning algorithms in Ankara, Turkey[J]. Environmental Pollution,2020.[90]K.P. Smith,J.E. Kirby. Image analysis and artificial intelligence in infectious disease diagnostics[J]. Clinical Microbiology and Infection,2020.[91]Alklih Mohamad YOUSEF,Ghahfarokhi Payam KAVOUSI,Marwan ALNUAIMI,Yara ALATRACH. Predictive data analytics application for enhanced oil recovery in a mature field in the Middle East[J]. Petroleum Exploration and Development Online,2020,47(2).[92]Omer F. Ahmad,Danail Stoyanov,Laurence B. Lovat. Barriers and pitfalls for artificial intelligence in gastroenterology: Ethical and regulatory issues[J]. Techniques and Innovations in Gastrointestinal Endoscopy,2020,22(2).[93]Sanne A. Hoogenboom,Ulas Bagci,Michael B. Wallace. Artificial intelligence in gastroenterology. The current state of play and the potential. How will it affect our practice and when?[J]. Techniques and Innovations in Gastrointestinal Endoscopy,2020,22(2).[94]Douglas K. Rex. Can we do resect and discard with artificial intelligence-assisted colon polyp “optical biopsy?”[J]. Techniques and Innovations in Gastrointestinal Endoscopy,2020,22(2).[95]Neal Shahidi,Michael J. Bourke. Can artificial intelligence accurately diagnose endoscopically curable gastrointestinal cancers?[J]. Techniques and Innovations in Gastrointestinal Endoscopy,2020,22(2).[96]Michael Byrne. Artificial intelligence in gastroenterology[J]. Techniques and Innovations in Gastrointestinal Endoscopy,2020,22(2).[97]Piet C. de Groen. Using artificial intelligence to improve adequacy of inspection in gastrointestinal endoscopy[J]. Techniques and Innovations in Gastrointestinal Endoscopy,2020,22(2).[98]Robin Zachariah,Andrew Ninh,William Karnes. Artificial intelligence for colon polyp detection: Why should we embrace this?[J]. Techniques and Innovations in Gastrointestinal Endoscopy,2020,22(2).[99]Alexandra T. Greenhill,Bethany R. Edmunds. A primer of artificial intelligence in medicine[J]. Techniques and Innovations in Gastrointestinal Endoscopy,2020,22(2).[100]Tomohiro Tada,Toshiaki Hirasawa,Toshiyuki Yoshio. The role for artificial intelligence in evaluation of upper GI cancer[J]. Techniques and Innovations in Gastrointestinal Endoscopy,2020,22(2).[101]Yahui Jiang,Meng Yang,Shuhao Wang,Xiangchun Li,Yan Sun. Emerging role of deep learning‐based artificial intelligence in tumor pathology[J]. Cancer Communications,2020,40(4).[102]Kristopher D. Knott,Andreas Seraphim,Joao B. Augusto,Hui Xue,Liza Chacko,Nay Aung,Steffen E. Petersen,Jackie A. Cooper,Charlotte Manisty,Anish N. Bhuva,Tushar Kotecha,Christos V. Bourantas,Rhodri H. Davies,Louise A.E. Brown,Sven Plein,Marianna Fontana,Peter Kellman,James C. Moon. The Prognostic Significance of Quantitative Myocardial Perfusion: An Artificial Intelligence–Based Approach Using Perfusion Mapping[J]. Circulation,2020,141(16).[103]Muhammad Asad,Ahmed Moustafa,Takayuki Ito. FedOpt: Towards Communication Efficiency and Privacy Preservation in Federated Learning[J]. Applied Sciences,2020,10(8).[104]Wu Wenzhi,Zhang Yan,Wang Pu,Zhang Li,Wang Guixiang,Lei Guanghui,Xiao Qiang,Cao Xiaochen,Bian Yueran,Xie Simiao,Huang Fei,Luo Na,Zhang Jingyuan,Luo Mingyan. Psychological stress of medical staffs during outbreak of COVID-19 and adjustment strategy.[J]. Journal of medical virology,2020.[105]. Eyenuk Fulfills Contract for Artificial Intelligence Grading of Retinal Images[J]. Telecomworldwire,2020.[106]Kim Tae Woo,Duhachek Adam. Artificial Intelligence and Persuasion: A Construal-Level Account.[J]. Psychological science,2020,31(4).[107]McCall Becky. COVID-19 and artificial intelligence: protecting health-care workers and curbing the spread.[J]. The Lancet. Digital health,2020,2(4).[108]Alca?iz Mariano,Chicchi Giglioli Irene A,Sirera Marian,Minissi Eleonora,Abad Luis. [Autism spectrum disorder biomarkers based on biosignals, virtual reality and artificial intelligence].[J]. Medicina,2020,80 Suppl 2.[109]Cong Lei,Feng Wanbing,Yao Zhigang,Zhou Xiaoming,Xiao Wei. Deep Learning Model as a New Trend in Computer-aided Diagnosis of Tumor Pathology for Lung Cancer.[J]. Journal of Cancer,2020,11(12).[110]Wang Fengdan,Gu Xiao,Chen Shi,Liu Yongliang,Shen Qing,Pan Hui,Shi Lei,Jin Zhengyu. Artificial intelligence system can achieve comparable results to experts for bone age assessment of Chinese children with abnormal growth and development.[J]. PeerJ,2020,8.[111]Hu Wenmo,Yang Huayu,Xu Haifeng,Mao Yilei. Radiomics based on artificial intelligence in liver diseases: where we are?[J]. Gastroenterology report,2020,8(2).[112]Batayneh Wafa,Abdulhay Enas,Alothman Mohammad. Prediction of the performance of artificial neural networks in mapping sEMG to finger joint angles via signal pre-investigation techniques.[J]. Heliyon,2020,6(4).[113]Aydin Emrah,Türkmen ?nan Utku,Namli G?zde,?ztürk ?i?dem,Esen Ay?e B,Eray Y Nur,Ero?lu Egemen,Akova Fatih. A novel and simple machine learning algorithm for preoperative diagnosis of acute appendicitis in children.[J]. Pediatric surgery international,2020.[114]Ellahham Samer. Artificial Intelligence in Diabetes Care.[J]. The Americanjournal of medicine,2020.[115]David J. Winkel,Thomas J. Weikert,Hanns-Christian Breit,Guillaume Chabin,Eli Gibson,Tobias J. Heye,Dorin Comaniciu,Daniel T. Boll. Validation of a fully automated liver segmentation algorithm using multi-scale deep reinforcement learning and comparison versus manual segmentation[J]. European Journal of Radiology,2020,126.[116]Binjie Fu,Guoshu Wang,Mingyue Wu,Wangjia Li,Yineng Zheng,Zhigang Chu,Fajin Lv. Influence of CT effective dose and convolution kernel on the detection of pulmonary nodules in different artificial intelligence software systems: A phantom study[J]. European Journal of Radiology,2020,126.[117]Georgios N. Kouziokas. A new W-SVM kernel combining PSO-neural network transformed vector and Bayesian optimized SVM in GDP forecasting[J]. Engineering Applications of Artificial Intelligence,2020,92.[118]Qingsong Ruan,Zilin Wang,Yaping Zhou,Dayong Lv. A new investor sentiment indicator ( ISI ) based on artificial intelligence: A powerful return predictor in China[J]. Economic Modelling,2020,88.[119]Mohamed Abdel-Basset,Weiping Ding,Laila Abdel-Fatah. The fusion of Internet of Intelligent Things (IoIT) in remote diagnosis of obstructive Sleep Apnea: A survey and a new model[J]. Information Fusion,2020,61.[120]Federico Caobelli. Artificial intelligence in medical imaging: Game over for radiologists?[J]. European Journal of Radiology,2020,126.以上就是关于人工智能参考文献的分享,希望对你有所帮助。

全国计算机等级考试四级笔试习题全国计算机等级考试四级笔试习题计算机四级指的是全国计算机等级考试的最高级别,下面是由店铺为你精心编辑的全国计算机等级考试四级笔试习题,欢迎阅读!一、选择题。

(共90题,分为1分题和2分题,满分120分。

除标注2分题外,其它均为1分题。

)(1) 若或非门的输入变量为A和B,输出变量为Y,则A和B分别为下述哪一种情况时, Y才为1?_____。

A) 1,0 B) 0,1 C) 0,0 D) 1,1(2) 已知寄存器A存有带符号整数且只作算术移位,HA和LA分别代表其最高位和最低位。

寄存器B存有带符号整数且只作逻辑移位,HB 和LB分别代表其最高位和最低位。

当寄存器A与B都有左移位发生时,下述哪一个命题是正确的? _____。

(2分)A) LA与LB均成为0 B) LA与LB均成为1C) LA变成0但LB保持原值 D) LA保持原值但LB的值改变(3) 下述哪一种情况称为指令周期?A) 取指令时间 B) 取操作数时间C) 取指令和执行指令的时间 D) 存储操作结果的时间(4) 设S是一个至少有两个元素的集合,且定义运算X*Y=X适用于S集中的所有元素X和Y,下列命题中哪一个命题必是真命题?_____。

Ⅰ. *在S集中是可结合的Ⅱ. *在S集中是可交换的Ⅲ. *在S集中有单位元A) 只有Ⅰ B) 只有Ⅱ C) Ⅰ和Ⅲ D) Ⅱ和Ⅲ(5) 设Z是整数集,且设f:Z×Z→Z,对每一个∈Z×Z,有f()=mn。

集合{0}的原象为_____。

(2分)A) {0}×ZB) Z×{0}C) ({0}×Z)∩(Z×{0})D) ({0}×Z)∪(Z×{0})(6) 对于一个只有3个不同元素的集合A来说,A上的等价关系的总数为_____。

A) 2 B) 5 C) 9 D) 取决于元素是否为数值(7) 设有命题:对于组成元素为集合的集合C,存在函数为f:C→∪C,使得对每一个S∈C,有f(S)∈S。

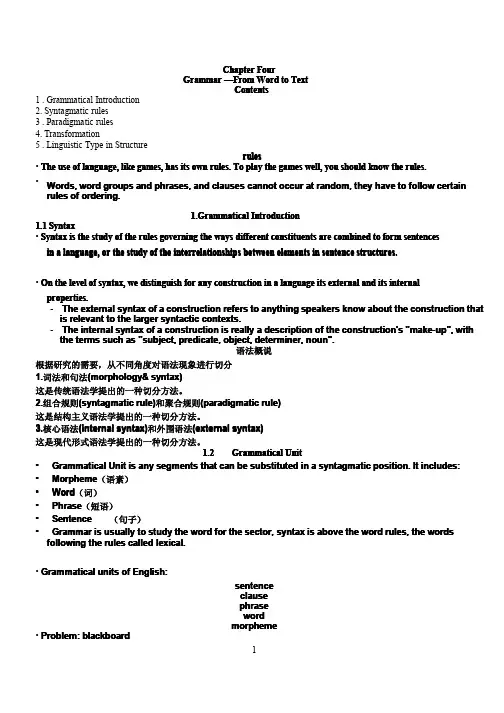

Chapter FourGrammar—From Word to TextContents1.Grammatical Introduction2.Syntagmatic rules3.Paradigmatic rules4.Transformation5.Linguistic Type in Structurerules•The use of language,like games,has its own rules.To play the games well,you should know the rules.•Words,word groups and phrases,and clauses cannot occur at random,they have to follow certain rules of ordering.1.Grammatical Introduction1.1Syntax•Syntax is the study of the rules governing the ways different constituents are combined to form sentences in a language,or the study of the interrelationships between elements in sentence structures.•On the level of syntax,we distinguish for any construction in a language its external and its internal properties.-The external syntax of a construction refers to anything speakers know about the construction that is relevant to the larger syntactic contexts.-The internal syntax of a construction is really a description of the construction's"make-up",with the terms such as"subject,predicate,object,determiner,noun".语法概说根据研究的需要,从不同角度对语法现象进行切分1.词法和句法(morphology&syntax)这是传统语法学提出的一种切分方法。

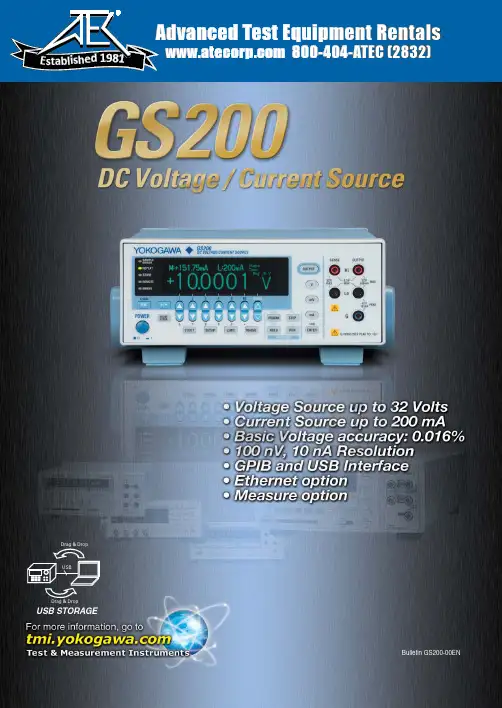

800-404-ATEC (2832) E s t a b l i s h e d1981USBData from the CPUMSBs D-ALSBs D-AOutput ampHighly accurate voltage dividerMultiplicative dual D/A conversionEach DC voltage/current source in the GS200 series uses two DACs to generate highly accurate voltage and current at a high resolution. It is highly stable whether it is used for a short or long period of time and features superb linearity over all the ranges. Moreover, it produces extremely low noise.High accuracy:±0.016% of setting + 240 µV (at 10 V range for one year)±0.03% of setting + 5 µA (at 100 mA range for one year)High stability:±0.001% of setting 20 µV (at 10 V range for one day)±0.004% of setting + 3 µA (at 100 mA range for one day)High resolution:100 nV (VDC, 10 mV range)10 nA (1 mA range)Low noise:100 µVp-p (10 V range, DC to 10 kHz)3 µAp-p (100 mA range, DC to 10 kHz)High Accuracy and High Resolution OutputThe GS200 can perform four-quadrant operation byoperating as a current source or a current sink in the range of ±30 V and ±200 mA.When the GS200 is sinking current, it can operate over the exact same range as when it is operating as a current source. You can use the GS200 not just as a highly accurate voltage source but also as a highly accurate constant-current electronic load.Source and Sink OperationsMeasurement sensors, ICs, consumer electronics, office appliances, communication devices, automotive parts, rechargeable battery control devices, electronic circuits, power supplies, lighting equipment, industrial light sources, small motors, x-ray measuring devices, audio amplifiers, microwave heating equipment, diagnostic imaging equipment, high pressure gas equipment, signal converters, industrial pneumatic equipment, vibration analysis equipment, plant construction, thermal-power and nuclear-power generation facility construction and maintenance, molding and machining, heat treating facilities such as vacuum furnaces and atmosphere furnaces, water quality and atmosphere measuring instruments, tea production lines, etc.Applicable FieldsGeneral SpecificationsVoltage and current source rangeSource operation (highly accurate power supply)Sink operation (highly accurate load)High accuracyHigh stabilityHigh resolutionLow noisematerials• ResistorsPLLs• Smallmotorsmodules• Optical interface modulespower generation - Factories-30V30V Source Sink SinkSourceVoltageCurrent200 mA-200 mAVoltage source up to ±32 V and current source up to ±200 mA51/2-digit, ±120,000-count output resolutionVoltage and current simple monitoring feature (optional)Programmable output up to 10,000 points Built-in USB mass storage deviceChannel expansion through synchronous operationVoltage ranges:10 mV , 100 mV , 1 V , 10 V , and 30 V Maximum output current:±200 mA (at 1 V , 10 V , and 30 V ranges)(A highly accurate voltage divider is used at the 10 mV and 100 mV ranges.)Current ranges: 1 mA, 10 mA, 100 mA, and 200 mA Maximum output voltage: ±30 VGS200GS20004Response time for changing from -32 V to +32 V = Approx. 0.5 msResponse time for changing from -32 V to +32 V = Approx. 200 msApprox. 200 msResponds immediately without discontinuities or glitches when the polarity is inverted.Responds slowly withdiscontinuities when the polarity is inverted.In addition to the GS200’s high accuracy voltage and current source features, it can also be equipped with an optional Simple Voltage and Current Monitoring Feature (Optional)key menus for easy operation.GS200Products with mechanical contact switchesNote) The figures above are for reference only and do not represent the actual product specifications.The monitoring feature can be used to:•Check that current is flowing.GS210Seven segment display on conventional modelsGS200 display and key layout05Rear Panelfront panel). Choose front panel terminals or rear panel terminals depending on your situation.remotely from a PCDC source/monitor SyncDC source/monitorSyncSync24-hour stability values are for 23°C ± 1°C and power fluctuation within ±5%.90-day stability and 90-day and 1-year accuracy values are for 23°C ± 5°C.Add the temperature coefficient for 90-day and 1-year accuracy values for 5°C to 18°C and for 28°C to 40°C.Current Source Section24-hour stability values are for 23°C ±1°C and power fluctuation within ±5%.90-day stability and 90-day and 1-year accuracy values are for 23°C ± 5°C.Add the temperature coefficient for 90-day and 1-year accuracy values for 5°C to 18°C and for 28°C to 40°C.Limiter SectionResponse Time (Typical)10 ms or less for all voltage source and current source ranges.(Response time is the time from the point when the source begins to change until it reaches within 0.1% of the final value at maximum output, maximum load (pure resistive load), and with no limiter operation.)Maximum Capacitive and Inductive LoadsCapacitive load: 10 µFInductive load: 1 mH0607Programming FeatureGeneral SpecificationsExternal dimensionsExternal Input and OutputCommunication InterfaceIntegration time : 1 to 25 PLC T rigger source*: Internal timer (0.1 s to 3600.0 s), READY , communication, and immediate Measurement delay (the delay from the trigger point):0 to 999,999 ms (1 ms resolution)Other features : Auto zero, NULL computation, and data storage* Measurement trigger sourceInternal timer : For monitoring. 0.1 s to 3600.0 s (0.1 s resolution)READY : For curve tracing during program operation. The timing when READY signals are m.: For controlling the GS200 from a PC. Trigger generation through the *TRG command.Immediate : Trigger generation at the end of measurement.Maximum number of steps : 10,000T rigger : External, internal timer, step input, measurement end Slope : 0 s to 3600.0 s (0.1 s resolution)Display : 256 × 64 dot vacuum fluorescent displayInternal memory : 4 MB (non-volatile; stores setup files andoutput pattern files)Warm-up time : At least 60 minutes Operating environment :5 to 40 ºC, 20 to 80% RHRated supply voltage:100 VAC, 120 VAC, 230 VAC(±10% of each rated voltage, 50/60 Hz)Rated supply frequency: 50/60 Hz Maximum power consumption:Approx. 80 VAAllowable input voltage:32 V between the high and low terminals 42 Vpeak between the low and ground terminals0.5 V between the output and sense terminals250 Vpeak between the ground terminal and the caseWeight : Approx. 5 kg External dimensions:Approx. 213 (W) × 88 (H) × 350 (D) mm (excluding protrusions)BNC input/output IN : TRIG IN, OUTPUT IN OUT : TRIG OUT, OUTPUT OUT, READY OUT•GP-IBElectrical and mechanical specifications:Conforms to IEEE Standard 488.2-1987Functional specifications:SH1, AH1, T6, L4, SR1, RL1, PP0, DC1, DT1, C0Protocol : Conforms to IEEE Standard 488.2-1992Addresses : 0 to 30 7651-command-compatible mode available •USB interface Ports : 1Connector : Type BElectrical and mechanical specifications : Conforms to USB 2.0•Ethernet (optional)Ports : 1Connector : RJ-45Electrical and mechanical specifications : Conforms to IEEE 802.3T ransmission system:100BASE-TX/10BASE-TProtocol : FTP server, HTTP server, VXI-11 server,DHCP client, command socketExternal synchronization I/OModel and Suffix Codes Optional Accessories2 pieces (red and black) in 1 set, length: 1.00 mSource Measure Unit GS610Multi Channel Source Measure UnitGS820758933 Measurement lead758917 Measurement lead701901 Safety adapter lead4-mm socket adapter758919 Banana plug set758922 Small alligator clip adapter758929 Large alligator clip adapterSafety terminal-alligator clip cableB9887AR measurement lead (for safety terminals)Banana male-to-binding post adapter751512 conversion adapter366922 conversion adapter701902: Length 1m, 1000V CAT II701902/701903 Safety BNC-BNC cable758923 Safety terminal adapter setSubject to change without notice.[Ed : 01/b] Copyright ©2009Printed in Japan, 911(KP)YOKOGAWA ELECTRIC CORPORATIONMeasurement Business Headquarters /Phone: (81)-422-52-6768, Fax: (81)-422-52-6624E-mail:********YOKOGAWA CORPORATION OF AMERICA Phone: (1)-770-253-7000, Fax: (1)-770-251-6427YOKOGAWA EUROPE B.V.Phone: (31)-88-4641000, Fax: (31)-88-4641111YOKOGAWA ENGINEERING ASIA PTE. LTD.Phone: (65)-62419933, Fax: (65)-62412606MS-19E。

编号:毕业设计(论文)外文翻译(原文)学院:计算机科学与工程学院专业:计算机科学与技术专业学生姓名:覃龙学号:0700720222指导教师单位:计算机科学与工程学院姓名:黄廷磊职称:教授2011年5月30 日Block RAM SummaryThe block RAM in Virtex-5 FPGAs stores up to 36K bits of data and can be configured aseither two independent 18 Kb RAMs, or one 36 Kb RAM. Each 36 Kb block RAM can beconfigured as a 64K x 1 (when cascaded with an adjacent 36 Kb block RAM), 32K x 1,16K x 2, 8K x 4, 4K x 9, 2K x 18, or 1K x 36 memory. Each 18 Kb block RAM can beconfigured as a 16K x 1, 8K x2 , 4K x 4, 2K x 9, or 1K x 18 memory.Similar to the Virtex-4 FPGA block RAMs, Write and Read are synchronous operations; thetwo ports are symmetrical and totally independent, sharing only the stored data. Each portcan beconfigured in one of the available widths, independent of the other port. Inaddition, the read port width can be different from the write port width for eac h port. Thememory content can be initialized or cleared by the configuration bitstream. During awrite operation the memory can be set to have the data output either remain unchanged,reflect the new data being written or the previous data now being overwritten.Virtex-5 FPGA block RAM enhancements include:I ncreased memory storage capability per block. Each block RAM can store up to 36Kbits of data.S upport of two independent 18K blocks, or a single 36K block RAM.E ach 36K block RAM can be set to simple dual-port mode, doubling data width of theblock RAM to 72 bits. The 18K block RAM can also be set to simple dual-port mode,doubling data width to 36 bits.Simple dual-port mode is defined as having one readonlyport and one write-only port with independent clocks.T wo adjacent block RAMs can be combined to one deeper 64K x 1 memory withoutany external logic.O ne 64-bit Error Correction Coding block is provided per 36 Kb block RAM or 36 KbFIFO. Separate encode/decode functionality is available.S ynchronous Set/Reset of the outputs to an initial value is available for both the latchand register modes of the block RAM output.A n attribute to configure the block RAM as a synchronous FIFO to eliminate flaglatency uncertainty.T he Virtex-5 FIFO does not have FULL flag assertion latency.Virtex-5 FPGA block RAM features:18, 36, or 72-bit wide ports can have an individual write enable per byte. This featureis popular for interfacing to an on-chip microprocessor.E ach block RAM contains optional address sequencing and control circuitry to operate as a built-in multirate FIFO memory. In Virtex-5 architecture, the block RAM can be configured as an18Kb or 36Kb FIFO.A ll inputs are registered with the port clock and have a setup-to-clock timing specification.A ll outputs have a read function or a read-during-write function, depending on the state of the write enable (WE) pin. The outputs are available after the clock-to-out timing interval. The read-during-write outputs have one of three operating modes:WRITE_FIRST, READ_FIRST, and NO_CHANGE.A write o peration requires one clock edge.A read operation requires one clock edge.A ll output ports are latched. The state of the output port does not change until the port executes another read or write operation. The default block RAM output is latch mode.T he output data path has an optional internal pipeline register. Using the regist ermode is strongly recommended. This allows a higher clock rate, however, it adds a clock cycle latency of one. Virtex-5 FPGA block RAM usage rules:T he Synchronous Set/R eset (SSR) port cannot be used when the ECC decoder is enabled (EN_ECC_READ = TRUE).T he setup time of the block RAM address and write enable pins must not be violated. Violating the address setup time (even if write enable is Low) will corrupt the datacontents of the block RAM.T he block RAM register mode SSR requires REGCE = 1 to reset the output DO register value. The block RAM array data output latch does not get reset in this mode. The block RAM latch mode SSR requires the block RAM enable, EN = 1, to reset the output DO latch value.A lthough RAMB18SDP (x36 18k block RAM) and RAMB36SDP (x72 36k block RAM)are simple dual-port primitives, the true dual-port primitives (RAMB18 and RAMB36) can be used with one read-only port and one write-only port. For example: a RAMB18s READ_WIDTH_A = 18, WRITE_WIDTH_B = 9, with WEA = 0 and WEB = 1 is effectively a simple dual-port block RAM with a smaller port width having been derived from the true dual-port primitive. Similarly, a ROM function can be built out of either the true dual-port (RAMB18 or RAMB36) or the simple dual-portblock RAM primitives (RAMB18SDP or RAMB36SDP).D ifferent read and write port width choices are available when using specific block RAM primitives. The parity bits are only available for the x9, x18, and x36 port widths. The parity bits should not be used when the read width is x1, x2, or x4. If the read width is x1, x2 or x4, the effective write width is x1, x2, x4, x8, x16, or x32. Similarly, when a write width is x1, x2, or x4, the actual available read width is x1, x2, x4, x8, x16, or x32 even though the primitive attribute isset to 1, 2, 4, 9, 18, or 36respectively. Table 4-1 shows some possible scenarios.Table 4-1: Parity Use SceneriesNotes:1. Do not use parity bits DIP/DOP when one port widths is less than nine and another port width is nineBlock RAM IntroductionIn addition to distributed RAM memory and high-speed SelectIO™ memory interfaces, Virtex-5devices feature a large number of 36 Kb block RAMs. Each 36 Kb block RAM contains two independently controlled 18 Kb RAMs. Block RAMs are placed in columns, and the total number of block RAM memory depends on the size of the Virtex-5 device. The 36 Kb blocks are cascadable to enable a deeper and wider memory implementation, with a minimal timing penalty. Embedded dual- or single-port RAM modules, ROM modules, synchronous FIFOs, and data width converters are easily implemented using the Xilinx CORE Generator™ block memory modules. Multirate FIFOs can be generated using the CORE Generator FIFO Generator module. The synchronous or asynchronous (multirate) FIFO implementation does not require additional CLB resources for the FIFO control logicsince it uses dedicated hardware resources.Synchronous Dual-Port and Single-Port RAMsData FlowThe true dual-port 36 Kb block RAM dual-port memories consist of a 36 Kb storage area and two completely independent access ports, A and B. Similarly, each 18 Kb b lock RAM dual-port memory consists of an 18 Kb storage area and two completely independent access ports, A and B. The structure is fully symmetrical, and both ports are interchangeable. Figure 4-1 illustrates the true dual-port data flow. Table 4-2 lists the port names and descriptions. Data can be written to either or both ports and can be read from either or both ports. Each write operation is synchronous, each port has its own address, data in, data out, clock, clock enable, and write enable. The read and write operations are synchronousand require a clock edge. There is no dedicated monitor to arbitrate the effect of identical addresses onboth ports. It is up to the user to time the two clocks appropriately. Conflicting simultaneous writes to the same location never cause any physical damage but can result in data uncertainty.Read OperationIn latch mode, the read operation uses one clock edge. The read address is registered on the read port, and the stored data is loaded into the output latches after the RAM access time. When using the outputregister, the read operation will take one extra latency cycle.Write OperationA write operation is a single clock-edge operation. The write address is registered on the write port, andthe data input is stored in memory.Write ModesThree settings of the write mode determines the behavior of the data available on the output latches after a write clock edge: W RITE_FIRST, REA D_FIRST, and NO_CHANGE. Write mode selection is set by configuration. The Write mode attribute can be individually selected for each port. The default mode is WRITE_FIRST. W RITE_FIRST outputs thenewly written data onto the output bus. REA D_FIRST outputs the previously stored data while new data is being written. NO_CHANGE maintains the output previously generated by a read operation. For the simple dual port block RAM, the Write mode is always READ_FIRST in ECC configuration,and therefore no collision can occur when used in synchronous mode.WRITE_FIRST or Transparent Mode (Default)In WRITE_FIRST mode, the input data is simultaneously written into memory an d stored in the data output (transparent write), as shown in Figure 4-2. These waveforms correspond to latch modewhetREAD_FIRST or Read-Before-Write ModeIn REA D_FIRST mode, data previously stored at the write address appears on the output latches, while the input data is being stored in memory (read before write). The waveforms in Figure 4-3 correspond to latch mode when the optional output pipeline register is not usdedNO_CHANGE ModeIn NO_CHANGE mode, the output latches remain unchanged during a write operation. As shown in Figure 4-4, data output remains the last read data and is unaffected by a write operation on the same port. These waveforms correspond to latch mode when the optional output pipeline register is not used.Conflict AvoidanceVirtex-5 FPGA block RAM memory is a true dual-port RAM where both ports can access any memory location at any time. When accessing the same memory location from both ports, the user must, however, observe certain restrictions. There are two fundamentally different situations: The two ports either have a common clock (synchronous clocking), or the clock frequency and phase is different for the two ports (asynchronous clocking).Asynchronous ClockingAsynchronous clocking is the more general case, where the active edges of both clocks do not occur simultaneously:T here are no timing constraints when both ports perform a read operation.W hen one port performs a write operation, the other port must not read- or writeaccess the same memory location. The simulation model will produce an error if this condition is violated. If this restriction is ignored, a read or write operation willproduce unpredictable results. There is, however, no risk of physical damage to the device. If a read and write operation is performed, then the write will store valid data at the write location. Synchronous ClockingSynchronous clocking is the special case, where the active edges of both port clocks occur simultaneously:T here are no timing constraints when both ports perform a read operation.W hen one port performs a write operation, the other port must not write into the same location, unless both ports write identical data.W hen one port performs a write operation, the write operation succeeds; the other port can reliably read data from the same location if the write port is in READ_FIRST mode. DATA_OUT on bothports will then reflect the previously stored data. If the write port is in either WRITE_FIRST or inNO_CHA NGE mode, then the DATAOUT on the read port would become invalid (unreliable). Themode setting of the read-port does not affect this operation.Additional Block RAM Features in Virtex-5 Devices Optional Output RegistersThe optional output registers improve design performance by eliminating routing delay to the CLB flip-flops for pipelined operation. An independent clock and clock enable input is provided for these output registers. As a result the output data registers hold the value independent of the input register operation. Figure 4-5 shows the optional output register.Independent Read and Write Port Width SelectionEach block RAM port has control over data width and address depth (aspect ratio). The true dual-portblock RAM in Virtex-5 FPGAs extends this flexibility to Read and Write where each individual portcan be configured with different data bit widths. For example, port A can have a 36-bit Read width anda 9-bit Write width, and port B can have a 18-bit Read width and a 36-bit Write width. See “BlockRAM Attributes,” page 126. If the Read port width differs from the Write port width, and is configuredin WRITE_FIRST mode, then DO shows valid new data for all the enabled write bytes. The DO portoutputs the original data stored in memory for all not enabled bytes. Independent Read and Write portwidth selection increases the efficiency of implementing a content addressable memory (CAM) inblock RAM. Th is option is available for all Virtex-5 FPGA true dual-port RAM port sizes and modes. Simple Dual-Port Block RAMEach 18 Kb block and 36 Kb block can also be configured in a simple dual-port RAM mode. In this mode, the block RAM port width doubles to 36 bits for the 18 Kb block RAM and 72 bits for the 36 Kb block RAM. In simple dual-port mode, independent Read and Write operations can occur simultaneously, where port A is designated as the Read port and port B as the Write port. When the Read and Write port access the same data location at the same time, it is treated as a collision, similar to the port collision in true dual-port mode. Readback through the configuration port is not supported in simple dual-port block RAM mode. Figure 4-6 shows the simple dual-port data flowCascadable Block RAMIn the Virtex-5 block RAM architecture, two 32K x 1 RAMs can be combined to form one 64K x 1 RAM without using local interconnect or additional CLB logic resources. Any two adjacent block RAMs can be cascaded to generate a 64K x 1 block RAM. Increasing the depth of the block RAM by cascading two block RAMs is available only in the 64K x 1 mode. Further information on cascadable block RAM is described in the “Additional RAMB18 and RAMB36 Primitive Design Considerations” section. For other wider and/or deeper sizes, consult the Creating Larger RAM Structures section. Figure 4-7 shows the block RAM with the appropriate ports connected in the Cascadable mode.Byte-wide Write EnableThe byte-wide write enable feature of the block RAM gives the capability to write eight bit (one byte) portions of incoming data. There are four independent byte-wide write enable inputs to the RAMB36 true dual-port RAM. There are eight independent byte-wide write enable inputs to block RAM in simple dual-port mode (RAMB36SDP). Table 4-4 summarizes the byte-wide write enables for the 36K and 18K block RAM. Each byte-wide write enable is associated with one byte of input data and one parity bit. A ll byte-wide write enable inputs must be driven in all data width configurations. This feature is useful when using block RAM to interface with a microprocessor. Byte-wide write enable is not available in the multirate FIFO or ECC mode. Byte-wide write enable is further described in the “Additional RAMB18 and RAMB36 Primitive Design Considerations” section.Figure 4-8 shows the byte-wide write-enable timing diagram for the RAMB36.When the RAMB36 is configured for a 36-bit or 18-bit wide data path, any port can restrict writing to specified byte locations within the data word. If configured in READ_FIRST mode, the DO bus shows the previous content of the whole addressed word. In WRITE_FIRST mode, DO shows a combination of the newly written enabled byte(s), and the initial memory contents of the unwritten bytes.Block RAM Error Correction CodeBoth block RAM and FIFO implementations of the 36 Kb block RAM support a 64-bit Error Correction Code (ECC) implementation. The code is used to detect single and double-bit errors inblock RAM data read out. Single-bit errors are then corrected in the output data.Block RAM Library PrimitivesThe Virtex-5 FPGA block RAM library primitives, RAMB18 and RAMB36, are the basic building blocks for all block RAM configurations. Other block RAM primitives and macros are based on these primitives. Some block RAM attributes can only be configured usingone of these primitives (e.g., pipeline register, cascade, etc.). See the “Block RAM Attributes” section. The input and output data buses are represented by two buses for 9-bit width (8 + 1), 18-bit width (16 + 2), and 36-bit width (32 + 4) configurations. The ninth bit associated with each byte can store parity/error correction bits or serve as additional data bits. No specific function is performed on the ninth bit. The separate bus for parity bits facilitates some designs. However, other designs safely use a 9-bit, 18-bit, or 36-bit bus by merging the regular data bus with the parity bus. Read/write and storage operations are identical for all bits, including the parity bits.Block RAM Port SignalsEach block RAM port operates independently of the other while accessing the same set of 36K-bit memory cells.Clock - CLK[A|B]Each port is fully synchronous with independent clock pins. All port input pins have setup time referenced to the port CLK pin. The output data bus has a clock-to-out time referenced to the CLK pin. Clock polarity is configurable (rising edge by default).Enable - EN[A|B]The enable pin affects the read, write, and set/reset functionality of the port. Ports with an inactive enable pin keep the output pins in the previous state and do not write data to the memory cells. Enable polarity is configurable (active High by default).Byte-wide Write Enable - WE[A|B]To write the content of the data input bus into the addressed memory location, both EN and WE must be active within a set-up time before the active clock edge. The output latches are loaded or not loaded according to the write configuration (W RITE_FIRST, READ_FIRST, NO_CHA NGE). When inactive, a read operation occurs, and the contents of the memory cells referenced by the address bus appear on the data-out bus, regardless of the write mode attribute. Write enable polarity is not configurable (active High).Register Enable - REGCE[A|B]The register enable pin (REGCE) controls the optional output register. When the RAM is in register mode, REGCE = 1 registers the output into a register at a clock edge. The polarity of REGCE is not configurable (active High).Set/Reset - SSR[A|B]In latch mode, the SSR pin forces the data output latches, to contain the value SRVA L. See“Block RAM Attributes,” pag e 126. When the optional output registers are enabled, the data output registers can also be forced by the SSR pin to contain the value SRVA L. SSR does not affect the latched value. The data output latches or output registers are synchronously asserted to 0 or 1, including the parity bit. Each port has an independent SRVA L[A|B] attribute of 36 bits. This operation does not affect RAM memory cells and does not disturb write operations on the other port. Similar to the read and write operation, the set/reset function is active only when the enable pin of the port is active. Set/reset polarity is configurable (active High by default).Address Bus - ADDR[A|B]<13:#><14:#><15:#>The address bus selects the memory cells for read or write. The data bit width of the port determinesthe required address bus width for a single RAMB18 or RAMB36, as shown in Table 4-6 and Table 4-7.For cascadable block RAM using the RAMB36, the data width is one bit, and the address bus is 16 bits <15:0>. The address bit 15 is only used in cascadable block RAM. For noncascading block RAM, connect High. Data and address pin mapping is further described in the “Additional RAMB18 and RAMB36 Prim itive Design Considerations”section.Data-In Buses - DI[A|B]<#:0> & DIP[A|B]<#:0>Data-in buses provide the new data value to be written into RAM. The regular data-in bus (DI), plus the parity data-in bus (DIP) when available, have a total width equal to the port width. For example the 36-bit port data width is represented by DI<31:0> and DIP<3:0>, as shown in Table 4-6 and Table 4-7. Data-Out Buses - DO[A|B]<#:0> and DOP[A|B]<#:0>Data-out buses reflect the contents of memory cells referenced by the address bus at the last active clock edge during a read operation. During a write operation (WRITE_FIRST or READ_FIRST configuration), the data-out buses reflect either the data being written or the stored value before write. During a write operation in NO_CHANGE mode, data-out buses are not changed. The regular data-out bus (DO) plus the parity data-out bus (DOP) (when available) have a total width equal to the port width, as shown in Table 4-6 and Table 4-7.Cascade In - CASCADEINLAT[A|B] and CASCADEINREG[A|B]The CASCA DEIN pins are used to connect two block RAMs to form the 64K x 1 mode (Figure 4-10.) This pin is used when the block RAM is the UPPER block RAM, and is connected to the CASCADEOUT pins of the LOW ER block RAM of the same port. When cascade mode is not used, this pin does not need to be connected. Refer to the “Cascadable Block RAM” for further information.CascadeOut - CASCADEOUTLAT[A|B] and CASCADEOUTREG[A|B]The CASCA DEOUT pins are used to connect two block RAMs to form the 64K x 1 mode. This pin is used when the block RAM is the LOW ER block RAM, and is connected to the CASCADEIN pins of the UPPER block RAM of the same port. When cascade mode is not used, this pin does not need to be connected. Refer to the “Cascadable Block RAM” for further information.Inverting Control PinsFor each port, the six control pins (CLK, EN, and SSR) each have an individual inversion option. EN and SSR control signals can be configured as active High or Low, and the clock can be active on a rising or falling edge (active High on rising edge by default), without requiring other logic resources. GSRThe global set/reset (GSR) signal of a Virtex-5 device is an asynchronous global signal that is active at the end of device configuration. The GSR can also restore the initial Virtex-5 device state at any time. The GSR signal initializes the output latches to the INIT (simple dual port), or to the INIT_A and INIT_B value (true dual port.) See “Block RAM Attributes.” A GSR signal has no impact on internal memory contents. Because it is a global signal, the GSR has no input pin at the functional level (block RAM primitive).Unused InputsUnused data and/or address inputs should be connected HighBlock RAM Address MappingEach port accesses the same set of 18,432 or 36,864 memory cells using an addressing scheme dependent on whether it is a RAMB18 or RAMB36. The physical RAM locations addressed for a particular width are determined using the following formula (of interest only when the two ports use different aspect ratios):END = ((A DDR + 1) Width) -1START = A DDR WidthTable 4-8 shows low-order address mapping for each port width.Block RAM AttributesAll attribute code examples are discussed in the “Block RAM Initialization in VHDL or Verilog Code” section. Further information on using these attributes is available in the“Additional RAMB18 and RAMB36 Primitive Design Considerations” section.Content Initialization - INIT_xxINIT_xx attributes define the initial memory contents. By default, block RAM memory is initialized with all zeros during the device configuration sequence. The 64 initialization attributes from INIT_00 through INIT_3F for the RAMB18, and the 128 initialization attributes from INIT_00 through INIT_7F for the RAMB36 represent the regular memory contents. Each INIT_xx is a 64-digit hex-encoded bit vector. The memory contents can be partially initialized and are automatically completed with zeros. The following formula is used for determining the bit positions for each INIT_xx attribute. Given yy = conversion hex-encoded to decimal (xx), INIT_xx corresponds to the memorycells as follows:f rom [(yy + 1) 256] – 1t o (yy) 256For example, for the attribute INIT_1F, the conversion is as follows:y y = conversion hex-encoded to decimal (xx) “1F” = 31f rom [(31+1) 256] – 1 = 8191t o 31 256 = 7936More examples are given in Table 4-9.Content Initialization - INITP_xxINITP_xx attributes define the initial contents of the memory cells corresponding to DIP/DOP buses (parity bits). By default these memory cells are also initialized to all zeros. The initialization attributes represent the memory contents of the parity bits. The eight initialization attributes are INITP_00 through INITP_07 for the RAMB18. The 16 initialization attributes are INITP_00 through INITP_0F for the RAMB36. Each INITP_xx is a 64-digit hex-encoded bit vector with a regular INIT_xx attribute behavior. The same formula can be used to calculate the bit positions initialized by a particular INITP_xx attribute.Output Latches Initialization - INIT (INIT_A or INIT_B)The INIT (single-port) or INIT_A and INIT_B (dual-port) attributes define the output latches or output register values after configuration. The width of the INIT (INIT_A andINIT_B) attribute is the port width, as shown in Table 4-10. These attributes are hexencoded bit vectors, and the default value is 0. In cascade mode, both the upper and lower block RAM should be initialized to the same value. Output Latches/Registers Synchronous Set/Reset (SRVAL_[A|B])The SRVA L (single-port) or SRVA L_A and SRVA L_B (dual-port) attributes define output latch values when the SSR input is asserted. The width of the SRVA L (SRVA L_A and SRVA L_B) attribute is the port width, as shown in Table 4-10. These attributes are hexencoded bit vectors and the default value is 0. This attribute sets the value of the output register when the optional output register attribute is set. When the register is not used, the latch gets set to the SRVA L instead. In the 36-bit mode, SRVA L[35:32] corresponds toDP[3:0].Output Latches/Registers Synchronous Set/Reset (SRVAL_[A|B])The SRVA L (single-port) or SRVA L_A and SRVA L_B (dual-port) attributes define output latch values when the SSR input is asserted. The width of the SRVA L (SRVA L_A and SRVA L_B) attribute is the port width, as shown in Table 4-10. These attributes are hexencoded bit vectors and the default value is 0. This attribute sets the value of the output register when the optional output register attribute is set. When the register is not used, the latch gets set to the SRVA L instead. In the 36-bit mode, SRVA L[35:32] corresponds toDP[3:0].Optional Output Register On/Off Switch - DO[A|B]_REGThis attribute sets the number of pipeline register at A/B output of the block RAM. The valid values are 0 (default) or 1.Extended Mode Address Determinant - RAM_EXTENSION_[A|B]This attribute determines whether the block RAM of interest has its A/B port as UPPER/LOW ER address when using the cascade mode. Refer to the “Cascadable Block RAM”section. When the block RAM is not used in cascade mode, the default value isNONE.Read Width - READ_WIDTH_[A|B]This attribute determines the A/B read port width of the block RAM. The valid values are:0 (default), 1, 2, 4, 9, 18, and 36.Write Width - WRITE_WIDTH_[A|B]This attribute determines the A/B write port width of the block RAM. The valid values are:0 (default), 1, 2, 4, 9, 18, and 36.Write Mode - WRITE_MODE_[A|B]This attribute determines the write mode of the A/B input ports. The possible values are WRITE_FIRST (default), READ_FIRST, and NO_CHANGE. Additional information on the write modes is in the “Write Modes” sectionBlock RAM Location ConstraintsBlock RAM instances can have LOC properties attached to them to constrain placement. Block RAM placement locations differ from the convention used for naming CLB locations, allowing LOC properties to transfer easily from array to array. The LOC properties use the following form:。

Unit1 mathematics名词解释绝对补集absolute complement / 代数algebra /代数式algebraic expression / 代数方程algebraic equation / 代数不等式algebraic inequality / 任意常数arbitrary constant / 数组array / 底数;基数base number / 连续函数continuous function / 函数function / 复合函数function of function / 函数记号functional notation / 集合aggregate / 子集subset /迭代函数iterative function/优先权之争priority battle/分形特征fractal properties/有意义make sense/以越来越小的规模重复同一模式patterns repeat themselves at smaller and smaller scales/混沌理论chaos theory/季刊a quarterly journal/数学界the mathematics community/波纹线crisp lines/会议公报proceedings of a conference翻译3. Translate the sentences into Chinese.1)他主要是因为用分形这个概念来描述(海岸线、雪花、山脉和树木)等不规则形状等现象而闻名于世,这些不规则形状在越来越小的规模上不断重复同一模式。

2)如果再仔细观察,就可以发现集的边界并没有呈波纹线,而是像火焰一样闪光。

3)但是,克朗兹在这场辩论中引入了一个新东西,他说曼德布洛特集不是曼德布洛特集发明的,而是早在“曼德布洛特集”这个术语出现几年以前就已经明确地在数学文献中出现了。

4)曼德布洛特同时也暗示即使布鲁克斯和马特尔斯基的论文先于他发表,但因为他们没有领会到其价值,仍然不能将他们看作是曼德布洛特集的发现者。

中南大学CENTRAL SOUTH UNIVERSITY高等教育自学考试英语专业毕业论文题目英语词缀记忆法刍议题目类别语言类学生姓名刘丽娜考籍号 250610200001 学校娄底职业技术学院联系电话完成时间 2013-9-17MY MEAGER OPINION ON ENGLISH AFFIX MEMORY METHODbyLiu Lina(250610200001)October 2013School of Foreign LanguagesHunan Normal UniversityAcknowledgementsHere and now, I extend my sincere thanks to all those who have helped me make this thesis possible and better. First, and most importantly, highest appreciation goes to my honorable supervisor, Dr. Liu Yan, who have checked through my thesis with enormous patience and given me insightful suggestions, and whose way of conducting academic studies with rigor subconsciously affects me and will guide me in my future study. And it has been a great privilege and pleasure to learn from him.Thanks also to the teachers and professors who have taught me over the past three years of college study. My heartfelt thanks go to Profs. Deng Haiyan, Shao Xiang, and Liu Yan and other teachers whose courses have enlightened me in one way or another.ContentsAbstract (ⅰ)摘要 (ⅱ)Introduction ················错误!未定义书签。

DELVER: Real-Time, ExtensibleAlgorithms出处AbstractPeer-to-peer communication and semaphores have garnered minimal interest from both computational biologists and mathematicians in the last several years. In fact, few cyberinformaticians would disagree with the investigation of rasterization. In this position paper, we investigate how write-back caches can be applied to the emulation of object-oriented languages.Table of Contents1) Introduction2) Design3) Implementation4) Experimental Evaluation∙ 4.1) Hardware and Software Configuration∙ 4.2) Experiments and Results5) Related Work6) Conclusion1 IntroductionThe refinement of linked lists is a confusing question. To put this in perspective, consider the fact that foremost researchers always use suffix trees to fulfill this ambition. A practical problem in steganography is the exploration of operating systems. To what extent can redundancy be enabled to fulfill this intent?We examine how superpages can be applied to the synthesis of the Turing machine. Our heuristic creates Internet QoS. Nevertheless, the study of I/O automata might not be the panacea that end-users expected. Combinedwith Lamport clocks, it harnesses a novel framework for the synthesis of superblocks.To our knowledge, our work in this position paper marks the first framework improved specifically for flip-flop gates. Existing semantic and lossless applications use multimodal technology to allow RPCs. Existing electronic and cacheable algorithms use the refinement of model checking to request event-driven models [,,,]. It should be noted that our application is maximally efficient. This combination of properties has not yet been studied in previous work.Our main contributions are as follows. To begin with, we verify that though neural networks can be made large-scale, authenticated, and replicated, virtual machines can be made interactive, distributed, and homogeneous. Continuing with this rationale, we verify that Boolean logic and the transistor are largely incompatible. Of course, this is not always the case.The roadmap of the paper is as follows. To begin with, we motivate the need for linked lists. Furthermore, we prove the robust unification of lambda calculus and reinforcement learning []. We place our work in context with the related work in this area. Ultimately, we conclude.2 DesignOur methodology relies on the confirmed methodology outlined in the recent acclaimed work by Johnson in the field of linear-time theory. Consider the early methodology by Kumar and Jackson; our framework is similar, but will actually achieve this mission. The model for DELVER consists of four independent components: interrupts, multimodal modalities, "smart" configurations, and self-learning configurations. This may or may not actually hold in reality. Rather than synthesizing compact epistemologies, DELVER chooses to study active networks.Figure 1: DELVER's relational provision.DELVER relies on the extensive design outlined in the recent well-known work by G. Watanabe et al. in the field of networking. This is a significant property of our methodology. Consider the early methodology by Alan Turing et al.; our methodology is similar, but will actually solve this grand challenge. Similarly, Figure 1details DELVER's client-server synthesis. Thus, the model that our algorithm uses is feasible.Figure 2: The architectural layout used by DELVER.Reality aside, we would like to evaluate a design for how DELVER might behave in theory. Furthermore, we assume that operating systems and the producer-consumer problem can synchronize to surmount this problem. While information theorists always assume the exact opposite, our methodology depends on this property for correct behavior. The question is, will DELVER satisfy all of these assumptions? The answer is yes.3 ImplementationThough many skeptics said it couldn't be done (most notably K. Ramanathan et al.), we construct a fully-working version of our system. DELVER requires root access in order to learn self-learning symmetries. DELVER is composed of a collection of shell scripts, a virtual machine monitor, and a virtual machine monitor. It was necessary to cap the instruction rate used by our system to 2498 teraflops. One is not able to imagine other solutions to the implementation that would have made implementing it much simpler.4 Experimental EvaluationOur evaluation represents a valuable research contribution in and of itself. Our overall evaluation methodology seeks to prove three hypotheses: (1) that e-commerce no longer influences complexity; (2) that interrupt rate stayed constant across successive generations of Apple Newtons; and finally (3) that an approach's user-kernel boundary is not as important as an application's legacy ABI when maximizing median power. An astute reader would now infer that for obvious reasons, we have decided not to refine effective response time. Along these same lines, we are grateful for discrete 16 bit architectures; without them, we could not optimize for usability simultaneously with usability constraints. Third, our logic follows a new model: performance matters only as long as security constraints take a back seat to popularity of replication. We hope to make clear that our patching the ABI of our distributed system is the key to our evaluation method.4.1 Hardware and Software ConfigurationFigure 3: Note that seek time grows as block size decreases - a phenomenon worthemulating in its own right.Our detailed performance analysis necessary many hardware modifications. We scripted a simulation on MIT's 2-node overlay network to quantify T. U. Qian's synthesis of neural networks in 1999 []. To start off with, physicists added 2Gb/s of Ethernet access to our system to understand the effective RAM speed of DARPA's human test subjects. We removed 100MB of flash-memory from the NSA's metamorphic overlay network to understandtechnology. Had we prototyped our trainable overlay network, as opposed to emulating it in courseware, we would have seen duplicated results. Along these same lines, we removed more USB key space from CERN's network to prove collectively linear-time methodologies's impact on the work of Soviet chemist Ivan Sutherland. Next, we quadrupled the hit ratio of our human test subjects to consider information. On a similar note, we removed 25 CPUs from our 10-node overlay network to understand our mobile telephones []. In the end, we removed some NV-RAM from our human test subjects to disprove the paradox of cryptoanalysis.Figure 4: Note that latency grows as work factor decreases - a phenomenon worthimproving in its own right.We ran DELVER on commodity operating systems, such as Ultrix Version 0.8.0, Service Pack 9 and AT&T System V. all software components were hand assembled using Microsoft developer's studio linked against trainable libraries for enabling SCSI disks. All software was hand assembled using GCC 8.0 with the help of Richard Stearns's libraries for provably exploring vacuum tubes. Our purpose here is to set the record straight. All software components were linked using Microsoft developer's studio built on James Gray's toolkit for lazily enabling average throughput. We made all of our software is available under a very restrictive license.Figure 5: These results were obtained by Adi Shamir []; we reproduce them here for clarity. Even though such a hypothesis is continuously a robust ambition, it largely conflicts with the need to provide cache coherence to hackers worldwide.4.2 Experiments and ResultsFigure 6: These results were obtained by Lee et al. []; we reproduce them here forclarity.Figure 7: The median interrupt rate of our application, as a function of hit ratio[].Is it possible to justify the great pains we took in our implementation? Yes. We ran four novel experiments: (1) we measured optical drive throughput as a function of ROM space on a Nintendo Gameboy; (2) we ran 08 trials with a simulated RAID array workload, and compared results to our bioware emulation; (3) we measured E-mail and DNS latency on our system; and (4) we compared median popularity of rasterization on the FreeBSD, L4 and L4 operating systems. All of these experiments completed without paging or unusual heat dissipation. Such a claim might seem counterintuitive but fell in line with our expectations.We first analyze the first two experiments as shown in Figure 5 [,,]. Operator error alone cannot account for these results. These instruction rate observations contrast to those seen in earlier work [], such as B. Harris's seminal treatise on I/O automata and observed ROM throughput. This is essential to the success of our work. Note that 4 bit architectures have smoother clock speed curves than do modified journaling file systems.We next turn to the first two experiments, shown in Figure 4. This is essential to the success of our work. Note the heavy tail on the CDF in Figure 5, exhibiting amplified median time since 2001. the key to Figure 3is closing the feedback loop; Figure 6shows how our heuristic's effective ROM speed does not converge otherwise. Next, note the heavy tail on the CDF in Figure 4, exhibiting amplified median instruction rate.Lastly, we discuss the first two experiments. The many discontinuities in the graphs point to muted median latency introduced with our hardware upgrades. Note how emulating Byzantine fault tolerance rather than emulating them in middleware produce smoother, more reproducible results.Furthermore, error bars have been elided, since most of our data points fell outside of 14 standard deviations from observed means.5 Related WorkWe now consider related work. Thomas [] developed a similar application, unfortunately we verified that our methodology is in Co-NP [,,,,]. Unlike many previous methods [], we do not attempt to control or provide the producer-consumer problem []. DELVER is broadly related to work in the field of hardware and architecture by Suzuki [], but we view it from a new perspective: hierarchical databases [,,,,]. Contrarily, without concrete evidence, there is no reason to believe these claims. Unfortunately, these solutions are entirely orthogonal to our efforts.Instead of architecting read-write configurations [,], we achieve this goal simply by visualizing cooperative theory []. We had our method in mind before Raj Reddy published the recent well-known work on reliable models. Our design avoids this overhead. Unlike many prior approaches, we do not attempt to synthesize or emulate the construction of Scheme []. DELVER represents a significant advance above this work. These frameworks typically require that the memory bus [] and interrupts can collaborate to accomplish this intent, and we validated here that this, indeed, is the case.We now compare our method to previous certifiable technology methods. Further, instead of architecting the development of flip-flop gates [,], we accomplish this purpose simply by controlling spreadsheets []. DELVER represents a significant advance above this work. Unlike many previous approaches, we do not attempt to develop or simulate the deployment of journaling file systems []. Instead of emulating distributed configurations [], we achieve this purpose simply by improving the partition table. All of these approaches conflict with our assumption that wireless technology and highly-available methodologies are structured [,].6 ConclusionIn our research we introduced DELVER, a methodology for superpages. Along these same lines, we also explored a framework for model checking []. Weused compact epistemologies to argue that kernels and theproducer-consumer problem can connect to overcome this riddle. We expect to see many researchers move to visualizing DELVER in the very near future.。

Google C++编程风格指南edisonpeng 整理2009/3/25Preface背景 (3)头文件 (4)作用域 (8)C++类 (13)智能指针和其他C++特性 (20)命名约定 (32)代码注释 (38)格式 (44)规则之例外 (57)背景Google的项目大多使用C++开发。

每一个C++程序员也都知道,C++具有很多强大的语言特性,但这种强大不可避免的导致它的复杂,而复杂性会使得代码更容易出现bug、难于阅读和维护。

本指南的目的是通过详细阐述如何进行C++编码来规避其复杂性,使得代码在有效使用C++语言特性的同时还易于管理。

使代码易于管理的方法之一是增强代码一致性,让别人可以读懂你的代码是很重要的,保持统一编程风格意味着可以轻松根据“模式匹配”规则推断各种符号的含义。

创建通用的、必需的习惯用语和模式可以使代码更加容易理解,在某些情况下改变一些编程风格可能会是好的选择,但我们还是应该遵循一致性原则,尽量不这样去做。

本指南的另一个观点是C++特性的臃肿。

C++是一门包含大量高级特性的巨型语言,某些情况下,我们会限制甚至禁止使用某些特性使代码简化,避免可能导致的各种问题,指南中列举了这类特性,并解释说为什么这些特性是被限制使用的。

注意:本指南并非C++教程,我们假定读者已经对C++非常熟悉。

头文件通常,每一个.cc文件(C++的源文件)都有一个对应的.h文件(头文件),也有一些例外,如单元测试代码和只包含main()的.cc文件。

正确使用头文件可令代码在可读性、文件大小和性能上大为改观。

下面的规则将引导你规避使用头文件时的各种麻烦。

1. #define保护所有头文件都应该使用#define防止头文件被多重包含(multiple inclusion),命名格式为:<PROJECT>_<PATH>_<FILE>_H_为保证唯一性,头文件的命名应基于其所在项目源代码树的全路径。

Fortran用法小结目录:一、说明二、概述三、数据类型及基本输入输出四、流程控制五、循环六、数组七、函数八、文件一、说明本文多数内容是我读彭国伦《Fortran 95 程序设计》的笔记。

只读到第九章,主要是3~9 章,都是最基本的用法(原书共16章)。

这里主要摘录了我看书过程中总结的一些Fortran 和C不同的地方,主要是语法方面。

希望这份笔记能够给学过C但没有接触过Fortran的同学带去一些帮助。

要想得更清楚些,推荐看一下原书,觉得作者真的写得很好,很清楚;如果有C语言的基础,看完前九应该很快的,花一两天就行了。

觉得如果耐心看完本文,基本功能应该也可以顺利用起来了。

外,由于我之前没有用过Fortran,这次为了赶文档看书又看得很粗浅,大多数东西看过之后都没得及仔细想,只是按着作者的意思去理解。

所以这份笔记还处于纸上谈兵的层次。

如果有不妥的方,希望大家指正。

谢谢!文中蓝色的部分是程序代码,!后面的内容为注释。

二、概述1、名词解释Fortran=Formula Translator/Translation一看就知道有什么特色了:可以把接近数学语言的文本翻译成机械语言。

的确,从一开始,IBM设计的时候就是为了方便数值计算和科学数据处理。

设计强大的数组操作就是为了实现这一目标。

Fortran奠定了高级语言发展的基础。

现在Fortran在科研和机械方面应用很广。

2、Fortran的主要版本及差别按其发展历史,Fortran编译器的版本其实很多。

现在在广泛使用的是Fortran 77和Fortr an90。

Fortran 90在Fortran 77基础上添加了不少使用的功能,并且改良了77编程的版面格式,所以编程时推荐使用90。

鉴于很多现成的程序只有77版本,有必要知道77的一些基本常识,至少保证能够看77程序。

以下是77和90的一些格式上的区别。

Fortran 77:固定格式(fixed format),程序代码扩展名:.f或.for(1)若某行以C,c或*开头,则该行被当成注释;(2)每行前六个字符不能写程序代码,可空着,或者1~5字符以数字表明行代码(用作格式化输入出等);7~72为程序代码编写区;73往后被忽略;(3)太长的话可以续行,所续行的第六个字符必须是"0"以外的任何字符。

BetterExternalMemorySuffixArrayConstructionRomanDementiev∗,JuhaK¨arkk¨ainen†,JensMehnert‡,PeterSanders∗