实验七 硬件电子琴电路设计

- 格式:doc

- 大小:338.50 KB

- 文档页数:5

电子设计自动化实验报告

实验七硬件电子琴电路设计

一、实验目的

1.熟悉QuartusⅡ软件应用环境,了解实验流程。

2.编写简单的Verilog代码,并在QuartusⅡ中进行调试和验证,并在EDA6000中

下载代码和验证。

3.掌握硬件电子琴电路的设计方法,根据键入发出不同的音阶。

二、实验原理

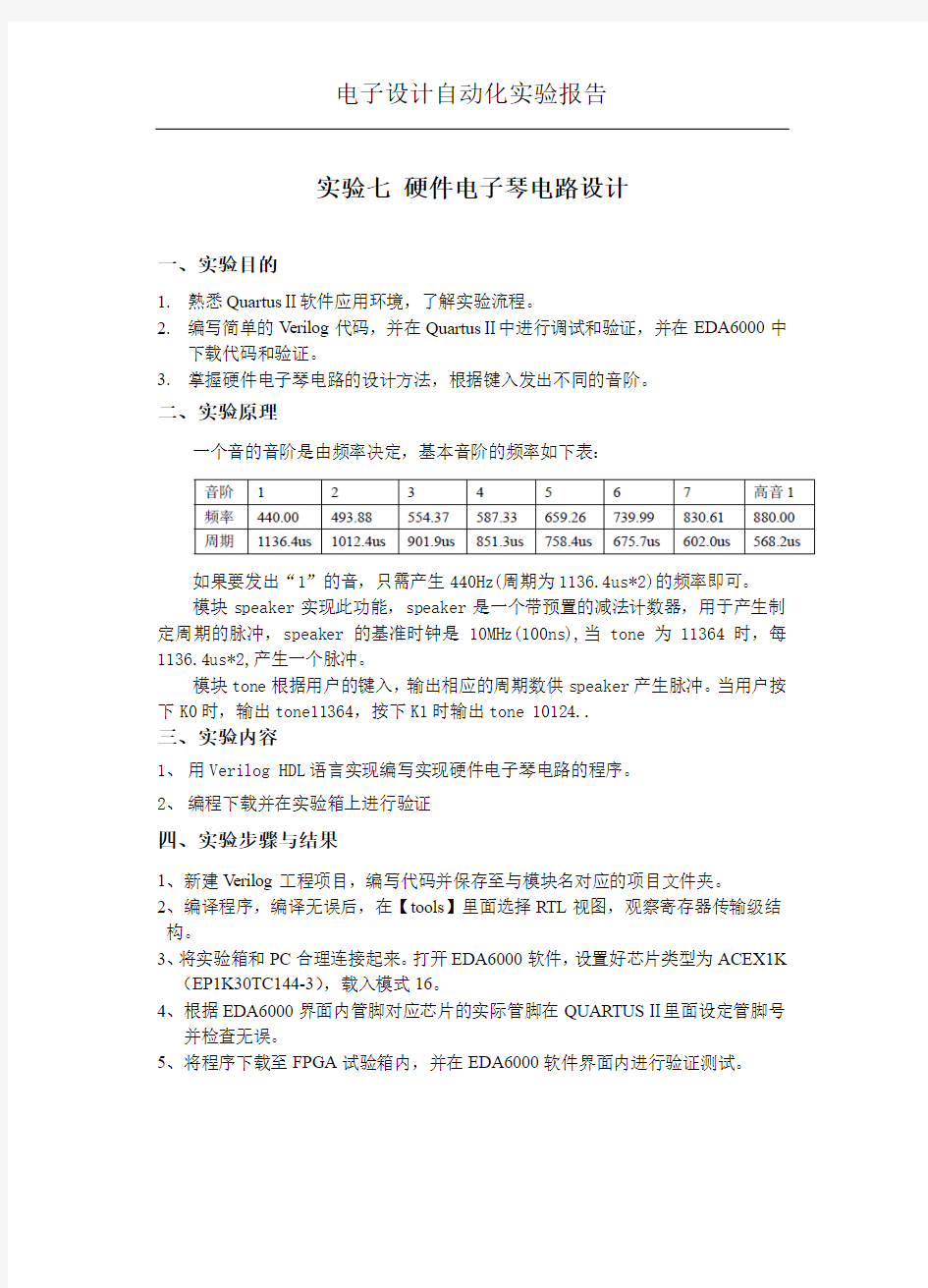

一个音的音阶是由频率决定,基本音阶的频率如下表:

如果要发出“1”的音,只需产生440Hz(周期为1136.4us*2)的频率即可。

模块speaker实现此功能,speaker是一个带预置的减法计数器,用于产生制定周期的脉冲,speaker的基准时钟是10MHz(100ns),当tone为11364时,每1136.4us*2,产生一个脉冲。

模块tone根据用户的键入,输出相应的周期数供speaker产生脉冲。当用户按下K0时,输出tone11364,按下K1时输出tone 10124..

三、实验内容

1、用Verilog HDL语言实现编写实现硬件电子琴电路的程序。

2、编程下载并在实验箱上进行验证

四、实验步骤与结果

1、新建Verilog工程项目,编写代码并保存至与模块名对应的项目文件夹。

2、编译程序,编译无误后,在【tools】里面选择RTL视图,观察寄存器传输级结构。

3、将实验箱和PC合理连接起来。打开EDA6000软件,设置好芯片类型为ACEX1K (EP1K30TC144-3),载入模式16。

4、根据EDA6000界面内管脚对应芯片的实际管脚在QUARTUSⅡ里面设定管脚号

并检查无误。

5、将程序下载至FPGA试验箱内,并在EDA6000软件界面内进行验证测试。

程序源代码:

module dzq(pcode,phigh,pspeaker,clk,key_in);

input clk;

input [7:0]key_in;

output phigh,pspeaker;

output [2:0]pcode;

reg phigh,pspeaker,lock;

integer q1,Q;

reg [2:0]pcode;

always @ (posedge clk )

begin

if(Q==0)

begin Q<=q1; lock<=1;end

else begin Q<=Q-1; lock<=0;end

end

always @(clk or key_in)

begin

case (key_in)

8'b00000001: begin phigh=0;pcode=3'b001;q1<=11364; end

8'b00000010: begin phigh=0;pcode=3'b010;q1<=10124;end

8'b00000100: begin phigh=0;pcode=3'b011;q1<=9019; end

8'b00001000: begin phigh=0;pcode=3'b100;q1<=8513; end

8'b00010000: begin phigh=0;pcode=3'b101;q1<=7584; end

8'b00100000: begin phigh=0;pcode=3'b110;q1<=6757; end

8'b01000000: begin phigh=0;pcode=3'b111;q1<=6020; end

8'b10000000: begin phigh=1;pcode=3'b001;q1<=5682; end

default : begin phigh=0;pcode=3'b000;q1<=0; end

endcase

end

always @(posedge lock)

pspeaker<=~pspeaker;

endmodule

编译:选择processing---start compilation命令,开始编译。也可直接点击面板上编译按钮。结果如图:

结构图,结果如图:

时序仿真

功能仿真

设置引脚:启动EDA6000,连接试验箱。装入模式16。根据右侧管脚提示进行管脚锁定。在QuartusⅡ界面中选择assignment—pins命令。可以用拖放的方式指定管脚,也可以在location中输入管脚号。最终结果如图所示:

试验箱测试:在QuartusⅡ界面中选择tools--- programmer命令。在弹出的界面中Mode选为passive serial。点击add hardware,选择byteblasterMV,添加驱动成功后,勾选program/configure,点击start,下载文件到试验箱。点击EDA6000start,开始测试。

五、实验总结

通过本次实验掌握了如何用Verilog HDL语言实现硬件电子琴电路的原理,进一步掌握了课堂上所学到的知识,但同时充分的感觉到了自己的不足之处,今后一定要加强自己弱势方面的学习,用心学好EDA教科书上的知识,并抽时间在课外

进行深入地学习。