电子琴实验报告乐曲硬件演奏电路设计本科论文

- 格式:docx

- 大小:611.69 KB

- 文档页数:17

电子琴的实验报告 WTD standardization office【WTD 5AB- WTDK 08- WTD 2C】单片机课程设计设计题目电子琴指导老师:苏参与实验者: moxiaoxiao专业:统本电信0801地点:3#楼北楼605电子琴一.设计目的:(1).培养综合运用知识的能力(2).朋友查阅资料,使用工程设计标准及编写设计文档的能力.(3).掌握单片机应用系统的设计方法.(4).提高计算机绘图能力二.设计任务:利用DP51PROC实验系统上的定时器/计数器,按键和蜂鸣器单元。

用单片机I/O口线控制蜂鸣器发出不同的音调,程序检测按键状态,7个按键中某一键按下时,蜂鸣器对应标称音阶.三.设计与调试环境KEIL uVision2 是众多单片机应用开发软件中优秀的软件之一,它支持众多不同公司的 MCS51 架构的芯片,它集编辑,编译,仿真等于一体,同时还支持,PLM ,汇编和 C 语言的程序设计,它的界面和常用的微软VC++的界面相似,界面友好,易学易用,在调试程序,软件仿真方面也有很强大的功能。

1:按下面的步骤建立一个项目:图 1-4 选取芯片图 1-5 新建程序文件(1)点击图1-5 中的 3 保存新建的程序,也可以用菜单 File-Save 或快捷键 Ctrl+S 进行保存。

因是新文件所以保存时会弹出类似图1-3 的文件操作窗口,我们把第一个程序命名为,保存在项目所在的目录中,这时程序单词有了不同的颜色,说明 KEIL 的 C 语法检查生效了。

如图1-6 鼠标在屏幕左边的 Source Group1 文件夹图标上右击弹出菜单,在这里可以做项目中增加减少文件等操作。

我们选“Add File to Group‘SourceGroup 1’”弹出文件窗口,选择刚刚保存的文件,按 ADD 按钮,关闭文件窗,程序文件已加到项目中了。

这时在 Source Group1 文件夹图标左边出现了一个小+号说明,文件组中有了文件,点击它可以展开查看。

![简易电子琴的设计[优秀范文五篇]](https://uimg.taocdn.com/51a3f65aa36925c52cc58bd63186bceb19e8ed12.webp)

简易电子琴的设计[优秀范文五篇]第一篇:简易电子琴的设计毕-1毕业设计任务书专业:班级:学生签名:一、设计题目简易电子琴的设计二、设计内容要求和技术参数(1)要求能够发出1、2、3、4、5、6、7等七个音符。

(2)使用元件:AT89C51、LM324,喇叭,按键等三、设计应完成的技术资料(1)写出设计过程(包括原理、方案)(2)系统硬件图并描述各部分的功能(3)对软件编程、排错调试、焊接技术、相关仪器设备的使用技能等方面得到较全面的锻炼和提高(4)写出此次设计的心得体会四、设计考核的主要知识与技能本课题是电子技术与单片机混合的综合性课题,主要考核《电子技术》与《单片机》的基本知识和应用能力。

五、设计时间:六、指导教师签名:第二篇:简易电子琴电路的设计电子综合实训任务书学生姓名:专业班级:指导老师:易迎彦工作单位:武汉理工大学理学院题目:简易电子琴电路的设计初始条件:直流可调稳压电源一台、万用表一块、面包板一块、元器件若干、剪刀、镊子等必备工具要求完成的主要任务:(包括电子综合实训工作量及其技术要求以及说明书撰写等具体要求)1、技术要求:设计一个玩具电子琴,设8个琴键,分别代表1、2、3、4、5、6、7、į八个不同音符,每按下一个琴键,扬声器发出一个音符的声音。

演奏时的音量和节拍可以调节2、主要任务:(一)设计方案(1)按照技术要求,提出自己的设计方案(多种)并进行比较;(2)以CC7555时基集成电路为主,设计一个玩具电子琴电路(实现方案);(3)依据设计方案,进行预答辩;(二)实现方案(4)根据设计的实现方案,画出电路逻辑图和装配图;(5)查阅资料,确定所需各元器件型号和参数;(6)在面包板上组装电路;(7)自拟调整测试方法,并调试电路使其达到设计指标要求;(8)撰写设计说明书,进行答辩。

3、撰写电子综合实训说明书:封面:题目,学院,专业,班级,姓名,学号,指导教师,日期任务书目录(自动生成)正文:1、技术指标;2、设计方案及其比较;3、实现方案;4、调试过程及结论;5、心得体会;6、参考文献成绩评定表时间安排:电子综合实训时间:19周-20周19周:明确任务,查阅资料,提出不同的设计方案(包括实现方案)并答辩; 20周:按照实现方案进行电路布线并调试通过;撰写电子综合实训说明书。

数字电子技术综合实验报告——简易电子琴(总42页)--本页仅作为文档封面,使用时请直接删除即可----内页可以根据需求调整合适字体及大小--数字电子技术综合实验报告2012--2013学年第二学期姓名:学号:班级:实验时间:实验指导老师:目录一、设计任务 (2)二、设计方案 (2)三、系统框图 (3)四、方案实现 (3)1.乐曲演奏的原理 (3)2.总体方案 (4)五、实验结果 (6)六、方案优化 (7)七、心得体会 (7)附录 (7)1.VHDL源程序 (7)2.各层次原理图 (35)3.编译报告 (40)题目: 简易电子琴设计摘要电子琴的设计大规模可编程逻辑器件(FPGA)作为系统的核心控制部分通过软件的设计编写然后进行软硬件的调试运行最终达到设计电路的乐器演奏、选歌及显示功能。

设计中采用计数原理控制演奏器发声,对音乐发生所必须确定的音符和节拍分别用程序语言实现。

可以用它来弹奏和播放乐曲。

特点是设计思路简单、清晰。

关键字:电子琴 CPLD一、设计任务1.基本要求(1)具有一般弹奏功能;(2)自动播放功能;(3)数码显示音符功能。

2.发挥部分(1)能通过选择键在多首歌曲中选择播放;(2)输出增加功率放大电路,增加歌曲容量;(3)增加音效或节拍可调;(4)无线弹奏。

二、设计方案采用大规模可编程逻辑器件(FPGA),利用quartusII,通过verilog代码实现简易电子琴演奏电路。

三、系统框图四、方案实现1.乐曲演奏的原理:乐曲演奏的原理:组成乐曲的每个音符的频率值(音调)以及持续时间(音长)是乐曲能持续演奏所需的两个基本数据,因此只要控制输出到扬声器的激励信号的频率的高低和持续的时间,就可以使扬声器发出持续的乐曲声。

音调的控制频率的高低决定了音调的高低。

音乐的十二平均率规定:每两个八度音(如简谱中的中音1与高音1)之间的频率相差一倍。

在两个八度音之间,又可分为十二个半音,每半个音的频率比为。

电子琴实训报告

一、实训内容

本次实训内容为电子琴基础实践,包括基础音乐理论学习、琴键按键技巧训练、曲目弹奏等内容。

二、实训过程

1. 音乐理论学习

在实训开始前,老师首先给我们讲解了音乐基础知识,包括音符、节奏、调式等内容。

通过这些知识的学习,我们更好地理解了音乐作品。

2. 琴键按键技巧训练

接下来,老师让我们开始琴键按键技巧的训练。

我们从最基础的音阶开始,一步步地学习了琴键的按法和演奏技巧。

经过反复练习和指导,我们逐渐掌握了正确的按键技巧。

3. 曲目弹奏

在学习了基础的音乐理论和琴键技巧后,我们开始学习一些曲

目的弹奏。

老师为我们精心挑选了一些适合初学者的曲目,包括

流行歌曲、古典音乐等。

我们通过练习这些曲目,更好地掌握了

琴键技巧和演奏技巧。

三、实训成果

通过两周的实践学习,我们在电子琴方面取得了很多进步。

我

们可以更加熟练地掌握琴键按键技巧,能够演奏一些简单的曲目。

同时,我们对音乐理论有了更深入的了解,能够更好地欣赏音乐

作品。

四、实训收获

通过这次实训,我们不仅学到了电子琴方面的知识和技巧,更

重要的是培养了我们的音乐素养和音乐爱好。

我们在实训中感受

到了音乐的美妙,也更深切地体会到了学习音乐的重要性。

五、总结

此次电子琴实践是一次非常有意义的学习经历。

我们在实践中不断地探索、学习、进步,让自己更加熟练地掌握电子琴技巧、完善音乐素养。

我们相信,这次实践将为我们未来的音乐之路奠定坚实的基础。

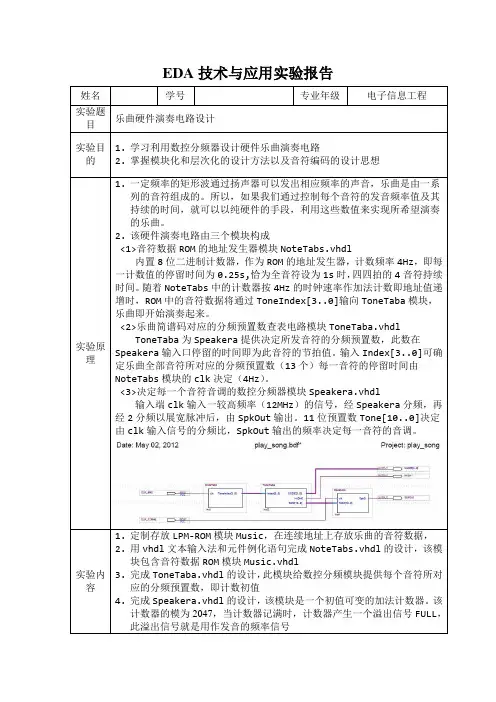

EDA技术与应用实验报告姓名学号专业年级电子信息工程实验题目乐曲硬件演奏电路设计实验目的1.学习利用数控分频器设计硬件乐曲演奏电路2.掌握模块化和层次化的设计方法以及音符编码的设计思想实验原理1.一定频率的矩形波通过扬声器可以发出相应频率的声音,乐曲是由一系列的音符组成的。

所以,如果我们通过控制每个音符的发音频率值及其持续的时间,就可以以纯硬件的手段,利用这些数值来实现所希望演奏的乐曲。

2.该硬件演奏电路由三个模块构成<1>音符数据ROM的地址发生器模块NoteTabs.vhdl内置8位二进制计数器,作为ROM的地址发生器,计数频率4Hz,即每一计数值的停留时间为0.25s,恰为全音符设为1s时,四四拍的4音符持续时间。

随着NoteTabs中的计数器按4Hz的时钟速率作加法计数即地址值递增时,ROM中的音符数据将通过ToneIndex[3..0]输向ToneTaba模块,乐曲即开始演奏起来。

<2>乐曲简谱码对应的分频预置数查表电路模块ToneTaba.vhdlToneTaba为Speakera提供决定所发音符的分频预置数,此数在Speakera输入口停留的时间即为此音符的节拍值。

输入Index[3..0]可确定乐曲全部音符所对应的分频预置数(13个)每一音符的停留时间由NoteTabs模块的clk决定(4Hz)。

<3>决定每一个音符音调的数控分频器模块Speakera.vhdl输入端clk输入一较高频率(12MHz)的信号,经Speakera分频,再经2分频以展宽脉冲后,由SpkOut输出。

11位预置数Tone[10..0]决定由clk输入信号的分频比,SpkOut输出的频率决定每一音符的音调。

实验内容1.定制存放LPM-ROM模块Music,在连续地址上存放乐曲的音符数据,2.用vhdl文本输入法和元件例化语句完成NoteTabs.vhdl的设计,该模块包含音符数据ROM模块Music.vhdl3.完成ToneTaba.vhdl的设计,此模块给数控分频模块提供每个音符所对应的分频预置数,即计数初值4.完成Speakera.vhdl的设计,该模块是一个初值可变的加法计数器。

电子琴实习报告篇一:电子琴设计实习报告单片机原理与应用技术课程设计报告基于单片机的电子琴控制系统专业班级:* 姓名:*时间:~指导教师:*XX年 1月 10日基于单片机的电子琴控制系统课程设计任务书1.设计目的与要求设计出一个基于单片机的电子琴控制系统。

准确地理解有关要求,独立完成系统设计,要求所设计的电路具有以下功能:(1)实现基本的音符1-7的弹奏和数码显示。

(2)自动弹奏播放一首简单的歌曲。

(3)随机弹奏曲子时,可以实时记忆,并可复读(重复播放)。

(扩展功能,可选择设计)2.设计内容(1)画出电路原理图,正确使用逻辑关系;(2)确定元器件及元件参数;(3)进行电路模拟仿真;(4)SCH 文件生成与打印输出。

3.编写设计报告写出设计的全过程,附上有关资料和图纸,有心得体会。

4.答辩在规定时间内,完成叙述并回答问题。

基于单片机的电子琴控制系统班级:* 姓名:*摘要:电子琴是现代电子科技与音乐结合的产物,是一种新型的键盘乐器,采用半导体集成电路,对乐音信号进行放大,通过扬声器产生音响。

用户可以自己弹奏乐曲,也可以自动伴奏。

单片机具有强大的控制功能和灵活的编程实现特性,便于设计各种以单片机为核心的控制系统。

本课程设计是用AT89S51单片机为核心控制元件,用其他外围电路配合单片机组成一个简单的电子琴控制系统,能实现音乐弹奏,自动播放音乐等功能。

本系统功能由单片机控制实现,具有运行稳定,电路简单,软件功能完善,控制系统可靠等特点。

关键词:电子琴,单片机,外围电路,系统分析,汇编程序,仿真,PCB,调试1 引言本次设计的电子琴控制系统由单片机最小系统加上按键电路,数码显示电路,声音播放电路组成,通过单片机内烧写的汇编程序来输出控制信号控制外围电路的工作。

电子琴设计不同于其他设计,需要输出1到7七个不同音阶的声音,因此信号的输出有其特殊性,可以利用单片机定时计数器产生不同频率的方波信号来形成七个不同的音阶,不同音阶的组合就能输出我们想要的音乐了。

摘要本设计是基于AT89S52单片机的简易电子琴设计。

主要组成是以51单片机最小系统为核心,通过键盘获取按键信息,通过运用单片机定时器等部件实现蜂鸣器发声同时用数码管同步显示。

本系统具有播放歌曲及选取按键输入高、中、低音的功能。

本设计的特点是:大部分功能通过软件实现,使电路简单明了,系统稳定性好。

电子琴是电子科技与音乐结合的产物是一种新型的键盘乐器。

一首音乐是许多不同的音阶组成的,而每个音阶对应着不同的频率,这样我们就可以利用不同的频率的组合,即可构成我们所想要的音乐了,当然对于单片机来产生不同的频率非常方便,我们可以利用单片机的定时计数器T0来产生这样方波频率信号,因此,我们只要把一首歌曲的音阶对应频率关系弄正确即可。

关键字:AT89S52,按键,数码管,蜂鸣器,音阶。

(要求宋体、小四号,行间距为固定值22磅。

字数500字以上。

介绍你所作设计的主要内容及主要方法和取得的结果,是整个报告的概括性内容,不要超过一页面)目录(小三号居中,加粗)1 概述………………………………………………………………………………1.1 51系列单片机简介89系列单片机是ATMEL公司的8位FLASH单片机系列。

89系列单片机是以8031为核心构成的,它和8051系列单片机外部端子是一样的、兼容的,其最大特点是片内含有FLASH存储器。

AT89S52单片机是一种低功耗、高性能、内含4KB的闪速存储器(Flash Memory)的8位微控制器。

片内闪速存储器的程序代码或数据可在线写入,也可通过常规的编程器编程。

(宋体、小四,行间距固定值18磅。

以下相同要求)……………………1.2 电子琴简介电子琴为键盘乐器,采用半导体集成电路,对乐音信号进行放大,通过扬声器产生音响。

电子琴有多种类型,为业余型和专业型。

使用五线谱,多为高低音双行记谱。

有时也用中音谱。

电子琴又称作电子键盘,属于电子乐器,发音音量可以自由调节。

音域较宽,和声丰富,甚至可以演奏出一个管弦乐队的效果,表现力极其丰富。

电子琴设计报告院系:计算机科学学院专业:计算机科学与技术学号:201003784姓名:张林峰班级:计科1002设计时间:2012.10.22设计地点:4#2号机房指导教师:严圣华目录一、总体方案二、硬件介绍三、音乐产生原理四、软件设计五、电子琴演示六、实验体会一、总体方案1.1设计要求1.要求达到电子琴的基本功能,可以用弹奏出简单的乐曲。

2.用键盘作出电子琴的按键,每键代表一个音符。

3.各音符按一定的顺序排列,必须符合电子琴的按键排列顺序。

4.固定音乐播放有按键控制。

1.2电子琴系统的组成STC89C52单片机设计微型电子琴的方法,仅需STC89C52最小系统,扩展一组矩阵键盘,再接一组发光二极管用来指示电子琴的工作状态。

本系统分为两个部分,一个是音乐另一个是电子琴。

音乐播放部分:音乐实际上是有固定周期的信号。

本文介绍用STC89C52的两个定时器(如T0,T1)控制,在P1.3脚上输出方波周期信号,产生乐音电子琴弹奏部分:实际上就是把每个按键所对应的值经过处理后发给单片机,再在单片机内把数字当作指针指向所对应的音符。

二、硬件介绍2.1 STC89C52STC89C52是一种低功耗、高性能CMOS8位微控制器,具有8K 在系统可编程Flash 存储器。

在单芯片上,拥有灵巧的8 位CPU 和在系统可编程Flash,使得STC89C52为众多嵌入式控制应用系统提供高灵活、超有效的解决方案。

具有以下标准功能:8k字节Flash,512字节RAM,32 位I/O 口线,,内置4KB EEPROM,MAX810复位电路,三个16 位定时器/计数器,一个6向量2级中断结构,全双工串行口。

2.2 STC89C52引脚图2.3引脚功能介绍在这里就只介绍一下制作电子琴所用到的一些引脚功能。

VCC:供电电压。

GND:接地。

P3.2 /INT0(外部中断0)P3.3 /INT1(外部中断1)P3.4 T0(记时器0外部输入)P3.5 T1(记时器1外部输入)P3口连接矩阵键盘用来控制音符输出及音乐播放。

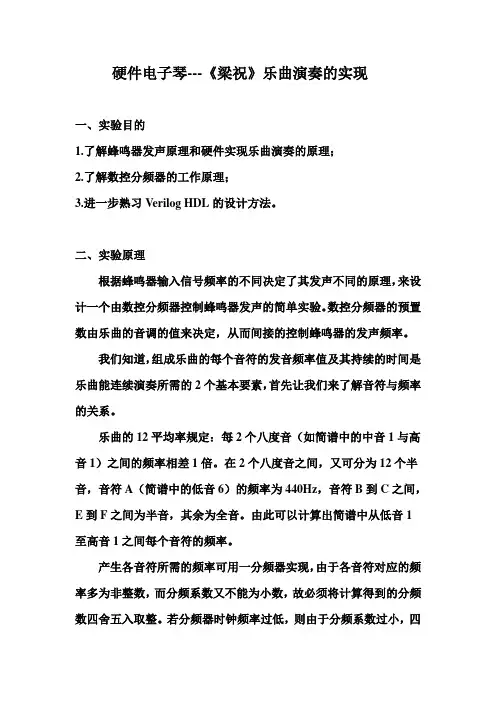

硬件电子琴---《梁祝》乐曲演奏的实现一、实验目的1.了解蜂鸣器发声原理和硬件实现乐曲演奏的原理;2.了解数控分频器的工作原理;3.进一步熟习Verilog HDL的设计方法。

二、实验原理根据蜂鸣器输入信号频率的不同决定了其发声不同的原理,来设计一个由数控分频器控制蜂鸣器发声的简单实验。

数控分频器的预置数由乐曲的音调的值来决定,从而间接的控制蜂鸣器的发声频率。

我们知道,组成乐曲的每个音符的发音频率值及其持续的时间是乐曲能连续演奏所需的2个基本要素,首先让我们来了解音符与频率的关系。

乐曲的12平均率规定:每2个八度音(如简谱中的中音1与高音1)之间的频率相差1倍。

在2个八度音之间,又可分为12个半音,音符A(简谱中的低音6)的频率为440Hz,音符B到C之间,E到F之间为半音,其余为全音。

由此可以计算出简谱中从低音1至高音1之间每个音符的频率。

产生各音符所需的频率可用一分频器实现,由于各音符对应的频率多为非整数,而分频系数又不能为小数,故必须将计算得到的分频数四舍五入取整。

若分频器时钟频率过低,则由于分频系数过小,四舍五入取整后的误差较大;若时钟频率过高,虽然误差较小,但会增加分频器的分频级数。

实际的设计应综合考虑两方面的因素,在尽量减小频率误差的前提下取合适的时钟频率。

这里设计的乐曲发生器选取5MHz的基准频率。

即使基准频率有所改变,实际上,只要各个音符间的相对频率关系不变,演奏出的乐曲听起来都不会“走调”。

化蝶简谱中各音符对应得分频系数如下表所示。

音符分频系数音符分频系数低音3 7584 低音5 6378 低音6 5682 低音7 5062 中音1 4778 中音2 4257 中音3 3792 中音5 3189 中音6 2841 高音1 2391为了减小输出的偶次谐波分量,最后输出到扬声器的波形应为对称方波,因此在到达扬声器之前,有一个二分频的分频器。

所以表中的分频系数是从5MHz频率二分频得到的2.5MHz频率基础上计算得出的。

毕业设计(论文)( 2013届)题目电子琴音乐的产生与演奏电路的设计学院电子与电气工程系专业应用电子技术班级应电1001班学号 *************学生姓名王雅琴指导教师黎杨梅摘要本文的主要内容是用STC89C51单片机为核心控制元件,设计一个可以实现演奏和播放音乐的简易电子琴。

以单片机作为主控核心,与键盘、扬声器等模块组成核心主控制模块。

在主控模块上设有16个按键和扬声器,应用中断系统和定时/计数原理控制其发声。

本系统运行稳定,其优点是硬件电路简单,软件功能完善,控制系统可靠,性价比较高等,具有一定的实用和参考价值。

关键词单片机;电子琴;键盘目录1.引言 (1)2.总体方案 (1)2.1.系统的设计要求 (1)2.2.电子琴系统的组成 (2)2.3.系统设计框图 (2)3. 硬件电路设计简介 (3)3.1.单片机STC89C51 (3)3.1.1.STC89C51的简介 (3)3.1.2.管脚功能 (4)3.1.3.在线编程 (5)3.1.4.电子琴系统单片机最小系统设计图 (5)3.2.矩阵式键盘 (6)3.2.1.矩阵式键盘的结构与工作原理 (6)3.2.2.矩阵式键盘的按键识别方法 (6)3.2.3.键盘接口必须具备的4个基本功能 (7)3.2.4.电子琴系统矩阵键盘硬件电路图 (7)3.3.音频功放电路设计 (8)3.3.1.LM386的结构与工作原理 (8)3.3.2.LM386的主要特性 (8)3.3.3.LM386的典型应用电路 (8)3.3.4.电子琴中音频功放电路图 (9)4. 软件设计 (10)4.1.音乐播放程序设计 (10)4.1.1.音乐背景知识 (10)4.1.2.单片机产生音乐的方法 (10)4.1.3.音乐播放软件设计 (12)4.2.放歌子程序设计 (13)4.3.系统整体软件流程设计 (14)5. 系统调试 (14)5.1.keil简介 (15)5.2.硬件调试 (15)5.3.软件调试 (15)5.4.综合调试 (15)6. 结论 (16)参考文献 (17)谢辞 (18)1.引言单片微型计算机是大规模集成电路技术发展的产物,属第四代电子计算机,他具有高性能、高速度、体积小、价格低廉、稳定可靠、应用广泛的特点。

武夷学院实验报告课程名称:逻辑设计与FPGA 项目名称:乐曲硬件演奏电路设计姓名:专业:微电子学班级: 14微电子学号: 04 实验日期实验预习成绩(百分制)实验指导教师签字:二、 实验过程记录部分:1.实验过程记录:1.1 输入信号锁相环PLL0调节: 图2.1 锁相环 管脚clk_50m (设置为B12)接入FPGA 内部的50mhz 的时钟信号,C0口为得到数控分屏器模块的输入时钟750KHZ ,将分频比设置为1/67,即50000000HZ/67=74.6K约等于75K ;c1口为2KHZ (配合下级的500分频模块),设置为:c1=50000000HZ/25000=2KHZ 。

1.2 500分频模块count500(即500进制的计数器):图2.2 分频电路程序设计 如图2.2,因为梁祝歌曲只用低音和中音来演奏,为1/4拍,即四分之一拍,每个音符持续0.25秒的时间。

因为前级电路已经实现了从50MHZ 到2KHZ 的转换,要得到4HZ 的频率,则用500进制的计数器(0到499的计数)产生的进位信号对2KHZ 实现500分频(输出波形分析见后)。

1.3 乐曲长度控制计数器cnt138设计:图2.3 乐曲长度控制计数器程序及元件图经查阅《EDA技术实用教程(第五版)》可知,《梁祝》这首歌曲总共有139个音符,其中包含末尾的3个休止符。

如图2.3,因此为了产生这139音符,因此想到开发一个139进制的计数器(计数值:0到138),实现用139状态代表139个音符。

又因为要配合下一级音符谱码存储模块的输入(ROM的输入一般为偶数位),因此将原本用7路线就可以表示完成的输出端cnt8增加一位线宽。

注:在本程序中,输出端cnt8由于定义成integer整型,在Quartus中被自动分配成了7根;也可以定义成vector型,而此时需要注意配合下级电路的权位最好写成cnt8: out std_logic_vector(7 downto 0).1.4 音符谱码存储模块设计构建:1.4.1 ROM的设置:图2.4 音符谱码存储模块ROM音符谱码存储模的主体构想,是为了让前级模块所产生的139个状态与实际音符(Do Re Mi Fa So La Si)构成映射。

单片机实验报告电子琴单片机实验报告电子琴引言:电子琴是一种流行的乐器,它通过电子元件产生声音,具有丰富的音色和音效。

在本次实验中,我们使用单片机来设计和制作一个简单的电子琴,通过按键触发不同的音调,实现基本的音乐演奏功能。

本文将介绍电子琴的原理、设计过程和实验结果。

一、原理电子琴的原理是基于音频合成技术,通过控制不同频率的声音波形来产生不同的音调。

而单片机作为电子琴的控制核心,负责接收按键信号,并通过输出引脚控制声音的发声。

具体来说,单片机通过读取按键的状态,判断按键是否按下,并根据按键的不同触发相应的音调发声。

二、设计过程1. 硬件设计在硬件设计方面,我们需要准备以下元件:单片机、按键、蜂鸣器、电阻、电容等。

首先,将按键连接到单片机的输入引脚上,以便检测按键的状态。

然后,将蜂鸣器连接到单片机的输出引脚上,以便通过控制引脚输出高低电平来实现声音的发声。

最后,根据需要添加电阻和电容等元件,以保证电路的稳定性和正确性。

2. 软件设计在软件设计方面,我们需要使用单片机的编程语言来实现电子琴的功能。

首先,我们需要设置单片机的输入引脚和输出引脚,并定义按键的状态和蜂鸣器的控制信号。

然后,我们需要编写程序来实现按键的检测和音调的控制。

具体来说,当按键按下时,单片机会读取按键的状态,并根据不同的按键触发不同的音调,同时控制蜂鸣器的输出信号,以实现声音的发声。

三、实验结果在实验过程中,我们成功地设计和制作了一个简单的电子琴。

通过按下不同的按键,我们可以听到不同的音调发声,从而演奏出简单的音乐。

实验结果表明,我们设计的电子琴具有良好的音效和音色,能够满足基本的音乐演奏需求。

结论:通过本次实验,我们深入了解了电子琴的原理和设计过程,并成功地制作了一个简单的电子琴。

通过单片机的控制,我们可以实现按键触发不同音调的发声,从而演奏出简单的音乐。

电子琴作为一种流行的乐器,具有广泛的应用和发展前景。

通过不断的学习和实践,我们相信可以设计出更加复杂和高级的电子琴,为音乐爱好者提供更多的乐器选择和音乐表达方式。

FPGA-CPLD原理及应用课程设计报告题目:电子琴学院: 信息与电子工程学院专业: 电子科学与技术学号:姓名:指导老师:时间:2013-7-15~2013-7-20一、摘要电子琴是数字电路中的一个典型应用。

在实际的硬件设计中用到的器件非常多,连线比较复杂,同时会产生比较大的延时,从而造成测量误差较大,可靠性不好。

以EDA工具作为开发手段,运用VHDL硬件描述语言将使整个系统大大简化,提高了电子琴整体的性能和可靠性。

关键词:电子琴 SOPC SOPC Builder Nios II DE2 音符二、设计要求方案一:采用数字逻辑电路制作,用IC拼凑焊接实现。

其特点是直接用现成的IC组合而成,简单方便,但本系统需用到许多分频器,这就使得需要用到相当多的IC,从而造成了体积过于庞大,而且连线也会比较复杂。

方案二:采用单片机实现,通过软件编程,仿真后将程序用编程器写入到单片机芯片上,该方案成本低,稳定度也比较好,但外围电路多,特别是播放音乐时需要用到大容量的外部存储器,这样就增加了编程难度,调试不够直观,也不够灵活方便。

方案三:采用可编程逻辑器件(FPGA)制作,将所有器件集成在一块芯片上,大大减小了电子琴的体积,用VHDL编程实现时更加方便,而且易于进行功能扩展,并可调试仿真,制作时间大大缩短,因此选用了方案三进行设计。

电子琴设计原理乐曲都是由一连串的音符组成,按照乐曲的乐谱依次输出这些音符所对应的频率,就可以在扬声器上连续地发出各个音符的音调。

为了准确地演奏出一首乐曲,仅仅让扬声器能够发出声音是远远不够的,还必须准确地控制乐曲的节奏,即每个音符的持续时间。

由此可见,乐曲中每个音符的发音频率以及音符持续的时间是乐曲能够连续演奏的两个关键因素。

乐曲的12平均率规定:每2个八度音之间的频率要相差1倍,比如简谱中的中音2与高音2。

在2个八度音之间,又可分为12个半音。

另外,音符A(简谱中的低音5)的频率为392Hz,音符E到F之间、B到C之间为半音,其余为全音。

单片机电子琴设计报告硬件设计部分————————————————————————————————作者:————————————————————————————————日期:课程设计报告课程名称:微机原理课程设计题目:简易电子琴设计学院:系:专业:班级:学号:学生姓名:起讫日期:指导教师:摘要随着社会的发展进步,音乐逐渐成为我们生活中很重要的一部分,有人曾说喜欢音乐的人不会向恶。

我们都会抽空欣赏世界名曲,作为对精神的洗礼。

本论文设计一个基于单片机的简易电子琴。

电子琴是现代电子科技与音乐结合的产物,是一种新型的键盘乐器。

它在现代音乐扮演着重要的角色,单片机具有强大的控制功能和灵活的编程实现特性,它已经溶入现代人们的生活中,成为不可替代的一部分。

本系统是以51系列单片机AT89C51为主控制器,附有独立键盘、点阵、扬声器组成。

系统完成显示输入信息、播放相应音符等基本功能。

本系统运行稳定,其优点是硬件电路简单,软件功能完善,控制系统可靠,性价比较高等,具有一定的实用和参考价值。

关键词:AT89C51,点阵,独立键盘,蜂鸣器.目录第1章概述—-—--————--—--—--———-—-—---——--—---——————————-——-—-—-———-———-—---————-—-—-—-——-———3第2章课程设计任务及要求---—---—-———————-—---——-———-———---——----———-——--—-———-———-—32。

1 设计任务---—--—-———-—---————--——-——---—-—---——————---—---—-—----—---————-————-—-—-—-—-—32.2 设计要求--—--——-———----—-—--—-——-----———-—-———-——----—-—--———----—---—————-—-—------—-—3第3章硬件设计---—-——--—-—---——--—--------———---—----———----—-—-———-———--—-—--—-——--—-——---33.1设计方案--——-—----—-----——--—————————-—-—-———--—-----——-——-—--—----——--—————---—-——————43。

基于单片机的简易电子琴设计摘要随着科学技术的不断发展,单片机的应用日益成熟。

单片机集成度高、处理功能强大、价格低廉使其在各个领域得到广泛应用。

同时电子琴作科学技术与音乐共同发展的产物,在这个电子信息化的时代,为音乐的大众化做出了不可代替的贡献。

本文主要介绍一种基于51单片机的简易电子琴设计方案。

它采用了STC公司出品的一款低功耗、高性能单片机STC89C52芯片作为主控单元,与4*4矩阵键盘、复位电路、LED双位数码显示器、扬声器等组成主控核心模块。

文章详细论述了电子琴硬件设计和软件结构设计流程,采用了Altium Designer 09画出原理图、PCB图,通过Keil编程软件对电子琴进行软件编程,然后进行软硬件的调试运行并将程序烧录到STC89C52芯片中。

此系统运行比较稳定,具有硬件设计电路简单、清晰,成本低,软件功能完善,控制系统牢靠,性价比高等优点,具有一定的实用和参考价值。

关键词:STC89C52;电子琴;矩阵键盘AbstractAlong with the development of science and technology, the application of SCM increasingly mature. Single chip microcomputer high level of integration, processing powerful, low prices make it is widely used in various fields. At the same time the keyboards for science and technology and music common development of the product, in the electronic information era, for music's popular do can't replace contribution.This paper mainly introduces a kind of simple keyboard based on 51 SCM design scheme. It USES the STC product of our company a low power consumption, high performance microprocessor STC89C52 chips as the master unit, and 4 * 4 matrix keyboard and reset circuit, LED digital display, a double master core module and other components of the speaker. This paper discusses the design of hardware and software structure keyboard design process, the use of a Altium Designer 09 draw a diagram, PCB figure, through the Keil software keyboard to software programming, then the software and hardware debugging run and will burn to STC89C52 chip program. Operation of the system is stable and has the hardware circuit design simple, clear, and the cost is low, the software perfect function, control system firm, price higher advantages, has certain practical and reference value.Key words : stc89c52; keyboard; matrix keyboard目录摘要 (I)Abstract (II)1 绪论 (1)1.1 设计的目的和意义 (1)1.2 设计的主要内容 (1)2 系统概述 (2)2.1 系统工作原理 (2)2.2 系统结构组成 (2)2.2.1 电源电路 (2)2.2.2 控制部分 (3)2.2.3 显示部分 (3)2.2.4 发声部分 (3)2.3 主要芯片及元件的介绍 (3)2.3.1 STC89C52单片机简介 (3)2.3.2 芯片引脚介绍 (4)2.3.3 STC89C52时钟介绍 (6)2.3.4 双位LED数码显示器简介 (7)3 硬件电路的设计 (9)3.1 电源电路的设计 (9)3.2 复位电路的设计 (10)3.2.1 复位操作 (10)3.2.2 复位信号及其产生 (11)3.3 键盘控制电路 (12)3.3.1 矩阵式键盘的概述 (12)3.3.2 矩阵式键盘按键识别原理及方法 (12)3.4 显示电路 (13)4 系统软件设计 (14)4.1 如何利用单片机实现音乐节拍 (14)4.2 如何用单片机产生音频脉冲 (15)4.2.1 音符和频率的关系 (15)4.2.2 定义初值 (16)4.3 音乐发生程序流程图 (17)结论 (18)参考文献 (19)附录一电子琴源程序 (20)附录二原理图 (24)附录三 PCB图 (25)附录四实物图 (26)致谢 (27)1 绪论1.1 设计的目的和意义单片机又称单片微型计算机,英文字母的缩写MCU。

电子琴实验报告一,实验目的1. 学习使用AT89S52单片机的功能,进行单片机编程,实现键盘演奏音乐的功能,进一步加深对于单片机功能实现过程的理解,强化单片机编程的能力。

2. 设计实现各种功能,包括对音乐的录音以及回访放能,要求能实现各种不同音调,在编程过程中必须考虑到各种细节,例如按键的干扰问题以及滞键。

二,实验要求基本要求:1:能够通过键盘演奏音符。

2:能够保存演奏的音乐,并实现回放。

3:有音调调整功能(如:C调,G调)。

4: 自由发挥其他功能.5: 要求有单片机硬件系统框图,电路原理图,软件流程图。

三,实验基本原理在单片机的设计中,电子琴是一个典型的例子,电子琴的实现需要用到单片机AT89S52、蜂鸣器等模块。

而在本次的实验中,我们利用简单的模块,实现了一个简单的电子琴功能,使用单片机可以驱动蜂鸣器发出声音,还可以控制其发出不同的音调,在一首歌曲里面,不同的音阶对应着不同的频率,在蜂鸣器的发音原理里面,我们只需要给蜂鸣器输入不同的脉冲,蜂鸣器就会发出对应的声音,因此,我们只需要弄明白音阶对应的脉冲就可以了。

在键盘控制中,每个按键对应不同的音阶,按键按下的时候,单片机程序里面都会执行一次程序判断是否有前一次的按键被按下,按键按下以后会控制单片机对蜂鸣器输出不同频率的方波,每种情况对应不同的音阶或者音调。

一首歌曲就是有不同的音阶构成,从而就实现了电子琴的功能。

四,实验设计分析针对要实现的功能,采用AT89S52单片机进行设计,AT89S52单片机是一款低功耗,高性能CMOS8位单片机,片内含4KB在线可编程(ISP)的可反复擦写1000次的Flash只读程序存储器,器件采用高密度、非易失性存储技术制造,兼容标准MCS- 51指令系统及80C51引脚结构。

这样,既能做到经济合理又能实现预期的功能。

在设计程序的时候,分析道电子的功能有三个模块构成,分别是单片机本身,键盘按键输入和蜂鸣器的功能响应。

心于儿心正弦波振荡电路的电子琴设计与制作实训报告本次实训的主要内容是电子琴的原理与设计。

电子琴主要是通过对电路的设置来完成对音乐的控制。

主要有键盘功能、音效、电性能和电路功能四大类器件。

通过对电路的设置后,对键盘进行音效的设定和制作,来达到调节电子琴音效的目的。

通过电子琴这个项目的实训来了解到电子琴在制作时,需要通过键盘和电性能来调节音效和音乐表现力,而我的操作思路是通过对一些简单开关来实现音效和音乐表现力。

1.琴键功能键盘功能主要包括按击键功能和按音键功能。

按击键时,按键内部的振荡电荷会通过击键板产生一个正弦波的振荡频率和振荡电压,通过振荡电压作用到键盘的两个金属琴键上产生两个与琴键形状相同的正弦波频率和振荡电压。

在键盘面板上设有两个金属琴键和一个可调键盘(由数字键盘调整)。

在按键设置上要注意三个参数:按下琴键时键盘内部会有一个对应的数字键盘(可调键盘)发出三种不同的音频;按下音键时键盘内部会有一个对应的音乐按键(可调键盘)发出与乐器音效相同的音频;按下音键时键内会有一个对应的录音按钮(不可调键盘)发出相应的音频。

这三个参数的调整可以在一定程度上调节电子琴音效的效果和大小等。

2.音效调节用键盘可以对音效进行调节,音效调节也是最重要的一个因素。

我在第一节课就讲了音高的调节,音高调节主要是为了降低音量以及增加音质。

而调整音量主要是为了减少音高和音质。

通过开关按键设置音高、音质和音量,然后将电路的控制开关触点进行调整即可。

通过调节音程来调整音效。

同时调节电路的输出电阻以降低电阻值并减小输出电容的电感数量以提高输出电压。

3.电性能功能电性能就是通过电流调节来实现音乐的音效和演奏的音量控制的器件,在对电路进行设置时,需要考虑到电路的响应速度和反应时间,在对电路进行调整时,需要根据信号的速度和反馈的时间来进行调整。

例如如果频率为5 kHz电源输入的电压为100 V,信号所经过的时间为30 s即为5 kHz电路所产生的声音电流为50 mA;如果频率为5 kHz电源输入的电压为10 V或60 mA,信号所经过的时间为40 s即为60 mA电路所产生的声音电流为30 mA。

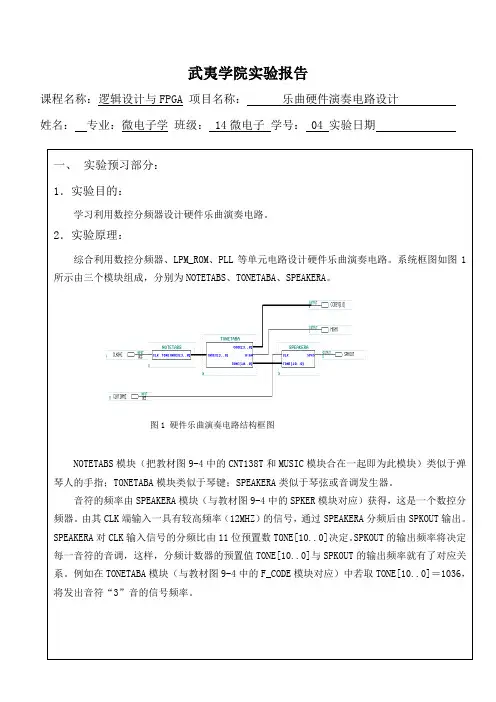

武夷学院实验报告课程名称:逻辑设计与FPGA 项目名称:乐曲硬件演奏电路设计 ______________姓名: 专业:微电子学 班级:14微电子 学号:04实验日期、 实验预习部分: 1. 实验目的:学习利用数控分频器设计硬件乐曲演奏电路。

2. 实验原理:综合利用数控分频器、LPM ROMPLL 等单元电路设计硬件乐曲演奏电路。

系统框图如图1所示由三个模块组成,分别为 NOTETABSTONETABASPEAKERANOTETAB 模块(把教材图9-4中的CNT138T 和MUSIC 模块合在一起即为此模块)类似于弹 琴人的手指;TONETAB 模块类似于琴键;SPEAKER 类似于琴弦或音调发生器。

音符的频率由SPEAKER 模块(与教材图9-4中的SPKEF 模块对应)获得,这是一个数控分 频器。

由其CLK 端输入一具有较高频率(12MHZ 的信号,通过SPEAKER 分频后由SPKOU 输出。

SPEAKER 对CLK 输入信号的分频比由11位预置数TONE[10..0]决定。

SPKOU 的输出频率将决定每一音符的音调,这样,分频计数器的预置值 TONE[10..0]与SPKOU的输出频率就有了对应关系。

例如在TONETAB 模块(与教材图9-4中的F_COD 模块对应)中若取 TONE[10..0] = 1036,图1硬件乐曲演奏电路结构框图i.;E-Z将发出音符“ 3”音的信号频率。

实验预习成绩(百分制)____________________ 实验指导教师签字:_________________________实验过程记录部分: 1实验过程记录:1.1输入信号锁相环PLLO 调节:图2.1锁相环管脚clk_50m (设置为B12)接入FPGA 内部的50mhz 的时钟信号,CO 口为得到数控分屏器 模块的输入时钟 750KHZ 将分频比设置为1/67,即50000000HZ/67=74.6K 约等于75K; cl 口为 2KHZ (配合下级的500分频模块),设置为:c 仁50000000HZ/25000=2KHZ1.2 500分频模块count500 (即500进制的计数器):如图2.2,因为梁祝歌曲只用低音和中音来演奏,为 1/4拍,即四分之一拍,每个音符持续 0.25秒的时间。

因为前级电路已经实现了从50MHZ 到2KHZ 的转换,要得到4HZ 的频率,则用500 进制的计数器(0到499的计数)产生的进位信号对 2KHZ 实现500分频(输出波形分析见后)。

dncIkDPLLOClkRatio =1- FDC (%)€0 1JS7 c cocl -飞0050.00inst7;50khz ::ck Sum [ rdf>clkD frequency: 50.D00 Ml HzUode: IMcrmal 图2.2分频电路程序设计1.3乐曲长度控制计数器cnt138设计:hd | 宦]rmjsic.bdP1library leeej2use icee:■兰cd_lc3giLQ_L:l£4 ・目1丄;3use leee ・st d_logxc^tms i.gneci ■日丄丄;4S entity cntlSS is5B port (elk: in std_logic;6cntS: 口口匸xntegez range 0 to 139}J7end cntl38;B E arehiteetuEe:bhv af ent 13 B is9^xgnal ql : xnceger range 0 co 138;10H begin11S process (elk) begin12 B if elk1event and 匚丄k=V then13Eif ql=138 tlien ql<=0;.14 E elaie qlC"ql+lj15end if;16end xf;17end process;IB cnt6<=<il;19 end bhvr图2.3乐曲长度控制计数器程序及元件图经查阅《EDA技术实用教程(第五版)》可知,《梁祝》这首歌曲总共有139个音符,其中包含末尾的3个休止符。

如图2.3,因此为了产生这139音符,因此想到开发一个139进制的计数器(计数值:0到138),实现用139状态代表139个音符。

又因为要配合下一级音符谱码存储模块的输入(ROM的输入一般为偶数位),因此将原本用7路线就可以表示完成的输出端cnt8增加一位线宽。

注:在本程序中,输出端cnt8由于定义成integer整型,在Quartus中被自动分配成了7根;也可以定义成vector 型,而此时需要注意配合下级电路的权位最好写成cnt8: outstd_logic_vector(7 dow nto 0).1.4音符谱码存储模块设计构建:1.4.1 ROM的设置:图2.4音符谱码存储模块ROM音符谱码存储模的主体构想,是为了让前级模块所产生的139个状态与实际音符(DoRe Mi Fa So La Si )构成映射。

因此需要构建一个包含《梁祝》乐谱的 mif 文件。

1.4.2构建《梁祝》乐谱.mif 文件:文件(町锚(E)式(O 〕fe(V) KI DEPTH256;WIDTHI ;ADDRES S RADI X =UNS; DATA_RADIX = UNS. CONTENTBEGIN003 ;013 ; 023 ; 033 : 045 ; 055 ; 065 ;076 . 088 ; 098 ; 108 ; 119 ; 126 . 138 ; 145 ; 155 ;1612 : 1712 ;图2.5《梁祝》乐谱(部分截取)因此综上所述,结合1.3的分析,音符谱码存储 ROM 即输入为8位数据线,含256bit 数 据(实际只用了 139bit );输出为4根线,这是由于《梁祝》这首歌曲只有低音的 123567,以及 中音的12356合高音部分的1,加上休止符一共13个状态,因此用4根数据线完全足够。

出于简化电路设计原则以及综合考虑电路测试的难易程度, 我将高音部分的1当做中音的7 来处理,将13个状态音符分为低音音符,中音音符和休止符;这样的好处是:在测试时候,只 需用一个LED 的亮灭并结合七段数码管来具体表示播放的音符,此时若灯亮且七段数码管显示 为“7”,实际代表输出为高音的“ DO'。

注:在以下的段落中,若出现“中音”,则用以表示“中音”的1235和“高音”的1.1.5分频预置查表电路 f code构建:图2.6 f code 模块代码及原理图由前级电路可知,从mscicsionROM 模块的输出端q 输出了 13个音符(13个状态),而扬声 器发出声音的实质是通过播放不同的声音频率实现的,而要实现将统一的频率分为不同的频率 则必须引入实现分频功能的模块,由《数字电子技术基础(第五版)》的“时序电路章节”知识可知:普通的实现分频功能的计数器实现分频的原理是当计数值达到计数器最大模值N 时,跳转到“预置数M',因此可以实现“ N-M+1'分频的功能;由此,我想到,如果将原本固定的“预 置数”端,用一个模块代替,进而产生可以随需求变化而变化的预置数,这样就可以实现对不 同音符频率的分频功能。

因此,本级模块最主要功能是将已有音符映射成对应的预置数。

因为下级模块“数控分频器”的最大计数值为 11位2进制数,因此本级模块的输出TOO 也 为11位线宽。

因为下级模块数控分频器的最大计数值为2047,预置数为 NT ,计数模值为2047-NT+1=2048-NT,女口 NT=912,那么计数模值(分频系数)为 2047-912=1135,因此将十进 制的912改为^一位二进制的01110010000,赋值给T0g (如图2.6),作为输出。

同时COD 歸输出对应的音符(1到7),送至下级电路“谱码指示模块”;同时为了区别输 出的音符为“低音”的(1到7)还是“中音”的(1到7),因此定义输出端口 H,并接到FPGA 的一个LED 若灯不亮则表示为“低音”,若点亮则表示“高音”,再配合谱码指示模块中的“七 段数码管”上显示的数值进而显示具体的音符。

lUsEary le-ee;USQ iee« B Btd_logic_lL64 ・ all ?H entity f =e^«le IsB pD^t- ( TNX : i?i i ;t.d_.l.ag'ic_v»ctigE i 3 dpvFitiQ 0) i CODE: Qut std_logie_veetor downto 0];Si : cut Jtd_Lagic 1;TOO; cutc^vectcix (10 damtci 0))end p@ aE-chitecxuzrs one af f_c&de is D be :g±n search Tprocass CTNX) bagin wh»n.11Q00O ,T => TOO <-rF 11X11111111"CODE<-,r OOODwh&n^OOOl 1- TOO31100000101" F CODE<=,,OOCI1 whBEL^OOlO^ «> TOO w^OLHODlOOOO"CCDE«GOLD when^Oll 11=> TOO ^"LOOOQGOllM"CODE<=' 0011 wheti n OlOl n ,TOO CODEC-' 01<31 «hsn n G110ra=> TOO <=rB LD100Q01G10r,CODE<=' 0110 whe-n^Olll*=■> TOO <-'"10101011100** «•CQDE'L-' 0111 whs n n1000 "" => TOQ ^-ra 101IQ000010"CQDE<^' 0001=>TOO <=ifc L01110Q1000ifc • CODE<=i 0010■A TOO ^-^LLOaQQOOllO"CDDE<-' 0011 when H 1100" TOO <=,kLlDD1010110" FCODE<=* Olfil wheEi^HOl"1TOO <-n.LLQiaai£j (j 100r» i CODE<«!0110=> TOO <=",l i LOilOOOGOO ,i r CODE<=' OOCilINX 卩・期CODEJ3..0]HTOOflO.O]€7呂BS ease Inx 丄日IE二;—773-;;Hc-'O r ;--llS7; i Hc=*O F f —l<Wi;H*- 10 *■ ;"1372; wheel ath.ej :s TOO <-"11111111111" ; CCDE«--,!,O-DDn"j: H<-' 0 r ;--2Q4" r and : Jend pzaeeaa; «nd;xe13:L2B1.6数控分频器模块spker 设计:如图2.7,该模块主要作用是将预置数通过计数器与对应音符的频率构成映射。