VHDL实验报告一2选1多路选择器

- 格式:doc

- 大小:70.00 KB

- 文档页数:6

实验一

实验目的:

熟悉quartus的vhdl文本设计流程全过程,学习简单的组合电路的设计,多层次的电路设计,仿真和硬件测试

二、实验内容

内容(一)用vhdl语言设计2选1多路选择器

参考例3-1程序设计如下:

library ieee;

use ieee.std_logic_1164.all;

entity mux21a is

port (a,b,s:in bit;

y: out bit);

end entity mux21a;

architecture one of mux21a is

begin

y<=a when s='0' else b;

end architecture one

全程编译后软件提示0错误,3警告,可以继续下面仿真操作。

程序分析:

这是一个2选1多路选择器,a和b分别为两个数字输入端的端口名,s为通道选择控制信号输入端的端口名,y为输出端的端口名。

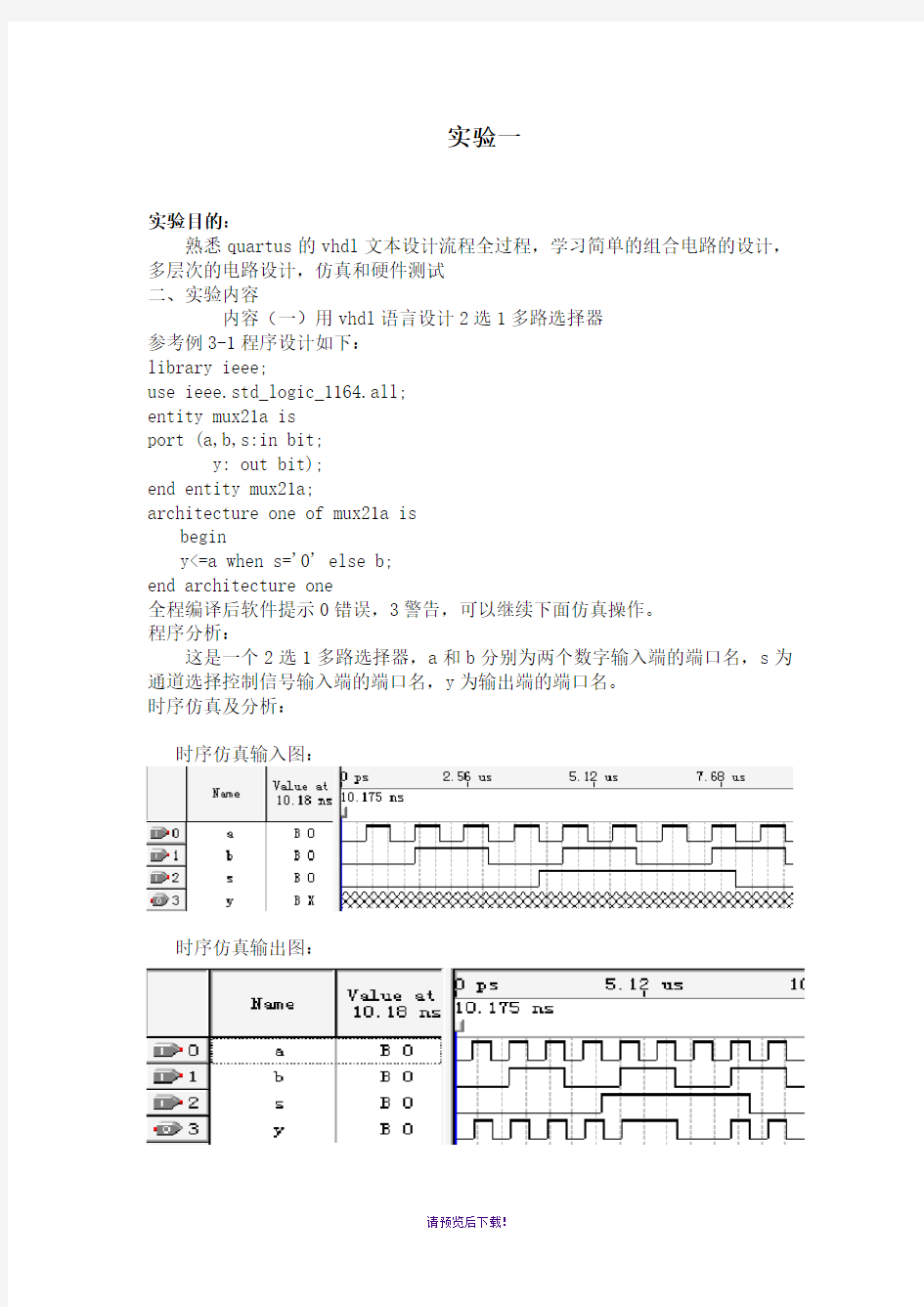

时序仿真及分析:

时序仿真输入图:

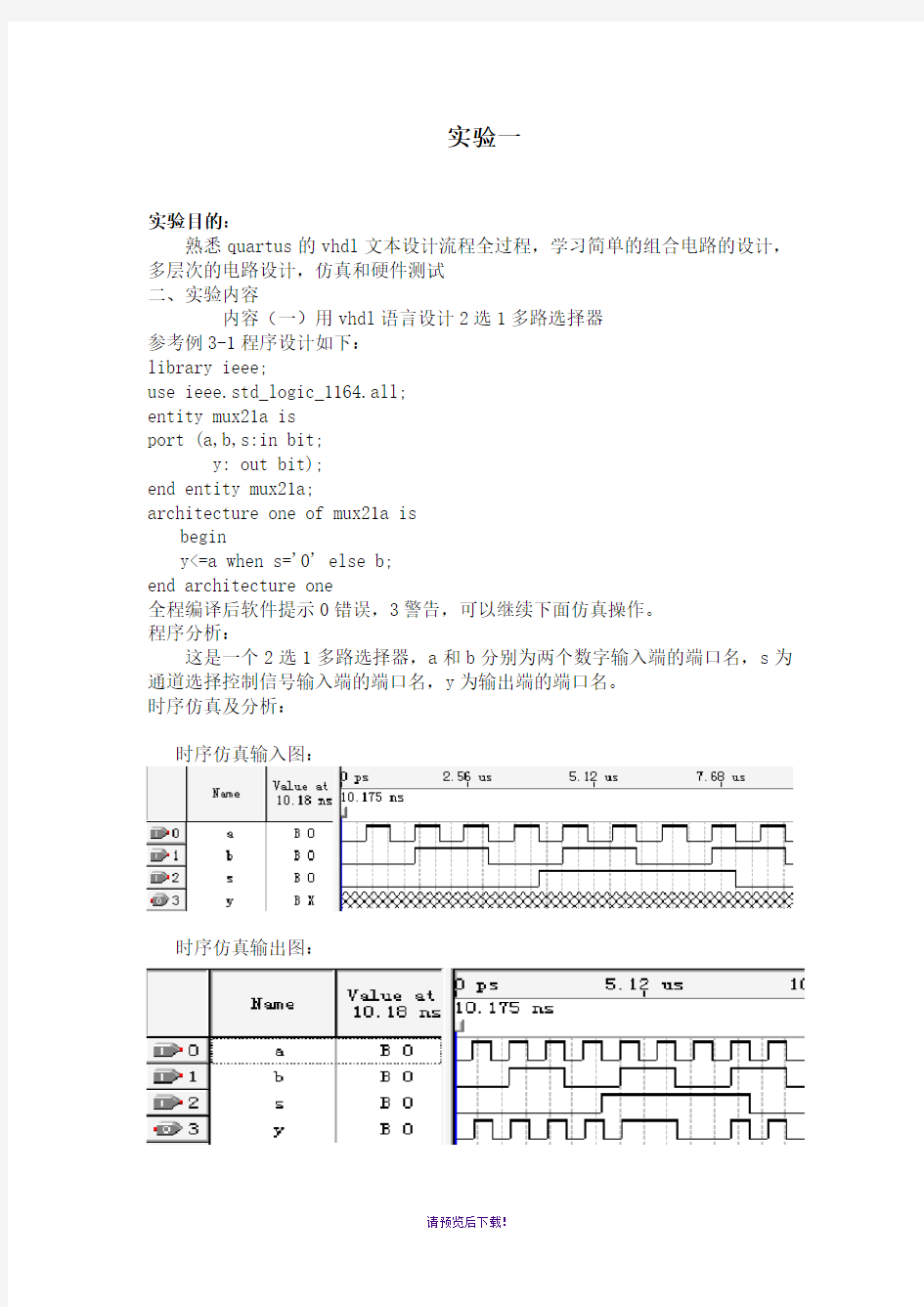

时序仿真输出图:

时序分析:

由上面两图可以得知:当s=0时,y口输出a,当s=1时,y口输出b

下载和硬件测试:

引脚锁定图:

程序下载完成后,选择实验电路模式5,通过短路帽选择clock0接256Hz 信号,clock2接8Hz信号。通过键一控制s,当键一进行切换时,明显能听到扬声器发出两种不同音调的声音。

实验内容(二)双二选一多路选择器设计

程序设计:

library ieee;

use ieee.std_logic_1164.all;

entity mux21a is

port (a,b,s:in bit;

y: out bit);

end entity mux21a;

architecture one of mux21a is

begin

y<=a when s='0' else b;

end architecture one;

entity muxk is

port (a1,a2,a3,s0,s1:in bit;

outy:out bit);

end entity muxk;

architecture bhv of muxk is

component mux21a

port (a,b,s:in bit;

y:out bit);

end component;

signal tmp: bit;

begin

u1:mux21a port map(a=>a2,b=>a3,s=>s0,y=>tmp);

u2:mux21a port map(a=>a1,b=>tmp,s=>s1,y=>outy);

end architecture bhv;

全程编译后软件提示0错误,2警告

程序分析:

这是一个双2选1多路选择器,a1、a2和a3分别为两个数字输入端的端口名,s0、s1为通道选择控制信号输入端的端口名,outy为输出端的端口名。实体mux21a是一个2选一选通电路,实体muxk是元件的例化,其作用是将两个mux21a组合成一个3选1多路选择器。

时序仿真及分析:

时序仿真输入图

时序仿真输出图

时序分析:

从仿真出来的结果,我们不难发现,s0和s1做为a1、a2、a3的选通控制信号。当s0=0.、s1=0时,outy输出a1;当s0=0.、s1=1时,outy输出a2;当s0=1.、s1=0时,outy输出a1;当s1=1.、s2=1时,outy输出a3;

下载和硬件测试:

引脚锁定图

程序下载完成后,选择实验电路模式5,通过短路帽选择clock0接256Hz 信号,clock2接8Hz信号,clock5接1024Hz。通过键一、键二分别控制s1、s2,当键一、键二进行切换时,明显能听到扬声器发出三种不同音调率的声音。

实验结果:

在实验一中内容一和内容二编译,仿真都没问题,除了有两三个警告以外,并无其他错误,但是在下载过程中,由于设置编程器处出现一点问题,导致下载

失败,经过请教,调整后成功运行

四、实验过程所出现的问题及其解决

首先,仿真结果出现延时,应该将a,b,s的周期增大些,且要保证单位为us,刚开始做实验内容(一)时,文件夹名字与程序中所用的实体名不一致,导致程序运行时无法找到文件夹,无法正常工作,经更改后,正常运行,同时文件夹名字不用汉字和数字,以免出错。每次修改过程都应该注意保存,才能将修改的结果反映到所输出的波形中,刚开始常常忘记,经过多次操作后才能够熟练运用。

HDL程序设计

—组合逻辑电路设计

班级:08级通信工程二班

学号:

姓名:

(注:可编辑下载,若有不当之处,请指正,谢谢!)