51单片机P0口上拉电阻的深入研究

- 格式:docx

- 大小:17.93 KB

- 文档页数:2

单片机上拉电阻、下拉电阻的详解和选取一、定义1、上拉就是将不确定的信号通过一个电阻嵌位在高电平!“电阻同时起限流作用”!下拉同理!2、上拉是对器件注入电流,下拉是输出电流3、弱强只是上拉电阻的阻值不同,没有什么严格区分4、对于非集电极(或漏极)开路输出型电路(如普通门电路)提升电流和电压的能力是有限的,上拉电阻的功能主要是为集电极开路输出型电路输出电流通道。

二、拉电阻作用1、一般作单键触发使用时,如果IC本身没有内接电阻,为了使单键维持在不被触发的状态或是触发后回到原状态,必须在IC外部另接一电阻。

2、数字电路有三种状态:高电平、低电平、和高阻状态,有些应用场合不希望出现高阻状态,可以通过上拉电阻或下拉电阻的方式使处于稳定状态,具体视设计要求而定!3、一般说的是I/O端口,有的可以设置,有的不可以设置,有的是内置,有的是需要外接,I/O端口的输出类似与一个三极管的C,当C接通过一个电阻和电源连接在一起的时候,该电阻成为上C拉电阻,也就是说,如果该端口正常时为高电平;C通过一个电阻和地连接在一起的时候,该电阻称为下拉电阻,使该端口平时为低电平,作用吗:比如:“当一个接有上拉电阻的端口设为输入状态时,他的常态就为高电平,用于检测低电平的输入”。

4、上拉电阻是用来解决总线驱动能力不足时提供电流的。

一般说法是拉电流,下拉电阻是用来吸收电流的,也就是我们通常所说的灌电流5、接电阻就是为了防止输入端悬空6、减弱外部电流对芯片产生的干扰7、保护cmos内的保护二极管,一般电流不大于10mA8、通过上拉或下拉来增加或减小驱动电流9、改变电平的电位,常用在TTL-CMOS匹配10、在引脚悬空时有确定的状态11、增加高电平输出时的驱动能力。

12、为OC门提供电流三、上拉电阻应用原则1、当TTL电路驱动COMS电路时,如果TTL电路输出的高电平低于COMS电路的最低高电平(一般为3。

51单片机P0口的结构及功能下图画出了P0口的某位P0.n 的结构图,它由一个输出锁存器、两个三态输入缓冲器和输出驱动器及控制电路组成;由于P0口既可以作为通用I/O口使用,又可以作为地址/数据总线使用,所以在P0口的电路中有一个多路转换开关MUX 。

在内部控制信号的作用下,多路开关MUX 可以分别接通锁存器输出和地址/数据总线。

数据/地址两个输入缓当P0口作为I/O口使用时,CPU 内部发控制电平0封锁与门,将输出上拉场效应管T1截止,同时使多路开关MUX 把锁存器的Q 非端与输出场效应管T2的栅极接通。

当P0口作为输出口使用时,显然内部总线与P0口同相位。

(内部总线为1时候,Q 非端为0,T2截止,则引脚电平为1, ;当内部总线为0时候,Q 非端为1,T2导通,则引脚电平为0 )写脉冲加在D 触发器的CL 上,内部总线就会向端口引脚输出数据。

由于输出驱动级是漏极开路电路,故需要加上拉电阻。

当P0口作为输入口使用时候,具有读引脚和读端口两种情况,因而端口中设有两个三态输入缓冲器用于读操作。

下面一个缓冲器用于读端口引脚处数据,当执行一条由端口输入的指令时候,读脉冲把该三态门打开,这样端口引脚处数据经过缓冲器进去内部总线。

这类操作由直接传送类指令实现。

在端口有输出口转变为输入口的时候,必须先向对应的锁存器写1,使FET 管子截止,这样做是为了防止T2导通后把该引脚嵌位到低电平。

P1-P3口在执行读操作时候也要先向相应的端口锁存器写1.读端口是通过上面的缓冲器读锁存器Q 端的状态。

这样设计的目的是为了适应对端口的“读-写-改”指令的需要。

这个操作是CPU 自动进行的,用户不必关心。

其他三个端口也有相应的硬件电路设计。

在扩展系统中,P0口作为低八位地址线,数据线使用,可分为两种情况。

一种是以P0口引脚输出地址/数据信息。

这时候CPU 内部发控制电平1,打开与门,同时使多路开关MUX 把CPU 内部地址数据线与T2栅极反相接通。

电阻之上拉电阻与下拉电阻详解(转)上拉(Pull Up )或下拉(Pull Down)电阻(两者统称为“拉电阻”)最基本的作⽤是:将状态不确定的信号线通过⼀个电阻将其箝位⾄⾼电平(上拉)或低电平(下拉),⽆论它的具体⽤法如何,这个基本的作⽤都是相同的,只是在不同应⽤场合中会对电阻的阻值要求有所不同,从⽽也引出了诸多新的概念,本节我们就来⼩谈⼀下这些内容。

如果拉电阻⽤于输⼊信号引脚,通常的作⽤是将信号线强制箝位⾄某个电平,以防⽌信号线因悬空⽽出现不确定的状态,继⽽导致系统出现不期望的状态,如下图所⽰:在实际应⽤中,10K欧姆的电阻是使⽤数量最多的拉电阻。

需要使⽤上拉电阻还是下拉电阻,主要取决于电路系统本⾝的需要,⽐如,对于⾼有效的使能控制信号(EN),我们希望电路系统在上电后应处于⽆效状态,则会使⽤下拉电阻。

假设这个使能信号是⽤来控制电机的,如果悬空的话,此信号线可能在上电后(或在运⾏中)受到其它噪声⼲扰⽽误触发为⾼电平,从⽽导致电机出现不期望的转动,这肯定不是我们想要的,此时可以增加⼀个下拉电阻。

⽽相应的,对于低有效的复位控制信号(RST#),我们希望上电复位后处于⽆效状态,则应使⽤上拉电阻。

⼤多数具备逻辑控制功能的芯⽚(如单⽚机、FPGA等)都会集成上拉或下拉电阻,⽤户可根据需要选择是否打开,STM32单⽚机GPIO模式即包含上拉或下拉,如下图所⽰(来⾃ST数据⼿册):根据拉电阻的阻值⼤⼩,我们还可以分为强拉或弱拉(weak pull-up/down),芯⽚内部集成的拉电阻通常都是弱拉(电阻⽐较⼤),拉电阻越⼩则表⽰电平能⼒越强(强拉),可以抵抗外部噪声的能⼒也越强(也就是说,不期望出现的⼲扰噪声如果要更改强拉的信号电平,则需要的能量也必须相应加强),但是拉电阻越⼩则相应的功耗也越⼤,因为正常信号要改变信号线的状态也需要更多的能量,在能量消耗这⼀⽅⾯,拉电阻是绝不会有所偏颇的,如下图所⽰:对于上拉电阻R1⽽⾔,控制信号每次拉低L都会产⽣VCC/R1的电流消耗(没有上拉电阻则电流为0),相应的,对于下拉电阻R2⽽⾔,控制信号每次拉⾼H也会产⽣VCC/R2R 电流消耗(本⽂假设⾼电平即为VCC)。

单片机上拉电阻下拉电阻的详解和选取一、定义1、上拉就是将不确定的信号通过一个电阻嵌位在高电平!“电阻同时起限流作用”!下拉同理!2、上拉是对器件注入电流,下拉是输出电流3、弱强只是上拉电阻的阻值不同,没有什么严格区分4、对于非集电极(或漏极)开路输出型电路(如普通门电路)提升电流和电压的能力是有限的,上拉电阻的功能主要是为集电极开路输出型电路输出电流通道。

二、拉电阻作用1、一般作单键触发使用时,如果IC本身没有内接电阻,为了使单键维持在不被触发的状态或是触发后回到原状态,必须在IC外部另接一电阻。

2、数字电路有三种状态:高电平、低电平、和高阻状态,有些应用场合不希望出现高阻状态,可以通过上拉电阻或下拉电阻的方式使处于稳定状态,具体视设计要求而定!3、一般说的是I/O端口,有的可以设置,有的不可以设置,有的是内置,有的是需要外接,I/O端口的输出类似与一个三极管的C,当C接通过一个电阻和电源连接在一起的时候,该电阻成为上C拉电阻,也就是说,如果该端口正常时为高电平;C通过一个电阻和地连接在一起的时候,该电阻称为下拉电阻,使该端口平时为低电平,作用吗:比如:“当一个接有上拉电阻的端口设为输入状态时,他的常态就为高电平,用于检测低电平的输入”。

4、上拉电阻是用来解决总线驱动能力不足时提供电流的。

一般说法是拉电流,下拉电阻是用来吸收电流的,也就是我们通常所说的灌电流5、接电阻就是为了防止输入端悬空6、减弱外部电流对芯片产生的干扰7、保护cmos内的保护二极管,一般电流不大于10mA8、通过上拉或下拉来增加或减小驱动电流9、改变电平的电位,常用在TTL-CMOS匹配10、在引脚悬空时有确定的状态11、增加高电平输出时的驱动能力。

12、为OC门提供电流三、上拉电阻应用原则1、当TTL电路驱动COMS电路时,如果TTL电路输出的高电平低于COMS电路的最低高电平(一般为3。

5V),这时就需要在TTL的输出端接上拉电阻,以提高输出高电平的值。

单片机IO口结构及上拉电阻MCS-51有4组8位I/O口:P0、P1、P2和P3口,P1、P2和P3为准双向口,P0口则为双向三态输入输出口,下面我们分别介绍这几个口线。

一、P0口和P2口图1和图2为P0口和P2口其中一位的电路图。

由图可见,电路中包含一个数据输出锁存器(D触发器)和两个三态数据输入缓冲器,另外还有一个数据输出的驱动(T1和T2)和控制电路。

这两组口线用来作为CPU与外部数据存储器、外部程序存储器和I/O扩展口,而不能象P1、P3直接用作输出口。

它们一起可以作为外部地址总线,P0口身兼两职,既可作为地址总线,也可作为数据总线。

图1 单片机P0口内部一位结构图图2 单片机P0口内部一位结构图P2口作为外部数据存储器或程序存储器的地址总线的高8位输出口AB8-AB15,P0口由ALE选通作为地址总线的低8位输出口AB0-AB7。

外部的程序存储器由PSEN信号选通,数据存储器则由WR和RD读写信号选通,因为2^16=64k,所以MCS-51最大可外接64kB的程序存储器和数据存储器。

二、P1口图3为P1口其中一位的电路图,P1口为8位准双向口,每一位均可单独定义为输入或输出口,当作为输入口时,1写入锁存器,Q(非)=0,T2截止,内上拉电阻将电位拉至"1",此时该口输出为1,当0写入锁存器,Q(非)=1,T2导通,输出则为0。

图3 单片机P2口内部一位结构图作为输入口时,锁存器置1,Q(非)=0,T2截止,此时该位既可以把外部电路拉成低电平,也可由内部上拉电阻拉成高电平,正因为这个原因,所以P1口常称为准双向口。

需要说明的是,作为输入口使用时,有两种情况:1.首先是读锁存器的内容,进行处理后再写到锁存器中,这种操作即读—修改—写操作,象JBC(逻辑判断)、CPL(取反)、INC(递增)、DEC(递减)、ANL(与逻辑)和ORL(逻辑或)指令均属于这类操作。

2.读P1口线状态时,打开三态门G2,将外部状态读入CPU。

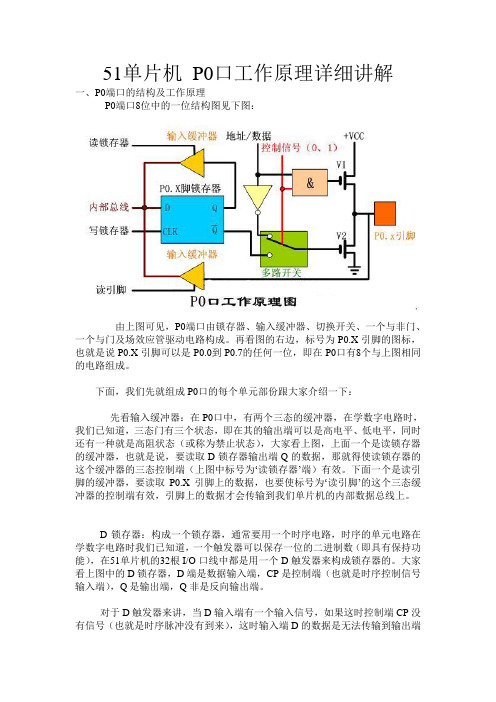

51单片机P0口工作原理详细讲解一、P0端口的结构及工作原理P0端口8位中的一位结构图见下图:由上图可见,P0端口由锁存器、输入缓冲器、切换开关、一个与非门、一个与门及场效应管驱动电路构成。

再看图的右边,标号为P0.X引脚的图标,也就是说P0.X引脚可以是P0.0到P0.7的任何一位,即在P0口有8个与上图相同的电路组成。

下面,我们先就组成P0口的每个单元部份跟大家介绍一下:先看输入缓冲器:在P0口中,有两个三态的缓冲器,在学数字电路时,我们已知道,三态门有三个状态,即在其的输出端可以是高电平、低电平,同时还有一种就是高阻状态(或称为禁止状态),大家看上图,上面一个是读锁存器的缓冲器,也就是说,要读取D锁存器输出端Q的数据,那就得使读锁存器的这个缓冲器的三态控制端(上图中标号为…读锁存器‟端)有效。

下面一个是读引脚的缓冲器,要读取P0.X引脚上的数据,也要使标号为…读引脚‟的这个三态缓冲器的控制端有效,引脚上的数据才会传输到我们单片机的内部数据总线上。

D锁存器:构成一个锁存器,通常要用一个时序电路,时序的单元电路在学数字电路时我们已知道,一个触发器可以保存一位的二进制数(即具有保持功能),在51单片机的32根I/O口线中都是用一个D触发器来构成锁存器的。

大家看上图中的D锁存器,D端是数据输入端,CP是控制端(也就是时序控制信号输入端),Q是输出端,Q非是反向输出端。

对于D触发器来讲,当D输入端有一个输入信号,如果这时控制端CP没有信号(也就是时序脉冲没有到来),这时输入端D的数据是无法传输到输出端Q及反向输出端Q非的。

如果时序控制端CP的时序脉冲一旦到了,这时D端输入的数据就会传输到Q及Q非端。

数据传送过来后,当CP时序控制端的时序信号消失了,这时,输出端还会保持着上次输入端D的数据(即把上次的数据锁存起来了)。

如果下一个时序控制脉冲信号来了,这时D端的数据才再次传送到Q端,从而改变Q端的状态。

单⽚机上拉电阻应该选多⼤?

⾸先解释⼀下上拉电阻:上拉电阻的作⽤就是将不确定的信号通过⼀个电阻钳位在⾼电平,电阻同时起限流作⽤。

那么对于普通的51单⽚机芯⽚来说,有P0~P3四类共32个输出串⼝,⽽P1~P3内部⾃带上拉电阻,除⾮它的驱动能⼒不⾜以驱动后续电路,才会考虑加上拉。

由于P0⼝内部没有上拉电阻,是开漏的。

所以P0⼝作为I/O⼝输出时,输出低电平为0,输出⾼电平为⾼阻态(并⾮5V,相当于悬空状态)。

也就是说P0 ⼝不能真正的输出⾼电平,给所接的负载提供电流,因此在要求输出为⾼电平时必须接上拉电阻,不过⼀般传输地址和数据时不接也没事。

怎么选择上拉电阻的阻值?

上拉就是要把VCC的电压拉给串⼝使⽤,这样串⼝输出⾼电平是,值才会⼤。

⽽上拉电阻也起到⼀个限流的作⽤。

具体的值选多⼤,要看串⼝驱动的是什么电路了。

不过⼀般常⽤10K、4.7K、5.1K这些阻值的电阻。

1、假如驱动的是LED,上拉电阻范围建议选择在200~3K,具体选择要看你需要LED多亮了。

2、驱动三极管,对于NPN,毫⽆疑问NPN管是⾼电平有效的,因此上拉电阻的阻值⽤2K~20K 之间的,具体的⼤⼩还要看晶体管的集电极接的是什么负载。

对于PNP管,毫⽽低电平有效的,因此上拉电阻的阻值⽤100K以上的就⾏了,在开关管电压保持⾼电平,三极管截⽌不产⽣误动作。

3、对于驱动TTL集成电路,上拉电阻的阻值要⽤1~10K之间的。

零是起源写于20180729。

51单片机AD采集电压和上拉电阻关系问题分析:由于键盘的结构,无非就是两个金属片的接通或断开。

但是接入ULN2003后无法正常工作,说明是接入ULN2003影响到了P1口电平的变化。

用万用表测的电压,当单片机输出高电平时,P1、0~P1、3电压1V左右,P1、4~P1、7电压4、3V左右,于是测AT89s52高低电平的判决电位,在1、3V左右。

这样P1、0~P1、3始终是低电平,键盘根本无法实现扫描功能。

解决方法,只要抬高P1口高电平时的电位,就可以正常工作,1、在P1口到ULN2003上串接电阻,起到分压的作用,就可以抬高电平。

2、给P1口接上拉电阻,跟P1口内部电阻并联,减小上拉电阻阻值,减小分得的电压,从而抬高P0口高电平电位。

采用第二种方案可以抬高电平到2、5V左右。

键盘工作正常。

另外:我在做液晶显示实验的时候,数据线用的P0口,无法正常工作,不显示字符。

但是乱动一下数据线就可以完成显示,但是显示现象并不正常,字符不是一次写入,而是乱动几次才能写完全部内容,正常应该一次全部显示。

原因是由于,我的P0口中有六个端口都外接并联三个发光二极管。

,因为从资料上查到,P0口每一个端口最大可以吸收10MA电流,总电流不能超过26MA电流。

这样算我的总电流已经到了40MA,呵呵。

见笑了。

所以怀疑是驱动的问题。

于是去掉了几个二极管。

显示一切正常。

似乎问题已经解决,但总觉得还是有点问题,于是又经过几次试验,发现只有当P0、7端口的并联二极管去掉一个,再在其他端口接上一个发光二极管。

此时也可以正常显示。

但是这样P0口吸收电流在38MA,也超过了26MA不少。

所以不是吸收电流太大的问题。

仔细分析当端口并联外接三个二极管的时候等效于加了一个700欧左右的电阻,于是把二极管去掉换成一个1k电阻,液晶也无法显示。

经过仔细分析,我认为,由于P0、7是液晶忙信号的返回线路当这个端口返回高电平时说明,液晶正在处理数据,无法接收新的数据,返回0时说明空闲,可以接收新数据。

单⽚机IO⼝结构及上拉电阻单⽚机IO⼝结构及上拉电阻MCS-51有4组8位I/O⼝:P0、P1、P2和P3⼝,P1、P2和P3为准双向⼝,P0⼝则为双向三态输⼊输出⼝,下⾯我们分别介绍这⼏个⼝线。

⼀、P0⼝和P2⼝图1和图2为P0⼝和P2⼝其中⼀位的电路图。

由图可见,电路中包含⼀个数据输出锁存器(D触发器)和两个三态数据输⼊缓冲器,另外还有⼀个数据输出的驱动(T1和T2)和控制电路。

这两组⼝线⽤来作为CPU与外部数据存储器、外部程序存储器和I/O扩展⼝,⽽不能象P1、P3直接⽤作输出⼝。

它们⼀起可以作为外部地址总线,P0⼝⾝兼两职,既可作为地址总线,也可作为数据总线。

图1 单⽚机P0⼝内部⼀位结构图图2 单⽚机P0⼝内部⼀位结构图P2⼝作为外部数据存储器或程序存储器的地址总线的⾼8位输出⼝AB8-AB15,P0⼝由ALE选通作为地址总线的低8位输出⼝AB0-AB7。

外部的程序存储器由PSEN信号选通,数据存储器则由WR和RD读写信号选通,因为2^16=64k,所以MCS-51最⼤可外接64kB的程序存储器和数据存储器。

⼆、P1⼝图3为P1⼝其中⼀位的电路图,P1⼝为8位准双向⼝,每⼀位均可单独定义为输⼊或输出⼝,当作为输⼊⼝时,1写⼊锁存器,Q(⾮)=0,T2截⽌,内上拉电阻将电位拉⾄"1",此时该⼝输出为1,当0写⼊锁存器,Q(⾮)=1,T2导通,输出则为0。

图3 单⽚机P2⼝内部⼀位结构图作为输⼊⼝时,锁存器置1,Q(⾮)=0,T2截⽌,此时该位既可以把外部电路拉成低电平,也可由内部上拉电阻拉成⾼电平,正因为这个原因,所以P1⼝常称为准双向⼝。

需要说明的是,作为输⼊⼝使⽤时,有两种情况:1.⾸先是读锁存器的内容,进⾏处理后再写到锁存器中,这种操作即读—修改—写操作,象JBC(逻辑判断)、CPL(取反)、INC(递增)、DEC(递减)、ANL(与逻辑)和ORL(逻辑或)指令均属于这类操作。

要是你!怎么解决引脚单片机的上拉电阻问题?

单片机的引脚,可以用程序来控制,输出高、低电平,这些可算是单片机的输出电压。

但是,程序控制不了单片机的输出电流。

单片机的输出电流,很大程度上是取决于引脚上的外接器件。

单片机输出低电平时,将允许外部器件,向单片机引脚内灌入电流,这个电流,称为“灌电流”,外部电路称为“灌电流负载”;单片机输出高电平时,则允许外部器件,从单片机的引脚,拉出电流,这个电流,称为“拉电流”,外部电路称为“拉电流负载”。

这些电流一般是多少?最大限度是多少?这就是常见的单片机输出驱动能力的问题。

早期的51 系列单片机的带负载能力,是很小的,仅仅用“能带动多少个TTL 输入端”来说明的。

P1、P2 和P3口,每个引脚可以都带动 3 个TTL 输入端,只有P0 口的能力强,它可以带动8 个!

分析一下TTL 的输入特性,就可以发现,51 单片机基本上就没有什幺驱动能力。

它的引脚,甚至不能带动当时的LED 进行正常发光。

记得是在AT89C51 单片机流行起来之后,做而论道才发现:单片机引脚的能力大为增强,可以直接带动LED 发光了。

从AT89C51 单片机的PDF 手册文件中可以看到,稳态输出时,“灌电流”的上限为:

Maximum IOL per port pin: 10 mA;

Maximum IOL per 8-bit port

ort 0: 26 mA,Ports 1, 2, 3: 15 mA;

Maximum total I for all output pins: 71 mA.。

51单片机P0口上拉电阻的深入研究

如果是驱动led,那么用1K左右的就行了。

如果希

望亮度大一些,电阻可减小,最小不要小于200欧姆,

否则电流太大;如果希望亮度小一些,电阻可增大,增

加到多少呢,主要看亮度情况,以亮度合适为准,一般

来说超过3K以上时,亮度就很弱了,但是对于超高亮度的LED,有时候电阻为10K时觉得亮度还能够用。

通常就用1k的。

对于驱动光耦合器,如果是高电位有效,即耦合器输入端接端口和地之间,那么和LED的情况是一样的;如

果是低电位有效,即耦合器输入端接端口和VCC之间,

那么除了要串接一个1——4.7k之间的电阻

以外,同时上拉电阻的阻值就可以用的特别大,用

100k——500K之间的都行,当然用10K的也

可以,但是考虑到省电问题,没有必要用那么小的。

对于驱动晶体管,又分为PNP和NPN管两种情况:对于NPN,毫无疑问NPN管是高电平有效的,因此上拉电阻的阻值用2K——20K之间的,具体的大小还

要看晶体管的集电极接的是什么负载,对于LED类负载,由于发管电流很小,因此上拉电阻的阻值可以用20k的,但是对于管子的集电极为继电器负载时,由于集电极电

流大,因此上拉电阻的阻值最好不要大于4.7K,有时候

甚至用2K的。

对于PNP管,毫无疑问PNP管是低电平有效的,因此上拉电阻的阻值用100K以上的就行了,且管子的基极必须串接一个1——10K的电阻,阻值的大小要看管子集电极的负载是什么,对于LED类负载,由于发光电流很小,因此基极串接的电阻的阻值可

以用20k的,但是对于管子的集电极为继电器负载时,

由于集电极电流大,因此基极电阻的阻值最好不要大于4.7K。

对于驱动TTL集成电路,上拉电阻的阻值要用

1——10K之间的,有时候电阻太大的话是拉

不起来的,因此用的阻值较小。

但是对于CMOS集成电路,上拉电阻的阻值就可以用的很大,一般不小于20K,我

通常用100K的,实际上对于CMOS电路,上拉电阻的阻值用1M的也是可以的,但是要注意上拉电阻的阻值太大的时候,容易产生干扰,尤其是线路板的线条很长的时候,这种干扰更严重,这种情况下上拉电阻不宜过大,一般

要小于100K,有时候甚至小于10K。

根据以上分析,上拉电阻的阻值的选取是有很多讲究的,不能乱用。