MOSFET模型参数的提取

- 格式:doc

- 大小:997.50 KB

- 文档页数:13

硅基射频器件的建模与参数提取建模是指将硅基射频器件的物理过程和特性以数学模型的形式表达出来,以实现对器件性能的预测和分析。

硅基射频器件的建模有多种方法,常用的包括电路建模、物理建模和系统建模等。

一般来说,建模的过程包括以下几个步骤:1.设计器件几何结构:根据硅基射频器件的实际结构和尺寸,利用CAD软件进行建模和设计。

2.建立电路模型:根据硅基射频器件的特性和工作原理,选择合适的电路模型进行建模。

常用的电路模型包括小信号模型、大信号模型和非线性模型等。

3.参数提取:通过实验测量或仿真分析,提取硅基射频器件的各种参数。

这些参数包括S参数(散射参数)、Y参数、Z参数、H参数、过程参数等。

4.模型验证:将提取得到的参数输入到建立的电路模型中进行仿真,与实际测试结果进行比较,验证模型的准确性和合理性。

参数提取是建模过程中的一项关键工作,它是在实际测试或仿真过程中,通过测量或分析得到硅基射频器件的各种特性参数。

参数提取的过程中需要注意以下几点:1.测试设备的选择:选择合适的测试设备,如网络分析仪、功率计、频谱分析仪等。

要保证测试设备具备足够的精度和灵敏度。

2.测试方法的选择:根据硅基射频器件的特性和要求,选择合适的测试方法。

常用的测试方法包括小信号测试、大信号测试、直流参数测试、频率响应测试等。

3.数据处理和分析:将测试得到的原始数据进行处理和分析,提取出硅基射频器件的各种特性参数。

常见的数据处理方法包括线性回归、参数拟合、频谱分析等。

4.参数的准确性和可靠性:要对提取得到的参数进行验证和评估,确保其准确性和可靠性。

可以通过与其他测试结果的比较、重复测试和统计分析等方法进行验证。

总之,硅基射频器件的建模和参数提取是实现对器件性能优化和改进的关键步骤。

通过合理选择建模方法、测试设备和测试方法,以及准确提取和验证器件参数,可以为硅基射频器件的设计和应用提供有力支持。

LDMOS模型设计及参数提取文燕【摘要】In recent years, due to its drain, gate and source are on the chip surface, LDMOS is easy for lowvoltage device integration. So they have been widely used to power integrated circuits and radio frequency fields. All along, the high-voltage LDMOS modeling is a very complex issue. By analyzing the high-voltage LDMOS structure and physical properties, we obtain the quasi-saturation voltage, self-heating effect and the voltage-controlled resistance in drift region about LDMOS. These characteristics is similar to those of the JFET, thus we establish MOS+JFET circuit model about high-voltage LDMOS devices. By designing a 1.0~tm 40V LDMOS model mask of CMOS process, we extract parameters. Experimental results show that the analytical solution of the model parameters consist with the measured values, but also reflects the inherent characteristics of LDMOS devices. Therefore, this new model can be a good guide of LDMOS device engineering applications.%近年来,LDMOS由于其漏极、栅极和源极都在芯片表面,易于和低压器件集成,因而被广泛应用到功率集成电路和射频领域,一直以来,高压LDMOS的建模是一个十分复杂的问题。

finfet单元结构的寄生参数提取FinFET(Fin Field-Effect Transistor)是一种三维晶体管结构,其带来了新的寄生参数,需要进行提取和建模。

寄生参数是指在电路元件中存在且具有一定影响的电阻、电容和电感等参数。

对于FinFET单元结构,其中的寄生参数包括通道电阻、接触电阻、源/漏接触电阻、栅氧电容、外延电阻等,下面将对这些寄生参数进行详细的提取方法进行介绍。

首先,通道电阻是FinFET单元结构中的一个重要寄生参数。

它影响了传输特性和输出特性的性能。

常用的提取方法是基于建模和测量的结合。

在建模方面,可以使用二维有限元方法或二维瞬态电流导数方法进行计算模拟。

而在测量方面,可以通过量测终端I-V曲线和直流注入方法进行实验测量。

通过这些方法可以获得通道电阻的数值和变化规律。

其次,接触电阻是FinFET单元结构中的另一个重要寄生参数。

它影响了信号传输的稳定性和速度。

接触电阻的提取方法可以分为电学方法和物理方法两种。

电学方法主要通过测量接触电阻的电流-电压关系,如线性插值法或基于界面Hamiltonian的方法。

而物理方法主要通过X射线能谱学和原子力显微镜技术等手段进行非接触测量。

这些方法可以获得接触电阻的数值和分布情况。

此外,源/漏接触电阻也是需要提取的寄生参数之一。

它对FinFET 单元结构的低电压操作和快速开关速度具有重要影响。

提取方法主要是通过测量晶体管结构的源/漏接触电压和电流关系,获取接触电阻的数值和特性。

栅氧电容是FinFET单元结构中的一个重要寄生参数。

它在FinFET 单元结构的小尺寸和高频操作中起到关键作用。

常用的提取方法包括基于测量和建模的方法。

测量方法主要通过C-V(电容-电压)曲线测量、电流充放技术和频率响应技术进行实验测量。

而建模方法可以通过有限元分析和开路时域反射法进行计算模拟。

这些方法可以获得栅氧电容的数值和变化规律。

最后,外延电阻是寄生参数中的一个重要因素。

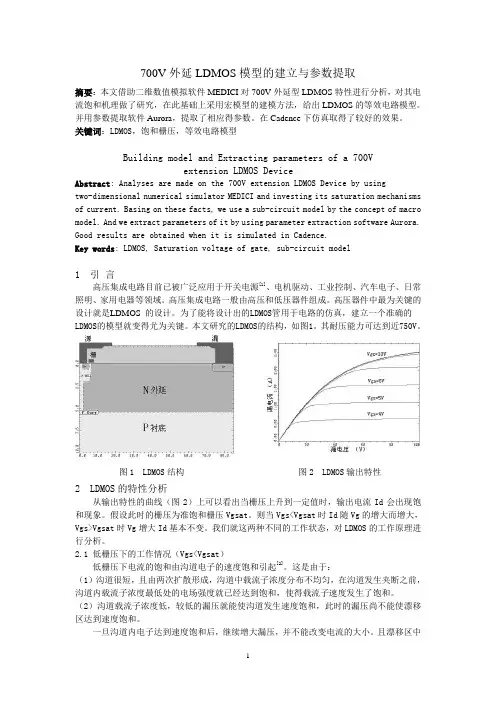

700V外延LDMOS模型的建立与参数提取摘要:本文借助二维数值模拟软件MEDICI对700V外延型LDMOS特性进行分析,对其电流饱和机理做了研究,在此基础上采用宏模型的建模方法,给出LDMOS的等效电路模型。

并用参数提取软件Aurora,提取了相应得参数。

在Cadence下仿真取得了较好的效果。

关键词:LDMOS,饱和栅压,等效电路模型Building model and Extracting parameters of a 700Vextension LDMOS DeviceAbstract: Analyses are made on the 700V extension LDMOS Device by usingtwo-dimensional numerical simulator MEDICI and investing its saturation mechanisms of current. Basing on these facts, we use a sub-circuit model by the concept of macro model. And we extract parameters of it by using parameter extraction software Aurora. Good results are obtained when it is simulated in Cadence.Key words: LDMOS, Saturation voltage of gate, sub-circuit model1 引言高压集成电路目前已被广泛应用于开关电源[1]、电机驱动、工业控制、汽车电子、日常照明、家用电器等领域。

高压集成电路一般由高压和低压器件组成。

高压器件中最为关键的设计就是LDMOS 的设计。

为了能将设计出的LDMOS管用于电路的仿真,建立一个准确的LDMOS的模型就变得尤为关键。

元器件模型参数的优化提取微电子学院贾新章(2013. 11 )PSpice中的模型和模型参数库一、概述:为元器件建立模型参数的步骤二、采用Model Editor分组提取模型参数三、基于器件物理原理计算部分模型参数四、建立适用于高级分析的元器件模型参数描述五、元器件模型参数的综合优化提取。

六、为元器件模型描述建立元器件符号七、将新建模型设置为PSpice仿真可以调用的库文件一、概述:为元器件建立模型参数的步骤第一步:优化提取模型参数1、采用Model Editor分组提取模型参数;2、基于器件物理原理,计算部分模型参数;3、为元器件建立适用于高级分析的模型参数描述;4、采用PSpice/Optimizer进行一次综合优化提取。

(采用前面结果作为优化提取模型参数的最佳初值)第二步:建立供Capture绘制电路图调用的元器件符号第三步:将新建模型设置为PSpice仿真可以调用的库文件。

下面将分别介绍每一部分的操作方法。

PSpice中的模型和模型参数库一、概述:为元器件建立模型参数的步骤二、采用Model Editor分组提取模型参数三、基于器件物理原理计算部分模型参数四、建立适用于高级分析的元器件模型参数描述五、元器件模型参数的综合优化提取。

六、为元器件模型描述建立元器件符号七、将新建模型设置为PSpice仿真可以调用的库文件二、采用Model Editor分组提取模型参数Model Editor模块可以对其支持的几种元器件,依据元器件的各种端特性数据,分组优化提取相应当模型参数数据。

(1) 调用MODEL EDITOR模块;(2) 选择执行Model/New命令,从对话框中设置模型类型。

下面以提取双极型晶体管模型参数为例(3)完成设置之后,点击OK,窗口就会更新为参数提取界面,不同的模型类型所对应的界面不相同,但界面的结构形式是一样的,分为三个子窗口。

特性数据输入窗口模型列表窗口参数列表窗口(4) 分组提取各组模型参数:将测试得到的器件外部端特性数据分别输入相应的特性窗口,分组进行参数提取。

MOS FET 参数介绍VDSS 最大漏-源电压在栅源短接,漏-源额定电压(VDSS)是指漏-源未发生雪崩击穿前所能施加的最大电压。

根据温度的不同,实际雪崩击穿电压可能低于额定VDSS。

关于V(BR)DSS 的详细描述请参见静电学特性.VGS 最大栅源电压VGS额定电压是栅源两极间可以施加的最大电压。

设定该额定电压的主要目的是防止电压过高导致的栅氧化层损伤。

实际栅氧化层可承受的电压远高于额定电压,但是会随制造工艺的不同而改变,因此保持VGS在额定电压以内可以保证应用的可靠性。

ID - 连续漏电流ID定义为芯片在最大额定结温TJ(max)下,管表面温度在25℃或者更高温度下,可允许的最大连续直流电流。

该参数为结与管壳之间额定热阻RθJC和管壳温度的函数:ID中并不包含开关损耗,并且实际使用时保持管表面温度在25℃(Tcase)也很难。

因此,硬开关应用中实际开关电流通常小于ID 额定值@ TC = 25℃的一半,通常在1/3~1/4。

补充,如果采用热阻JA的话可以估算出特定温度下的ID,这个值更有现实意义。

IDM -脉冲漏极电流该参数反映了器件可以处理的脉冲电流的高低,脉冲电流要远高于连续的直流电流。

定义IDM的目的在于:线的欧姆区。

对于一定的栅-源电压,MOSFET导通后,存在最大的漏极电流。

如图所示,对于给定的一个栅-源电压,如果工作点位于线性区域内,漏极电流的增大会提高漏-源电压,由此增大导通损耗。

长时间工作在大功率之下,将导致器件失效。

因此,在典型栅极驱动电压下,需要将额定IDM设定在区域之下。

区域的分界点在Vgs和曲线相交点。

因此需要设定电流密度上限,防止芯片温度过高而烧毁。

这本质上是为了防止过高电流流经封装引线,因为在某些情况下,整个芯片上最“薄弱的连接”不是芯片,而是封装引线。

考虑到热效应对于IDM的限制,温度的升高依赖于脉冲宽度,脉冲间的时间间隔,散热状况,RDS(on)以与脉冲电流的波形和幅度。

MOSFET主要参数指标:Vds:DS击穿电压。

当Vsg=0V时,MOS的DS所能承受的做大电压,一般此电压有一定的余量。

Rds(on):DS的导致电阻。

当Vgs=100V时,MOS的DS之间的电阻。

Id:最大DS电流。

会随温度的升高而降低。

绝对最大额定参数:Vds:见Features(产品特点)Vgs:最大GS电压,一般为:-20V~+20V(要注意可能是负的,针对不同形式的MOSFET)Id:见Features.Idm:最大脉冲DS电流,会随温度的升高而降低,体现一个抗冲击能力,跟脉冲时间也有关系。

Pd:最大耗散功率。

Tj:最大工作结温,通常为150度和175度。

Tstg:最大存储温度。

Iar:雪崩电流。

Ear:重复雪崩击穿能量。

Eas:单次脉冲雪崩击穿能量。

电器特性:BVdss:DS击穿电压。

Idss:饱和DS电流,uA级的电流Rds(on):见FeaturesIgss:GS驱动电流,nA级的电流gfs:跨导Qg:G总充电电量Qgs:GS充电电量Qgd:GD充电电量,Miller Effect(密勒效应)Td(on):导通延迟时间,从有输出电压上升到10%开始到Vds下降到其幅值90%的时间,Tr:上升时间。

输出电压Vds从90%下降到其幅值10%的时间。

Td(off):关断延迟时间,输入电压下降到90%开始到Vds上升到其关断电压10%时的时间。

Tf:下降时间,输出电压Vds从10%上升到其幅值90%的时间Ciss:输入电容,=Cgd+CgsCoss:输出电容,=Cds+CgdCrss:反向传输电容,=CgcCds---漏-源电容Cdu---漏-衬底电容Cgd---栅-漏电容Cgs---栅-源电容Ciss---栅短路共源输入电容Coss---栅短路共源输出电容Crss---栅短路共源反向传输电容D---占空比di/dt---电流上升率dv/dt---电压上升率Id---漏极电流(直流)Idm---漏极脉冲电流Id(on)---通态漏极电流IDQ---静态漏极电流(射频功率管)IDS---漏-源电流IDSM---最大漏源电流IDSS---栅-源短路时,漏极电流IDS(sat)---沟道饱和电流(漏源饱和电流)Ig---栅极电流(直流)IGF---正向栅电流IGR---反向栅电流IGDO---源极开路时,截止栅电流。

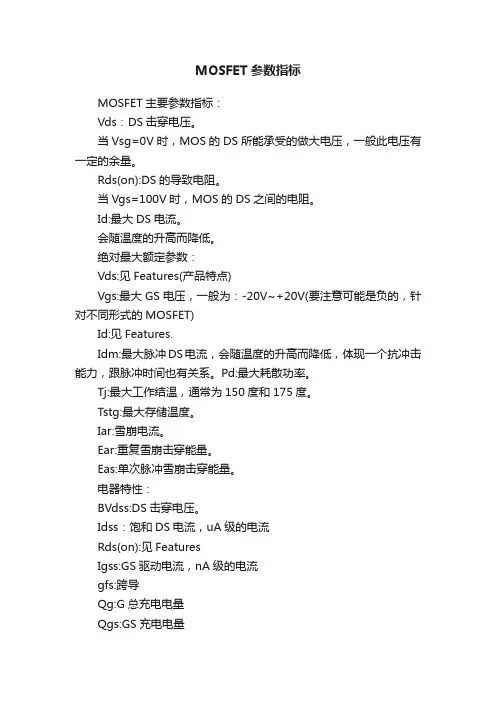

MOSFET参数指标MOSFET主要参数指标:Vds:DS击穿电压。

当Vsg=0V时,MOS的DS所能承受的做大电压,一般此电压有一定的余量。

Rds(on):DS的导致电阻。

当Vgs=100V时,MOS的DS之间的电阻。

Id:最大DS电流。

会随温度的升高而降低。

绝对最大额定参数:Vds:见Features(产品特点)Vgs:最大GS电压,一般为:-20V~+20V(要注意可能是负的,针对不同形式的MOSFET)Id:见Features.Idm:最大脉冲DS电流,会随温度的升高而降低,体现一个抗冲击能力,跟脉冲时间也有关系。

Pd:最大耗散功率。

Tj:最大工作结温,通常为150度和175度。

Tstg:最大存储温度。

Iar:雪崩电流。

Ear:重复雪崩击穿能量。

Eas:单次脉冲雪崩击穿能量。

电器特性:BVdss:DS击穿电压。

Idss:饱和DS电流,uA级的电流Rds(on):见FeaturesIgss:GS驱动电流,nA级的电流gfs:跨导Qg:G总充电电量Qgs:GS充电电量Qgd:GD充电电量,Miller Effect(密勒效应)Td(on):导通延迟时间,从有输出电压上升到10%开始到Vds下降到其幅值90%的时间,Tr:上升时间。

输出电压Vds从90%下降到其幅值10%的时间。

Td(off):关断延迟时间,输入电压下降到90%开始到Vds上升到其关断电压10%时的时间。

Tf:下降时间,输出电压Vds从10%上升到其幅值90%的时间Ciss:输入电容,=Cgd+CgsCoss:输出电容,=Cds+CgdCrss:反向传输电容,=CgcCds---漏-源电容Cdu---漏-衬底电容Cgd---栅-漏电容Cgs---栅-源电容Ciss---栅短路共源输入电容Coss---栅短路共源输出电容Crss---栅短路共源反向传输电容D---占空比di/dt---电流上升率dv/dt---电压上升率Id---漏极电流(直流)Idm---漏极脉冲电流Id(on)---通态漏极电流IDQ---静态漏极电流(射频功率管)IDS---漏-源电流IDSM---最大漏源电流IDSS---栅-源短路时,漏极电流IDS(sat)---沟道饱和电流(漏源饱和电流)Ig---栅极电流(直流)IGF---正向栅电流IGR---反向栅电流IGDO---源极开路时,截止栅电流。

基于BSIM3的超深亚微米器件建模及模型参数提取

陈松涛;刘晓彦;杜刚;韩汝琦

【期刊名称】《固体电子学研究与进展》

【年(卷),期】2003(23)4

【摘要】对适用于超深亚微米电路模拟的 MOSFET器件模型进行了研究 ,完成计入量子效应、多晶硅耗尽效应等基于 BSIM3的 MOSFET模型。

针对阈值电压模型以及 I- V模型中的参数编写了模型参数提取程序 ,采用最小二乘法原理 ,并采用麦夸脱算法以降低参数提取结果对初值的依赖 ,对已有参数进行了修正。

模型以及参数提取结果都分别进行了验证。

【总页数】6页(P406-411)

【关键词】BSIM3;超深亚微米器件;器件模型;参数提取;微电子技术

【作者】陈松涛;刘晓彦;杜刚;韩汝琦

【作者单位】北京大学微电子学研究所

【正文语种】中文

【中图分类】TN4

【相关文献】

1.深亚微米电路NMOS器件HCI退化建模与仿真 [J], 李康;马晓华;郝跃;陈海峰;王俊平

2.超陡倒掺杂分布对超深亚微米金属-氧化物-半导体器件总剂量辐照特性的改善[J], 王思浩;鲁庆;王文华;安霞;黄如

3.深亚微米CMOS器件建模与BSIM模型 [J], 陈志坚;郑学仁;姚若河;李斌

4.深亚微米pMOS器件HCI退化建模与仿真方法 [J], 李康;郝跃;刘红侠;方建平;薛鸿民

5.亚微米MOSFET的BSIM3模型参数提取 [J], 夏增浪;胡贵才

因版权原因,仅展示原文概要,查看原文内容请购买。

提取mos管总剂量效应后bsim4spice参数一、实验内容和要求。

实验内容:(1)使用S-Edit绘制电路图,将其转换成Spice文件。

(2)利用T-Spice的对话框添加仿真命令。

(3)利用W-Edit观察波形。

实验要求:利用Tanner软件中的S-Edit、T-Spice和W-Edit,对NMOS管的参数进行仿真。

NMOS器件的T-Spice参数仿真内容如下:MOS管转移特性曲线(给定VDS、W、L,扫描VGS)MOS管输出特性曲线(给定VGS、W、L,扫描VDS)温度对MOS管输入/输出特性的影响(给定VGS、VDS、W、L,扫描Temp)MOS管W对输入/输出特性的影响(给定VGS、VDS、W/L,扫描W)MOS管L对输入/输出特性的影响(给定VGS、VDS、W/L,扫描L)MOS管W/L对输入/输出特性的影响(给定VGS、VDS、L,扫描W)。

MOS管开关电路输入/输出波形(输入一定频率的方波)。

在MOS管开关电路输入/输出波形中找出传输时间、上升时间和下降时间。

MOS管开关电路传输特性曲线。

MOS管W/L对传输特性的影响(给定L、扫描w)在MOS管传输特性曲线上找出测量输入、输出电压门限,计算噪声裕度。

(2)记录操作步骤,截取相应图片,完成实验报告。

二、实验环境、Tanner软件简介及SPICE命令。

实验环境:Tanner(S-Edit,T-Spice,W-Edit)SPICE命令的插入:Edit-Insert Command命令或工具中的,打开T-Spice Command Tool(T-Spice命令工具)对话框,可以在活动输入文件中插入命令。

《电子器件》实验讲义目录实验一用图示仪测量双极型晶体管的直流参数 (2)实验二晶体管开关时间的测量 (10)实验三晶体管特征频率的测量 (16)实验四晶体管基极电阻的测量 (22)实验五晶体管功率增益和噪声系数的测量 (28)实验六双极型晶体管模型参数提取 (36)实验七MOS结构高频C-V特性测试 (48)实验八MOSFET模型参数的提取 (54)实验九发光二极管参数的测量 (68)实验十半导体激光器常用参数的测定(一) (74)实验十一半导体激光器参数测量(二) (80)实验一 用图示仪测量双极型晶体管的直流参数晶体管在电子技术方面具有广泛的应用。

在制造晶体管和集成电路以及使用晶体管的过程中,都要检测其性能。

晶体管输入、输出及传输特性普遍采用直接显示的方法来获得特性曲线,进而可测量各种直流参数。

晶体管直流参数测试仪很多 ,JT-1型晶体管特性图示仪是最常用的 一种。

本实验的目的是了解JT-1型特性图示仪原理,掌握其使用方法,并用这种仪器进行晶体管直流参数测试及芯片检测,分析晶体管质量,分析晶体管质量,找出失效原因,作为进一步改进器件性能的依据。

一、实验原理利用图示仪测试晶体管输出特性曲线的原理如图1所示。

图中BG 代表被测的 晶体管,R B 、E B 构成基极偏流电路。

取E B >>V BE ,可使I B =(E B - V BE )/ R B 基本保持恒定。

在晶体管C-E 之间加入一锯齿波扫描电压,并引入一个小的取样电阻R C ,这样加到示波器上X 轴和Y 轴的电压分别为V x =V ce =V ca +V ac =V ca -I c R c ≈V caV y =-I c .R c α∝-I c图1测试输出特性曲线的原理电路当I B 恒定时,在示波器的屏幕上可以看到一根I c —V ce 的特性曲线,即晶体管共发射极输出特性曲线。

为了显示一组在不同I B 的特性曲线簇Ici=Φ(Ici, V ce )应该在X 轴的锯齿波扫描电压每变化一个周期时,使I B 也有一个相应的变化,所以应将图1中的E B 改为能随X 轴的锯齿波扫描电压变化的阶梯电压。

2.2场效应管功能及参数介绍开关电源的基本电路由“交流一直转换电路”, “开关型功率变换器”, “控制电路”和整流稳波电路”而组成.输入的电网电压通过“交流一直流转换电路”中的整流和稳器转换成直流电,该直流电源作为“开关型功率变换器”的输入电源,经过“开关型功率更换器”将直流电转变为高频脉冲电波电压输出给“整流滤波电路”,变成平滑直流供给负载,控制电路则起着控制“开关型功率变换器”工作的作用.开关型功率变换器是开关电源的主电路,开关电源的能量转换,电压变换就由它承担.在直流变换器的基础上,由于高频脉冲技术及开关变换技术的进一步发展,出现了推挽式开关型功率变换器,全挢式开关型功率变换器,半挢式﹑单端正激式.单端反激式开关型功率变换器.其控制方法可分为脉冲宽度调制(PWM)和脉冲频调制(PFM)两种.开关电源最重要的组件是MOSFET,它的开通和关短控制着整个电源运转.MOSFET原意是MOS(METAL OXIDE SEWILONDUCTOR,金属氧化物半导体)FET(FIELD DFFECT TRAHSISTOR,场效应晶体),即以金属层(M)的栅极隔着氧化层(0),利用电场的效应来控制半导体(S)的场效应晶体管.功率场应晶体管也分为结型绝缘栅型,但通常主要指绝缘栅型中的MOS型(Metal Oxide Semi Conductor FET),简称功率MOSFET(Power MOSPET).结型功率场效应晶体管一般称作静电感应晶体管(STATIC INTUCTION TRANSISTOR,缩写为SIT).其特点是用栅极电压来控制漏极电流,驱动电路简单,需要的驱动功率小,开关速度快,工作频率高,热稳定性优于GTR,电流容量小,耐压低,一般只适用于功率不超过10KW的电力电子装置.国际整流器公司.(在International Rectifier,缩写IR)把MOSFET用于高压的器件归纳为第3,6,9代,其中包括3,5代,而用于低压的则为第5,7,8代.功率MOSFET按导电沟通可分P沟道和N沟道;按栅极电压幅值可分为耗尽型(当栅极电压为零时漏,源极之间就存在导电沟道)和增强型(对于N或P沟道器,件栅极电压大珪或小于零时才存在导电沟道,功率MOSFET主要是N沟道增强型).2.2.1.功率MOSFET的结构功率MOSPET的内部结构和电气符号如下周所示,其导通时只有一种极性的载流子(多子)参与导电,是单极型晶体管.导电机理与小功率MOS管相同,但结构上有极大区别.小功率MOS管是横向导电器件,功率MOSFET大都采用垂直导电结构,又称为VMOSFET.大大提高了MOSFET 器件的耐压和耐电流能力.按垂直导电结构的差异,又分为利用V型槽实现垂直导电的VVMOSFET和具有垂直导电双扩散MOS结构的VDMOSFET的结构为多元集.如国际整流器公司的HEXFET采用六边形单元;西门子公司的STPMOSFET采用了正方形单元;摩托罗拉公司的TMOS采用了矩形单元按“品”字形排列.2.2.2功率MOSFET的工作方式截止:漏极间加正电源,栅源极间电压为零.P基区与N漂移区之间形成的PN结,反偏;漏源极之间无电流流过.导电:在栅源极间加正电压Vgs,栅极是绝缘的,所以不会有栅极电流流过.但栅极的正电压会将其下P区中的空穴推开.,而将P区中的少子---电子吸引到栅极下面的P区表面.当Vgs大于UT(开启电压或阀值电压)时,栅极下面P区表面的电子浓度将超过空穴的浓度,P型半导体反型成N型而成为反型层,该反型层形成N沟道而PN结缩小消失,漏极和源极导电.2.2.3功率MOSFET的基本特性1.静态特性其转移特性和转出特性如图所示漏极电流Id和栅源间电压Vgs的关系为MOSFET的转移特性.Id较大时,Id与Vgs的关系近似线性 ,曲线的斜率定义为跨导Gfs.在恒流区内,N信道增强型MOSFET的Id可近似表示为:id=Ido(Vgs/VT-1)² (Vgs>VT)图2.3 场效应管的静态特性或取Ido是Vgs=2Vt时的id值MOSFET的漏极伏安特性(输出特性)与GTR的对应关系为:截止区对应于GTR的截止区;饱和区对应于GTR的放大区;非饱和区对应于GTR的饱和区.MOSFET工作在开关状态,即在截止区和非饱和区之间来回转换.MOSFET漏源极之间有寄生二极管,漏源极间加反向电压时器件导通.功率MOSFET的通态分数,对器件幷联时的均流有利.2.动态特性其测试电路和开关过程如下图所示,开遍延迟时间Td(on)指Vp前沿时刻到Vs等于Vt幷开始出Id的时刻间的时间段.上升时间Tr指Vgs上升到MOSFET进入非绝和区的栅压Vgsp的时间段.Id稳态值由漏级电源电压Ve和漏级负载电阻决定.Vgsp的大小和Id的稳态值有关.Vgs达到Vgsp后,在Vp作用下继续升高直至达到稳态,但Id已不变.开通时间ton指开通延迟时间与上升时间之和.关断延迟时间td(off)指Vp下降到零起,Cin通过Rs和Rg放电,Vgs按指数曲线下降到Vgsp时,Id开始减小为零的时间段.下降时间在指Vgs从Vgsp继续下降起,Id减小,到Vgs<Vt时沟道消失,Id下降到零为止时间段.关段时间 toff指关断延迟时间和下降时间之和.3.MOSFET的开关速度MOSFET的开关速度和Cin充放电有很大关系.使用者无法降低Cin,但可降低驱动电路内阻Ro,减小时间常数,加快开关速度.MOSFET只靠多子导电,不存在少子储存效应,因而关断过程非常迅速.它的开关时间在10~100ns之间,工作频率可迖100KHE以上,是主要电力电子器件中最高的. 场控器件静态时几乎不需输入电流.但在开关过程中需对输入电容充放电,仍需一定的驱动动率.开关频率越高,所需要的驱动功率越大.图2.4 场效应管的开关波形4.动态性能的改进在器件应用是除了要考虑器件的电压,电流,频率外,还必须牚握在应用中如何保护器件,不使器件在瞬志变化中受损害.晶间管是两个双极型晶体管的组合,又加上因大面积带来的大电容,所以,其dv/dt能力是较为脆弱的.对di/dt来说,它还存在一个导通区的扩展问题,所以也带来相当严格的限制.功率MOSFET的情况有很大的不同.它的dv/dt及di/dt的能力常以每纳秒的能力来估量.尽管如此,它也存在动态性能的限制,对于这些,我们可以以从功率MOSFET的基本结构予以理解.图2.5 功率MOSFET的等效电路如图2.5所示,除了考虑器件的每一部分存在电容以外,还必须考虑MOSFET还幷联着一个二极管,同时,从某个角度看,它还存在一个寄生晶体管(就像IGBT)也寄生着一个晶间管一样),这几个方面是研MOSFET动态特性很重要的因素.首先,MOSFET结构中所附带的寄生二极管具有一定的雪崩能力.通常用单次雪崩能力和重复雪崩能力来表迖.当反向di/dt很大时,二极管会承受一个速度非常快的脉冲尖制,它有可能进入雪崩区,一旦超越其雪崩能力就有可能将器件损坏.对于任一种PN结二极管来说,仔细研究其动态特性是相当复杂的.它们和我们一般理解PN结正向时导通而反向时阻断的简单概念很不相同.当电流迅速下降时,二极管有一阶段失去反向阻断能力,即所谓反向恢复时间.PN结要求迅速导通时,也会有一段时间幷不显示很低的电阻.在功率MOSFET中,一旦二极管有正向注入,所注入的少数载流子也会增加,是作务多子器件的MOSFET的复杂性.应在功率MOSFET的统计过程采取措施,使其中的寄生晶体管尽量不起作用.在不同代的功率MOSFET中所采取的措施有所不同,但总的原则是使漏极下的横向电阻Rb的值尽量小.因为,只有在漏极N区下的横向电阻流过足够电流,为这N区功力正偏的条件下,寄生的双极性晶阐管才开始发难.然而,在严峻的动态条件下,因dv/dt通过相应电容引起的横向电流可能足够小.此时,这个寄生的双极性晶体管就会启动,有可能给MOSFET带来损坏,所以,考虑瞬志性能时,对功率MOSFET器件内部的各个电容都必须予以注意.2.3.4 MOSFET的主要参数1.漏源击穿电压Udss:Udss通常为结温在25℃ ~150℃之间,对漏源极的击穿电压.该参数限制了MOSFET的最高工作电压,常用的MOSFET的Udss通常在1000V以下.尤其以500V及以下器件的各项性能最佳.需要注意的是,常用的MOSFET的漏源击穿电压具有正温度系数,因此在温度低于测试条件时,Udss会低于产品手册中给出的资料.2.漏极连续电流额定Id和漏极脉冲电流峰值Idm:这是标称电力MOSFET电流定额的参数,一般情况下,Idm是Id的2~4倍.工作温度对器件的漏极电流影响很大,生产厂商通常也会给出不同壳温下,允许的漏极连续电流变化情况.在计算实际器件参数时,必须考虑其损耗及散热情况得出壳温,由此核算器件的电流定额.通常在壳温为80~90℃时,器件可用的连续工作电流只有Tc=25℃时Id的60%~70%.3.漏源通态电阻Rds(on):该参数是栅源间施加一定电压(10~15V)时,漏源间的导通电阻,漏源通态电阻Rds(on)直接影响器件的通态降及损耗,通常对于额定电压低﹑电流大的器件,Rds(on)较小.此外, Rds(on)还与驱动电压及结温有关.增大驱动电压,可以减小Rds(on). Rds(on)具有正的温度系数随着结温的升高而增加,这一特性使MOSFET幷联运行较为容易.4.栅源电压Ugss:由于栅源之间的SiQ2绝缘层很薄,Ugs|>20V时将导致绝/缘层击穿.因此在焊接﹑驱动等方面必须注意.5.跨导Gfs:在规定的工作点下,MOSFET转移特性曲线的斜率称为该器件跨导,即Gfs=Did/dugs6.极间电容:MOSFET的三个电极之间分别存在极间电容Cgs﹑Cgd和Cds.,一般生产厂商提供的是漏源极短路时的输入电容Ciss﹑共源极输出电容Coss和反向转移电容Crss.它们之间的关系是:Ciss=Cgs+CgdCrss=CgdCoss=Cgd+Cds尽管MOSFET是用栅源间电压驱动的,阻抗很高,但由于存在输入电容Ciss,开关过程中驱动电路要对输入电容充放电.这样,用作高频开关时,驱动电路必须具有很低的内阻抗及一定的驱动电流能力.2.2.5米勒效应与米勒电容值和三极管一样,米勒效应和米电容值是MOSFET高频环路的一重要参数,在图下44中是一个简单的高频晶体管模型,图中产生一个负载电阻连接到输出,在这里我们确定电流增益,目的就是为了论证米勒效应.在输入结点a上,我们利用KCL电流环路,可以写出如下方程:Ii=jwCgsVgs+jwCgd(Vgs-Vds) ①在这里Ii是输入电流,类似地在输出结点b上的点输出电流为:Vds/RL+gmVgs+jwCgd(Vds-Vgs)=0 ②我们可以联立①②消去Vds,输入电流可以为:Ii=jw{Cgs+Cgd[1+gmRL/1+jwRLCgd]}Vgs ③一般情况下,(wRLCgd)远比1小,因此我们可以忽略jwRLCgd,因此③方程可以写为:Ii=jw[Cgs+Cgd(1+gmRL)]Vgs ④而由我们以前关于米勒电容的描述方程,参数Cm,即米勒电容值可表示如下:Cm=Cgd(1+gmRL).在方程⑤中可以清楚地表明附加D极迭加电容的等效容值,当晶体管被偏置在饱和区时,作为放大电路中,总的Cgd电容值主要是迭加电容,由于米勒效应迭加电容会翻倍,并且在一个限定的放大宽带里会变成一个有意义的参数,追求小的迭加电容是其结构的又一挑战.MOSFET的关断频率ft被定义为在电流增益为1时的频率,或是输入电流Ii的幅值等于理想负载电流Id,即Ii=jw(Cgs+Cm)Vgs;理想负载电流:Id=gmVgs ⑥因此电流幅度的增益为:∣Ai∣=∣Id∣/∣Ii∣∣Ai∣=∣Id∣/∣Ii∣=gm/2πf(Cgs+Cm) ⑦∣Ai∣=1,我们可以得到关断频率Ft=gm/2π (Cgs+Cm) = gm/2πCG在这里CG是一个输入g极电容的等效值.2.2.6 MOSFET的驱动驱动电路是电力电子主电路与控制电路之间的接口,是实现主电路中电力电子器件按照预定的设想运行的重要环节.采用性能良好驱动电路,可以使电力电子器件工作在较为理想的开关状态,缩短开关时间,减小开关损耗.此外,对器件或整个装置的一些保护措施也往往设在驱动电路中,或通过驱动电路实现,因此驱动电路对装置的运行效率﹑可靠性和安全性都有重要的影响.驱动电路的基本任务是将控制电路发出的信号转换为加在电力电子器件控制端和公共端之间﹑可以使其开通或关断的信号.同时驱动电路通常还具有电气隔离及电力电子器件的保护等功能.电气隔离是实现主电路间电量的隔离,在含有多个开关器件的电路中,电气隔离通常是保证电路正常工作的必要环节,同时电气隔离可以减少主电路开关噪声对控制电路的影响,幷提高控制电路的安全性.电气隔离一般采用光隔离(如光耦合器)或磁隔离(如脉冲变压器)来实现.MOSFET为电压驱动型器件,其静态输入电阻很大,所以需要的驱动功率较小.但由于栅源间﹑栅射间存在输入电容,当器高频通断时,电容频繁充放电,为快速建立驱动电压,要求驱动电路输出电阻小,且具有一定的驱动功率.MOSFET开通的栅源极间驱动电压一般取10~15V,在器件关断时,对器件施加反向电压可减小关断时间,保证器件可靠关断,反向电压一般为0~15V.此外,在栅极驱动回路中,通常需串入一个低值电阻(数欧至数十欧),以减小寄生振荡,该电阻阻值应随被驱动器件电流额定值的增大而减小.2.2.7 MOSFET的栅极驱动电流和驱动电阻的算法在MOSFET的驱动中,它不像双晶体一样,要使用精确的逆向电流才能使晶体管关闭,这是由于MOSFET为多数载流子的半导体,因此只要将栅极额到源极电压移去,就可将MOSFET关闭.移去栅极电压时,这时漏源之间会呈现很高的阻抗,因而除了漏电流外,可抑制其它电流的产生.MOSFET的直流输入阻抗是非常高的.在Vgs等与10V时,其栅极电流只是毫安级的.因此一旦栅极被驱动起来,在Vgs等与10V时,这个电流可以被忽略.然而,在栅-源极间有一个相当大的电容值,这就需要一个相对大的电流值,使栅极至源极电压脉冲波必须传输足够的电流,在期望的时间内,给输入电容器充电, 假如Vgs等与10V时来驱动栅极的开关来控制漏极电流的开关速率,在这里栅极驱动电流值一定要被精确算出来.在图2.6中,在Vgs等与10V时,Ig由两部分I1和I2组成,包括两个电容C1何C2.其中是栅极到源极的的结电容,可用Ciss来表示,C2是栅极到漏极的结电容,可用Crss来表示.对于在开通时间Tr,栅-源电压为10V时,栅极所需的驱动电流I1为图2.6 场效应管的工作电路然而,当驱动电流达到10V时,漏极的开关电压是从Vdc到Vgs之间的变动,有时会被带的更低.由于在此期间C2最高变动电压为Vdc,最低变动为10V.所以在此期间其所需的驱动电流I2为此外,驱动电压源阻抗Rg必须很低,目的就是为了实现晶体管的高速开关作用,这里我们有下面一个简略的公式可以大体算出2.2.8 MOSFET栅极驱动的优化设计MOS管的驱动对于MOS管的工作效果起着决定性的作用.我们往往既要考虑减少开关损耗,又要求驱动波形较好,即振荡小.过冲小,EMI 小,这往往是立相矛盾的;需要寻求一个平衡点即驱动电路的优化设计.优化驱动电路设计包含两个部分,一是最优化的驱动电流,电压的波形,二是最优化的驱动电压,电流的大小.在驱动电路优化设计之前我们必须先清楚MOS管的模型,MOS管的开关过程,MOS[管的栅极电荷以及MOS管有的输入输出电荷,跨越电荷,等效电荷等参数对驱动的影响.(1)MOS管的模型MOS管的等效电路模型及寄生参数如下图所示.其中LP和R9代表封装端到实际的栅极间线路的电感和电阻.C1代表从栅极到源端N4间的电阻,它的值是由结构因的.C2+C4代表从栅极到源P区间的电容,C2是电介质电容,其值是因定的,而C4由源极到漏极的耗尽区的大小决定,幷随栅极电压的大小而改变.当栅极电压从0升到Vgs(th)时,C4使整个栅极源电容增加10%~15%.C3+C5也是由一个固定大小的电介质电容和一个可变电容构成,当漏极电压改变极性时,其可变电容变得相当大.C6也是随漏极电压变换的漏涛电容.MOS管的输入ˋ输出电容ˋ跨越电容和栅源电容,栅漏电容,漏源电容间的关系如下:Ciss=Cgs+Cgd~C1+C4+C5;(Crss=Cgd~C5)Coss=Cds+Cgd~C5+C6(2)MOS管的开通过程开关管的开关模式电路如下所示,二极管可以是外接的或MOS管已有的,.开关管在开通时的二极管电压,电流波形如下图所示.在图中阶段1.开关管关断,开关电流为零,此时二极管电流和电感电流相等;在阶段2开关打开,开关电流上升,同时二极管电流下降.开关电流上升的斜率和二极管电流下降的斜率的绝对值相同,符号相反;在阶段3开关电流继续上升,二极管电流继续下降,幷且二极管从负的反向最大电流Irrm开始减小,开关管的从正的最大电流也开始减小,它们斜率的绝对值相等;在阶段5开关管完全开通,二极管的反向恢复完成.开关管电流等于电感电流.下图二是存储电荷高或低的两种二极管电流,电压波形.从图中我们可以看出存储电荷少,即在空载或轻载时是最坏条件.所以我们优化驱动电路设计时应着直考虑前置电流低的情况,即空载或轻载的情况,应使这时二极管产生的振动在可接受范围内.(3)栅极电荷Qg和驱动效果的关系栅极电荷Qg是使栅极电压0从升到10v所需的栅极电荷,它可以表示为驱动电流X开通时间或栅极电容X栅极电压.现在大部分MOS 管的栅极电荷Qg值从几十nC到一二百nC.栅极电荷Qg包括栅极到源极电荷Qgs和栅极到漏极电荷,Qgd,即密勒电荷.Qgs是使栅极电从0升到门限值(约3v)所需电荷;Qgd是漏极电压下降时克服密勒效应所需电荷.这存在于Vgs,曲线比较平坦的第二段(如图一所示),此时栅极电压不变,栅极电荷积聚而漏极电压急剧下降,也就是在这时候需要驱动尖峰电流限制,这由苾片内部完成或外接电阻完成.实际的Qg还可以略大,以减小等效Ron,但是太大也不益,所以10v到12v的驱动电压是比较合理的.这还包含一个重要的事实:需要一个高的尖峰电流以减小MOS管损耗和转换时间.重要的是,对于IC来说,MOS管的平均电容负荷幷不是MOS管的输入电容Ciss,而是等效输入电容Ceff:Ceff=Qg/Vgs,即整个0<Vgs<Vgs(th)的等效电容,而Ciss只是Vgs=0时的等效电容.漏极电流大Qg波形的Qgd阶段出现,此时漏极电压依然很高,MOS管的损耗此时最大,幷随Vds的减小而减小.Qgd的大部分用来减小Vds 从关断电压到Vgs(th)产生的密勒效应.Qg波形第三段的等效负载电容是: Ceff=[Qg-(Qgd+Qgs)]/[10v-Vgs(th)](4)优化栅极驱动设计在大多数的开关功率应用电路中,当栅极被驱动,开关导通时漏极电流上升的速度是漏极电压下降速度的几倍,这将造成功率损耗增加.为了解决问题,我们可以增加栅极驱动电流,但增加栅极驱动电流上升斜率又将带来过冲.振荡EMI等问题.为了优化栅极驱动设计,这些互相矛盾的要求必须寻求一个平衡点,而这个平稀点就是开关导通蛙漏极电流上升的速度和漏极电压下降速度相等这样一种波形,理想的驱动波形如下图所示:图中的Vgs波形包括了这样几部分:Vgs第一段是快速上升到门限电压;Vgs第二段是比较缓的上升速度以减慢漏极电流折上升速度,但此时的Vgs也必须满足所需的漏极电流值;Vgs第四段快速上升使漏极电压快速下降;Vgs第五段是充电到最后的值.当然,要得到完全一样的驱动波形是很困难的,但是可以得到一个大概的驱动电流波形,其上升时间等于理想的漏电压下降时间或漏极电流上的时间,幷且具有足够的尖峰值来充电开关期间的较大等效电容.该栅极尖峰电流Ip的计算是:电荷必须完全满足开关时期的寄生电容所需,即Qg=Ip*ton/2 而Qg=Ciss[2.5Vgs(th)+Id/Gm]+Crss(Vdd-Vgs(th))其中ton=tn+td+tr 所以Ip=2/ton Ciss[2.5Vgs(th)+Id/Gm]+Crss[Vdd-Vgs(th)]2.2.9.MOS上的热耗计算半导体的失效率通过多年的测试才能更好的估计出与温度之间的关系,在这里重现出内部的图面,如下所示:这是一幅从统计学上预计了NPN硅晶体管的特性,它也表明了一般大多数电子元器件随温度上升的快速增长失效率.特别是在高温下,其作用十分明显.如一个晶体管在180度时的寿命只有在25度时的1/20,或者可以说有20倍的失效率.图2.7 半导体内部的图面明显的,当有更多的类型的元器件导入到电源中时,其失效率就对高温更加的敏感.因此,对一个电源来讲,必须考虑它的温升,在组件的选用时更是如此.因此在这里考虑MOS的温升是十分有必要的.(1)在MOS上的热量分析(与电路中的电流相当)明显,根部是管中最热的地方,由左向右传递,最后到达散热器中,这个散热器与空气环境相连.存在一个热传导器与散热器相连.其传导率Q由Fourier定理来求:Q=(A*Td)/(L*Rθ)在此,Q为热率, Td为两部分的温度差,A为穿过部分的面积,L为传导长度也即传导宽度. Rθ为结与空气间的热阻.A和L是物理数据,在此可以近似的表示为:QαTd/Rd 与 I=V/R 相似的但这一公式只适用于一般的固体热传导.若是用热管来传导,将有一个不是线性的热阻,则就不遵循这一平衡.而在热传导不好的金属中,在一般的晶体温度下各种随温度的热阻是微不足道的,可以把其忽略.(2)热阻Rθ(相当于电路中的电阻)任以以上为例,假定消耗了10J/S(Q=10W),热量也跟着消耗(在此相对于10A电流)将加重内部的温差Td, 在热阻上相应的就有热量发出.当一稳态被建立,在内部的温度可能被聚集起来由于温度的上升和热阻的散热.在本例中,是由边缘的表面与空气交换温度.内部温度恒定,其它形式的温度在内部能通过由右到左集累.如图,可见其关系式图2.8 热阻等效由上图可见,可以认为有三个热阻Rjc,Rch,Rha.其中从右至左, Rha是最重要的,因它在其中是最大的.它指由边缘传热到空气中的热阻值.第二个Rch指有一个来自边缘通过云母绝热片,到达MOS的表壳.而最后一个Rjc是指壳到内部结点的热阻.为方便,可以认为每一部分的热阻都是独立的,在内部开始交换.这样,等同于电路中的电阻,则有其整个的热阻为Rθ= Rjc+Rch+Rha.可以用这个来衡量由结点到空气的总的温度差.用公式表示为:T=Q*Rθ (其中的T为温升, Q为结点上的消耗.)(3)结温的计算由以上可见,因损耗机易被知道,MOS的结温很容易就被建立.而在实际中,开关模式中的损耗是机难建立的,由于这样的因素,我们必须建立热模型,通过测俩不同的温度下穿过内部已知热阻的热量来算.温差可以由每秒中结上产生的热量和热阻来定义.由前图给出,已知热率和温差.对每一个热器件,可以用下式表示:△T=Wj* Rθ (其中△T为温差, Wj为结上的损耗)不同内部的温度可以用下式表示:热器表面温度Th:Th=( Wj* Rha)+Tamb (其中的Tamb为空气温度)MOS表面的温度:Tds=[ Wj*( Rch+Rha)]+ Tamb结温度是整个穿过组件的温度,包括环境温度:Tj=[ Wj*( Rjc+Rch+Rha)]+ Tamb由以上可知,如果在结上的能耗和热阻到热器或者散热器上的损耗已知,那幺这个结和内部的温度就可以被清楚计算,若果散热器上的温度被测量出来和热阻已知的情况下,结温损耗也就可以知道了.。

实验二NMOS工艺流程模拟及电学参数提取模拟实验一、实验目的1. 熟悉Silvaco TCAD的仿真模拟环境;2.掌握基本的nmos工艺流程,以及如何在TCAD环境下进行nmos工艺流程模拟;3.掌握器件参数提前方法,以及不同工艺组合对nmos晶体管的阈值电压、薄层电阻等电学参数的影响;二、实验要求①仔细阅读实验内容,独立编写程序,掌握基本的TCAD使用;②熟悉nmos晶体管的基本工艺流程,和关键工艺参数;③记录Tonyplot的仿真结果,并进行相关分析。

三、实验内容1. nmos晶体管整体工艺模拟设计nmos晶体管工艺流程模拟程序,运行得到相应的器件模型(参考教程p57~p60页程序)NMOS晶体管的基本工艺流程:a.衬底硅氧化:在衬底表面产生一层相对较厚的SiO2有选择地刻蚀氧化区,暴露出将来用来生成MOS晶体管的硅表面;b.用一高质量的氧化物薄膜覆盖在Si表面,这层氧化物最终将形成MOS晶体管的栅极氧化物;c.在薄氧化层顶部淀积一层多晶硅。

多晶硅可以用做MOS晶体管的栅电极材料,也可以用做硅集成电路中的互连线;d.成型和刻蚀多晶硅层,形成互连线和MOS管的栅极,刻蚀未覆盖多晶硅的那层薄栅极氧化物,裸露出硅表层,这样就可以在其上面形成源区和漏区了;e.通过扩散或离子注入的方式,整个硅表层就会被高浓度的杂质所掺杂,形成源区和漏区;f.用一层SiO2绝缘层覆盖整个表面对绝缘的氧化层成型得到源极和漏极的接触孔,表层蒸发覆盖一层铝,形成互连线,将金属层成型并刻蚀,其表层形成了MOS管的互连。

NMOS晶体管工艺流程模拟程序:go athena#line x loc=0 spac=0.1line x loc=0.2 spac=0.006line x loc=0.4 spac=0.006line x loc=0.5 spac=0.01##line y loc=0.00 spac=0.002line y loc=0.2 spac=0.005line y loc=0.5 spac=0.05line y loc=0.8 spac=0.15#init orientation=100 c.phos=1e14 space.mul=2# pwell formation including masking o? of the nwell#di?us time=30 temp=1000 dryo2 press=1.00 hcl=3#etch oxide thick=0.02##P–well Implantimplant boron dose=8e12 energy=100 pears#di?us temp=950 time=100 weto2 hcl=3## N–well implant not shown# welldrive starts heredi?us time=50 temp=1000 t.rate=4.000 dryo2 press=0.10 hcl=3 #di?us time=220 temp=1200 nitro press=1#di?us time=90 temp=1200 t.rate=?4.444 nitro press=1#etch oxide all## sacri?cial “cleaning”oxidedi?us time=20 temp=1000 dryo2 press=1 hcl=3#etch oxide all# gate oxide grown heredi?us time=11 temp=925 dryo2 press=1.00 hcl=3## Extract a design parameterextract name=“gateox”thickness oxide mat.occno=1 x.val=0.5 ##vt adjust implantimplant boron dose=9.5e11 energy=10 pearson#depo poly thick=0.2 divi=10##from now on the situation is 2–D#etch poly left p1.x=0.35#method fermi compressdi?use time=3 temp=900 weto2 press=1.0#implant phosphor dose=3.0e13 energy=20 pearson#depo oxide thick=0.120 divisions=8#etch oxide dry thick=0.120#implant arsenic dose=5.0e15 energy=50 pearson#method fermi compressdi?use time=1 temp=900 nitro press=1.0# pattern s/d contact metaletch oxide left p1.x=0.2deposit alumin thick=0.03 divi=2etch alumin right p1.x=0.18# Extract design parameters# extract ?nal S/D Xjextract name=“nxj”xj silicon mat.occno=1 x.val=0.1 junc.occno=1# extract the N++ regions sheet resistanceextract name=“n++ sheet rho”sheet.res material=“Silicon”\mat.occno=1 x.val=0.05 region.occno=1# extract the sheet rho under the spacer, of the LDD regionextract name=“ldd sheet rho”sheet.res material=“Silicon”\mat.occno=1 x.val=0.3 region.occno=1# extract the surface conc under the channel.extract name=“chan surf conc”surf.conc impurity=“Net Doping”\ material=“Silicon”mat.occno=1 x.val=0.45# extract a curve of conductance versus bias.extract start material=“Polysilicon”mat.occno=1 \bias=0.0 bias.step=0.2 bias.stop=2 x.val=0.45extract done name=“sheet cond v bias”\curve(bias,1dn.conduct material=“Silicon”mat.occno=1 region.occno=1) \ out?le=“extract.dat”# extract the long chan Vtextract name=“n1dvt”1dvt ntype vb=0.0 qss=1e10 x.val=0.49structure mirror rightelectrode name=gate x=0.5 y=0.1electrode name=source x=0.1electrode name=drain x=0.9electrode name=substrate backsidestructure out?le=mos0.str# plot the structuretonyplotmos0.str-setmos0.set2.晶体管电学参数提取在晶体管工艺仿真程序基础上,设计结深、源漏电阻等电学参数提取程序,并分析工艺参数(掺杂溶度,掺杂区域、材料等)对器件电学性能的影响。

MOSFET模型参数的提取 计算机辅助电路分析(CAA)在LSI和VLSI设计中已成为必不可少的手段。为了优化电路,提高性能,希望CAA的结果尽量与实际电路相接近。因此,程序采用的模型要精确。SPICE-II是目前国内外最为流行的电路分析程序,它的MOSFET模型虽然尚不完善,但已有分级的MOS 1到3三种具一定精度且较实用的模型。确定模型后,提取模型参数十分重要,它和器件工艺及尺寸密切相关。尽管多数模型是以器件物理为依据的,但按其物理意义给出的模型参数往往不能精确的反映器件的电学性能。因此,必须从实验数据中提取模型参数。提取过程也就是理论模型与实际器件特性之间用参数来加以拟合的过程。可见,实测与优化程序结合使用应该是提取模型参数最为有效的方法。 MOS FET模型参数提取也是综合性较强的实验,其目的和要求是: 1、熟悉SPICE-II程序中MOS模型及其模型参数; 2、掌握实验提取MOS模型参数的方法; 3、学习使用优化程序提取模型参数的方法。

一、实验原理 1、 SPICE-II程序MOS FET模型及其参数提取

程序含三种MOS模型,总共模型参数42个(表1)。由标记LEVEL指明选用级别。一级模型即常用的平方律特性描述的Shichman-Hodges模型,考虑了衬垫调制效率和沟道长度调制效应。二级模型考虑了短沟、窄沟对阈电压的影响,迁移率随表面电场的变化,载流子极限速度引起的电流饱和和调制以及弱反型电流等二级效应,给出了完整的漏电流表达式。三级模型是半经验模型,采用一些经验参数来描述类似于MOS2的二级效应。 MOS管沟道长度较短时,需用二级模型。理论上,小于8um时,应有短沟等效应。实际上5um以下才需要二级模型。当短至2um以下,二级效应复杂到难以解析表达时,启用三级模型。MOS模型参数的提取一般需要计算机辅助才能进行。有两种实用方法,一是利用管子各工作区的特点,分段线性拟合提取;二是直接拟合输出特性的优化提取。其中,直流参数的优化提取尚有不足之处:优化所获仅是拟合所需的特定参数,物理意义不确,难以反馈指导工艺和结构的设计;只适合当前模型,模型稍做改动,要重新提取,不利于分段模型;对初值和权重的选取要求很高。 2、模型公式 N沟MOSFET瞬态模型如图1所示。当将图中二极管和漏电流倒向,即为P沟模型。若去掉其中电容即变为直流模型。 (1) 一般模型(MOS1模型) 漏电流表达式分正向工作区和反向工作区两种情况:

1) 正向工作区,0DsV前提下:

表1. MOS场效应晶体管模型参数表 序号 名称 含义 单位 隐含值 举例 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 LEVEL VOT KP GAMMA PHI LAMBDA RD RS CBD CBS IS PB CGSO CGDO CGBO RSH CJ MJ CJSM MJSM JS TOX NSUB NSS NFS TPG XJ LD UO UCRIT UEXP UTRA VMAX NEFF 模型标志 零偏压阈值电压 跨导参数 体阈值参数 表面势 沟道长度调制效应(仅对MOS1和MOS2) 漏欧姆电阻 源欧姆电阻 零偏压B-D结电容 零偏压B-S结电容 衬底结饱和电流 衬底结电势 每米沟道宽度的栅-源覆盖电容 每米沟道宽度的栅-漏覆盖电容 每米沟道宽度的栅-衬底覆盖电容 漏和源扩散区薄层电阻 每平方米结面积的零偏压衬底结底部电容 衬底结底部梯度因子 每米结周界的零偏压衬底结侧壁电容 衬底结侧壁梯度因子 每平方米结面积的零偏压衬底结饱和电流 氧化层厚度 衬底掺杂 表面态密度 表面快态密度 栅材料类型 0 铝栅 1 硅栅,掺杂和衬底相反 -1 硅栅,掺杂和衬底相同 结深 横向扩散 表面迁移率 迁移率下降的临界电场(对MOS2) 迁移率下降的临界电场指数(对MOS2) 横向电场系数(对迁移率)(MOS2时删去) 载流子的最大漂移速度 总沟道电荷(固定的和可动的)(对MOS2) - V A·V2 V2/1 V V1 F F A V F·m1 F·m1 F·m1 方/ F·m2 - F·m1 - A·m2 m cm3 cm2 cm2 - m m cm2·V1·s1 V·cm1 - - m·s1 - 1 0.0 2.0E-5 0.0 0.6 0.0 0.0 0.0 0.0 0.0 1.0E-11 0.8 0.0 0.0 0.0 0.0 0.0 0.5 0.0 0.33 0.0 1.0E-7 0.0 0.0 0.0 1 0.0 0.0 600 1.0E4 0.0 0.0 0.0 1.0 1.0 3.1E-5 0.37 0.65 0.02 1.0 1.0 20FF 20FF 1.0E-15 0.87 4.0E-11 4.0E-11 2.0E-10 10.0 2.0E-4 0.5 1.0E-3

1.0E-7 4.0E15 1.0E10 1.0E10

1um 0.8um 700 1.0E4 0.7 0.3 5.0E4 5.0 35 36 37 38 39 40 41 42 XQC KF AF FC DELTA THETA ETA KAPPA 薄氧化层电容的模型标志和漏端沟道电荷 分配系数(0~0.5) 闪烁噪声系数 闪烁噪声指数 正偏时耗尽电容公式中的系数 阈值电压宽度效应(对MOS2和MOS3) 迁移率调制系数(对MOS3) 静态反馈系数(对MOS3) 饱和场因子(对MOS3) - - - - - V1 - - 1.0 0.0 1.0 0.5 0.0 0.0 0.0 0.2 0.4 1.0E-26 1.2

1.0 0.1 1.0 0.5

当0THGsVV为截止区,ID=0; 当DSTHGsVVV0为饱和区, )1()()2/(2DSTHGSDVVVI(1) 当THGSDSVVV0为线性区 )1(])(2[)2/(2DSDSDSTHGSDVVVVVI(2)

其中, 0(22)THTFBSSVVV (3)

[/(2)]pDKWLL (4) 2)反向运用时,将S与D互换且注意电压极性即可。公式中THV系有效阈值电压,DL是横向扩散长度。0TV、Kp、、、B(即2F)是直流分析的五个基本模型参数。前三个出现在饱和区DI公式中,体现了沟道调制效应;后二个出现在THV式中,体现了衬底偏置效应。程序优先使用直接给定的 0TV、Kp、、和B数值,否则自行计算取得。所用关系式是:

0TFBBBVV (5)

00pxKC (6)

02/subsixqNC (7) (2/)ln(/)BsubiKTqNn(8)

0/FBGCssxVqNC(9)

000/xxxCT(10)

图38.1 N沟MOSFET模型瞬态等效电路

'D

DDRBDC

C

GSCGBCSR

BSCBSIBDIGB

'S上面oxT(氧化膜厚度)、ssN(表面态密度)、subN(衬底浓度)和DL都是工艺参数,0

是低表面电场下表面迁移率,GC为栅-衬底接触电势差,由subN和栅材料决定。 (2) 二级模型(MOS2模型) 1)阈值电压修正

0()4siTHFBBSBBSBBSxVVVVCW(11)

22[1(112)]2JSDSJJXWW

LXX(12)

1/2[2()/()]DsiBBSDSsubWVVqN(13)

1/2[2()/()]SsiBBSsubWVqN(14)

其中SW、DW和JX分别为源、漏结耗尽宽度和扩散结层深,为窄沟效应系数,S体现了短沟效应和栅漏静电反馈效应。 2)迁移率修正

exp00[]()UcrltsiS

xGSTHTraDS

UCVVUV

/GSTHTraDScrltsioxVVUVUC(15) 引入了crltU,TraU,expU来修正未考虑表面场影响的0,SPICE-IIG文本TraU取零。 3)漏源电流方程修正 a) 强反型(线性区)电流公式

/2/2{()22[()()]}3DSDSoxGSTHDSSDSBBSBBSVWICVVVLVVV

(16)

()4siTHFBBBBSoxVVVWC (17) 14sioxWC (18)

其中,TNV和包含了短沟效应,S是因表面电场影响迁移率的修正。 b)弱反型(亚阈区)电流公式(onGSVV下)

DI=DI(线性区公式取)exp[()/]GSonGSonVVqVVnKT(19)