例:如图所示为边沿JK触发器74LS74的CP、D、/RD、/SD 端的输入波形,请画出输出端

Q的波形。设触发器的初始状态为Q=0.

初态为 0,故保持为 0。

保持 置 0保持置 1 例:如图所示为边沿JK触发器74LS74的CP、D、/RD、/SD 端的输入波形,请画出输出端Q的波形。

例:如图所示为边沿JK触发器74LS74的CP、D、/RD、/SD 端的输入波形,请画出输出端Q的波形。

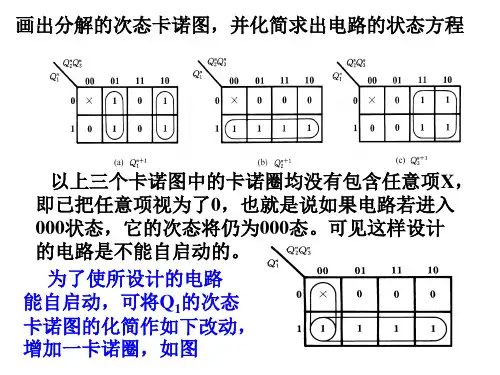

取值组合,与电路初原态来的为状0态,无故关。保持为 0。

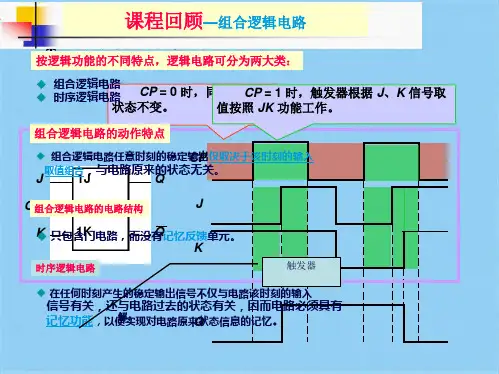

组合逻辑电路任意时刻的稳定输C出P 仅取决于该时刻的输入 J 取值组合1J,与电路原来Q的状态无关。

CP组合逻辑电C路1 的电路结构

J

K 只包含1K门电路,而没有Q记忆反馈单元。 K

时序逻辑电路

触发器

在任何时刻产生的稳定输出信号不仅与电路该时刻的输入

信号有关,还与电路过去的状态有关,因而电路必须具有 记忆功能,以便解实:现对电路原来Q状态信息的记忆。

主要有特性表、特性方程、驱动表

(又称激励表)、状态转换图和波形图

D (又称时序图)等。

画出 Q 和 Q 的波形。

CP

组合逻辑电路任意时刻的稳定输出仅取决于该时刻的输入

CP = 0,同步触发器状态不变

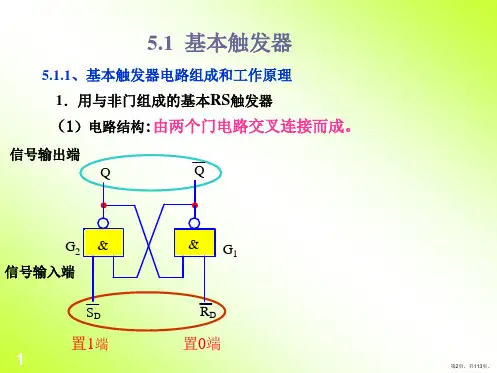

置 0 端 RD 和置 1 端 SD 低电平有效。

定义:Q=1,Q=0为触发器的1状态

解:

Q

触发器

同步触发器在 CP = 1 期间能发生多次翻转,这种现象称为 空翻

信号有关,还与电路过去的状态有关,因而电路必须具有

组合逻辑电路的电路结构

解: RD SD Qn+1

Q

0 0 不定

01 0

Q