高速模数转换器(ADC)的INL DNL测量

- 格式:docx

- 大小:101.95 KB

- 文档页数:7

高速模数转换器(ADC)的INL/DNL测量摘要:尽管积分非线性和微分非线性不是高速、高动态性能数据转换器最重要的参数,但在高分辨率成像应用中却具有重要意义。

本文简要回顾了这两个参数的定义,并给出了两种不同但常用的测量高速模数转换器(ADC)的INL/DNL的方法。

近期,许多厂商推出了具有出色的静态和动态特性的高性能模数转换器(ADC)。

你或许会问,“他们是如何测量这些性能的,采用什么设备?”。

下面的讨论将聚焦于有关ADC两个重要的精度参数的测量技术:积分非线性(INL)和微分非线性(DNL)。

尽管INL和DNL对于应用在通信和高速数据采集系统的高性能数据转换器来讲不算是最重要的电气特性参数,但它们在高分辨率成像应用中却具有重要意义。

除非经常接触ADC,否则你会很容易忘记这些参数的确切定义和重要性。

因此,下一节给出了这些定义的简要回顾。

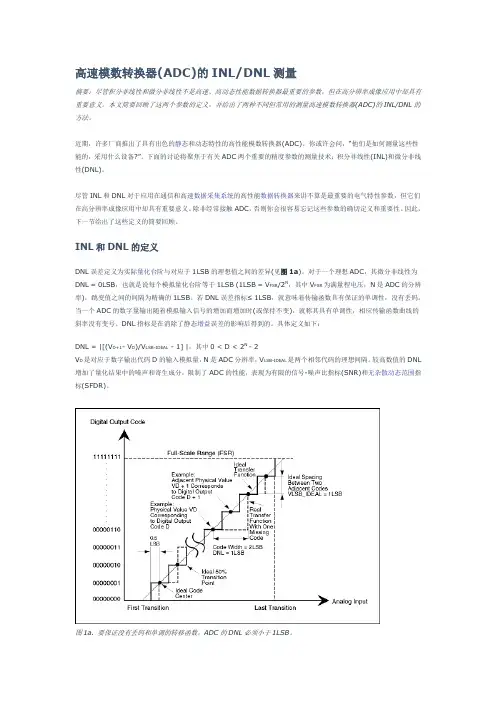

INL和DNL的定义DNL误差定义为实际量化台阶与对应于1LSB的理想值之间的差异(见图1a)。

对于一个理想ADC,其微分非线性为DNL = 0LSB,也就是说每个模拟量化台阶等于1LSB (1LSB = V FSR/2N,其中V FSR为满量程电压,N是ADC的分辨率),跳变值之间的间隔为精确的1LSB。

若DNL误差指标≤ 1LSB,就意味着传输函数具有保证的单调性,没有丢码。

当一个ADC的数字量输出随着模拟输入信号的增加而增加时(或保持不变),就称其具有单调性,相应传输函数曲线的斜率没有变号。

DNL指标是在消除了静态增益误差的影响后得到的。

具体定义如下:DNL = |[(V D+1- V D)/V LSB-IDEAL - 1] |,其中0 < D < 2N - 2V D是对应于数字输出代码D的输入模拟量,N是ADC分辨率,V LSB-IDEAL是两个相邻代码的理想间隔。

较高数值的DNL 增加了量化结果中的噪声和寄生成分,限制了ADC的性能,表现为有限的信号-噪声比指标(SNR)和无杂散动态范围指标(SFDR)。

基于Matlab的高速高精度ADC测试研究戴澜;姜岩峰;刘文楷【摘要】高速高精度模数转换器(ADC)一直是研究热点,相应地ADC的测试技术显得尤为重要;文章首先对ADC动静态参数进行研究,利用概率统计理论得到性能参数的数学表示;然后提出一种ADC动静态参数测试电路实现方案,利用上述性能参数的研究成果和提出的测试电路,对所设计的一种12位50MHz流水线ADC性能参数进行测试,并基于Matlab工具对测试数据进行分析,得到SFDR为65dB,ENOB为9.1位,SNR为56.9 dB,SNDR为56 dB,INL为I.8LSB,试验数据证明了测试方案的可行性.【期刊名称】《计算机测量与控制》【年(卷),期】2010(018)009【总页数】3页(P2044-2045,2049)【关键词】频谱分析;Matlab;动/静态参数;信噪比【作者】戴澜;姜岩峰;刘文楷【作者单位】北方工业大学信息学院微电子系,北京,100144;北方工业大学信息学院微电子系,北京,100144;北方工业大学信息学院微电子系,北京,100144【正文语种】中文【中图分类】TN7920 引言随着电子技术的发展,模数转换(ADC)在电子系统中显得尤为重要,对ADC的速度和精度要求也越来越高,高速高精度ADC的设计逐步成为研究热点,相应测试技术研究的也更加关注[1]。

论文对高速高精度ADC动静态参数测试方法进行研究:基于Matlab工具对ADC 静态参数、动态参数进行分析;提出高速高精度ADC测试方电路,并对12位50M Hz流水线ADC进行测试,给出测试结果。

1 静态性能测试积分非线性(INL)、差分非线性(DN L)、失调(O ffset)等参数是属于静态性能测试范畴。

静态性能参数采用码密度直方图来进行测试,码密度直方图测试是基于ADC对输入信号的采样是随机的,即对输入信号的同一电平不存在重复采样,然后通过对输出的不同代码的个数进行统计、计算每一个代码出现的概率,利用统计的概率和理想概率的对照,得到静态性能参数[2-3]。

12位高速AD转换器AD92260引言随着半导体技术、集成技术和计算机技术的飞速发展,数字技术已经渗入到科研、生产和生活的各个领域。

像数字仪器、数字通讯、数字电器和数字控制等以数字技术为基础的产品和系统层出不穷。

而对于自然界中广泛的以模拟信号为主的物理信号的数字技术处理,必然面临着模拟信号转换成数字信号的采集过程。

于是,在数字电路设计向着高速、超高速的方向发展的同时,与之相匹配的数据采集系统必须具有更高的采样速率,同时能提供更丰富的原始数据信息。

A/D转换器的基本原理:典型的A/D转换器一般包括前置滤波器、采样/保持电路、量化电路和编码电路。

前置滤波被称为抗混叠滤波,是为了防止高频信号混叠到A/D转换器的基带内。

混叠滤波通常是由A/D转换器本身的带宽限制特性来实现。

紧接着是采样/保持电路,这个电路在采样时钟的控制下对输入信号进行采样,使其成为时间离散信号;保持电路则在转换过程中保持采样值不变。

A/D转换器将采样到的模拟信号转换成相应的输出代码,这段时间被称为A/D转换器的转换时间。

转换通过量化步骤来完成。

量化和编码过程就是实际的转换过程,将时间离散的信号量转化为最接近的二进制码输出。

1概述AD9226是ADI公司生产的单片、单电源供电、12位精度、65Msps高速模数转换器,片内集成高性能的采样保持放大器(sample-and-hold amplifier SHA)和参考电压源。

AD9226采用带有误差校正逻辑的多级差分流水结构,以保证在65Msps采样率下获得精确的12位数据。

同时,AD9226还具有较低的功耗(475mw)和较高的信噪比(69dB)。

2主要特性2.1 引脚功能AD9226有28-Lead SSOP(28脚窄间距小外型塑封)和48-Lead LQFP(48脚薄型四方扁平封装)两种封装格式。

首先以28-Lead SSOP为例介绍,其引脚分布如图1所示:图1功能定义为:DRVDD为数字电源引脚,工作电压3V/5V。

ADC的分类比较及性能指标1 A/D转换器的分类与比较 (1)1.1 逐次比较式ADC (1)1.2 快闪式(Flash)ADC (2)1.3 折叠插值式(Folding&Interpolation)ADC (3)1.4 流水线式ADC (4)1.5 ∑-Δ型ADC (6)1.6 不同ADC结构性能比较 (6)2 ADC的性能指标 (7)2.1 静态特性指标 (7)2.2 动态特性指标 (11)1 A/D转换器的分类与比较A/D转换器(ADC)是模拟系统与数字系统接口的关键部件,长期以来一直被广泛应用于雷达、通信、电子对抗、声纳、卫星、导弹、测控系统、地震、医疗、仪器仪表、图像和音频等领域。

随着计算机和通信产业的迅猛发展,进一步推动了ADC在便携式设备上的应用并使其有了长足进步,ADC正逐步向高速、高精度和低功耗的方向发展。

通常,A/D转换器具有三个基本功能:采样、量化和编码。

如何实现这三个功能,决定了A/D转换器的电路结构和工作性能。

A/D转换器的分类很多,按采样频率可划分为奈奎斯特采样ADC和过采样ADC,奈奎斯特采样ADC又可划分为高速ADC、中速ADC和低速ADC;按性能划分为高速ADC和高精度ADC;按结构划分为串行ADC、并行ADC和串并行ADC。

在频率范围内还可以按电路结构细分为更多种类。

中低速ADC可分为积分型ADC、过采样Sigma-Delta型ADC、逐次逼近型ADC、Algonithmic ADC;高速ADC可以分为闪电式ADC、两步型ADC、流水线ADC、内插性ADC、折叠型ADC和时间交织型ADC。

下面主要介绍几种常用的、应用最广泛的ADC结构,它们是:逐次比较式(S A R)ADC、快闪式(F l a s h)ADC、折叠插入式(F o ld i n g&Interpolation)ADC、流水线式(Pipelined)ADC和∑-Δ型A/D转换器。

1.1 逐次比较式ADC图1 SAR ADC原理图图1是SAR ADC的原理框图。

高速ADC/DAC 测试原理及测试方法随着数字信号处理技术和数字电路工作速度的提高,随着数字信号处理技术和数字电路工作速度的提高,以及对于系统灵敏度等以及对于系统灵敏度等要求的不断提高,对于高速、高精度的ADC ADC、、DAC 的指标都提出了很高的要求。

比如在移动通信、图像采集等应用领域中,一方面要求ADC 有比较高的采样率以采集高带宽的输入信号,另一方面又要有比较高的位数以分辨细微的变化。

因此,保证ADC/DAC 在高速采样情况下的精度是一个很关键的问题。

ADC/DAC 芯片的性能测芯片的性能测试试是由芯片芯片生产厂家完成生产厂家完成生产厂家完成的,的,的,需需要借助昂贵借助昂贵的的半导体测试仪器试仪器,,但是对于是对于板级板级板级和系统和系统和系统级级的设计人员来说设计人员来说,,更重更重要的是如要的是如要的是如何验何验何验证芯片在证芯片在板级或板级或系统系统系统级级应用应用上上的真正真正性能指标。

性能指标。

一、ADC的主要参数ADC 的主要指标分要指标分为静态为静态为静态指标和动指标和动指标和动态态指标2大类大类。

静态静态指标指标指标主主要有要有::•Differential Non-Linearity (DNL)•Integral Non-Linearity (INL)•Offset Error•Full Scale Gain Error动态指标指标主主要有要有::•Total harmonic distortion (THD)•Signal-to-noise plus distortion (SINAD)•Effective Number of Bits (ENOB) •Signal-to-noise ratio (SNR) •Spurious free dynamic range (SFDR)二、ADC 的测试方案要进行ADC 这些众多这些众多指标的指标的指标的验验证,证,基本基本基本的方的方的方法法是给ADC 的输入的输入端端输入一个理想的信号,的信号,然后然后然后对对ADC 转换转换以以后的数的数据进行据进行据进行采集和分采集和分采集和分析析,因此,,因此,ADC ADC 的性能测的性能测试试需要多台仪器多台仪器的的配合并配合并用用软件软件对测对测对测试结果进行试结果进行试结果进行分分析。

ADC INL DNLADCLNA ADC ADC INL INL DNL DNLINL N 0 INL ADC 1ADC INL = [(VD-VZERO)/VLSB-IDEAL]-D 0 < D < 2N - 1INLDNL ADC VFSR ≤1LSBDNLLSB 1a DNL = 0LSB 1LSB 1LSB = VFSR/2N N ADC 1LSB DNL ADC DNLVDD V ZERO VLSB-IDEALNADCINLINL DNLDNLDACDUT PC X-Y DACDNL = [(VD+1 - VD)/VLSB-IDEAL - 1] 0 < D < 2N - 2 VD ADC D VLSB-IDEAL DNL ADC SNR N ADC ADC X-Y VDIFFADCDAC DAC V DIFF INL DNLSFDR INL LSBFSR INLINLADCINL (1b)13DIGITAL OUTPUT CODEDIGITAL OUTPUT CODE11111111 . . . . . . . . . . . . 00000110 00000011FULL-SCALE RANGE (FSR) IDEAL TRANSFER EXAMPLE: FUNCTION ADJACENT PHYSICAL VALUE VD+1 CORRESPONDS TO DIGITAL OUTPUT CODE D+1 EXAMPLE: PHYSICAL VALUE VD CORRESPONDS TO DIGITAL OUTPUT CODE D CODE WIDTH = 2LSB 0.5LSB11111111IDEAL SPACING BETWEEN TWO ADJACENT CODES VLSB - IDEAL = 1LSB REAL TRANSFER FUNCTION WITH ONE MISSING CODE. . . . . . . . . . . 00000111 00000110 00000101 00000100 00000011 00000010 00000001 00000000ACTUAL ADC TRANSFER FUNCTION BEFORE OFFSET AND GAIN CORRECTIONINL ERROR (BEST-STRAIGHT-LINE INL)ACTUAL ADC TRANSFER CURVE AFTER OFFSET AND GAIN CORRECTION INL ERROR (ENDPOINT INL) BEST-STRAIGHTLINE FIT IDEAL TRANSFER CURVE V OFFSET (LSB) ANALOG INPUT00000010 00000001 00000000IDEAL 50% TRANSITION POINT IDEAL CODE CENTER FIRST TRANSITION LAST TRANSITION ANALOG INPUT1a. ≤1LSBADCDNL1b.ADCADC50% 50%ADC1b ADC 2 ADC ADC PC 2N-1 N ADC MAX108 MAX108 P Q P > QOUT DVM INL/DNL 314dV/dt INL/DNL 4a , 4b INL S50% L SAR L DAC 5CDUTRAMP dV dt +=I CN-BIT ADCINTEGRATORNNN 2 -1 CODES UNDER TEST FROM PCPRECISION DVM CURRENT SOURCESCLOCKDIGITAL MAGNITUDE COMPARATORISINKSIGNAL LINES ‘>’ AND ‘<’ OF THE MAGNITUDE COMPARATOR DIRECTLY CONTROL THE CURRENT FLOW OF THE TWO CURRENT SOURCES.><2.1.5GHz, +4dBm HP8662/3A SINE-WAVE SOURCE EXTERNAL 50 TERMINATION TO GNDI CLKCLK+ +5V ANALOG VIN+ SERVO-LOOP CIRCUIT -5V ANALOG VIN-MAX108EVKIT+5V DIGITAL +3.3V DIGITALQOUTPPC 16 DATA HP16500C DATA ANALYSIS SYSTEM DREADY+ POWER SUPPLIESGPIB3.MAX108EVKITMAX10815INLDNLDAC DAC N ADC DAC ADC 16 1/8LSBDACINLDNLADC SNR SNR N 6.02 + 1.762M MSNRdB = N2M-1SNRSAR 16INL DNL TOC0.5 0.4 0.3 0.2INTEGRAL NONLINEARITY vs. DIGITAL OUTPUT CODE (LOW-FREQUENCY SERVO-LOOP DATA)0.5 0.4 0.3 0.2 DNL (LSB) 0.1 0 -0.1 -0.2 -0.3 -0.4 -0.5DIFFERENTIAL NONLINEARITY vs. DIGITAL OUTPUT CODE (LOW-FREQUENCY SERVO-LOOP DATA)INL (LSB)0.1 0 -0.1 -0.2 -0.3 -0.4 -0.5 0 32 64 96 128 160 192 224 256 DIGITAL OUTPUT CODE03264 96 128 160 192 224 DIGITAL OUTPUT CODE2564a.MAX108 ADCINL4b.MAX108 ADCDNL16SUCCESSIVE APPROXIMATION REGISTER SAR L END OF CONVERSION EOC DATAREAD L BACK AFTER END OF CONVERSION L-BIT DAC N-BIT ADCL>NN DIGITAL MAGNITUDE COMPARATOR NN 2 -1 CODES UNDER TEST FROM PCCLOCKCLOCK‘DATA’ COUNTER COUNTS WHEN ‘>’ OUTPUT OF THE MAGNITUDE COMPARATOR IS A ‘1’. DIVIDE-BY SR FLIP FLOP S Q R CLK RESET REFERENCE COUNTER COUNTS EVERY CLOCK PULSE DIGITAL AVERAGER RDIVIDE-BY 2M>2M-1RESET CLOCK 1 ‘1’5.DACSAR SAR SAR/DAC 1/2FSR 1/4FSR MSB LSB SAR N SARReferencesJohns, D., and K. Martin. 1997. Analog Integrated Circuit Design. Plasche, R. van de. 1994. Integrated Analog-toDigital and Digital-to-Analog Converters. Sanchez-Sinencio, E., and A. G. Andreou. 1999. Low-Voltage/Low-Power Integrated Circuits and Systems—Low-Voltage Mixed-Signal Circuits. MAX108 data sheet. Rev. 1, 5/99. Maxim Integrated Products. MAX108EVKIT data sheet. Rev. 0, 6/99. Maxim Integrated Products.1/4FSR N DAC17。

http://www.cicmag.com(总第238期)2019·3·图2微分非线性误差DNL图1理想器件1前言随着高速数字电路的发展,高速ADC 在航天国防、数字通信、卫星通信、图像处理等众多领域得到了非常广泛的应用。

ADC 的采样率和垂直分辨率越来越高,对ADC 指标的测试也提出了更高要求。

2测试参数2.1静态参数ADC 的测试指标和参数主要分为静态参数和动态参数两类。

其中静态参数又称线性参数,反映的是器件内部电路的误差。

对ADC 来说,这些内部误差包括器件的增益、偏移、微分非线性(DNL )和积分非线性(INL )误差,这些参数说明了静止的模拟信号转换成数字信号的情况,主要关注具体电平与相应数字编码之间的关系。

测试ADC 静态性能时,要考虑两个重要因素:第一,不仅要给一个既定的模拟电压,电压精度要高,还必须考虑模拟电压的范围以及代码间的转换特性;第二,静态测试是一个交互性过程,要在不同输入信号下测试实际输出。

静态测试的主要项目有:微分非线性误差、积分非线性误差、偏移与增益误差。

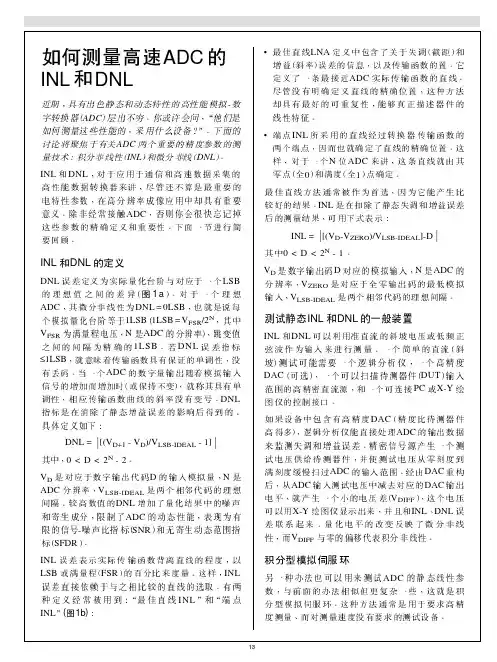

1.微分非线性误差(DNL ,Differential nonlin-earity )理想ADC 器件,相邻两个数据刻度之间,对应模拟电压的差值(步距)都是一样的。

但实际上,相邻两刻度之间的间距不可能都是相等的。

所以,ADC 相邻两刻度之间最大的差异与理想步距的差值,就叫微分非线性DNL ,也称为差分非线性,以LSB 为单位(LSB ,最低有效位,即理论上的最小可分辨模拟电压值,比如1.024V 基准电压,10bit 的ADC ,其LSB 为0.001V )。

理想器件,DNL 都应该为0LSB ,如图1。

而实际器件,如图2,DNL =(2.2-1)LSB =1.2LSB 。

高速高精度ADC 的测试方法孙承志(是德科技)69http://www.cicmag.com(总第238期)2019·3·图4频谱分析方法2.积分非线性误差(INL ,Integral nonlinearity )积分非线性表示了ADC 器件在所有的数值点上对应的模拟值和真实值之间误差最大的那一点的误差值,也就是输出数值偏离线性最大的距离。

ADC INL DNLADCLNA ADC ADC INL INL DNL DNLINL N 0 INL ADC 1ADC INL = [(VD-VZERO)/VLSB-IDEAL]-D 0 < D < 2N - 1INLDNL ADC VFSR ≤1LSBDNLLSB 1a DNL = 0LSB 1LSB 1LSB = VFSR/2N N ADC 1LSB DNL ADC DNLVDD V ZERO VLSB-IDEALNADCINLINL DNLDNLDACDUT PC X-Y DACDNL = [(VD+1 - VD)/VLSB-IDEAL - 1] 0 < D < 2N - 2 VD ADC D VLSB-IDEAL DNL ADC SNR N ADC ADC X-Y VDIFFADCDAC DAC V DIFF INL DNLSFDR INL LSBFSR INLINLADCINL (1b)13DIGITAL OUTPUT CODEDIGITAL OUTPUT CODE11111111 . . . . . . . . . . . . 00000110 00000011FULL-SCALE RANGE (FSR) IDEAL TRANSFER EXAMPLE: FUNCTION ADJACENT PHYSICAL VALUE VD+1 CORRESPONDS TO DIGITAL OUTPUT CODE D+1 EXAMPLE: PHYSICAL VALUE VD CORRESPONDS TO DIGITAL OUTPUT CODE D CODE WIDTH = 2LSB 0.5LSB11111111IDEAL SPACING BETWEEN TWO ADJACENT CODES VLSB - IDEAL = 1LSB REAL TRANSFER FUNCTION WITH ONE MISSING CODE. . . . . . . . . . . 00000111 00000110 00000101 00000100 00000011 00000010 00000001 00000000ACTUAL ADC TRANSFER FUNCTION BEFORE OFFSET AND GAIN CORRECTIONINL ERROR (BEST-STRAIGHT-LINE INL)ACTUAL ADC TRANSFER CURVE AFTER OFFSET AND GAIN CORRECTION INL ERROR (ENDPOINT INL) BEST-STRAIGHTLINE FIT IDEAL TRANSFER CURVE V OFFSET (LSB) ANALOG INPUT00000010 00000001 00000000IDEAL 50% TRANSITION POINT IDEAL CODE CENTER FIRST TRANSITION LAST TRANSITION ANALOG INPUT1a. ≤1LSBADCDNL1b.ADCADC50% 50%ADC1b ADC 2 ADC ADC PC 2N-1 N ADC MAX108 MAX108 P Q P > QOUT DVM INL/DNL 314dV/dt INL/DNL 4a , 4b INL S50% L SAR L DAC 5CDUTRAMP dV dt +=I CN-BIT ADCINTEGRATORNNN 2 -1 CODES UNDER TEST FROM PCPRECISION DVM CURRENT SOURCESCLOCKDIGITAL MAGNITUDE COMPARATORISINKSIGNAL LINES ‘>’ AND ‘<’ OF THE MAGNITUDE COMPARATOR DIRECTLY CONTROL THE CURRENT FLOW OF THE TWO CURRENT SOURCES.><2.1.5GHz, +4dBm HP8662/3A SINE-WAVE SOURCE EXTERNAL 50 TERMINATION TO GNDI CLKCLK+ +5V ANALOG VIN+ SERVO-LOOP CIRCUIT -5V ANALOG VIN-MAX108EVKIT+5V DIGITAL +3.3V DIGITALQOUTPPC 16 DATA HP16500C DATA ANALYSIS SYSTEM DREADY+ POWER SUPPLIESGPIB3.MAX108EVKITMAX10815INLDNLDAC DAC N ADC DAC ADC 16 1/8LSBDACINLDNLADC SNR SNR N 6.02 + 1.762M MSNRdB = N2M-1SNRSAR 16INL DNL TOC0.5 0.4 0.3 0.2INTEGRAL NONLINEARITY vs. DIGITAL OUTPUT CODE (LOW-FREQUENCY SERVO-LOOP DATA)0.5 0.4 0.3 0.2 DNL (LSB) 0.1 0 -0.1 -0.2 -0.3 -0.4 -0.5DIFFERENTIAL NONLINEARITY vs. DIGITAL OUTPUT CODE (LOW-FREQUENCY SERVO-LOOP DATA)INL (LSB)0.1 0 -0.1 -0.2 -0.3 -0.4 -0.5 0 32 64 96 128 160 192 224 256 DIGITAL OUTPUT CODE03264 96 128 160 192 224 DIGITAL OUTPUT CODE2564a.MAX108 ADCINL4b.MAX108 ADCDNL16SUCCESSIVE APPROXIMATION REGISTER SAR L END OF CONVERSION EOC DATAREAD L BACK AFTER END OF CONVERSION L-BIT DAC N-BIT ADCL>NN DIGITAL MAGNITUDE COMPARATOR NN 2 -1 CODES UNDER TEST FROM PCCLOCKCLOCK‘DATA’ COUNTER COUNTS WHEN ‘>’ OUTPUT OF THE MAGNITUDE COMPARATOR IS A ‘1’. DIVIDE-BY SR FLIP FLOP S Q R CLK RESET REFERENCE COUNTER COUNTS EVERY CLOCK PULSE DIGITAL AVERAGER RDIVIDE-BY 2M>2M-1RESET CLOCK 1 ‘1’5.DACSAR SAR SAR/DAC 1/2FSR 1/4FSR MSB LSB SAR N SARReferencesJohns, D., and K. Martin. 1997. Analog Integrated Circuit Design. Plasche, R. van de. 1994. Integrated Analog-toDigital and Digital-to-Analog Converters. Sanchez-Sinencio, E., and A. G. Andreou. 1999. Low-Voltage/Low-Power Integrated Circuits and Systems—Low-Voltage Mixed-Signal Circuits. MAX108 data sheet. Rev. 1, 5/99. Maxim Integrated Products. MAX108EVKIT data sheet. Rev. 0, 6/99. Maxim Integrated Products.1/4FSR N DAC17。

高速模数转换器(ADC)的INL/DNL测量摘要:尽管积分非线性和微分非线性不是高速、高动态性能数据转换器最重要的参数,但在高分辨率成像应用中却具有重要意义。

本文简要回顾了这两个参数的定义,并给出了两种不同但常用的测量高速模数转换器(ADC)的INL/DNL的方法。

近期,许多厂商推出了具有出色的静态和动态特性的高性能模数转换器(ADC)。

你或许会问,“他们是如何测量这些性能的,采用什么设备?”。

下面的讨论将聚焦于有关ADC两个重要的精度参数的测量技术:积分非线性(INL)和微分非线性(DNL)。

尽管INL和DNL对于应用在通信和高速数据采集系统的高性能数据转换器来讲不算是最重要的电气特性参数,但它们在高分辨率成像应用中却具有重要意义。

除非经常接触ADC,否则你会很容易忘记这些参数的确切定义和重要性。

因此,下一节给出了这些定义的简要回顾。

INL和DNL的定义DNL误差定义为实际量化台阶与对应于1LSB的理想值之间的差异(见图1a)。

对于一个理想ADC,其微分非线性为DNL = 0LSB,也就是说每个模拟量化台阶等于1LSB (1LSB = V FSR/2N,其中V FSR为满量程电压,N是ADC的分辨率),跳变值之间的间隔为精确的1LSB。

若DNL误差指标≤ 1LSB,就意味着传输函数具有保证的单调性,没有丢码。

当一个ADC的数字量输出随着模拟输入信号的增加而增加时(或保持不变),就称其具有单调性,相应传输函数曲线的斜率没有变号。

DNL指标是在消除了静态增益误差的影响后得到的。

具体定义如下:DNL = |[(V D+1- V D)/V LSB-IDEAL - 1] |,其中0 < D < 2N - 2V D是对应于数字输出代码D的输入模拟量,N是ADC分辨率,V LSB-IDEAL是两个相邻代码的理想间隔。

较高数值的DNL增加了量化结果中的噪声和寄生成分,限制了ADC的性能,表现为有限的信号-噪声比指标(SNR)和无杂散动态范围指标(SFDR)。

模数转换器的误差分析赵磊吴丽萍韩媛媛河北工业大学 (2006-05-3110:02)分类:技术版块现代测试系统和现代工业应用系统中,模数转换器(ADC)是不可或缺的元器件之一.由于ADC的广泛应用,一般数据采集系统都由传感器电路和ADC构成.但很多时候,数据采集系统所表现的性能往往低于预期值.出现这种情况,人们首先考虑的原因是传感器和信号调理电路的非线性以及被测试参数的稳定性和准确性.但实际上,ADC的性能指标也是数据采集系统性能下降的重要原因.本文的目的是以MAXIM公司生产14位,8通道,同步采样ADC转换器MAX1324为例,解释最常见的误差源,并介绍进行上述误差补偿的方法.某些误差补偿的方法理解和实施起来都比较容易,而有些方法则不那么显浅易懂.如果采用方法得当的话,可大幅提高系统的整体性能.一、系统误差性能分析数据采集系统的误差是信号通道上的每个元器件所贡献的误差项的总和.因此总误差的均方根可由下式给出: .其中,E 代表某个特定元器件的误差项.作为具体分析,假定数据采集系统允许0.1%的误差或者说需要l0位的精度.在这种情况下,如果采用l0位分辨率的ADC显然是不合要求的.如果采用l2位的转换器,我们可能会想当然地认为精度已经足够高,但是在没有仔细检查其规格说明书之前,我们并不能保证该转换器就具有l2位的性能(实际情况可能更好或者更糟).例如,一个具有±4LSB积分非线性误差(INL)的l2位ADC,在其他误差都修正的情况下,只能提供10位的精度,或者说提供0.1的精度,而一个具有0.5LSB INL的器件则可以提供0.0122的误差或者13位的精度.在我们假定的数据采集系统中,若ADC 允许0.075的误差(或ll位精度),而留给其他电路的误差余量为0.025,这其中包括传感电路、前端信号调理电路(运放、多路复用器等等),或许还有DAC、PWM 及其他模拟电路.二、ADC直流性能分析模数转换器的直流性能包括微分非线性、积分非线性、失调和增益误差以及其他误差.模数转换器一般以LSB为单位提供各种误差.其相应关系可以表示为:ERR =LSB/2n.其中,n为模数转换器的转换位数,LSB为以LSB为单位的最大误差,ERR为以百分号为单位的误差.1.微分非线性微分非线性(DNL)误差揭示的是一个输出码与其相邻码之间的间隔.这个间隔通过测量输入电压的幅度变化,然后转换成以LSB为单位后得到.当输入电压扫过ADC的工作范围时,所有输出码组合(全“0”到全“1”)会依次出现在转换器的输出端.这种关系称作“无丢码”.但实际上由于器件的微分非线性,常常出现以下几种情况.当DNL误差小于±1LSB时,不会出现丢码的现象,如图1(-0.5LSB无丢码);当DNL误差等于±1LSB时,生产厂商会特别声明是否丢码(如图1:1LSB无丢码,图2:-1LSB丢10码);当DNL误差大于±1LSB时有丢码(如图3:当VIN =V0时,可能为01,l0,ll码).微分非线性(DNL)误差与丢码之间的关系如表1.而MAX1324的DNL误差为±1LSB,声明为无丢码,所以具有14位精度.在一定条件下可以允许丢码的存在.因为一般说来,同系列产品在性能条件不同时价格相差较大,在满足性能要求的前提下,选购低等级的ADC将大幅度节省元件成本,同时又满足系统要求.2.积分非线性积分非线性(INL)定义为微分非线性(DNL)误差的积分.在实际分析ADC精度时,一般采用INL误差.INL误差定义为转换器测量结果与理想转换函数的差.其相应关系可以表示为:ERR=LSB/2n.积分非线性(INL)误差各种表示之间的关系如表2.而MAX1324的INL误差为±1.5LSB,声明为无丢码(14位精度),则它的分辨率误差是:ERR=LSB/214=1.5/214=0.0091552%.3.失调和增益误差失调误差也称为零漂,是指系统在0V输入电压时或其附近时ADC产生的漂移.对于失调误差的修正,可以比较容易利用微控制器(μC)或数字信号处理器(DSP)进行修正.如果转换器允许双极性输入信号,操作将非常简单.对于双极性系统,失调误差只是平移了转换函数,但并没有减少可用编码的数量(如图4所示).双极性系统失调误差的修正有两种方法.一种方法是可以简单地平移X轴和Y轴,使负满度点(FS1-+OFFSET)与单极性的零点相对应,就能简单地消除失调误差.另一种方法是采用迭代法,首先给ADC输入施加一个0V电压并执行一次转换,转换结果反应了双极性零点失调误差,然后确定负满度点,并围绕它进行调节增益误差,如此反复进行直到零漂修正完毕.我们以MAX1324为例说明失调误差与输入电压的关系.MAX1324的失调误差为±3LSB,相当于±0.9155mV的输入电压误差(以5V为基准作参考电压),在进行失调误差修正时必须于扣除3个码以补偿失调电压,而在失调误差为+3LSB时满量程电压值就变成了4.0845V,超过上述电压值就会产生溢出现象;在失调误差为-3LSB时,假设对于单极性输入,在0~0.9155mV之间,输出均为零,直到0.9155mV 时才出现第一次跳变,这同样使ADC动态范围变小了.增益误差定义为满度量程误差减去失调误差.满度误差在转换函数曲线上最后一次ADC跳变处进行测量,并和理想ADC转换函数进行比较.继续以MAX1324为例说明增益误差的含义.MAX1324的增益误差为±4LSB,那么在5V参考电压的条件下其相应的电压误差4.9988V和5.0012V,这两种情况都使系统性能受到影响.对-4LSB,高端的4个码无效;对于+4LSB,输入电压的动态范围低了.总之,对于失调误差和增益误差可以通过软件实现误差的修正.4.温漂温漂在数据采集系统中是一个相当重要的指标,但往往被忽略.在工业应用中,由于环境温度的变化,系统温漂可能会严重影响系统精度.对有些系统来讲,参考电压的精度不是个大问题,因为温度被保持恒定,避免了温度偏移的影响.还有一些系统采用一种比例测量法,用同一信号源激励传感器和参考电压,可以消除基准引起的误差,因为激励源和基准同时漂移,漂移误差相互抵消.也有系统用补偿手段消除基准漂移.5.基准无论是内部基准或者外部基准,它都是ADC的一个最大的潜在误差源.在很多情况下内置于芯片内部的基准源都没有严格的规格,而外部基准往往需要精密电源,与基准有关的误差源包括温漂、电压噪声以及负载调整等.在实用的ADC系统中,还有一些误差源,如码源噪声、失调温漂、增益漂移,它们在某种条件下,可能会对系统精度产生影响,但只要采用适当的手段就可以使相应误差最小,进而不会影响系统精度.三、交流特性在实际数据采集系统中,很多情况下输入模拟信号是交流信号.仅有DNL和INL符合系统要求并不能说明ADC能同样合格地处理交流信号.因为DNL和INL是在直流条件下测试的.ADC系统中的交流信号指标差要有信一噪比(SNR)、信号-噪声加失真比(SINAD)、总谐波失真(THD)以及无杂散动态范围(SFDR).在ADC系统中,SINAD比SNR更准确描述被测信号与杂散信号的关系,大多数ADC列出SINAD 而不采用SNR.对于一个理想的ADC:SINAD=(6.02×N+1.76)dB其中N为转换器的位数.所以理想的l2为转换器,SINAD为74dB.而对上式进行变换可得:N=(SINAD-1.76)/6.02这个方程式为等效位数的定义,即ENOB.在实际应用时我们关注SINAD为最小值时的等效位数,该位数是信号频率逐渐逼近Nyquist上限时,SINAD因THD的增加而达到的极限值.以MAX1324为例,其极限值为70dB,等效位数为14位,即有0.7LSB的误差或0.017的精度.四、应用分析假设我们的系统允许0.1%的误差,且ADC允许0.075%的误差,并且假设我们需要测试的直流信号.如果我们选用MAX1324,其具有±1LSB的DNL误差,±1.5LSB的INL误差(0.0366%),±3LSB的失调误差(0.0732%),±4LSB的增益误差(0.0977%),5ppm/℃的温漂系数,在50℃的范围内产生0.025%的误差,共计0.0616%的误差.还有0.0134%的误差供基准电压源使用,该误差允许存在67μV 的峰-峰值电压噪声(5V基准电压),若考虑负载(ADC)电流对基准的影响,其电压噪声会略小.在这种情况下,基准电压源可以满足上述条件,而且也有比较多的选择余地.以上例子我们没有讨论交流性能.若在实际数据采集系统中交流信号是被测信号,还必须考虑交流信号的误差,并作进一步的分析.五、结束语一个性能良好的数据采集系统不仅仅是设计原理的优化及其实现方法,系统的误差分析是设计成本和性能指标的必要前提条件.只有充分考虑系统各部分的误差才能使系统更好地满足设计性能要求.。

高速ADC/DAC的测试方法演讲内容大家好,我是今天做分享的任彦楠,非常荣幸能和大家交流,今天我分享的内容是within 我的knowledge, 也希望将我不懂的地方向大家请教。

今天我要和大家分享的是高速ADC/DAC的测试方法~ADC主要的测试指标分为静态指标和动态指标两类:静态指标,包括INL、DNL;动态指标,主要是基于SFDR,在此基础之上计算的ENOB(有效位数)。

尽量言简意赅吧。

ADC的测试方法,其实简单来说,就是输入和输出,输入怎么给?输出怎么测?怎么计算?以及换算到spec。

输入主要是两部分:数据和clk。

大家知道ADC的数据和clk都用什么给信号吗?听众答:ADC的数据是指输入的模拟信号吗?任老师:哈哈,是的,信号发生器;然而对于ADC,尤其是高精度的ADC,最关键的是信号源的选择,这里需要的是高精度的信号源,也就是说信号源的动态范围要高于被测ADC两个精度位以上,这是关键之一。

第二,就是信号源和clk的同步。

接着,我们来看输出,ADC输出的是digital信号,也就是说输出采样到的是数字信号。

但是ADC的动态参数表示都是基于频谱分析的方法。

也就是说要将输出、采样到的数字信号用FFT变换到频域,这就是大家看到ADC的测试程序为什么主函数是FFT 函数的原因。

我记得我们当时实验室测得,10bit以上ADC,都至少是1024点。

听众问:或者转到频域,频率精度到什么精度才合适?任老师:实测的时候,你有时会发现,FFT点数选的少,测试结果会好,不知大家有没有碰到过这种情况?嗯,但其实这是一种假象。

你想10bit ADC输出的全位分辨率就是1024,如果没有采到1024个点,说明丢失了部分数据,不能真实反映ADC的性能。

所以大家测。

高速模数转换器(ADC)的INL/DNL测量摘要:尽管积分非线性和微分非线性不是高速、高动态性能数据转换器最重要的参数,但在高分辨率成像应用中却具有重要意义。

本文简要回顾了这两个参数的定义,并给出了两种不同但常用的测量高速模数转换器(ADC)的INL/DNL的方法。

近期,许多厂商推出了具有出色的静态和动态特性的高性能模数转换器(ADC)。

你或许会问,“他们是如何测量这些性能的,采用什么设备?”。

下面的讨论将聚焦于有关ADC两个重要的精度参数的测量技术:积分非线性(INL)和微分非线性(DNL)。

尽管INL和DNL对于应用在通信和高速数据采集系统的高性能数据转换器来讲不算是最重要的电气特性参数,但它们在高分辨率成像应用中却具有重要意义。

除非经常接触ADC,否则你会很容易忘记这些参数的确切定义和重要性。

因此,下一节给出了这些定义的简要回顾。

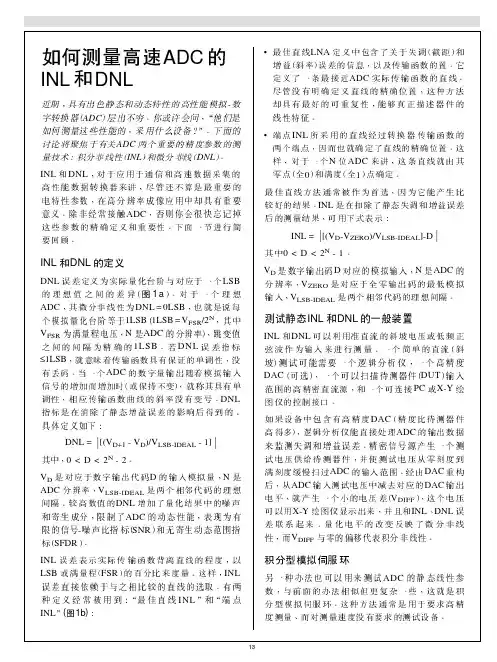

INL和DNL的定义DNL误差定义为实际量化台阶与对应于1LSB的理想值之间的差异(见图1a)。

对于一个理想ADC,其微分非线性为DNL = 0LSB,也就是说每个模拟量化台阶等于1LSB (1LSB = V FSR/2N,其中V FSR为满量程电压,N是ADC的分辨率),跳变值之间的间隔为精确的1LSB。

若DNL误差指标≤ 1LSB,就意味着传输函数具有保证的单调性,没有丢码。

当一个ADC的数字量输出随着模拟输入信号的增加而增加时(或保持不变),就称其具有单调性,相应传输函数曲线的斜率没有变号。

DNL指标是在消除了静态增益误差的影响后得到的。

具体定义如下:DNL = |[(V D+1- V D)/V LSB-IDEAL - 1] |,其中0 < D < 2N - 2V D是对应于数字输出代码D的输入模拟量,N是ADC分辨率,V LSB-IDEAL是两个相邻代码的理想间隔。

较高数值的DNL增加了量化结果中的噪声和寄生成分,限制了ADC的性能,表现为有限的信号-噪声比指标(SNR)和无杂散动态范围指标(SFDR)。

图1a. 要保证没有丢码和单调的转移函数,ADC的DNL必须小于1LSB。

INL误差表示实际传输函数背离直线的程度,以LSB或满量程的百分比(FSR)来度量。

这样,INL 误差直接依赖于与之相比较的直线的选取。

至少有两个定义是常用的:“最佳直线INL”和“端点INL” (见图1b):∙最佳直线INL定义中包含了关于失调(截距)和增益(斜率)误差的信息,以及传输函数的位置(在后面讨论)。

它定义了一条最接近ADC实际传输函数的直线。

没有明确定义直线的精确位置,但这种方法却具有最好的可重复性,能够真正描述器件的线性特征。

∙端点INL所采用的直线经过转换器传输函数的两个端点,因而也就确定了直线的精确位置。

这样,对于一个N位ADC来讲,这条直线就由其零点(全0)和其满度(全1)点确定。

最佳直线方法通常被作为首选,因为它能产生比较好的结果。

INL是在扣除了静态失调和增益误差后的测量结果,可用下式表示:INL = | [(V D - V ZERO)/V LSB-IDEAL] - D |,其中0 < D < 2N-1V D是数字输出码D对应的模拟输入,N是ADC的分辨率,V ZERO是对应于全零输出码的最低模拟输入,V LSB-IDEAL是两个相邻代码的理想间隔。

图1b. 最佳直线法和端点法是定义ADC线性特性的两种可行办法转移函数理想ADC的转移函数是阶梯状的,其中每一个台阶对应于某个特定的数字输出代码,而每一次阶跃代表两个相邻代码间的转变。

必须确定这些阶跃所对应的输入电压,以便对ADC的许多特性参数进行规范。

这项任务会极为复杂,尤其是对于高速转换器中充满噪声的过渡状态,以及那些接近于最终结果、并变化缓慢的数字量。

过渡状态没有在图1b中显著标出,而是作为一种概率函数表达,更为接近实际。

当慢慢增加的输入电压经过过渡点时,ADC将一个接一个地输出相邻代码。

按照定义,在过渡点对应的输入电压下,ADC输出相邻两个代码的几率相等。

正确的过渡过渡电压是指输出数码在两个相邻代码间发生跳变时输入电压。

名义模拟值,对应于两个相邻过渡电压之间的某输入电压所产生的数字输出码,定义为此范围的中点(50%点)。

如果过渡间隔的边界已知,该50%点很容易算出。

过渡点的确定可以通过测量某一个区间,然后将该区间除以其间出现过的相邻代码的次数后得到。

测试静态INL和DNL的一般装置INL和DNL可以利用准直流的斜坡电压或低频正弦波作为输入来进行测量。

一个简单的直流(斜坡)测试可能需要一个逻辑分析仪,一个高精度DAC (可选),一个可以扫描待测器件(DUT)输入范围的高精密直流源,和一个可连接PC或X-Y绘图仪的控制接口。

如果设备中包含有高精度DAC (精度比待测器件高得多),逻辑分析仪能直接处理ADC的输出数据来监测失调和增益误差。

精密信号源产生一个测试电压供给待测器件,并使测试电压从零刻度到满刻度缓慢扫过ADC的输入范围。

经由DAC重构后,从ADC输入测试电压中减去对应的DAC输出电平,就产生一个小的电压差(V DIFF),这个电压可以用X-Y绘图仪显示出来,并且和INL、DNL误差联系起来。

量化电平的改变反映了微分非线性,而V DIFF与零的偏移代表积分非线性。

积分型模拟伺服环另一种办法也可以用来测试ADC的静态线性参数,与前面的办法相似但更复杂一些,这就是使用积分型模拟伺服环。

这种方法通常是用于要求高精度测量、而对测量速度没有要求的测试设备。

典型的模拟伺服环(见图2)包含一个积分器和两个电流源,连接于ADC输入端。

其中一个电流源向积分器注入电流,另一个则吸出电流。

数值比较器连接于ADC输出并对两个电流源进行控制。

数值比较器的另一输入由PC控制,后者可以对N位转换器的2N - 1个测试码进行扫描。

图2. 模拟积分伺服环的电路配置如果环路反馈的极性正确的话,数值比较器就会驱使电流源“伺服”模拟输入跟随给定的代码跳变。

理想情况下,这将在模拟输入端产生一个小的三角波。

数值比较器控制斜坡信号的方向和速度。

在跟随一次跳变时积分器的斜率必须快,而在采用精密数字电压表(DVM)进行测量时,为了降低叠加的三角波过冲峰值,又要求积分器足够慢。

在MAX108的INL/DNL测试中,伺服板通过两个连接器连接到评估板(见图3)。

第一个连接器建立起MAX108的主(或副)输出端口和数值比较器的锁存输入口(P)的连接。

第二个连接器将伺服环(数值比较器的Q端口)和用于生成参照码的计算机连接起来。

图3. 借助MAX108EVKIT和模拟积分伺服环,该测试装置可以确定MAX108的INL和DNL特性。

数值比较器的判决结果解码后通过P > QOUT输出端输出并送往积分器单元。

每一次的比较结果都独立地控制开关的逻辑输入,驱动积分电路产生出满足需要的斜坡电压,供给待测器件的两路输入。

这种方法具有其优越性,但也有一些不足之处:∙为了降低噪声,三角斜坡应该具有低的dV/dt。

这有利于产生可重复的数码,但要获得精确测量它需要很长的积分时间。

∙正、负斜坡的斜率必须匹配方可达到50%点,并且必须对低电平三角波取平均后才可获得所需要的直流电平。

∙在设计积分器时常常要求仔细选择充电电容。

为了尽量减小由于电容的“存储效应”而造成的潜在误差,应选择具有低介质吸收的积分电容。

∙测量精度正比于积分时间而反比于建立时间。

将一个数字电压表连接到模拟积分伺服环中,就可测出INL/DNL误差与输出量的关系(图4a和图4b)。

值得注意的是,INL与输出码关系曲线中的抛物线形或弓形曲线表明偶次谐波占主导地位,若曲线呈“S状”,则说明奇次谐波占主导地位。

图4a. 该曲线给出了MAX108 ADC的典型积分非线性特性,由模拟积分伺服环测得。

图4b. 该曲线给出了MAX108 ADC的典型微分非线性特性,由模拟积分伺服环测得。

为了消除上述方法的缺陷,可以对伺服环中的积分单元加以改进,代之以一个L位的逐次逼近寄存器(SAR) (用于捕获待测器件的输出码)、一个L位DAC、以及一个简单的平均值电路。

再结合一个数值比较器,该电路就组成了一个逐次逼近型转换器结构(见图5和后续的“SAR转换器”部分),其中,由数值比较器对DAC进行控制、读取其输出、并完成逐次逼近。

同时,DAC 提供一个高分辨率的直流电平给被测N位ADC的输入。

在这个实例中,采用一个16位DAC将ADC校准至1/8LSB精度,同时获得最可信转移曲线。

图5. 用逐次逼近寄存器和DAC结构取代模拟伺服环中的积分器单元当接近终值时,由于受到噪声的影响,数值比较器会来回跳动而变得不稳定,此时,平均值电路的优势就突显出来了。

平均值电路包含两个除法计数器。

“参考”计数器具有2M个时钟的周期,其中M是一个可编程的整数,用来控制计数周期(同时也决定了测量时间)。

“数据”计数器仅在数值比较器输出为高时递增,其周期等于前者的一半,即2M-1个时钟。

参考计数器和数据计数器共同工作的效果是对高、低电平的数量进行了平均,结果被保存于一个触发器,并进而传送到SAR寄存器。

这个过程重复16次(在本例中)后便产生了完整的输出码。

和前面的方法一样,它也有优点和不足之处:∙测试装置的输入电压由数字量定义,这样可以简便地修改求取平均值的测式样点。

∙逐次逼近方式提供给待测器件模拟输入的是一个直流电平,而非斜坡电压。

∙不足之处在于,反馈环中的DAC限制了输入电压的分辨率。

SAR转换器SAR转换器的工作类似于旧时药剂师的天平。

一边是未知的输入采样,另一边是由SAR/DAC 结构产生的首个砝码(最高有效位,等于满量程输出的一半)。

如果未知重量大于1/2FSR,则保留首个砝码并再增加1/4FSR。

否则,用1/4FSR砝码代之。

将这个步骤重复N次,从MSB到LSB,SAR转换器就可得到所需要的输出代码。

N是SAR结构中DAC的分辨率,每个砝码代表1个二进位。

INL和DNL的动态测试要测定ADC的动态非线性,可以对其施加一个满度正弦输入,然后在其全功率输入带宽内测量转换器的信噪比(SNR)。

对于一个理想的N位转换器,理论SNR (仅考虑量化噪声,无失真)如下:SNR (单位为dB) = N×6.02 +1.76这个公式包含了瞬变、积分非线性和采样时间的不确定性等效应的影响。

除此之外的非线性成分可以通过测量恒频输入时的SNR来获得,并可得到一个随输入信号幅度的变化关系。

例如,使信号幅度扫过整个输入范围,从零到满量程或者反之,当输入幅度逼近转换器满量程时,转换输出将与信号源发生较大偏移。

要确定产生这种偏移,排除失真和时钟不稳定性因素的原因,可采用频谱分析仪分析量化噪声与频率的关系。