异步串行接口

- 格式:doc

- 大小:30.50 KB

- 文档页数:3

ASI异步串行口,SDI、TS、ASI、DS3码流的区别就是传输流数据信号的一种接口类型有三种:即同步并行接口(SPI) 改:SPI全称是"Serial Peripheral Interface",意为串行外围接口,不是什么同步并行接口,是串行的.、异步串行接口(ASI)和同步串行接口(SSI)。

其中,ASI和SPI接口较常用。

ASI接口的数据传输速率为270Mb/s,在进行码率调整之前,需要将ASI接口中的同步字节删除,进行串并转换,再进一步处理。

SPI接口传输数据率可变,帧与帧之间必须是连续的。

ASI接口卡的主要功能是将MPEG-2的传送流数据用DVB-ASI或SPI接口以恒定码率传送出去。

传送流数据可以是编码器、复用器或者别的传送流产生器产生并通过计算机的PCI总线按批传送至该传送卡。

传送卡先将数据缓存,然后根据用户所要求的输出码率将数据输出。

传送码率可在用户控制界面上预先设定,要求该码率与数据输入速率保持一致。

可应用于图像传输系统、数据传输系统、监控系统、电视会议系统、机顶盒前端等。

我们在使用编解码、复用、适配设备时常常会接触到TS流、SDI、ASI、SD3接口,它们的说明书也常常把ASI称作TS流,它们之间有什么不同呢?我们知道模拟信号(也叫连续信号)经过抽样、量化后变成在时间和幅度上都不连续的信号(也叫离散信号),这样的信号还不是数字信号,需要把离散信号转换成数字符号(如自然二进制码),这种码流是没有经过编码压缩的基带信号,码率较大,占用较大的传输带宽,这种码流的传输接口是SDI接口,也叫串行数字接口,码率是270 M,它属于信道码流,有些厂家的编码器除了复合视频输入端口还有SDI输入端口。

TS流是信源码流,最高码率为44.209 Mbit/s,它是经过信源编码后的压缩码流,为了使欲传输的信源信息在传输速率一定的条件下更快更多地传输,还要把数据进行压缩,也就是通过信源编码去掉信息中多余的部分,从而提高通信的有效性,信源编码包括霍夫曼编码、LZ编码等多种SDI 是Serial Digital Interface 的缩写,也就是串行数字接口串行接口是把数据字的各个比特以及相应的数据通过单一通道顺序传送的接口。

第4章异步串行通信本章导读:目前几乎所有的台式电脑都带有9芯的异步串行通信口,简称串行口或COM 口.由于历史的原因,通常所说的串行通信就是指异步串行通信。

USB、以太网等也用串行方式通信,但与这里所说的异步串行通信物理机制不同。

有的台式电脑带有两个串行口: COM1 口和COM2 口,部分笔记本电脑也带有串行口。

随着 USB接口的普及,串行口的地位逐渐降低,但是作为设备间简便的通信方式,在相当长的时间内,串行口还不会消失,在市场上也可很容易购买到USB到串行口的转接器因为简单且常用的串行通信只需要三根线(发送线、接收线和地线),所以串行通信仍然是MCU与外界通信的简便方式之一。

实现异步串行通信功能的模块在一部分MCU中被称为通用异步收发器(Universal Asynch¬ronous Receiver/Transmitters, UART ),在另一些 MCU 中被称为串行通信接口( Serial Communication Interface, SCI)。

串行通信接口可以将终端或个人计算机连接到MCU,也可将几个分散的 MCU连接成通信网络,本章的主要知识点有①阐述了串口相关的基础知识;②描述了K60串口糢块的功能概要;③介绍了串口模块驱动构件编程时涉及的相关寄存器;④设计并封装了串行通信的驱动构件;⑤给出第一个中断例程的执行过程和设计流程。

本章介绍的K60UART模块的工作原理以及编程实例,这些编程实例都使用了基于构件的编程思想,读者在阅读时可以仔细体会,以求得对编程方法有更深刻的理解本章所出现的UART 字眼,在没有其他说明的情况下,都是特指K60的UART模块,本章串口驱动编程涉及的寄存器全部给出其详细介绍,目的是让读者对嵌入式底层驱动编程设计的寄存器有个直观的了解,以后各章节将不再给出相关寄存器的详细介绍。

4.1异步串行通信的基础知识本节简要概括了串行通信中常用的基本概念,为学习MCU的串行接口编程做准备。

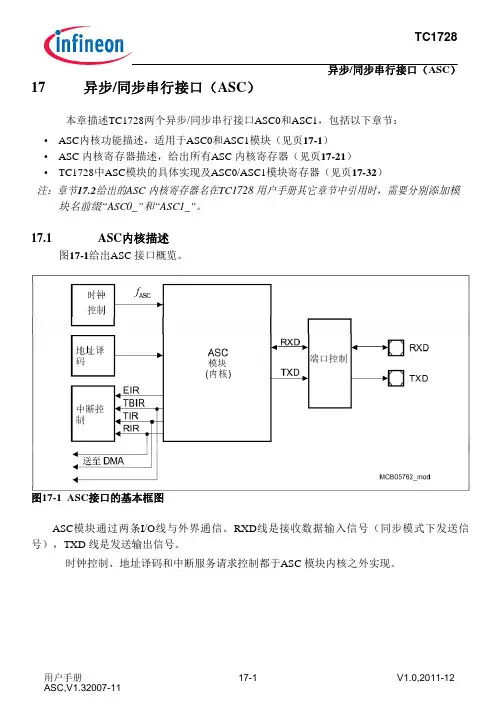

17异步/同步串行接口(ASC)本章描述TC1728两个异步/同步串行接口ASC0和ASC1,包括以下章节:•ASC内核功能描述,适用于ASC0和ASC1模块(见页17-1)•ASC内核寄存器描述,给出所有ASC内核寄存器(见页17-21)•TC1728中ASC模块的具体实现及ASC0/ASC1模块寄存器(见页17-32)注:章节17.2给出的ASC内核寄存器名在TC1728用户手册其它章节中引用时,需要分别添加模块名前缀“ASC0_”和“ASC1_”。

17.1ASC内核描述图17-1给出ASC接口概览。

图17-1ASC接口的基本框图ASC模块通过两条I/O线与外界通信。

RXD线是接收数据输入信号(同步模式下发送信号),TXD线是发送输出信号。

时钟控制、地址译码和中断服务请求控制都于ASC模块内核之外实现。

17.1.1概述ASC支持TC1728和其它微控制器、微处理器或外部外设进行串行通信。

ASC支持全双工异步通信和半双工同步通信。

同步模式下,数据的发送或接收与ASC 产生的移位时钟同步。

异步模式下,数据传送的宽度(8位或9位)、奇偶校验的产生、以及停止位的个数均可编程设定。

为了提高数据传送的可靠性,ASC模块提供了多种硬件错误检测功能,如奇偶校验错误、帧错误以及溢出错误检测。

数据发送/接收双缓存。

进行多处理器通信时,采用数据字节和地址字节区分机制。

可选择回环模式用于测试用途。

13位波特率发生器为ASC提供独立的串行时钟信号,该时钟信号可通过预分频器(用分数分频器实现)进行精确调整。

特性•全双工异步工作模式–8位或9位数据帧,LSB在先–奇偶校验位产生/检查–1个或2个停止位–波特率范围6.875Mbit/s-1.64bit/s(@110MHz模块时钟)–具有地址/数据字节自动检测功能的多处理器通信模式–回环功能•半双工8位同步工作模式–波特率范围13.75Mbit/s-1119bit/s(@110MHz模块时钟)•发送/接收双缓存•中断产生–在发送缓存为空的情况下–在发送一帧中的最后一位的情况下–在接收缓存已满的情况下–在产生错误的情况下(帧错误、奇偶校验错误、溢出错误)•实现特性–到DMA控制器的连接–用于波特率检测和LIN断开信号测量的GPTA(LTC)接收器输入的连接17.1.2一般操作ASC支持波特率高达MB/s的全双工异步通信和波特率高达MB/s的半双工同步通信(@MHz模块时钟)。

SPI:高速同步串行口。

3~4线接口,收发独立、可同步进行UART:通用异步串行口。

按照标准波特率完成双向通讯,速度慢I2C:一种串行传输方式,三线制,网上可找到其通信协议和用法的3根线实现数据双向传输串行外围接口 Serial peripheral interfaceUART:通用异步收发器UART是用于控制计算机与串行设备的芯片。

有一点要注意的是,它提供了RS-232C数据终端设备接口,这样计算机就可以和调制解调器或其它使用RS-232C接口的串行设备通信了。

作为接口的一部分,UART还提供以下功能:将由计算机内部传送过来的并行数据转换为输出的串行数据流。

将计算机外部来的串行数据转换为字节,供计算机内部使用并行数据的器件使用。

在输出的串行数据流中加入奇偶校验位,并对从外部接收的数据流进行奇偶校验。

在输出数据流中加入启停标记,并从接收数据流中删除启停标记。

处理由键盘或鼠标发出的中断信号(键盘和鼠票也是串行设备)。

可以处理计算机与外部串行设备的同步管理问题。

有一些比较高档的UART还提供输入输出数据的缓冲区,现在比较新的UART 是16550,它可以在计算机需要处理数据前在其缓冲区内存储16字节数据,而通常的UART是8250。

现在如果您购买一个内置的调制解调器,此调制解调器内部通常就会有16550 UART。

I2C:能用于替代标准的并行总线,能连接的各种集成电路和功能模块。

I2C是多主控总线,所以任何一个设备都能像主控器一样工作,并控制总线。

总线上每一个设备都有一个独一无二的地址,根据设备它们自己的能力,它们可以作为发射器或接收器工作。

多路微控制器能在同一个I2C总线上共存。

更详细的区别:第一个区别当然是名字:SPI(Serial Peripheral Interface:串行外设接口);I2C(INTER IC BUS:意为IC之间总线)UART(Universal Asynchronous Receiver Transmitter:通用异步收发器)第二,区别在电气信号线上:SPI总线由三条信号线组成:串行时钟(SCLK)、串行数据输出(SDO)、串行数据输入(SDI)。

数据通信的几个术语:并行:数据各位同时进行传送串行:数据逐位顺序进行传送全双工:(串行通信)收/发可同时进行半双工:(串行通信)收/发不可同时进行异步串行通信:以字符为单位进行传送同步串行通信:以数据块为单位进行传送波特率(bps.):1.UARTUART(Universal Asynchronous Receiver and Transmitter)通用异步收发器(异步串行通信口),是一种通用的数据通信协议,它包括了RS232、RS499、RS423、RS422和RS485等接口标准规范和总线标准规范,即UART 是异步串行通信口的总称。

而RS232、RS499、RS423、RS422和RS485等,是对应各种异步串行通信口的接口标准和总线标准,它规定了通信口的电气特性、传输速率、连接特性和接口的机械特性等内容,这些东东都是物理层的概念。

通信协议,是属于通信网络中的数据链路层的概念。

1.2 UART通信协议UART使用的是异步,串行通信。

串行通信是指利用一条传输线将资料一位位地顺序传送。

特点是通信线路简单,利用简单的线缆就可实现通信,降低成本,适用于远距离通信,但传输速度慢的应用场合。

异步通信以一个字符为传输单位,通信中两个字符间的时间间隔多少是不固定的,然而在同一个字符中的两个相邻位间的时间间隔是固定的。

数据传送速率用波特率来表示,即每秒钟传送的二进制位数。

例如数据传送速率为120字符/秒,而每一个字符为10位(1个起始位,7个数据位,1个校验位,1个结束位),则其传送的波特率为10×120=1200字符/秒=1200波特。

数据通信格式如下图:其中各位的意义如下:起始位:先发出一个逻辑”0”信号,表示传输字符的开始。

数据位:可以是5~8位逻辑”0”或”1”。

如ASCII码(7位),扩展BCD码(8位)。

小端传输校验位:数据位加上这一位后,使得“1”的位数应为偶数(偶校验)或奇数(奇校验)停止位:它是一个字符数据的结束标志。

异步串行接口(ASI) 、串行数字接口(S DI)、同步并行接口(SPI)两种完全不同的接口都简称为S PI,一种是"Serial P eriphe ral Interfa ce",意为串行外围接口,另一种是“Synchro nous Paralle l Interfa ce”,意为同步并行接口。

本文的SPI指后者。

SDI标准由S MPTE进行定义,广泛应用在广播和视频产品中。

SDI标准描述了怎样通过视频同轴电缆在剪辑设备之间传送未压缩的串行数字视频数据。

有两种SDI标准:SD-SDI和HD-SDI,它们基于不同的数据速率。

这两种标准的基本电气规范相同,主要不同点是,H D-SDI有较高的数据速率,1.485 Gbps,而SD-SDI数据速率在143 Mbps到540 Mbps之间,270 Mbps是最流行的速率。

SDI是Ser ial Digital Interfa ce 的缩写,也就是串行数字接口,它是SMPTE 259M中定义的串行数字接口,该接口采用10比特传输与非归零反向(NRZI)编码。

在传送ITU-R BT.601(A部分)4:2:2级别信号时,其时钟还率为270 Mb/s,这就是如今大名鼎鼎的SDI,后来,SDI 逐渐成为数字设备的标准配置,在此基础上终于实现了演播室、主控、播控系统的数字化;SDI是信道码流,这种码流是没有经过编码压缩的基带信号,码率较大,占用较大的传输带宽;随着高清晰度电视技术加速发展,采用串行数字接口传输高清信号已在行业内达成共识,为此,SMPTE在292M标准中定义了时钟频率达1. 5 Gb/s级别的串行数字接口HD-SDI,时钟频率提升到1.485 Gb/s;高速接口芯片技术的进步使3Gb/s级别的串行接口成为可能,SMPTE 424M也给出了类似的3Gb/s级别接口的定义。

本文以Cisco路由器为例,介绍了路由器上常用接口的类型、特点和应用场合。

1 EIA/TIA 232EIA/TIA 232有时又被称作RS-232 C.RS(Recommended Standard)代表推荐标准(EIA制定的标准一般都被冠以"RS" ),232是标识号,C代表RS-232的最新一次修改。

它是由是美国电子工业协会/电信工业协会(Electronic Industries Association / Telecommunications Industries Association,EIA/TIA)在1969年公布的通信协议标准。

它最初主要用于近距离的DTE和DCE 设备之间的通信。

后来被广泛用于计算机的串行接口(COM1、COM2等)与终端或外设之间的近地连接标准。

该标准在数据传输速率20K bps时,最长的通信距离为15米。

该标准对应的国际标准是CCITT推荐的标准V.24.这个标准对串行接口通信的有关问题,如电缆、接口的机械、电气特性、信号功能及传送过程特性进行了描述。

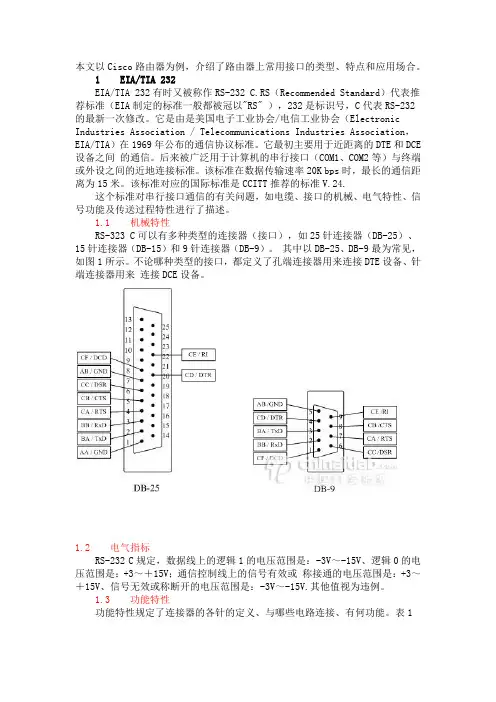

1.1 机械特性RS-323 C可以有多种类型的连接器(接口),如25针连接器(DB-25)、15针连接器(DB-15)和9针连接器(DB-9)。

其中以DB-25、DB-9最为常见,如图1所示。

不论哪种类型的接口,都定义了孔端连接器用来连接DTE设备、针端连接器用来连接DCE设备。

1.2 电气指标RS-232 C规定,数据线上的逻辑1的电压范围是:-3V~-15V、逻辑0的电压范围是:+3~+15V;通信控制线上的信号有效或称接通的电压范围是:+3~+15V、信号无效或称断开的电压范围是:-3V~-15V.其他值视为违例。

1.3 功能特性功能特性规定了连接器的各针的定义、与哪些电路连接、有何功能。

表1给出了DB-25常用的一些针的定义、功能等。

表1 RS-232 C的功能特性描述其中:第1针GND,是设备的保护地,与设备机壳相连。

串行异步通信程序设计串行异步通信程序设计串行异步通信,也称为串口通信,是一种常见的计算机间通信方式,它通常用于连接计算机和外部设备,如打印机、调制解调器等。

在串行异步通信中,数据按比特流的形式传输,而不是按字节或块传输,这使得通信速度更快,但也增加了数据传输中的错误检测和校正难度。

在本文中,我们将介绍如何设计一个串行异步通信程序。

一、串口基础知识在介绍串口通信程序设计之前,我们先来了解一些串口的基础知识。

串口是一种异步串行通信接口,通常包括一个发送引脚(TX)、一个接收引脚(RX)、一个数据位(D)、一个校验位(P)和一个停止位(S)。

串口的工作原理如下:1. 将数据按照字节分割成比特,加上校验位和停止位,形成数据帧;2. 将数据帧通过串口发送引脚发送出去;3. 接收端通过串口接收引脚接收到数据,然后进行错误检测和校正。

在串口通信中,数据帧的大小和格式必须在发送和接收端保持一致。

例如,在两台计算机之间使用串口进行通信时,它们必须使用相同的数据位、校验位和停止位参数设置。

二、串口通信程序设计在设计串口通信程序时,需要考虑以下几个方面:1. 设计串口驱动程序;2. 设计串口配置程序;3. 设计串口发送和接收程序。

接下来,我们将逐一介绍这些方面。

1. 设计串口驱动程序串口驱动程序是串口通信的核心部分,它用于控制串口的发送和接收,以及数据帧的格式化和解析。

在设计一个串口驱动程序时,需要考虑以下几个方面:(1)串口的初始化:包括设置数据位、校验位、停止位等参数;(2)数据帧的格式化:将数据按照串口配置中的参数进行格式化,形成数据帧;(3)数据帧的解析:在接收端,需要对接收到的数据帧进行解析,提取出有效数据;(4)发送和接收的状态控制:控制发送和接收的状态,包括启动和停止发送、启动和停止接收等。

2. 设计串口配置程序串口配置程序用于配置串口参数,包括数据位、校验位、停止位等参数。

在设计一个串口配置程序时,需要考虑以下几个方面:(1)接口定义:定义串口配置程序与串口驱动程序之间的接口,包括调用方法和参数格式;(2)界面设计:设计一个用户友好的界面,方便用户进行串口参数配置;(3)参数验证:在用户输入参数后,需要对参数进行验证,确保参数符合串口通信规范。

通用异步串行通讯接口一般应用方法通用异步串行通讯(UART,以下简称:串口通讯),是一般嵌入式工程控制系统中使用非常普遍的一种通讯方式,又主要是以TTL电平、RS232、RS485或RS422总线方式为最多。

所以,一般从事工控行业的IT工程师,需撑握串口通讯的一般应用方法,包括接口总线的硬件及通讯协议的软件。

但还是有不少的工程师对此不了解,因此该技术文章对串口通讯应用相关的硬件及软件进行一些描述。

串口设备在一般的PC机、单片机、ARM处理器等常用的CPU都有,且有些芯片多达好几个串口。

串口通讯是按“字节”进行数据传输,每一个字节的传输由这几个位元素组成:起始位、数据位、校验位、停止位。

其中,数据位由应用程序填装,校验位是通过应用程序设置相应的控制寄存器设置,为可选位。

设置好校验并填装好要发送的数据后,串口控制器会自动生成数据通讯的波形。

因此在通讯波形中就会根据校验设置,增加或不增加校验波形时钟。

串口通讯的时序如下所示:∙空闲:通讯线上没有任何数据在通讯,这时通讯电平为高电平(均以TTL进行说明)∙起始位:通讯电平由高电平变为低电平,表示开始∙数据位:开始位以后,接就是数据位,且低位在前,高位在后。

(根据不同的控制器,通讯位可设置为7位、8位、9位,具体的要视应用而确定)∙校验位:根据数据位的高电平个数及校验设置要求,在该位出现一个高电平或低电平∙停止位:通讯电平由低电平变为高电平后且通讯位数据位已达到指定个数,则表示停止通讯。

串口通讯的各通讯电平距离说明:TTL:最长安全通讯距离视控制器而定,一般不要超过30cmRS232:最长安全通讯距离不要超过2MRS485/RS422:最长安全通讯距离不能超过1KM如果两个通讯设备在同一个PCB基板或很近的两个板卡之间,可以使用TTL电平进行通讯,如同一机箱内的两个单片机微控制系统。

如果两个通讯设备相距很近,但没有在同一系统中,可以使用RS232进行通讯,如控制系统与PC机之间。

串行同步/异步接口SPI: Serial peripheral interface 接口设备间通信的同步串行接口,常用于嵌入式系统中芯片间的通信。

SPI采用主从结构,主设备控制时钟信号来发送和接收数据,从设备根据时钟信号进行发送和接收。

I2C(Inter-integrated circuit)接口是基于一种同步串行传输的通信协议,用于连接集成电路芯片。

这个接口中,每个设备都有唯一的地址,此接口采用双线结构,一根时钟信号,一根数据传输。

USB Universal serial bus: 接口是一种用于连接计算机和外部设备的通信接口。

USB采用四线制,其中两根线用于发送和接收数据,一根用于时钟,一根用于供电。

UART是一种串行异步接口,universal asynchronous receiver /transmitter, 用于计算机和外部设备之间传输数据。

接口采用两线制,一根发送数据,一根接收数据。

RS232 Recommend standard 232, 通用的串行异步接口标准,用于计算机和外部设备之间的数据传输。

接口采用双线制,其中一个发送数据,另一个接收数据。

在传送数据时,发送设备和接收设备需要通过特定的数据格式和控制信号进行同步。

串行光纤接口是通过光纤传输数据的接口,具有高速,长距离传输的特点,常见的有Fiber Channel 和Gigabit ethernet。

XFI 和SFI 都是高速串行接口,但是物理层和电气特性不同。

XFI接口是10G 以太网物理层接口,而SFI 接口是SONET/SDH 物理层接口。

此外,XFI接口使用的单模光纤,SFI使用的是多模光纤。

Fiber channel 是一种高速,可靠的串行光纤接口,用于连接存储设备和计算机等设备。

采用光纤传输,具有高宽带,低延迟,长距离传输等特点,适用于数据中心等高性能计算场景。

Gigabit ethernet 是一种高速局域网接口,采用光纤传输,具有高速可靠,低延迟的特点。

at89c51单片机内部串行接口的4种工作方式1. 引言[at89c51单片机](是一款基于8051内核的8位微控制器,广泛应用于嵌入式系统中。

它具有内部串行接口,该接口可以与外部设备进行通信。

本文将详细介绍at89c51单片机内部串行接口的四种工作方式。

2. 串行数据传输的基本概念首先,我们需要了解一些串行数据传输的基本概念。

串行数据传输是指将数据位按照顺序一个接一个地传输,而不是同时传输整个字节。

在串行数据传输中,数据位按照一定的时钟脉冲进行传输,接收方根据时钟脉冲来恢复数据。

3. 工作方式一:同步串行通信(Synchronous Serial Communication)在同步串行通信中,数据的传输是在系统时钟的同步控制下进行的。

发送端在发送数据之前,需要根据系统时钟生成一个同步时钟信号。

接收端利用该同步时钟信号来接收和恢复数据。

以下是同步串行通信的工作流程: 1. 发送端根据系统时钟将数据位顺序发送。

2. 接收端根据同样的系统时钟接收数据位,并恢复数据。

同步串行通信具有以下特点: - 数据传输速率高,可靠性强。

- 发送端和接收端之间需要事先约定好系统时钟频率。

4. 工作方式二:异步串行通信(Asynchronous Serial Communication)在异步串行通信中,数据的传输不是在系统时钟的同步控制下进行的,而是通过起始位和停止位进行同步。

以下是异步串行通信的工作流程: 1. 发送端将数据位按照一定的时钟脉冲速率发送。

2. 接收端根据起始位和停止位来确定数据的起止位置,并恢复数据。

异步串行通信具有以下特点: - 数据传输速率较低,但适用于相对简单的通信需求。

- 发送端和接收端之间无需事先约定好系统时钟频率。

5. 工作方式三:SPI(Serial Peripheral Interface)SPI(Serial Peripheral Interface)是一种常用的同步串行通信协议,常用于单片机与外部设备之间的通信。

异步串行接口

在目前的DVB-C广播电视系统的传输接口中,有两种MPEG-2视频传输接口标准:异步串行接口标准ASI和同步并行接口SPI。

SPI一共有11位有用信号,每位信号差分成两个信号用来提高传输抗干扰性,在物理链接上用DB25传输,因此连线多且复杂,传输距离短,容易出现故障。

但SPI是并行11位信号,处理简单且扩展性强,因此目前一般的MPEG-2视频编码器的输出和视频***的输入都是标准的并行1 1位信号。

ASI用串行传输,只需一根同轴电缆线传输,连线简单,传输距离长。

根据SPI和ASI的优缺点,需要传输信号的SPI和ASI的互相转换。

1 SPI信号结构

并行传输系统SPI包括一位时钟信号、8位数据信号、一位帧同步信号PSYNC 和一位数据有效信号DVALID。

帧同步信号对应TS包的同步字节047H,DVALID信号用来区分TS包的长度为188个字节或204个字节。

当TS包长为188字节时,D VALID信号一直为高,同时所有信号都与时钟信号保持同步。

2 ASI接口

ASI传输流可以有不同数据速率,但传输速率恒定,为270Mbps,因此ASI可以发送和接收不同速率的MPEG-2数据。

ASI传输系统为分层结构。

最高层、第2

层使用MPEG-2标准ISO/IEC 13818-(Systems),第0层和第1层是基于ISO/I EO CD 14165-1的FC纤维信道。

FC支持多种物理传输媒介。

首先将包同步的MPEG-2传送包的8-bit码字转换成10-bit码字;接着在并/串转换时,当要求输入一个新字、而数据源还没有准备好时,应插入一个K28.5的同步字,以达到ASI的固定270Mbps传输速率。

所形成的串行比特流将通过缓冲/驱动电路和耦合网络,送到同轴电缆连接器上。

插入同步码字可以有三种方法:传输码流的单个字节前后不能都是同步字;传输码流的单个字节前后必须都是同步字;或者是两者的组合。

到达同轴电缆的接收数据,首先要经过连接器和耦合网络耦合到恢复时钟和数据的电路上,然后进行串/并变换;为了恢复字节同步,ASI***必须先搜寻到K28.5同步字,一旦搜索到该同步字,即为随后接收的数据标定了边界,从而建立了***输出字节的正确字节排列;最后进行10/8-bit变换,恢复出包同步的MPEG-2 TS码流数据。

但是K28.5同步字不是有效数据,因此解码时必须删除。

3 ASI接口实现方案

在本方案中,MPEG-2 TS码流由单片MPEG-2编码器MB86390提供,它输出符合SPI标准的并行11位信号,TS包长度为188个字节。

在SPI/ASI转换方案中,

主要选用CYPRESS公司cyb923/cyb933芯片、异步FIFO和逻辑编程器CPLD实现。

cyb923主要实现码字的8/10bit转换、插入同步字K28.5和并/串变换。

ASI的传输速率恒定为270MHz,而输入MPEG-2 TS码率是不同的,所以要用FIFO实现速率匹配,需要对输入的SPI数据、FIFO和cyb923之间的通信进行逻辑控制。

综合性能、价格和程序复杂度的考虑,本方案采用xilinx公司的CPLD逻辑编程器XC9 5108;用VHDL编程实现对它们的逻辑控制。

ASI的解码也是相似的过程,cyb933主要实现10/8bit转换、去除同步字K28.5和串并变换。

3.1 ASI编码

在ASI的编码过程中,只需将MPEG-2 TS的八位数据和一位TS码率传输时钟输入到CPLD。

因为在本方案中,TS格式为188个字节,因此数据有效信号DVALI D一直为高,CPLD忽略这个信号,只管接收TS码流数据,而不用关心TS码流的同步头。

PSYNC帧同步信号也一样忽略。

CPLD将接收到的数据以TS码率时钟写入FIFO。

当FIFO半满时,CPLD接收到FIFO的半满信号,然后CPLD给cyb923发FIFO可读信号,cyb923以27Mbps读取FIFO中的数据;当CPLD计数到cyb92 3读取了一定数量的FIFO数据,CPLD则向cyb923发送FIFO不可读信号,防止FI FO读空。

MPEG-2传输码率的并行最大速度为27/8=3.375Mbps,而读FIFO速率为27Mbps,因此FIFO不会有溢出。

考虑到延时,本方案选用较小容量的FIFO720 2。

cyb923在FIFO不可读时,向ASI码流中填充K28.5以维持270Mbps的固定传输速率。

最后串行数据经过驱动就可用同轴电缆传送出去。

本方案中,同步字K28.5的插入采用传输码流的单个字节前后不能都是K28.5同步字的方式。

这种方案相对其它两种方案来说,判断和处理都相对简单。

3.2 ASI解码

在ASI的接收端,输入的ASI码流经过均衡后,输入到cyb933芯片。

它由内部的时钟锁相环首先锁定ASI码流时钟,检测同步字K28.5;找到后即确定了ASI 比特流顺序,然后进行串/并转换。

由此可知,检测到K28.5,即字节对齐是ASI解码的重要前提,由此cyb933定义了一套检测字节同步的方法。

考虑到传输误码等原因可能造成假K28.5,因此cyb93 3采用双字节确认方法。

即连续两个字节都是K28.5,才确认字节同步了,接着进入正常的单字节解码状态。

在解码状态,如果在64个解码字节中,CPLD计数到有16个字节是错误的,则CPLD必须向cyb933发送信息,要求cyb933重新进行字节同步。

字节同步后,因为K28.5是cyb923插入的同步字节,不能作为有效数据输出,cyb933自动略除这些同步字节。

当cyb933检测到有效数据时,cyb933将输出一位当前数据有效的指示,如果把这个信号当作FIFO的写有效,则FIFO中的数据一定都是有效数据了。

当FIFO半满时,CPLD接收FIFO的半满信号后,CPLD读取FI

FO中的数据,并根据读出的字节是否是047H来确定TS包的同步字节;如果找到T S包同步字,将恢复对应的帧同步信号,此时CPLD计数188恢复出完整的TS包,接下来的字节如果不是047H,说明输入数据有误,CPLD将丢弃这些数据直到找到0 47H同步字,在此期间CPLD输出TS空包。

重新包同步后,CPLD才又开始计数输出正确的188字节的MPEG-2 TS包,从而恢复出SPI正确的11位信号。

同样,当FIFO数据不可读时,CPLD也输出TS空包,以维持输出的MPEG-2码率恒定。

在SPI转ASI的设计中,直接对SPI数据进行ASI编码,而不考虑误码问题。

主要考虑SPI数据直接从MB390输出,没有经过远距离传输,因而降低了ASI编码逻辑控制的复杂度。

在ASI解码过程中,ASI数据经过远距离传输,要考虑误码的因素,所以增加了字节和包的重同步设计,以增加抗干扰能力。

本方案在实际应用中很好地实现了SPI/ASI的相互转换。