基于DSP-BIOS的FIR数字滤波器设计与实现

- 格式:docx

- 大小:12.01 KB

- 文档页数:2

基于DSP 的FIR 数字滤波器 (设计实验)一、实验目的1.了解FIR (Finite Impulse Response 有限冲激响应)滤波器的原理及使用方法;2.了解使用MATLAT 语言设计FIR 滤波器的方法;3.了解DSP 对FIR 滤波器的设计及编程方法;4.熟悉在CCS 环境下对FIR 滤波器的调试方法; 二、实验原理数字滤波是DSP 的最基本应用,利用MAC (乘、累加)指令和循环寻址可以方便地完成滤波运算。

两种常用的数字滤波器:FIR (有限冲激响应)滤波器和IIR (无限冲激响应)滤波器的DSP 实现。

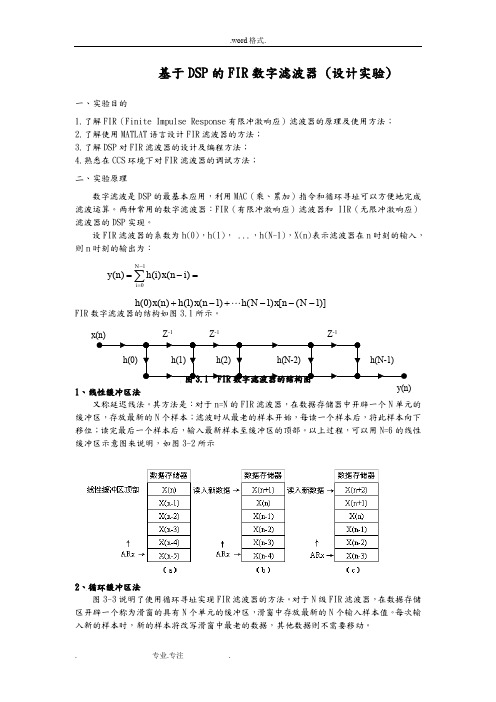

设FIR 滤波器的系数为h(0),h(1), ...,h(N-1),X(n)表示滤波器在n 时刻的输入,则n 时刻的输出为: FIR 数字滤波器的结构如图3.1所示。

1、线性缓冲区法又称延迟线法。

其方法是:对于n=N 的FIR 滤波器,在数据存储器中开辟一个N 单元的缓冲区,存放最新的N 个样本;滤波时从最老的样本开始,每读一个样本后,将此样本向下移位;读完最后一个样本后,输入最新样本至缓冲区的顶部。

以上过程,可以用N=6的线性缓冲区示意图来说明,如图3-2所示图3-2 N=6的线性缓冲区示意图2、循环缓冲区法图3-3说明了使用循环寻址实现FIR 滤波器的方法。

对于N 级FIR 滤波器,在数据存储区开辟一个称为滑窗的具有N 个单元的缓冲区,滑窗中存放最新的N 个输入样本值。

每次输入新的样本时,新的样本将改写滑窗中最老的数据,其他数据则不需要移动。

10()()()(0)()(1)(1)(1)[(1)]N i y n h i x n i h x n h x n h N x n N -==-=+-+---∑Z -1Z -1Z -1y(n)图3-3 FIR滤波器循环缓冲区存储器图三、实验内容与步骤设计一个FIR低通滤波器,通带边界频率为1500Hz,通带波纹小于1dB;阻带边界频率为2000Hz,阻带衰减大于40dB;采样频率为8000Hz。

基于DSP实现的FIR低通滤波器FIR(有限脉冲响应)低通滤波器是一种常见的数字信号处理(DSP)滤波器。

它的设计和实现非常灵活,可以用于去除数字信号中高频成分,使得信号能在一定的频率范围内进行平滑处理。

FIR低通滤波器有很多种设计方法,其中最简单的方法是基于窗函数设计,例如矩形窗、汉宁窗、布莱克曼窗等。

这些窗函数的选择取决于滤波器的性能要求和频率响应的形状。

在DSP中,FIR低通滤波器的实现可以采用直接形式、级联形式、并行形式和迭代形式等多种结构。

其中直接形式是最简单和直观的实现方式,也是最容易理解和实现的一种结构。

直接形式的FIR低通滤波器由一个延迟线、一组乘法器和加法器组成。

延迟线用于延迟输入信号,乘法器用于对延迟后的信号进行调制,而加法器则将调制后的信号相加得到输出信号。

```----------------------,,,x(n) -->, Delay ,-->, Multiply,-->--+ Sum ,--> y(n)Line ,,,----------------------```在实现过程中,需要注意的是延迟线的设置和乘法器的系数。

延迟线的长度决定了滤波器的阶数,即滤波器对输入信号的响应范围。

乘法器的系数则决定了滤波器的频率响应,可以通过窗函数的选取来确定。

通常,FIR滤波器的实现可以通过查表法或者卷积法来实现。

查表法通过预先计算所有可能的输入组合,并将其存储在一张查找表中,以减少计算量。

卷积法则通过将输入信号和滤波器的冲击响应进行卷积运算来得到输出信号。

当实现FIR低通滤波器时,还需要考虑滤波器的性能指标和算法的优化。

常见的性能指标包括滤波器的截止频率、抗混叠性能、通带和阻带的幅频特性等。

算法的优化可以从以下几个方面考虑:乘法器的系数选择、滤波器结构的选择、滤波器长度的选择和存储器的优化等。

总之,基于DSP实现的FIR低通滤波器是一种常用的数字信号处理滤波器,它可以用于去除数字信号中的高频成分,平滑信号的频谱。

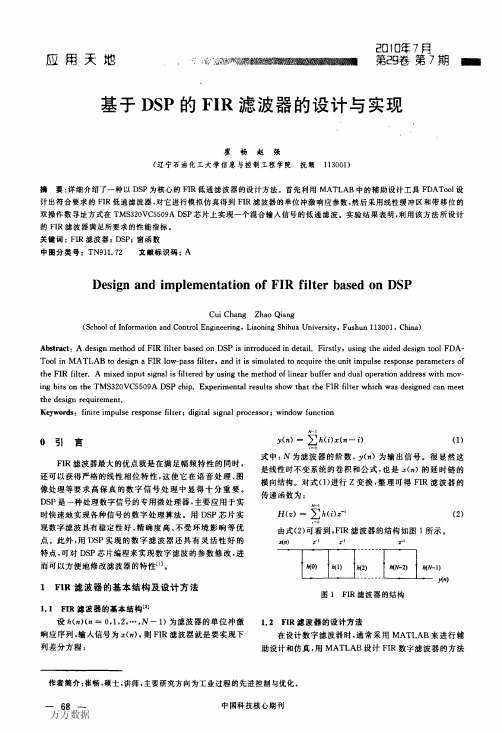

万方数据万方数据应用天地图4输入信号的波形及频谱图5输出信号的波形及频谱己口l口年7月第己g卷第7期嘲输入波形为一个低频率的正弦波与一个高频率的正弦波叠加而成。

通过观察频域和时域图得知:输入波形中的低频波形通过了滤波器,而高频部分则基本被滤除。

4结束语本文研究了FIR滤波器的原理和结构,并结合基于TMS320VC5509A开发的实验系统,介绍了FIR滤波器的设计及其DSP实现。

实验结果表明,所设计的FIR滤波器满足各项要求。

同时由于全部程序采用汇编语言编写,具有占用存储空间少、运行速度快、稳定可靠等优点,能够更好地适应需要实时滤波的场合。

参考文献刘万松.基于DSP的FIR数字滤波器的设计[D].贵州:贵州大学,2008:34-50.刘艳萍.DSP技术原理及应用教程[M].北京:北京航空航天大学出版社,2005:229-236.陈怀琛,吴大正,高西全.MATLAB及在电子信息课程中的应用[M].3版.北京:电子工业出版社,2007:218—219.王兵锋.FIR数字滤波器设计与仿真研究[D].哈尔滨:哈尔滨理工大学,2009:13-25.姜阳,周锡青.DSP原理与应用实验EM].西安:西安电子科技大学出版社,2008:150-169.赵秀玲,张利,武玉强.MATLAB辅助DSP实现FIR数字滤波器[J].现代电子技术,2007(9):38—40.黄全振,李泉溪,陈中伟.基于TMS320C54X的FIR滤波器的系统设计及应用[J].河南理工大学学报,2008,27(3):314—318.张三军,郭庆.基于MATLAB与DSP的心电整系数数字滤波器设计[J].国外电子测量技术,2009,28(3):69—72.,q_,~I—¨__‘_”。

‰,__r‘_I∥—嘲-—呻¨,。

■Ir—l_—_-r’~●r‘~-一I_d_h,。

嘲_一I¨J‰p,qh—嘶一h,-h,_hH。

_,1__州h,~¨—HIPdqI,_hI—呻I●F“h-一一。

2006年7月25日第23卷第4期通信电源技术T e lecom Pow er T echno l og iesJu.l 25,2006,V o.l 23N o .4收稿日期:2006 03 10作者简介:王献峰(1980-),男,山东人,硕士研究生,研究方向:智能化自动化装置的研究。

文章编号:1009 3664(2006)04 0038 03设计应用基于DSP 的FI R 数字滤波器的设计与实现王献峰,石 东(天津科技大学电子信息与自动化学院,天津300222)摘要:F IR 数字滤波器广泛地应用于数字信号处理领域,本文对F IR 滤波器的工件原理和设计方法进行了简单的介绍。

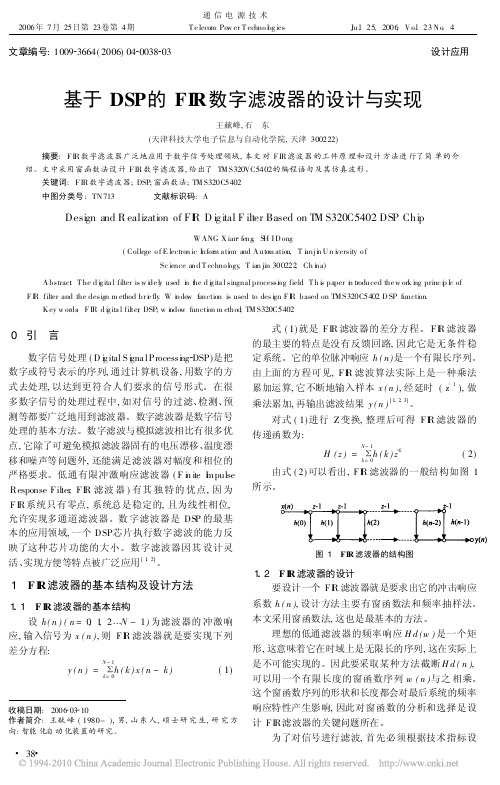

文中采用窗函数法设计F IR 数字滤波器,给出了TM S320VC5402的编程语句及其仿真波形。

关键词:F IR 数字滤波器;DSP;窗函数法;TM S320C5402中图分类号:TN 713文献标识码:ADesign and R ealization of FI R D ig ital F ilter Based on T M S320C5402DSP ChipW ANG X ian feng ,S H I D ong(College o f E lectron ic Infor m a ti on and A uto m ation ,T i anji n U n i versity o fSc ience and T echno l ogy ,T ian jin 300222,Ch i na)A bstract :T he d i g ita l filter is w i de l y used i n t he d i g ita l singnal processi ng field .T h i s paper i n troduced the w ork i ng princ i p l e of F I R filter and the design m ethod br i e fly .W i ndow f unction is used to des i gn F I R based on TM S320C5402D SP functi on .K ey w ords :F IR d i g ita l filter ;DSP;w i ndow functi on m ethod ;TM S320C54020 引 言数字信号处理(D i g ital S i g na lProcessi n g DSP)是把数字或符号表示的序列,通过计算机设备,用数字的方式去处理,以达到更符合人们要求的信号形式。

N -1一、试验目的:1、了解 FIR 滤波器的 DSP 实现方法;2、了解用 FIR 滤波器实现模拟信号滤波的全过程;3、把握 FIR 滤波器直接型构造的实现方法。

二、试验原理:FIR 滤波器是有限长单位脉冲响应数字滤波器,其系统函数一般式为:H (z ) = ∑ h (n )z - nn =0FIR 滤波器的通用 DSP 实现法与前面介绍的 IIR 滤波器构造的实现方法类似, 用 FIR 滤波器对模拟信进展滤波的构造图所示。

数字滤波器对模拟信号滤波的原理图本试验中在以通用DSP(TMS320)为核心的DSP 平台上承受窗函数设计法分别设计了 50 阶的高通、低通、带通 FIR 滤波器,其幅频特性分别如以下图形所示:50)B d (ed u t i n ga M 0 -50 -100-1501000 2023 3000 4000 5000 6000 7000 8000 9000 10000Frequency (Hz))s e r g e d ( e s a h P-500 -1000 -1500-20231000 2023 3000 4000 5000 6000 7000 8000 9000 10000Frequency (Hz)输入 保护滤波器输出A/D FIR 滤波器 D/A低通滤波器的频响特性)s e es no ps eRe dut i nga M1.510.510000 1000 2023 3000 4000 5000 6000 7000 8000Hertz9000 10000r g e d( e s a h P -1000-2023-3000-40000 1000 2023 3000 4000 5000 6000 7000 8000Hertz9000 10000es no ps eRe dut i nga Ms)1.510.50 1000 2023 3000 4000 5000 6000 7000 8000Hertz9000 10000e r ged(e sa hP-500-1000-15000 1000 2023 3000 4000 5000 6000 7000 8000Hertz9000 10000高通滤波器的频响特性带通滤波器的频响特性试验板信号源Input1GndGndOut3示波器试验名称:通用DSP 实现FIR 滤波器姓名:刘宇〔〕同组人:石龄佳〔〕三.试验原理图:图2-5 试验原理图四.试验仪器稳压电源一台,双踪示波器一台, 信号源一台,试验板一块五、试验内容及步骤:1、按试验连接图检查连线是否正确,然后依次翻开信号源﹑示波器﹑试验装置的电源开关。

基于DSP的FIR数字滤波器的设计与仿真毕业设计论文研究背景数字信号处理在现代通信、音视频处理、图像处理等领域中起着至关重要的作用,数字滤波器是数字信号处理中的重要内容。

其中FIR数字滤波器是一种常用的滤波器,其具有线性相位和稳定性等特点,在数字信号处理中应用广泛。

因此,本毕业设计将以FIR 数字滤波器为研究对象,结合DSP平台,进行数字滤波器的设计与仿真研究。

研究目标本文旨在设计一种基于DSP的FIR数字滤波器,并且研究其性能和仿真效果。

主要目标包括:1. 掌握DSP平台的开发流程和设计方法,包括硬件平台和软件开发技术。

2. 研究FIR数字滤波器的原理和特点,掌握其设计方法和计算技巧。

3. 基于DSP平台设计实现FIR数字滤波器,包括硬件和软件两个方面,满足设计要求。

4. 仿真FIR数字滤波器的性能和效果,验证设计的正确性和可行性。

5. 撰写毕业设计论文,总结设计过程和结果,体现出自己的设计思路和方法。

研究方法本研究采用如下方法:1. 研究DSP平台的开发流程和设计方法,包括使用硬件平台和软件开发技术。

2. 研究FIR数字滤波器的原理和特点,掌握其设计方法和计算技巧。

3. 基于DSP平台设计实现FIR数字滤波器,采用Verilog语言描述硬件电路,C语言编写软件程序。

4. 利用模拟工具对FIR数字滤波器进行仿真,测试性能和效果。

5. 撰写毕业设计论文,总结设计过程和结果,体现出自己的设计思路和方法。

预期结果本研究预期可以达到如下结果:1. 掌握DSP平台的开发流程和设计方法,能够应用于数字信号处理和嵌入式系统开发等领域。

2. 研究FIR数字滤波器的原理和特点,掌握其设计方法和计算技巧,能够进行数字信号处理相关工作。

3. 基于DSP平台设计实现FIR数字滤波器,满足设计要求,具有较好的性能和稳定性。

4. 仿真FIR数字滤波器的性能和效果,能够验证设计的正确性和可行性。

5. 撰写毕业设计论文,总结设计过程和结果,体现出自己的设计思路和方法,具有较好的表达和撰写能力。

毕业设计题目:基于DSP的FIR滤波器的设计与实现系:专业:班级:学号:学生姓名:导师姓名:完成日期:2013年6月7号诚信声明本人声明:1、本人所呈交的毕业设计(论文是在老师指导下进行的研究工作及取得的研究成果;2、据查证,除了文中特别加以标注和致谢的地方外,毕业设计(论文中不包含其他人已经公开发表过的研究成果,也不包含为获得其他教育机构的学位而使用过的材料;3、我承诺,本人提交的毕业设计(论文中的所有内容均真实、可信。

作者签名:日期:2013年月日毕业设计(论文任务书题目:基于DSP的FIR滤波器的设计与实现姓名系别专业班级学号指导老师职称教研室主任一、基本任务及要求:本次设计以FIR滤波器为研究对象,针对FIR滤波器的特点,研究FIR滤波器的设计方法,并在DSP试验箱上进行调试,软件设计包括:窗函数设计法和频率采样法的MATLAB仿真程序、DSP的滤波程序等。

二、进度安排及完成时间:1、第一周至第二周:明确课题任务及要求,搜集课题所需资料,了解本课题研究现状、存在问题及研究的实际意义。

2、第三周:查阅相关资料,自学相关内容,确定课题总体方案,确定个人研究重点,做好开题报告。

3、第四周至第七周:根据确定的设计方法—窗函数设计法和频率采样法设计FIR滤波器,并在MATLAB环境下进行仿真。

4、第8周至第十二周:FIR滤波器的DSP实现和调试。

5、第十三周至第十四周:整理资料,完成毕业论文编写,进行毕业答辩。

目录摘要 ................................................................................................................................I Abstract (II)第1章绪论 .. (11.1 数字滤波器的基本概念 (11.2 数字滤波器的分类 (11.3 数字滤波器的发展及其优点 (11.4 数字滤波器的实现方法 (21.5 DSP的发展状况及趋势 (3第2章 FIR数字滤波器的设计原理 (52.1 FIR滤波器的基本原理及设计方法 (52.1.1 FIR滤波器的基本原理 (52.1.2 FIR滤波器的设计方法 (52.2 FIR滤波器的窗函数设计法 (62.2.1窗函数设计法的基本原理 (62.4.2典型窗函数及其特性 (72.4.3窗函数所设计的FIR滤波器的性能分析 (10 2.3 FIR滤波器的频率采样设计法 (122.3.1频率采样设计法的基本原理 (122.3.2频率采样设计法的设计步骤 (13第3章 FIR滤波器的MATLAB仿真 (143.1 MATLAB简介 (143.2 窗函数设计法的MATLAB仿真 (143.2.1低通滤波器MATLAB仿真 (153.2.2带通滤波器MATLAB仿真 (193.2.3高通滤波器MATLAB仿真 (233.2.4结果分析 (263.3 频率采样法的MATLAB仿真 (26第4章 FIR滤波器的DSP实现 (304.1 TMS320C55x的硬件结构 (304.1.1 C55xCPU内部总线结构 (304.1.2 C55x的CPU组成 (304.1.3 C55x存储器配置 (304.1.4 C55x外设配置 (314.2 DSP实现FIR滤波器的硬件原理图 (314.3 利用MATLAB软件的FDATool设计FIR滤波器 (32 4.4 CCS环境下FIR滤波器的设计及软件仿真 (344.4.1程序框图 (344.4.2在CCS环境下进行FIR滤波器仿真 (344.4.3结果分析 (384.5 实时采样信号进行滤波的FIR滤波器的实现 (384.5.1设计原理 (384.5.2测试结果 (40结束语 (42参考文献 (43致谢 (44附录 (45MATLAB仿真程序 (45DSP实现程序 (49实时采样滤波程序 (52基于DSP的FIR滤波器的设计与实现摘要:在当今信息时代数字信号处理已成为一门极其重要的学科,数字信号处理在语音、图像等众多相关领域得到广泛的应用。

基于DSP实现的FIR低通滤波器FIR(Finite Impulse Response)低通滤波器是一种数字信号处理(DSP)算法,用于滤除输入信号中高于一些截止频率的频域成分,并使输出信号只包含低于该截止频率的成分。

FIR低通滤波器通常由一组脉冲响应函数(Impulse Response)的加权和组成,其中权重决定了滤波器的频率响应。

实现FIR低通滤波器的一种常见方法是使用离散时间线性卷积运算。

滤波器的输入信号通过一个延迟线数组,然后与一组权重向量进行内积。

该内积计算的结果即为滤波器的输出。

在DSP领域,用于实现FIR低通滤波器的算法有很多种,其中最常用的是基于迭代结构(Direct Form)的算法。

此算法按照滤波器的脉冲响应函数的长度进行迭代,每次迭代处理输入信号的一个样本。

该算法的优点是实现简单、稳定可靠。

下面是一个基于DSP实现的FIR低通滤波器的伪代码示例:```python#定义滤波器的截止频率和脉冲响应函数长度def cutoff_frequency = 1000 # 截止频率为1kHzdef length = 101 # 脉冲响应函数长度为101#初始化滤波器的权重向量def weights = [0.0] * length#计算滤波器的脉冲响应函数for i in range(length):#计算当前权重对应的频率frequency = i * sampling_rate / length#如果当前频率小于截止频率,则设置权重为1,否则为0weights[i] = 1 if frequency <= cutoff_frequency else 0#初始化输入和输出信号数组def input_signal = [0.0] * signal_lengthdef output_signal = [0.0] * signal_length#循环处理输入信号的每个样本for i in range(signal_length):#延迟线数组移位,并将当前输入样本放入延迟线的第一个位置delay_line[1:] = delay_line[:-1]delay_line[0] = input_signal[i]#计算滤波器的输出output_signal[i] = sum(delay_line * weights)```这段示例代码实现了一个FIR低通滤波器,截止频率为1kHz,脉冲响应函数长度为101、首先,根据截止频率计算出权重向量。

基于DSP/BIOS的FIR数字滤波器设计与实现

1 引言数字信号处理器(DSP)拥有强大的数字信号处理能力,与其配套的

集成可视化开发环境CCS(Coder Composer Stu-dio)更方便了DSP 应用程序的开发。

DSP/BIOS 是CCS 的重要组成部分,它实质上是一种基于DSP 平台的规

模可控的实时操作系统内核。

这里主要研究在DSP 上利用DSP,BIOS 实现

FIR 数字滤波器的方法。

2 TMS320F2812 及DSP/BIOS 内核介绍TMS320F2812 是基于TMS320C2XXX 内核的定点数字信号处理器,具有数字信号处理及强大

的事件管理和嵌入式控制功能,适于有大批量数据处理的控制系统。

其性能可

用于数字滤波器设计。

TMS320F2812 采用高性能的静态CMOS 技术,时钟频率达150 MHz;低功耗(内核电压1.9 V,I/O 口电压3.3 V);采用哈佛总

线结构,片上集成许多片上外设,可实现更多功能。

开发环境是集成开发环境CCS,支持C/C++/汇编嵌入式实时操作系统DSP/BIOS,JTAG 调试接口。

DSP/BIOS 内核是一个尺寸可伸缩的实时内核,它是为实时信号处理应用而

设计的,主要包括:(1)DSP/BIOS 配置工具。

该工具可用来创建和配置在应

用程序中使用的DSP/BIOS 内核对象,也可使用该工具配置存储器,线程优

先权以及中断处理;(2)DSP/BIOS 实时分析工具。

CCS 中的分析丁具使用户

可测试和分析目标DSP 上应用程序的运行,包括监测CPU 负荷、日志、线程

执行情况等;(3)DSP/BIOS API 函数。

用户在PC 端采用C、C++或汇编语言编写调用DSP/BIOS API 函数的应用程序;(4)器件支持库。

提供许多宏和函数,用来简化片上外设的配置和管理。

3 数字滤波器分析数字滤波器根据冲激响应持续时间可分为有限冲激响应

滤波器(FIR)和无限冲激响应滤波器(IIR)。

其中FIR 滤波器能够保证严格的线性

相位特性,且不存在稳定性问题。

窗函数法和频率采样法等是设计FIR 数字滤。