锡须的成长机制

- 格式:pdf

- 大小:870.83 KB

- 文档页数:12

锡须标准

锡须是一种从元器件和接头的锡镀层表面生长出来的细长形状的锡单晶,直径通常在0.3-10um之间,典型值为1-3um,长度在1-1000um之间,锡须有不同的形状,如针状、小丘状、柱状、花状、发散状等。

锡须的生成机理主要与热力学和电化学因素有关。

在热力学方面,锡须的形成是锡金属在一定温度下的自然生长过程。

在电化学方面,锡须的形成是锡金属在一定电位差下的电化学行为,当锡金属表面存在电位差时,会产生电化学腐蚀,从而形成锡须。

锡须的危害主要表现在电气短路、机械卡死、接触不良等方面。

如果这些导电的锡须长得太长,可能连到其他线路上,并导致电气短路;断裂后落在某些移动及光学器件之间可能产生弧光放电,烧坏电气元件等。

因此,针对锡须的生成和危害,可以采取以下预防措施:

1. 不要使用亮锡,最好使用雾锡。

2. 使用较厚的雾锡镀层(8-10um),以抑制应力的释放。

3. 电镀后24小时内退火(150℃/2hrs或180℃/lhrs),以减少锡层的应力。

4. 电镀后24小时内回流焊接,作用同退火。

5. 用N或Ag做阻挡层(1.3-2um),防止Cu扩散形成Cu6Sn5的IMC。

錫鬚生長試驗報告

一﹑試驗目的﹕

檢驗產品在試驗后是否有錫鬚產生﹐以確認產品的可靠性。

二﹑試驗樣品﹕

DIP產品

三﹑試驗樣品周期﹕

周期為﹕2028W

四﹑試驗樣品數量﹕

5PCS

五﹑試驗材料﹕

錫材(100%BAR)

六﹑試驗項目及條件﹕

1﹑高溫試驗﹕溫度﹕125±2℃﹐時間﹕1000小時參照(GB2423.2-89)

2﹑恆定濕熱試驗﹕溫度﹕85℃±2℃﹐濕度﹕85%±2%RH﹐時間﹕1000小時參照(GB2423.3-93) 3﹑熱沖擊試驗﹕最低溫度﹕-45℃最高溫度﹕85℃﹐保持時間﹕10分鐘﹐循環次數﹕1000次參照(GB2423.22-87)

七﹑試驗設備﹕

1﹑高溫試驗﹕高溫箱(PHH-101)

2﹑恆定濕熱試驗﹕高低溫交變潮濕試驗箱(ESL-04AGP)

3﹑熱沖擊試驗﹕溫試沖擊試驗箱(TSG-70H-W)

4﹑影像式精密測繪儀18-230倍

八﹑檢驗項目﹕

1﹑試驗前用影像式精密測繪儀18-230倍觀察焊點

2﹑試驗后用影像式精密測繪儀18-230倍觀察焊點

九﹑檢驗環境要求及標准﹕

1﹑環境要求﹕溫度﹕15~~30度﹔濕度45~~45%RH,

2﹑錫鬚標准﹕用影像式精密測繪儀18-230倍觀察焊點錫鬚小于600u"(約為最小PIN距1.27mm 的1/2)

十﹑試驗前后圖片如附件﹕

用影像式精密測繪儀18-230倍觀察焊點無錫錫鬚產生

DIP產品高溫試驗前﹑高溫試驗后無錫鬚產生

DIP產品恆定濕熱試驗試驗前﹑定濕熱試驗試驗后無錫鬚產生

十一﹑試驗結論﹕

合格

DIP產品溫度沖擊試驗前﹑溫度沖擊試驗后無錫鬚產生。

减轻镀锡表面的锡须生长使用纯锡铅表面处理时,可能会生长锡须,这是值得关注的问题之一。

近年来,人们已经做了大量的测试和分析工作,对于锡须在各种不同环境条件下的生长成因,有更多了解。

本文将讨论,在电子设备工程联合委员会(JEDEC)标准推荐的三个加速测试期间,锡须生长的机制。

作者:Sheila Chopin、Peng Su博士人们对减轻纯锡表面处理中生长锡须的现象已经有了广泛的研究。

这些研究数据说明,形成锡须的主要原因是表面的应力增大,它受到由各种因素的影响。

举个例子,电镀过程会因为颗粒大小、厚薄和污染物水平不同而影响镀锡表面的应力状态。

像温度和湿度这样的应用条件,也会诱导微观结构发生某种改变,从而影响锡须的生长速度。

本文讨论在电子设备工程联合委员会(JEDEC)推荐的三个测试条件下进行的测试。

在一定程度上,这些测试代表一些常见的实地应用条件。

在测试结果的基础上研制减轻锡须生长的技术,可以有效地用于现实环境。

加速测试JEDEC推荐的测试条件摘要列于表1。

对于空气对空气温度循环(AATC)测试,允许的温度范围是-40℃到85℃;但本文中所有研究使用的温度范围是-55℃到85℃。

在热循环测试中,导致锡须生长的原因,是三个测试中最简单的。

因为锡和引脚结构材料之间的热膨胀系数(CTE)不同,温度变化会在锡表面产生热应力。

由于使用的温度范围较宽,在一个很短的时间内,在表面中会产生很高的热应力,因而忽视由于速度较慢的机制而产生的应力。

在确定热应力大小时,锡颗粒的结晶方向是另一个重要因素。

锡晶格是各向异性的,这意味着,在不同的结晶面,或者沿着不同结晶方向,机械特性(如杨氏模量和热膨胀系数)有可能会发生变化。

对于镀锡表面,因为它通常由一层晶粒组成,我们需要关注只是水平方向元件的膨胀系数(CTE)和膨胀量(E)。

图1是这个模型的简化一维视图。

图1说明晶粒方向影响的一维视图。

当晶粒1和晶粒2的膨胀量和膨胀系数数值不同时,两种晶粒之间的应力就可能不同,即使它们的热应变相同也是如此。

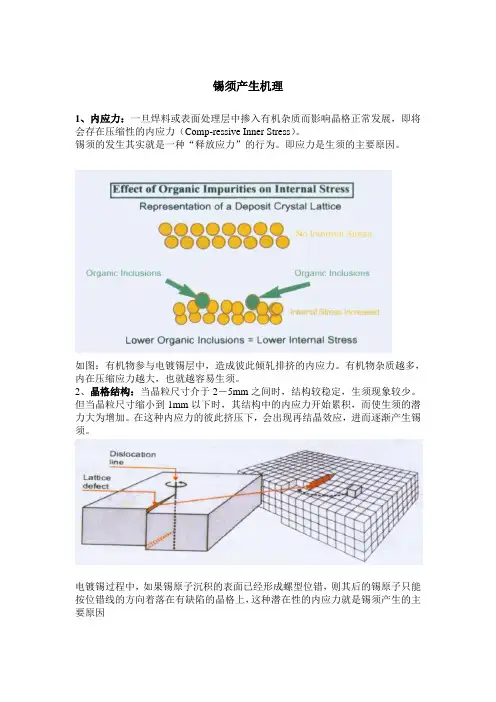

锡须产生机理

1、内应力:一旦焊料或表面处理层中掺入有机杂质而影响晶格正常发展,即将会存在压缩性的内应力(Comp-ressive Inner Stress)。

锡须的发生其实就是一种“释放应力”的行为。

即应力是生须的主要原因。

如图:有机物参与电镀锡层中,造成彼此倾轧排挤的内应力。

有机物杂质越多,内在压缩应力越大,也就越容易生须。

2、晶格结构:当晶粒尺寸介于2-5mm之间时,结构较稳定,生须现象较少。

但当晶粒尺寸缩小到1mm以下时,其结构中的内应力开始累积,而使生须的潜力大为增加。

在这种内应力的彼此挤压下,会出现再结晶效应,进而逐渐产生锡须。

电镀锡过程中,如果锡原子沉积的表面已经形成螺型位错,则其后的锡原子只能按位错线的方向着落在有缺陷的晶格上,这种潜在性的内应力就是锡须产生的主要原因。

锡须常识目录第一部分:锡须图片第二部分:什么是锡须?第三部分:锡须的形成原因第四部分:抑制锡须的方法第五部分:关于锡须的其他信息第一部分:锡须图片第二部分:什么是锡须?*要了解锡须,先对晶须有个概念:1) 晶须是一种头发状的晶体,它能从固体物质的表面直接生长出来,形状类似胡须,其直径是微米级,其长度达到数毫米级.2) 晶须的危害是:诱发电子线路短路,打火,噪音等问题.3) 晶须的生长速度随着温度的升高而加快,随着湿度的增加而加快.*锡须,也就是锡的晶须:1)它首先具备了晶须的主要特性.2)锡须主要从电镀层开始生长,尤其在铜或者黄铜表面镀亮面锡的镀层最为敏感.3)从晶须的历史来看发现只要添加微量的铅就可以抑制晶须的产生随着RoHS法令实施日期的日益临近从而就使得这个30年前的老问题再次浮出了水面主要针对在无铅焊接,引脚镀层采用纯锡工艺第三部分:锡须的形成原因*锡须形成的原因是应力,具体又可分为以下两种:1) 电镀后的残留应力为使焊点有光亮的外观,在引脚的电镀液中加入光亮剂,光亮剂的主要成分是碳和氢,电镀时,碳和氢,会附着在引脚上,导致镀层因材料的不匹配而引发内力的存在,将锡由内向外推,变成我们所说的锡须.2) 介金属化合物生成所引起的应力在储存的阶段中,锡与铜反应生成介金属化合物,镀层表面会因为氧化而形成氧化锡.由于介金属化合物与锡的密度/热膨胀系数等等参数都不一样,而氧化锡的生成会抑制应力的释放,所以会有一种由内而外的应力将锡向外推,变成我们所说的锡须.第四部分:抑制锡须的方法1) 采用雾面锡,镀液中不填加光亮剂2) 退火: 把电镀完的元件拿去烘烤一般要求150第五部分: 关于锡须的其他信息1) 锡须的接收标准:在500倍放大镜下观察,锡须<50um可接收.2) 当斜率>20高温情况下不会长锡须. 4) 晶须发现条件:一般来说+8585%但在室温因此用原来的试验方法很难判断有没有因晶须导致的故障。

一、什么是锡须生长锡须生长是在锡的表面按照锡的结晶形式生长的锡的可以导电的须状物,这种锡须的生长尤其是电镀锡比较明显。

锡须一般可以长到几个毫米,但是个别的可以长到10毫米,直径可以是几个微米,10个微米的比较少见。

美国宇航局太空飞行中心的一个电磁继电器发生的一次短路现象二、产生的机理有各种说法,但是比较主要的是应力产生机制。

对影响锡须生长的因素主要有:温度、湿度、热循环、应力、电场等温度循环对锡须的生长有很大的促进作用。

生长的温度在50℃最快,在20~25℃也可以生长,但一般认为在150℃就会结束生长。

三、可能产生的影响可能引起稳定的短路、瞬态短路(锡须熔断)、电弧、产生多于物(主要发生在密闭的腔体内,例如继电器、混合集成电路等)、使元件脱落,使电子元件的电性能和机械性能下降。

四、降低锡须生长引起的风险的方法:1、浸焊这种方式是在纯锡的表层浸一层锡铅的焊料,可以减缓纯锡的锡须生长。

2、给镀层覆盖一层物质锡须还可能生长。

3、剥掉原来的纯锡层后重新电镀一层锡铅对我公司生产的产品如果一定要进行端头的锡铅化我想到的有如下的方法:1、采购端头只有银钯的产品后自己进行镍和锡铅的电镀困难是采购的周期要长,现在有厂家可以生产,但是产品的容量范围没有现在的宽。

2、将现有的产品进行浸焊,这种方法的风险比较大,而且很容易引进缺陷。

3、直接对现有产品进行电镀,这种方法的缺点是容易引起损耗、绝缘电阻的降低。

其中2、3这两种方法生产的产品尺寸不容易控制,容易做大。

说明:锡须的生长和纯锡的东西在低温下的粉碎是两个概念,纯锡在低温下的粉碎是因为其发生相变而引起的,是整块金属的变化;锡须的生长是单个晶粒由于条件的允许而引起的生长,是部分金属的变化。

以下是美国军用的失效案例1. Military Airplane:G. Davy,, Northrop Grumman Electronic Systems Technical Article, October2002军用飞机2. Patriot Missile:Suspected tin whisker related problems (Fall 2000)爱国者导弹3. Phoenix Air to Air Missile:L. Corbid, "Constraints on the Use of Tin Plate in Miniature ElectronicCircuits", Proceedings 3rd International SAMPE Electronics Conference, pp. 773-779, June 20-22, 1989.Phoenix 空空导弹4. F-15 Radar: B. Nordwall, "Air Force Links Radar Problems to Growth of Tin Whiskers", AviationWeek and Space Technology, June, 20, 1986, pp. 65-70F-15 雷达5. U.S. Missile Program:J. Richardson, and B. Lasley, "Tin Whisker Initiated Vacuum Metal Arcingin Spacecraft Electronics," Proceedings 1992 Government Microcircuit Applications Conference, Vol.XVIII, pp. 119 - 122, November 10 - 12, 1992.导弹的一个部位(不会翻译)因为锡须产生了电弧(发生在电路中)6. U.S. Missile Program:K Heutel and R. Vetter, "Problem Notification: Tin Whisker growth inelectronic assemblies", Feb. 19, 1988, memorandum锡铅合金端头的产品主要应用在MIL-PRF-55681和高可靠领域。

电子封装锡和锡合金表面晶须标准研究发布时间:2022-05-09T08:14:17.102Z 来源:《新型城镇化》2022年9期作者:杨雅丽曲乐[导读] 本文简述了晶须的来源,形成机理及抑制措施,并结合JEDEC的标准对锡晶须标准制定进行指导。

珠海格力电器股份有限公司广东珠海 519000摘要:在当前电子封装行业,锡和锡合金易于产生锡须致使电器发生故障是一直以来困扰的难题,随着环保要求的提高,在锡中添加铅可以抑制锡晶须的生长已经不再是解决这一难题的绝佳方案,因此对锡晶须标准的研究成为必不可少的课题。

本文简述了晶须的来源,形成机理及抑制措施,并结合JEDEC的标准对锡晶须标准制定进行指导。

1引言锡和锡合金由于本身物理特性,易于在表面形成晶须致使电器发生故障,这一现象严重阻碍了电子封装行业的发展,尤其在航空航天、军事等高精端应用场景中,这一难题始终悬而未决。

而在实际应用过程中,针对晶须建立相关标准对于评价其使用性能尤为重要,因此对晶须的标准研究也是电子封装中必不可少的课题。

本文结合JESD22-A121A和JESD201A标准,即锡和锡合金表面晶须生长测量的测试方法、锡和锡合金表面涂层的锡须灵敏度环境验收要求,深入对锡晶须标准分析研究。

2晶须来源晶须是指一种呈纤维状的晶体,均匀的横截面积是其主要特征。

锡晶须则是在锡或锡合金表面自发生长出的晶须。

电子器件使用过程中晶须的存在造成相邻导体间短路、晶须短路导致金属蒸发放电等。

晶须的形成机理一直是业界研究的重点也是难点问题,目前尚无公认一致的结论。

目前提出的生长机制主要有位错机制、再结晶机制、氧化膜破裂(COT)机制、金属间化合物氧化分解机制、氢致晶须生长机制5种。

基于对晶须生长机制的探讨研究,提出了合金化、去应力退火[1]、中间隔离层、镀后重熔[2]、有机涂层、电镀工艺改进等几种锡晶须的抑制措施。

尽管目前除添加铅元素外还发现一些抑制锡晶须的措施,但仍无可量产并实现产业性抑制晶须的措施,锡晶须的产生无可避免,因此亟需建立对电子元器件中锡晶须的标准要求。

ipc9797 锡须标准

IPC 9797锡须标准是针对电子焊接行业的一项标准,旨在规范锡

须的形成、特性以及对焊接过程和产品可靠性的影响。

二、锡须的概念及形成原因

1. 锡须是指在焊接过程中,由于过量的锡元素在焊接接头上生长

而形成的细小锡丝。

2. 锡须的形成原因包括锡元素的扩散和界面上的应力等因素。

三、IPC 9797锡须标准的内容及要求

1. 标准要求焊接过程中锡须长度不得超过指定的数值。

2. 对于不同应用场景,标准将锡须分为可接受和不可接受两种级别。

3. 标准提供了对焊接接头进行检测和评估的方法和指导,以判断

锡须的可接受性。

四、锡须对焊接过程及产品可靠性的影响

1. 长锡须可能导致电气短路或焊接接头的断开,从而影响产品的

功能及可靠性。

2. 锡须在潮湿环境中容易发生电化学腐蚀,加速电子产品的老化。

五、对锡须的控制和预防措施

1. 合理控制焊接温度,避免过高温度导致锡元素过量扩散。

2. 使用适当的焊接材料和工艺参数,减少锡须形成的可能性。

3. 通过使用特殊的焊接工艺和涂覆保护层等方式,降低锡须的形

成和生长。

IPC 9797锡须标准是电子焊接行业的重要准则,通过对锡须的控

制和预防,可以提高焊接产品的质量和可靠性。

遵循标准的要求,采

取适当的措施,可有效减少锡须的产生,确保焊接接头的稳定性和耐

久性。

以上是对IPC 9797锡须标准的简要介绍,希望能为电子焊接行业

相关人士提供有关锡须的知识和指导。

无铅锡须——化学沉锡板锡须生长机理及特性研究2020/9/26整理资料摘要:锡须是化学沉锡表面处理应用推广遇到的最大阻碍,锡须的存在严重影响了产品的可靠性。

文章重点对锡须的生长机理进行了分析,通过实验设计对机理进一步验证。

探究了化学沉锡PCB不同区域锡须生长差异特性,得到了锡须的持续性生长规律,为化学沉锡板锡须改善提供参考依据。

关键词:锡须;沉锡;生长特性;前言随着目前全球推行环保,含铅焊料被禁止使用,产品开始转用无铅焊料完成PCB与元器件之间的焊接,如目前常用焊料Sn、Ag、Cu合金体系。

传统的有铅喷锡,逐渐被种类繁多的无铅化表面处理所替代,如:沉金、沉银、沉锡、无铅喷锡、OSP等,其中化学沉锡工艺,相较其他表面处理拥有更加优良润湿性能而成为目前流行的表面处理,如图1为不同表面处理与SAC305的润湿性能对比,化学沉锡对焊料具有最大的润湿力。

而且近年来微波高频板市场发展旺盛,化学沉锡PCB低损耗特、成本低廉的特性,获得了大量微波高频客户的青睐,化学沉锡表面处理的订单比例不断攀高。

然而目前随着PCB化学沉锡表面处理的推行,发现化学沉锡层自发生长锡须,为电子产品的可靠性埋下了致命风险。

锡须是从纯锡或锡合金镀层表面自发生长出来的一种细长形状的纯锡的结晶,锡须的直径通常为1~3μm;长度通常为1μm到1mm,最长可达到9mm。

锡须的形状多样,一般呈针状居多,如图2所示。

锡须的存在不仅使电路存在短路风险,还可能影响信号的完整性传输,对产品整机的可靠性及性能带来不利影响。

因此面对化学沉锡板的锡须生长危害,迫切需要对锡须的机理、生长特性展开研究,从机理认识角度规避锡须生长风险。

1.机理分析目前关于锡须的形成机理存在较多的模型,其中较为普遍的是压应力生长机理模型[1]。

Cu/Sn界面处由于“晶界扩散”模式生长出不规则IMC,对Sn层产生压应力,由于Sn面氧化膜的包裹下,应力产生积累,而从氧化膜的薄弱点“破土”萌生,在IMC的持续形成下,引发锡须自发生长的现象。

SMT部分工艺知识分享主要针对锡膏印刷、ICT 测试、Void 及锡须等方面的相关知识进行交流。

具体归纳如下:1.Solder Paste Print 锡膏印刷主要从锡膏粘刮刀并易导致锡膏漏印的角度来讲,分以下几个方面:锡膏方面:1)锡膏流变性不佳,致使锡膏无法顺利流入网孔。

这和锡膏的粘度高、颗粒大及助焊剂含量低有关。

2)锡膏的稳定性差,性能下降。

由锡粉颗粒和助焊剂发生化学反应而形成锡膏块。

这和锡膏的稳定性不佳和粘度高有关。

网板开口:网板开口形状不佳,孔壁不够光滑等都可能导致锡膏漏印量不足及成形不佳。

2.ICT TestICT 测试ICT 测试误判率大小主要和 ICT 测试针的性能、测试精度及锡膏助焊剂残留物的性能等方面有关。

锡膏残留物较多且较坚硬,ICT 测试针无法穿透松香残留物,易导致 ICT测试时误判甚至无法测试,给 ICT 测试带来极大的困扰!图片如下所示:Print3.Void 空洞由于无铅锡膏的表面张力比有铅大,因此无铅导入后,BGA/CSP 焊点的 Void 越来越受关注。

☆BGA/CSP 焊点内的 Void 分为两种:焊点内部和交界面处,如下图所示:☆业内普遍采用的 BGA/CSP 焊点 Void 含量的标准如下:面积百分比(Area%)☆Void 量的多少主要和以下几个因素有关: 1)表面张力的大小由于表在张力较大,气泡无法及时溢出而导致在焊点内形成 Void。

各合金的表面张力大小如下图所示:注:通常认为有 N2保护的回流环境 Void 的量会减少的观念是错的,其实 Void 量反而会增多。

这是因为 SnO(表面张力)<Sn(表面张力),在 N2 保护的环境下没有焊锡表面没有氧化层存在,而氧化层可以降低表面张力。

2)助焊剂气体的挥发助焊剂主要由树脂、溶剂、反应物、活性剂等组成,而在焊接过程中,大部分的溶剂、少量的活性剂等都挥发出去,而在焊点内部产生Void。

3)助焊剂助焊剂保留在焊球内,易形成 Void。

锡须危害及其预防评估措施摘要:随着无铅工艺的推广,锡镀层的锡须生长已成为一个值得重视的问题。

锡须引起的短路失效在电子领域的危害重大,但现阶段人们还无法从根源上阻止锡须生长。

针对锡须生长机理,我们推出常温常湿、高温高湿和温度循环三个环境应力激发试验,用于提前评估产品的锡须生长情况,减少后续使用过程中锡须过度生长引起产品功能失效的情况。

关键词:无铅工艺锡须环境应力激发试验1、引言随着绿色环保意识的日益加深,欧盟在2003年颁布了《关于在电子电气设备中限制使用某些有害物质指令》【1】,全球范围开始走向了无铅化的工艺流程。

电子行业中的锡铅焊料逐渐被无铅焊料代替,但随之而来的是许多新的可靠性问题,其中最典型的为锡须生长问题。

晶须是指金属表面生长出的细丝状金属,最常见的为焊锡镀层或锡焊点表面生长的锡晶须。

锡须产生的危害大致分为以下四种情况【2】:低压条件下,较小的电流可以在相邻两个不同电势区域产生持久稳定的短路;在高压条件下,可以瞬间熔断锡须造成瞬间短路;在航天器的真空环境中,锡须短路会导致金属蒸发放电,形成一个稳定的等离子电弧,使电子设备失效;在振动环境中,锡须易脱落从而引发电路短路。

1951年,Compton、Mendizza和Arnold【3】发现了锡须导致电路短路引发电容器失效的问题,将锡须正式引入人们的视场。

1986年,F15战斗机雷达因锡须产生的短路引发失效。

2000年,爱国者Ⅱ导弹由于镀锡引脚长出引发短路的锡须而出现事故【4】。

种种迹象表明锡须问题的预防将成为无铅化进程中的重要环节。

锡须生长是一个受内部应力影响的自发过程,且和外部环境条件密切相关。

本文通过三个环境试验来施加三种不同的应力,用于评估产品的抗锡须生长能力。

最大限度排除产品后续使用过程中生长锡须引发短路失效的可能。

2、试验验证2.1 常温常湿条件以Cu基底焊Sn为例,焊接完成后存放于常温常湿条件下,Cu会向Sn晶界扩散并形成金属间化合物Cu6Sn5,并相应产生压缩应力,促使锡须的形成。