实验3-6 Makefile编写实验

- 格式:doc

- 大小:53.00 KB

- 文档页数:4

Makefile的编写指导概述什么是makefile?或许很多Windows的程序员都不知道这个东西,因为那些Windows的IDE都为你做了这个工作,但我觉得要作一个好的和professional的程序员,makefile还是要懂。

这就好像现在有这么多的HTML的编辑器,但如果你想成为一个专业人士,你还是要了解HTML的标识的含义。

特别在Unix下的软件编译,你就不能不自己写makefile了,会不会写makefile,从一个侧面说明了一个人是否具备完成大型工程的能力。

因为,makefile关系到了整个工程的编译规则。

一个工程中的源文件不计数,其按类型、功能、模块分别放在若干个目录中,makefile定义了一系列的规则来指定,哪些文件需要先编译,哪些文件需要后编译,哪些文件需要重新编译,甚至于进行更复杂的功能操作,因为makefile就像一个Shell脚本一样,其中也可以执行操作系统的命令。

makefile带来的好处就是——“自动化编译”,一旦写好,只需要一个make命令,整个工程完全自动编译,极大的提高了软件开发的效率。

make是一个命令工具,是一个解释makefile中指令的命令工具,一般来说,大多数的IDE都有这个命令,比如:Delphi的make,Visual C++的nmake,Linux下GNU的make。

可见,makefile都成为了一种在工程方面的编译方法。

现在讲述如何写makefile的文章比较少,这是我想写这篇文章的原因。

当然,不同产商的make各不相同,也有不同的语法,但其本质都是在“文件依赖性”上做文章,这里,我仅对GNU的make进行讲述,我的环境是RedHat Linux 8.0,make的版本是3.80。

必竟,这个make是应用最为广泛的,也是用得最多的。

而且其还是最遵循于IEEE 1003.2-1992 标准的(POSIX.2)。

在这篇文档中,将以C/C++的源码作为我们基础,所以必然涉及一些关于C/C++的编译的知识,相关于这方面的容,还请各位查看相关的编译器的文档。

linux makefile编写规则(原创实用版)目录一、Makefile 简介二、Makefile 的规则1.目标文件2.依赖文件3.命令三、Makefile 中的变量1.通用变量2.局部变量四、Makefile 中的路径1.源文件路径2.目标文件路径3.库文件路径五、Makefile 编写实例六、总结正文一、Makefile 简介Makefile 是一个用于自动化构建和编译软件的脚本文件,通常在Linux 系统中使用。

它可以帮助开发者管理源代码,以及确定哪些文件需要编译,如何编译,以及编译后的文件如何链接。

通过编写 Makefile,开发者可以轻松地构建和维护复杂的软件项目。

Makefile 主要包括三类规则:目标文件、依赖文件和命令。

1.目标文件目标文件是 Makefile 中要生成的文件,可以是对象文件、库文件或执行文件。

在 Makefile 中,目标文件通常以“target”关键字开头,后面跟要生成的文件名。

例如:“target = main.o”。

2.依赖文件依赖文件是 Makefile 中要生成目标文件所需要的其他文件,通常是源代码文件。

在 Makefile 中,依赖文件通常以“prerequisites”关键字开头,后面跟要依赖的文件名。

例如:“prerequisites = a.c b.c”。

3.命令命令是用来生成目标文件的命令,通常是编译器或链接器。

在Makefile 中,命令通常以“command”关键字开头,后面跟要执行的命令。

例如:“command = gcc -o main.o a.c b.c”。

三、Makefile 中的变量Makefile 中的变量可以用于存储常量值,以便在 Makefile 中多次使用。

变量分为通用变量和局部变量。

1.通用变量通用变量是在整个 Makefile 中都可以使用的变量。

通用变量通常在Makefile 的开头定义,使用“define”关键字。

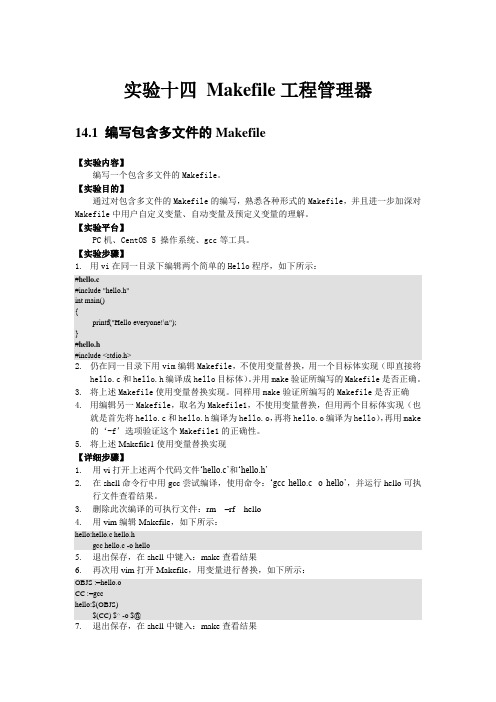

实验十四Makefile工程管理器14.1 编写包含多文件的Makefile【实验内容】编写一个包含多文件的Makefile。

【实验目的】通过对包含多文件的Makefile的编写,熟悉各种形式的Makefile,并且进一步加深对Makefile中用户自定义变量、自动变量及预定义变量的理解。

【实验平台】PC机、CentOS 5 操作系统、gcc等工具。

【实验步骤】1.用vi在同一目录下编辑两个简单的Hello程序,如下所示:#hello.c#include "hello.h"int main(){printf("Hello everyone!\n");}#hello.h#include <stdio.h>2.仍在同一目录下用vim编辑Makefile,不使用变量替换,用一个目标体实现(即直接将hello.c和hello.h编译成hello目标体)。

并用make验证所编写的Makefile是否正确。

3.将上述Makefile使用变量替换实现。

同样用make验证所编写的Makefile是否正确4.用编辑另一Makefile,取名为Makefile1,不使用变量替换,但用两个目标体实现(也就是首先将hello.c和hello.h编译为hello.o,再将hello.o编译为hello),再用make 的‘-f’选项验证这个Makefile1的正确性。

5.将上述Makefile1使用变量替换实现【详细步骤】1.用vi打开上述两个代码文件‘hello.c’和‘hello.h’2.在shell命令行中用gcc尝试编译,使用命令:‘gcc hello.c -o hello’,并运行hello可执行文件查看结果。

3.删除此次编译的可执行文件:rm –rf hello4.用vim编辑Makefile,如下所示:hello:hello.c hello.hgcc hello.c -o hello5.退出保存,在shell中键入:make查看结果6.再次用vim打开Makefile,用变量进行替换,如下所示:OBJS :=hello.oCC :=gcchello:$(OBJS)$(CC) $^ -o $@7.退出保存,在shell中键入:make查看结果8.用vim编辑Makefile1,如下所示:hello:hello.ogcc hello.o -o hellohello.o:hello.c hello.hgcc -c hello.c -o hello.o9.退出保存,在shell中键入:make –f Makefile1查看结果10.再次用vi编辑Makefile1,如下所示:OBJS1 :=hello.oOBJS2 :=hello.c hello.hCC :=gcchello:$(OBJS1)$(CC) $^ -o $@$(OBJS1):$(OBJS2)$(CC) -c $< -o $@在这里请注意区别‘$^’和‘$<’。

c语言makefile编写实例Makefile是用来管理程序编译的工具,可以方便地管理程序的编译过程。

使用Makefile可以大大简化程序的编译过程,提高程序的可维护性。

Makefile的语法比较简单,主要由目标、依赖和命令三部分组成。

下面我们以一个简单的C程序为例,来介绍如何使用Makefile进行编译。

假设我们有一个名为hello.c的程序,代码如下:```c#include <stdio.h>int main(){printf("Hello, world!\n");return 0;}```我们需要使用gcc编译器将其编译成可执行文件。

下面是一个简单的Makefile:```makefilehello: hello.cgcc -o hello hello.c```这个Makefile很简单,它定义了一个名为hello的目标,该目标依赖于hello.c文件,并使用gcc命令将其编译成可执行文件。

如果我们在终端中输入make命令,Makefile会自动执行编译过程:```$ makegcc -o hello hello.c```Makefile还可以定义多个目标,每个目标可以有多个依赖和多个命令。

下面是一个稍微复杂一些的Makefile:```makefileCC=gccCFLAGS=-Wall -gall: hello goodbyehello: hello.o$(CC) $(CFLAGS) -o hello hello.ogoodbye: goodbye.o$(CC) $(CFLAGS) -o goodbye goodbye.ohello.o: hello.c$(CC) $(CFLAGS) -c hello.cgoodbye.o: goodbye.c$(CC) $(CFLAGS) -c goodbye.cclean:rm -f *.o hello goodbye```这个Makefile定义了两个目标:all和clean。

实验二M akefile实验【实验目的】1、了解makefile的概念和构成。

2、会使用GNU make编译一个或者多个文件。

3、掌握Makefile文件的编写。

【实验条件】1、VMware虚拟机。

2、Redhat Linux平台。

【实验内容与步骤】1、使用命令编译程序在这里通过vi编译器来创建两个文件hello.c和makefile。

[hello.c]* test make file* Emdoor*#include "stdio.h"main(){printf( "wellcom emdoor!\n");}[makefile]# test for makefileCC = gccCFLAGS =all : hellohello: hello.o$(CC) $(CFLAGS) hello.o -o hellohello.o: hello.c$(CC) $(CFLAGS) -c hello.c -o hello.o clean:在将上述Makefile文件与源文件hello.c保存到同一目录之后,就可以在命令行中输入“make”命令来编译整个项目了。

make在执行过程中,首先会查找到Makefile文件第一条规则中的目标,即上述文件中的all。

根据设定好的规则,该目标需要依赖于hello。

由于all并不是一个已经存在的文件,所以每次在make被调用的时候,显然都需要先检查hello。

继续往下不难发现,hello目标是依赖于hello.o。

当make处理到目标hello.o时,会先查看其对应的依赖对象,这个以来对象是hello.c,此时就会对hello.c进行编译,得到目标文件hello.o,然后是目标文件hello.o被连接,得到可执行文件hello。

先后执行如下命令:可以看到输出结果:在Makefile中,并不是所有的目标都对应于磁盘上的文件。

有的目标存在只是为了形成一条规则,从而完成特定的工作,并不生成新的目标文件,这样的目标称为伪目标。

Python Makefile编写规则随着Python语言的流行和应用范围的不断扩大,开发人员在日常工作中经常会用到Makefile来管理代码的编译和部署过程。

Makefile 是一个用于组织代码编译和部署流程的工具,它可以帮助开发人员自动化代码构建的过程,提高工作效率。

在Python项目中,编写规范的Makefile可以帮助开发人员管理项目中繁杂的编译和部署过程,本文将介绍Python Makefile编写的规则和技巧。

一、Makefile简介Makefile是一个包含一系列规则的文件,用于指定代码的编译和部署过程。

它通常由一系列规则、依赖关系和命令组成,它告诉make命令如何编译和信息代码。

Makefile通常用于C/C++项目的编译,但在Python项目中同样有着广泛的应用。

二、Python Makefile编写规则1. 定义变量在编写Python Makefile时,首先需要定义一些变量,这些变量可以用于存储编译器、编译选项、源文件目录、目标文件目录等。

下面是一个简单的Python Makefile示例:```MakefileCC = pythonCFLAGS = -O2SRC_DIR = srcOBJ_DIR = obj```2. 定义规则在Makefile中,可以定义一系列规则来指定如何编译和信息代码。

在Python项目中,通常会定义编译规则、信息规则和清理规则。

下面是一个简单的Python Makefile示例:```Makefileall: $(OBJ_DIR)/m本人n.o$(CC) $(CFLAGS) $(OBJ_DIR)/m本人n.o -o app$(OBJ_DIR)/m本人n.o: $(SRC_DIR)/m本人n.py$(CC) $(CFLAGS) -c $(SRC_DIR)/m本人n.py -o $(OBJ_DIR)/m本人n.oclean:rm -f $(OBJ_DIR)/*.o app```在上面的示例中,定义了三个规则:all规则用于编译信息代码生成可执行文件,$(OBJ_DIR)/m本人n.o规则用于编译源文件生成目标文件,clean规则用于清理生成的目标文件和可执行文件。

手把手教你如何写Makefile陈皓 2005.04.01一、Makefile的规则在讲述这个Makefile之前,还是让我们先来粗略地看一看Makefile的规则。

target ... : prerequisites ...commandtarget也就是一个目标文件,可以是Object File,也可以是执行文件。

还可以是一个标签(Label),对于标签这种特性,在后续的“伪目标”章节中会有叙述。

prerequisites就是,要生成那个target所需要的文件或是目标。

command也就是make需要执行的命令。

(任意的Shell命令)这是一个文件的依赖关系,也就是说,target这一个或多个的目标文件依赖于prerequisites 中的文件,其生成规则定义在command中。

说白一点就是说,prerequisites中如果有一个以上的文件比target文件要新的话,command所定义的命令就会被执行。

这就是Makefile的规则。

也就是Makefile中最核心的内容。

说到底,Makefile的东西就是这样一点,好像我的这篇文档也该结束了。

呵呵。

还不尽然,这是Makefile的主线和核心,但要写好一个Makefile还不够,我会以后面一点一点地结合我的工作经验给你慢慢到来。

内容还多着呢。

:)二、一个示例正如前面所说的,如果一个工程有3个头文件,和8个C文件,我们为了完成前面所述的那三个规则,我们的Makefile应该是下面的这个样子的。

edit : main.o kbd.o command.o display.o \insert.o search.o files.o utils.occ -o edit main.o kbd.o command.o display.o \insert.o search.o files.o utils.omain.o : main.c defs.hcc -c main.ckbd.o : kbd.c defs.h command.hcc -c kbd.ccommand.o : command.c defs.h command.hcc -c command.cdisplay.o : display.c defs.h buffer.hcc -c display.cinsert.o : insert.c defs.h buffer.hcc -c insert.csearch.o : search.c defs.h buffer.hcc -c search.cfiles.o : files.c defs.h buffer.h command.hcc -c files.cutils.o : utils.c defs.hcc -c utils.cclean :rm edit main.o kbd.o command.o display.o \insert.o search.o files.o utils.o反斜杠(\)是换行符的意思。

实验三使用gcc编译器一.实验目的1、巩固vi的使用。

2、练习用Linux下gcc编译器运行c或c++程序。

3、练习使用make工具和调试工具gdb。

4、练习编写简单的c或c++程序。

二.实验内容用vi建立C++/C程序后,学习使用gcc编译器编译执行(命令格式详见实验指导书P100),查看结果。

1. helloworld程序。

2. 判断一个年份是平年还是闰年。

3. 打印九九乘法表。

三.实验步骤1、登陆Linux系统,操作方法请参考实验二。

2、使用vi编写helloworld.cpp程序(安装了vim的同学,可以输入vimhelloworld.cpp),保存。

程序代码如下:using namespace std;#include<iostream>int main(){cout<<”hello,world!\n”;return 0;}或编写helloworld.c程序,代码如下:#include<stdio.h>int main(){printf(“hello,world!\n”);return 0;}然后,利用g++ helloworld.cpp或gcc helloworld.c指令编译执行。

(如果没有任何输出提示,恭喜你,编译执行成功。

否则,会提示出错信息,请检查语法并修改。

)最后,在命令行输入 ./a.out 查看结果。

3、make工具在应用程序的开发过程中,若每次修改源文件都需要重新输入编译命令,这种做法很烦琐而且开发效率不高。

为了能快速组织源文件进行编译,linux中提供了make工具。

Make的运行过程前,必须编写Makefile文件。

它描述了软件包中文件之间的关系,提供更新每个文件的命令。

Make实验上是根据Makefile 来进行编译的。

以helloworld.c为例,编写makefile文件:helloworld:helloworld.ogcc –o helloworld helloworld.o(开头使用Tab键空格) helloworld.o:helloworld.cgcc –o helloworld.o –c helloworld.cclean:rm –f *.o hello然后,重新编译helloworld.c,命令:gcc –g helloworld.c –o helloworld 第三步,输入命令:make4、调试工具---gdb运行gdb调试程序通常的命令格式为:gdb 程序的文件名例如: gdb helloworld启动gdb调试工具后,进入gdb的调试界面。

Makefile编写规则(三)条件判断和伪⽬标Makefile编写规则(三)条件判断和伪⽬标Makefile条件判断使⽤ Makefile 编译⽂件时,可能会遇到需要分条件执⾏的情况,⽐如在⼀个⼯程⽂件中,可编译的源⽂件很多,但是它们的类型是不相同的,所以编译⽂件使⽤的编译器也是不同的。

⼿动编译去操作⽂件显然是不可⾏的(每个⽂件编译时需要注意的事项很多),所以 make 为我们提供了条件判断来解决这样的问题。

条件语句可以根据⼀个变量的值来控制 make 执⾏或者时忽略 Makefile 的特定部分,条件语句可以是两个不同的变量或者是常量和变量之间的⽐较。

注意:条件语句只能⽤于控制 make 实际执⾏的 Makefile ⽂件部分,不能控制规则的 shell 命令执⾏的过程。

下⾯是条件判断中使⽤到的⼀些关键字:关键字功能ifeq判断参数是否不相等,相等为 true,不相等为 false。

ifneq判断参数是否不相等,不相等为 true,相等为 false。

ifdef判断是否有值,有值为 true,没有值为 false。

ifndef判断是否有值,没有值为 true,有值为 false1)ideq和ifneq条件判断的使⽤⽅式如下:ifeq (ARG1, ARG2)ifeq 'ARG1' 'ARG2'ifeq "ARG1" "ARG2"ifeq "ARG1" 'ARG2'ifeq 'ARG1' "ARG2"实例:libs_for_gcc= -lgnunormal_libs=foo:$(objects)ifeq($(CC),gcc)$(CC) -o foo $(objects) $(libs_for_gcc)else$(CC) -o foo $(objects) $(noemal_libs)endif条件语句中使⽤到三个关键字“ifeq”、“else”、“endif”。

实验3-6 Makefile编写实验

【实验目的】

了解Makefile的基本概念和基本结构.

初步掌握编写简单Makefile的方法.

了解递归Make的编译过程

初步掌握利用GNU Make编译应用程序的方法

【实验步骤】

使用命令行的方式手动编译程序方法

第一步:利用文本编辑器创建hello.c文件

第二步:手动编译hello应用程序,在hello.c的目录的终端下输入:

[root@local]gcc –c hello.c

[root@local]gcc hello.o –o hello

通过ls命令查看当前目录下是否生成源代码hello.c的object文件hello.o和可执行文件hello,运行可执行文件hello。

查看一下运行结果。

[root@local]./hello

第三步:修改hello.c文件,重新手动编译应用程序。

第四步:删除hello.o和hello文件

[root@local]rm –f hello.o

[root@local]rm –f hello

利用GNU make 自动编译应用程序方法

第五步:利用文本编辑器创建一个makefile文件,并将其保存到与hello.c相同的目录下。

自己修改:$(CC) $(CFLAGS) –o hello hello.o

Hello.o:hello.c

$(CC) $(CFLAGS) –c hello.c

第六步:先后执行如下命令:

[root@local]$make

[root@local]$ls

[root@local]$./hello

查看并记录所生成的文件和运行的结果。

第七步:执行make clean命令:

[root@local]$make clean

第八步:修改hello.c文件,重复第2、3步操作,查看并记录所生成的文件和运行结果。

第九步:重新编辑makefile文件(斜黑体表示修改部分)

第十步:重复第2,3步操作,查看并记录所生成的文件和运行的结果。

比较这两种操作,写出你的结论。

同时指出$^ 、$@、$<在上述Makefile中的含义。

多个.c文件的编译

第十一步:创建文件hello1.c、hello2.c、hello.h和makefile

第十二步:先后执行如下命令

[root@local]$make

[root@local]$ls

[root@local]$./hello

查看并记录所生成的文件和运行的结果, 写出你的结论。

第十三步:修改makefile文件(斜黑体表示修改部分)

第十四步:重复第2步操作,查看并记录所生成的文件和运行的结果。