基于ADSP-TS201的/雷达恒虚警实现

- 格式:doc

- 大小:34.50 KB

- 文档页数:5

基于ADSP-TS201的大点数FFT实现穆文争;王启智;朱子平【摘要】为了解决雷达信号处理中大点数脉压问题,将一维大点数FFT拆成二维实现。

首先给出大点数FFT变换的数学原理,然后以96 K点为例,介绍了其在通用处理器ADSP-TS201的实现过程。

测试结果表明,所提出的处理方式不仅能正确实现大点数FFT变换,而且具有较好的实时性。

%In order to solve problem of great number of points pulse compression in radar signal processing, 1 di-mensional great number of points FFT can be realized by splitting it into two-dimension. The mathematical princi-ple of great number of points FFT is given firstly, then by taking 96K points as an example, the implementation process in general processor ADSP-TS201 is introduced. The test result shows that the proposed processing way not only realizes great number of points FFT correctly, but also with excellent real-time property.【期刊名称】《火控雷达技术》【年(卷),期】2014(000)002【总页数】5页(P53-57)【关键词】大点数FFT;脉压;ADSP-TS201【作者】穆文争;王启智;朱子平【作者单位】中国电子科技集团公司第三十八研究所合肥 230088;中国电子科技集团公司第三十八研究所合肥 230088;中国电子科技集团公司第三十八研究所合肥 230088【正文语种】中文【中图分类】TN957.510 引言在雷达信号处理中,FFT作为是频域脉压和谱分析的基础,是较为常用的一种变换,一般由数字信号处理器完成。

基于CPCI总线和TS201的通用雷达信号处理板设计

许月圆;李冬梅;宫慧敏

【期刊名称】《现代电子技术》

【年(卷),期】2009(32)2

【摘要】在介绍ADI公司TigerSharc系列处理器ADSP-TS201和PLX公司PCI9656这两款芯片,详细阐述处理板的整体结构和DSP与PCI9656的接口电路设计原理的基础上,提出一种ADSP-TS201基于桥芯片PCI9656实现与CPCI总线通信的雷达信号处理板的设计方案,实现RocketIO到DSP数据的高速传输,它克服了传统雷达信号处理板通用性差的缺点.

【总页数】3页(P129-131)

【作者】许月圆;李冬梅;宫慧敏

【作者单位】西安电子科技大学,陕西,西安,710071;中电集团27研究所,河南,郑州,450005;西安电子科技大学,陕西,西安,710071

【正文语种】中文

【中图分类】TP368.1

【相关文献】

1.基于TS201和FPGA的雷达信号处理运算板硬件设计 [J], 周正;李明

2.基于CPCI总线的通用FPGA信号处理板的设计 [J], 王本明;赵前晟;丁海锋;罗丰

3.基于TMS6678和XC6VLX240的通用雷达信号处理板设计 [J], 冯武;陈俊

4.基于ADSP TS201的雷达通用信号处理板的设计 [J], 弓晓颜

5.基于CPCI总线通用数字信号处理板的设计 [J], 郭高峰;郭锁喜;宋晓风

因版权原因,仅展示原文概要,查看原文内容请购买。

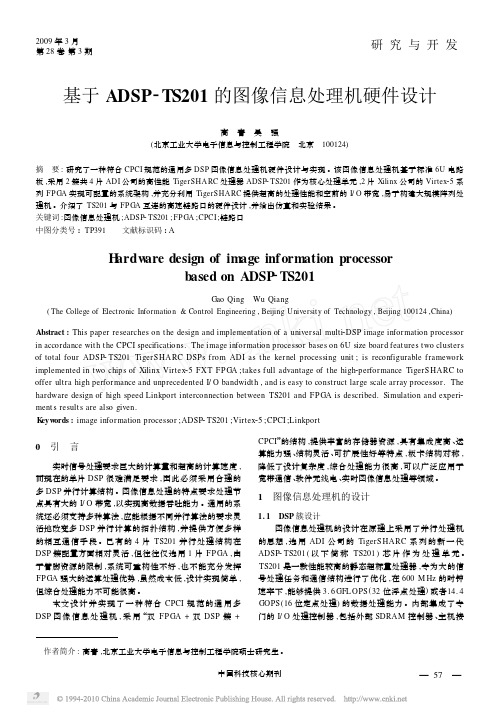

第28卷第3期基于ADSP 2TS201的图像信息处理机硬件设计高 青 吴 强(北京工业大学电子信息与控制工程学院 北京 100124)摘 要:研究了一种符合CPCI 规范的通用多DSP 图像信息处理机硬件设计与实现。

该图像信息处理机基于标准6U 电路板,采用2簇共4片ADI 公司的高性能TigerSHARC 处理器ADSP 2TS201作为核心处理单元,2片Xilinx 公司的Virtex 25系列FP GA 实现可配置的系统架构,并充分利用TigerSHARC 提供超高的处理性能和空前的I/O 带宽,易于构建大规模阵列处理机。

介绍了TS201与FP GA 互连的高速链路口的硬件设计,并给出仿真和实验结果。

关键词:图像信息处理机;ADSP 2TS201;FP GA ;CPCI ;链路口中图分类号:TP391 文献标识码:AH ardw are design of im age inform ation processor based on ADSP 2TS201Gao Qing Wu Qiang(The College of Electronic Information &Control Engineering ,Beijing University of Technology ,Beijing 100124,China )Abstract :This paper researches on t he design and implementation of a universal multi 2DSP image information processor in accordance wit h t he CPCI specifications.The image information processor bases on 6U size board feat ures two clusters of total four ADSP 2TS201TigerSHARC DSPs from ADI as t he kernel processing unit ;is reconfigurable framework implemented in two chip s of Xilinx Virtex 25FXT FP GA ;takes full advantage of t he high 2performance TigerSHARC to offer ultra high performance and unprecedented I/O bandwidt h ,and is easy to construct large scale array processor.The hardware design of high speed Linkport interconnection between TS201and FP GA is described.Simulation and experi 2ment s result s are also given.K eyw ords :image information processor ;ADSP 2TS201;Virtex 25;CPCI ;Linkport 作者简介:高青,北京工业大学电子信息与控制工程学院硕士研究生。

基于ADSP TS201的雷达信号处理机设计

现代雷达信号处理已成为雷达功能实现的关键,本文按照某型雷达信号处理机的系统需要,对其硬件结构及软件设计做了系统优化。

设计了1套以4片TS201和1片为核心信号处理板,该系统仅用l副板卡即实现空时二维信号处理。

实现了自适应副瓣相消,4路脉冲压缩与MTI/MTD,副瓣匿影和差波束测角等算法,可以完成对目标距离,方位偏差量的测算,满足系统需求。

1 系统组成分析

回波信号在天线上举行部分微波合成,形成和、差通道信号及两路辅助天线信号,举行IQ正交插值,1/8抽取后,形成4路待测数据,数据率共为128MB/s。

系统算法结构,1所示,主要由旁瓣相消模块,数字脉压模块,MTD处理模块由3部分组成。

和路信号MTD(FFT-CFAR)后经副瓣匿影若判定有目标则再由和、差两路数据计算方位偏差量。

以雷达工作的低重频模式为例,IQ数据为5 388点,重频为140 Hz,考虑到一定的时光余量,4路信号的传输及处理必需在<6.7 ms的时光内完成。

因此系统的数据速率、数据量及运算规模打算了系统设计必需具有以下特点:

(1)具有高性能浮点处理芯片,可完成旁瓣相消、脉冲压缩、相参堆积、杂波图、恒虚警处理。

(2)内部各处理芯片间可举行高速数据传递且可外部扩展存储芯片,保存大量数据。

(3)具备对外的数据接口和控制接口,并可输出故障检测信号。

(4)软件设计中必需举行大量优化,保证上述全部处理模块在1个脉冲周期内完成。

2 雷达处理机实现

2.1 硬件平台设计

系统运算量准时间要求,信号处理板需采纳多并行处理的结构,为达

第1页共5页。

基于ADSP-TS201的实时SAR成像研究杜江;李芬芬;梁毅;邢孟道【摘要】SAR成像具有数据率高、数据量大、算法复杂、处理实时性较难保证的特点.目前随着大容量、高速并行计算机技术的迅速发展,成像雷达信号处理实时性问题的研究获得了很大的发展.介绍了一种基于ADSP-TS201实时信号处理系统的体系结构和SAR实时成像算法流程,最后通过试验论证了该方法的正确性.【期刊名称】《现代电子技术》【年(卷),期】2008(031)009【总页数】4页(P38-40,44)【关键词】SAR成像;实时处理;并行处理;ADSP-TS201【作者】杜江;李芬芬;梁毅;邢孟道【作者单位】西安电子科技大学,雷达信号处理国家重点实验室,陕西,西安,710071;西安电子科技大学,雷达信号处理国家重点实验室,陕西,西安,710071;西安电子科技大学,雷达信号处理国家重点实验室,陕西,西安,710071;西安电子科技大学,雷达信号处理国家重点实验室,陕西,西安,710071【正文语种】中文【中图分类】TN41;TP331 引言SAR(合成孔径雷达)具有全天候、全天时、远距离、高分辨成像等特点,可以大大提高雷达的信息获取能力,特别是信息感知能力。

SAR成像可以获取高分辨率的图像,近年来受到了很大重视,在军用和民用方面都得到了广泛的应用和发展。

雷达成像经常用到许多经典的信号处理算法,比如滤波(FIR、IIR)、FFT、IFFT、相关算法等。

对于这些算法的实现,高速DSP芯片成了首选实时信号处理器件。

近年来,DSP性能不断提升,应用领域不断增强。

目前主流DSP制造商所生产的DSP已能满足算法复杂、运算速度高、寻址方式灵活和通信性能强大等需求。

高端的DSP生产商主要包括TI、Motorola和ADI。

其性能都有各自的优点,其中,ADI的TigerSHARC201的浮点处理能力达到3.6 GFLOP,内核时钟600 MHz,同时兼容定点运算,并且在内部结构上采用双处理器核,支持SIMD处理方式,是雷达信号处理领域理想的处理器。

基于ADSP-TS201S的雷达信号处理研究张泽云;赵宏生;徐朝阳【期刊名称】《舰船电子对抗》【年(卷),期】2011(034)003【摘要】介绍了ADI公司数字信号处理(DSP)芯片ADSP-TS201S的主要性能以及雷达信号处理的主要功能和算法,以雷达信号处理中常用的快速傅里叶变换(FFT)算法为例,结合TS201S的结构特点,讨论了如何通过优化软件编程的方法来缩短算法执行时间以满足系统实时性的要求,体现了TS201S对算法适应性强、程序调试方便、可靠性高的优点。

%This paper introduces the main performance of the digital signal processing(DSP) chip ADSP-TS20-1S of Analog Device Inc,the main function and algorithms of radar signal processing,taking the common fast Fourier transform(FFT) algorithm in the radar signal【总页数】4页(P46-48,57)【作者】张泽云;赵宏生;徐朝阳【作者单位】船舶重工集团公司723所,扬州225001;船舶重工集团公司723所,扬州225001;船舶重工集团公司723所,扬州225001【正文语种】中文【中图分类】TN957.51【相关文献】1.基于ADSP-TS201S的调频连续波雷达信号处理系统 [J], 曲昱;史林2.基于ADSP-TS201的实时SAR成像研究 [J], 杜江;李芬芬;梁毅;邢孟道3.基于Zynq的雷达信号处理系统的研究 [J], 赵蔚;王安印4.基于高性能计算的雷达信号处理研究综述 [J], 耿昭谦;朱虎明;李旭明;陈梅青;杨贵鹏5.基于ADSP-TS201S的通用雷达信号处理机的设计 [J], 顾颖;张雪婷;张飚因版权原因,仅展示原文概要,查看原文内容请购买。

恒虚警性能分析及在DSP芯片上的实现裴鑫;田孝华;李思佳【摘要】CFAR detection of radar targets in heavy clutter background is an important part in radar signal processing. But the research in the particular situation of airport is few. In order to provide a fit algorithm of CFAR. In this paper, first the principle of radar CFAR detection in Gauss distributed clutter ia discussed, then compared among four arrangements, the characteristics of ADSP- TS201 are introduced, and the way of realizing radar CFAR detection in clutter background based on ADSP-TS201 is proposed, and the results of simulation are provided at last.%强杂波背景中的雷达目标恒虚警检测是雷达信号处理的重要组成部分;在机场等特殊环境下的应用成为相关课题的研究对象;为了提供适于机场环境下的恒虚警处理算法,首先讨论了高斯杂波背景中雷达目标恒虚警检测的原理,然后对比分析了四种处理方案,并且介绍了数字信号处理芯片ADSP TS201的主要特点,针对机场环境阐述了基于数字信号处理芯片ADSP-TS201实现高斯杂波背景中雷达目标恒虚警检测的方法,最后采取机场实测信号实验结果验证,结果目标准确显示达到预期目标.【期刊名称】《计算机测量与控制》【年(卷),期】2011(019)012【总页数】4页(P3019-3022)【关键词】恒虚警;TS201;信号检测【作者】裴鑫;田孝华;李思佳【作者单位】空军工程大学电讯工程学院,陕西西安710077;空军工程大学电讯工程学院,陕西西安710077;空军工程大学电讯工程学院,陕西西安710077【正文语种】中文【中图分类】TN711.1;TN915.070 引言恒虚警率是雷达信号处理设备的主要战术技术指标之一[1]。

基于ADSP-TS201的/雷达恒虚警实现

2009-09-04 17:55:18 作者:来源:浏览次数:18 文字大小:【大】【中】【小】

1 引言

雷达恒虚警(CFAR-Constant False Alarm Rate)在雷达系统中有着重要的作用和地位。

恒虚警处理可以避免杂波变化影响的检测阈值,提高雷达在各种干扰情况下的检测能力。

美国模拟器件公司(ADD的ADSP-TS201处理器具有高速运算能力、可时分复用、并行处理、数据吞吐率高等特点。

该处理器片内集成大容量存储器,性价比高,并兼有ASIC 和FPGA的信号处理性能、指令集处理器的高度可编程性与灵活性,适用于高性能、大存储量的信号处理和图像应用。

本文主要讨论基于ADSP-TS201的恒虚警实现方法。

2 ADSP-TS201简介

ADSP-TS201采用超级哈佛结构,静态超标量操作适合多处理器模式运算,可直接构成分布式并行系统和共享存储式并行系统。

ADSP-TS201的主要性能指标如下:

最高工作主频600 MHz(1.67 ns指令周期);

支持IEEE浮点格式32 bit数据和40 bit扩展精度浮点格式。

同时支持8/16/32/64 bit 的定点数据格式;

允许128 bit的数据、指令和I/O端口访问,内部存储器带宽33.6 GB/s;

32 bit的地址总线提供4 G的统一寻址空间;

14通道的DMA控制器支持硬件和软件中断,支持优先级中断和嵌套中断;

4个全双工LINK端口支持最达500 MB/s的传输速度;

JTAG仿真接口允许多片DSP仿真。

3 ADSP-TS201与TS101性能比较

ADSP-TS201与ADSP-TS101相比,主要在运行速度、存储器结构和链路口结构上有差别,如表1所列。

通过比较可以看出ADSP-TS201的性能比较好,故选用ADSP-TS201实现雷达恒虚警检测。

4恒虚警检测原理

4.1选大单元平均CFAR(GO-CFAR)

云雨杂波和低分辨率雷达的海浪和地物杂波的包络服从瑞利分布,其概率密度函数为:

门限VT一旦确定,背景噪声(干扰)和杂波干扰会使虚警概率增加,因此恒虚警处理十分必要。

杂波干扰环境通常采用单元平均恒虚警。

实际工程中为了消除杂波边缘内侧虚警显著增大,采用选大单元平均恒虚警。

选大单元平均CFAR通过两侧2L个距离单元数据平均值估算杂波功率,用杂波功率对所检测的距离单元数据进行归一化并乘以门限,作为检测门限。

检测门限与检测单元比较,超过门限判断为有目标,低于门限判断为无目标。

4.2杂波图

杂波图可认为是CFAR中的一种,采用参考样本估计杂波电平。

将雷达周围的二维平面划分成许多方位距离单元,再将每个方位距离单元的接收信号存入存储器,每个存储单

元对应一个方位距离单元。

一个杂波图单元可以由一个或几个分辨单元组成。

按照不同的距离和不同的波位计算并存储杂波图,利用杂波图数据设置门限并与雷达回波相比较,检测低速目标。

杂波图分为动态杂波图和静态杂波图。

静态杂波图是在雷达建站时或者定期对雷达周围的杂波环境进行测量,静态杂波图对雷达回波信号按照特定公式进行归一化处理,一般用于接收机控制增益。

而动态杂波图随着天线扫描,每个方位单元存储的信号递归更新,天线多圈扫描后,幅度杂波图存储相应方位距离单元的杂波均值。

检测门限为相应方位距离单元杂波均值与门限之积。

如果被检测信号大于门限,则判为有目标,否则判为无目标。

5 恒虚警在ADSP-TS201上的实现

5.1运算量、存储量分析及时间估计

首先分析选大单元平均CFAR的运算量和时间。

以某一重复频率为例(重复频率为184μs,无模糊距离为27.6 km),整个距离的数据量约为3.6 K个32 bit的字。

处理一帧数据的时间约185.5 ms。

经多普勒补偿后数据量翻倍,实际处理一帧数据(定浮点转换、取模、CFAR)的时间约为314.5 ms。

因此仅用一片ADSP-TS201是无法实现的。

然后分析杂波图的存储量。

将雷达周围的二维平面划分为6个扫描区,每个扫描区有91个波位,每个波位存10层(前后各5层)杂波数据。

若一个杂波图单元由2个分辨单元组成,则一个杂波图单元存储16 bit,一个扫描区最大存储量约为30 M,ADSP-TS201内存不能存储杂波图数据。

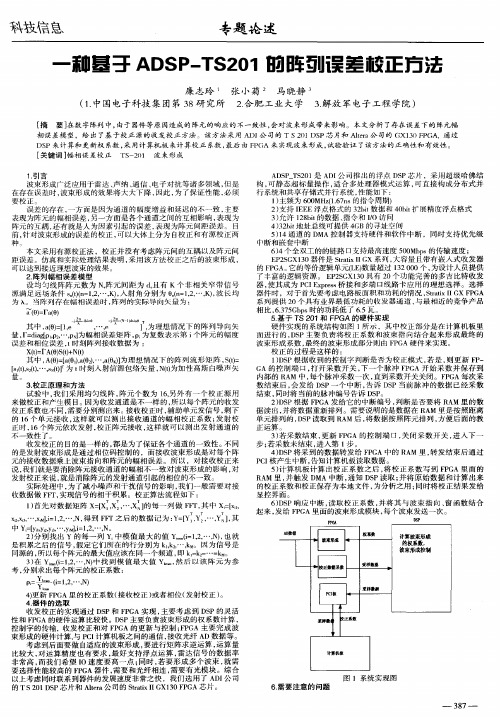

5.2硬件实现

采用两片ADSP-TS201实现硬件设计,每个处理器都连接一个32 MB×16 bit的SDRAM。

硬件连接图如图1所示。

图中,L表示链路口;F表示FLAG引脚;I表示外部中断引脚;IO表示输入输出引脚;DATA表示数据口。

DSP1与Flash相连接用于启动,DSP2与FPGA连接用于接收来自FPGA脉压后的复数数据。

两个处理器之间的点对点通信是通过链路口互联实现的,每个链路口以双向全双工方式工作。

两个DSP各自连接SDRAM用于存储杂波图数据。

DSP1采用EPROM加载方式,DSP2通过链路口加载。

5.3软件实现

软件设计主要实现:定浮点转换、取模、杂波图检测以及CFAR处理。

每部分程序都是一个子程序,便于调用、调试。

考虑到实时性要求,程序采用汇编语言,片内利用ADSP-TS201的X,Y双运算块并行运算。

由于选大单元平均CFAR处理要对两侧L个临近单元求和,取模可直接求和,把取模和CFAR用一个子程序完成,减少了读取数据的时间。

图2、图3分别为DSP1、DSP2的软件处理流图。

DSP1主要完成加载,频率通道号为奇数行数据的杂波图检测和CFAR,并将一帧数据检测到的目标信息发送给接口板。

DSP1的链路口3与接口板相连,将合并后的结果送给接口板用于模糊。

DSP2接收来自FPGA脉压后的数据,将频率通道号为奇数的数据发送至DSP1,偶数行数据DSP2自行处理。

一帧数据处理结束,DSP2将检测到的目标信息送至DSP1,经DSP1合并后再送出。

6系统仿真结果

软硬件设计完成后,进行功能测试。

图4是背景杂波服从瑞利分布时,采用ADSP-TS201汇编语言对整个雷达目标恒虚警检测过程仿真得到的结果。

采样点数为1 024点。

需要指出的是,恒虚警检测算法会带来不同程度的恒虚警损失,与邻近单元的个数L 和积累周期数有关,因此在实现时要尽量减小恒虚警损失。

7 结束语

介绍了在ADSP-TS201上实现杂波背景中雷达目标的恒虚警检测方法,具体讨论了实现过程中软硬件设计,并给出了系统仿真结果。