第8章数字集成电路晶体管级设计.

- 格式:ppt

- 大小:1.44 MB

- 文档页数:63

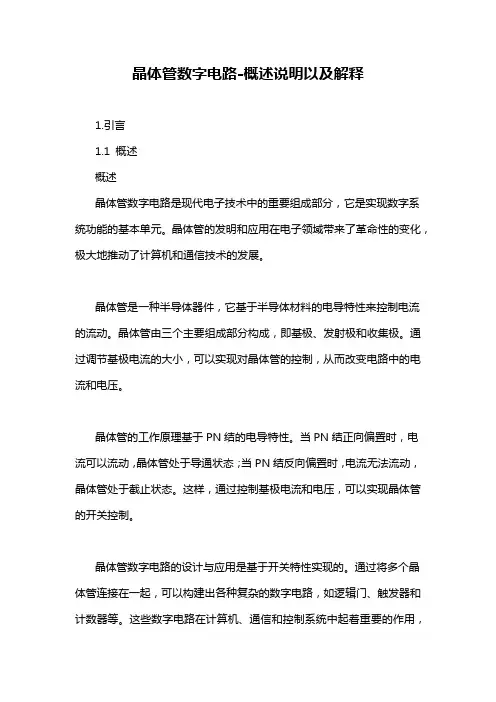

晶体管数字电路-概述说明以及解释1.引言1.1 概述概述晶体管数字电路是现代电子技术中的重要组成部分,它是实现数字系统功能的基本单元。

晶体管的发明和应用在电子领域带来了革命性的变化,极大地推动了计算机和通信技术的发展。

晶体管是一种半导体器件,它基于半导体材料的电导特性来控制电流的流动。

晶体管由三个主要组成部分构成,即基极、发射极和收集极。

通过调节基极电流的大小,可以实现对晶体管的控制,从而改变电路中的电流和电压。

晶体管的工作原理基于PN结的电导特性。

当PN结正向偏置时,电流可以流动,晶体管处于导通状态;当PN结反向偏置时,电流无法流动,晶体管处于截止状态。

这样,通过控制基极电流和电压,可以实现晶体管的开关控制。

晶体管数字电路的设计与应用是基于开关特性实现的。

通过将多个晶体管连接在一起,可以构建出各种复杂的数字电路,如逻辑门、触发器和计数器等。

这些数字电路在计算机、通信和控制系统中起着重要的作用,实现了数字信号的处理和转换。

晶体管数字电路的重要性不仅体现在其在计算机领域的广泛应用,还在于其在推动技术进步和社会发展方面的影响。

晶体管的小巧、高可靠性和低功耗等特点,使得数字电路可以更加紧凑和高效。

晶体管数字电路的快速发展也催生了计算机和通信技术的迅猛发展,为人类社会的进步做出了巨大贡献。

展望未来,晶体管数字电路仍然具有广阔的发展空间。

随着科技的不断进步,晶体管的尺寸会越来越小,集成度会越来越高,功耗会越来越低。

同时,晶体管数字电路的应用领域也将不断扩展,涵盖更多的领域和行业,如物联网、人工智能和新能源等。

总之,晶体管数字电路作为现代电子技术的基础,具有重要的应用价值和发展前景。

通过深入研究晶体管基础知识和工作原理,不断探索和创新晶体管数字电路的设计与应用,我们可以为推动技术进步和社会发展做出更大的贡献。

文章结构部分的内容可参考以下写法:1.2 文章结构本文主要分为引言、正文和结论三个部分。

在引言部分,我们将概述晶体管数字电路的重要性及其应用领域,并阐述本文的目的。

晶体管电路设计

晶体管是一种使用半导体材料制成的电子器件,广泛应用于电子设备中。

晶体管电路设计主要包括放大电路、开关电路和逻辑电路等。

下面以放大电路为例,简要介绍晶体管电路的设计过程。

首先,放大电路旨在将输入信号经过放大器放大后输出,一般需要确定放大器的增益、频率响应和电压偏置等参数。

以共射极放大电路为例,设计步骤如下:

1. 确定放大器的电压供应范围,一般为芯片规格提供的电源电压范围,如5V。

2. 确定放大器的输入电阻和输出电阻,一般根据应用需要确定,一般情况下,输入电阻应该大于输出电源才能更好地适应各种输入信号源,输出电阻则应该小于输入信号源。

3. 选择合适的晶体管型号和工作点。

根据应用要求选择合适的晶体管型号,根据电压供应范围、放大器工作点和输入输出电阻来确定最佳的工作点。

4. 计算放大器的增益。

根据晶体管的静态特性参数以及放大电路的拓扑结构计算放大器的增益。

5. 考虑反馈和补偿。

根据放大器的稳定性要求选择恰当的补偿电路和反馈电阻。

6. 优化设计并进行仿真。

对设计的放大电路进行电路的仿真和优化,验证其性能和稳定性。

7. PCB布线。

根据原理图进行PCB布线设计,注意电路的电磁兼容性和信号完整性。

8. 调试和测试。

将设计好的放大电路进行调试和测试,以保证性能和稳定性。

通过以上设计步骤,可以设计出满足需求的晶体管放大电路。

当然,设计晶体管电路还需要考虑众多因素,如噪声、功耗、温度稳定性等,在实际设计中还需要更加细致的考虑和优化。

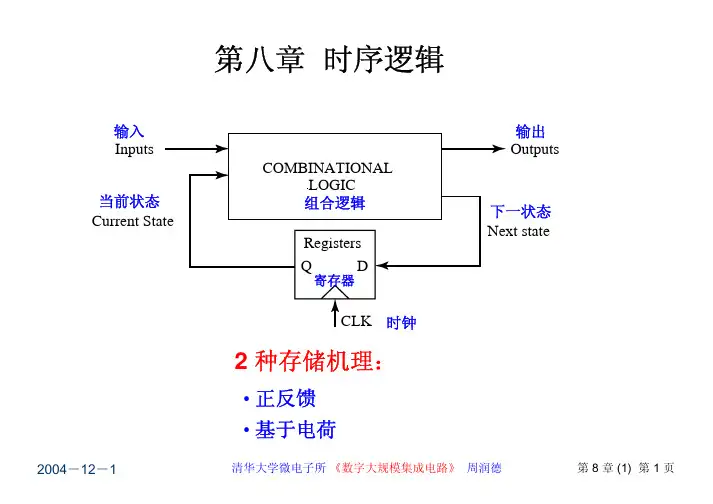

LOGIC对扰动不敏感(2)Register寄存器为存放二进制数据的器件,通常由Latch 构成。

一般地,寄存器为边沿触发。

(3)flip-flops(触发器)任何由交叉耦合的门形成的双稳电路Register 时序参数D Q Clk T Clk D tsu Q tc-q thold注意:数据的上升和下降时间不同时,延时将不同。

2004-12-1清华大学微电子所 《数字大规模集成电路》 周润德 第 8 章 (1) 第 11 页Latch 时序参数Latch 的时序( Timing )参数还要考虑tD 2 D Q DQtD-qQClkClktC 2QtC 2Q寄存器(Register)2004-12-1锁存器(Latch)第 8 章 (1) 第 12 页清华大学微电子所 《数字大规模集成电路》 周润德Latch 时序参数D Q Clk正电平 Latch 时钟负边沿T Clk D tc-q PWm thold td-q tsuQ注意:数据的上升和下降时间不同时,延时将不同。

2004-12-1清华大学微电子所 《数字大规模集成电路》 周润德 第 8 章 (1) 第 13 页最高时钟频率φ FF’s LOGIC tp,comb最高时钟频率需要满足:tclk-Q + tplogic+ tsetup < T =但同时需要满足:其中tplogic = tp,comb (max) tcd:污染延时(contamination delay) = 最小延时(minimum delay)第 8 章 (1) 第 14 页tcdreg + tcdlogic > thold =2004-12-1其中清华大学微电子所 《数字大规模集成电路》 周润德研究不同时刻 (t1, t2)FF1φ (t1) LOGIC t p,combφ (t2)CLKt1tsu D tholdFF1 输入数据 应保持稳定t tsuF F2t2holdtFF2 输入数据 应保持稳定tclk-q QFF1 输出数据 经组合逻辑到达 t 已达稳定 寄存器输入端tclk-Qtp,comb (max)tsetup因此要求:tclk-Q + tp,comb (max) + tsetup < T =2004-12-1清华大学微电子所 《数字大规模集成电路》 周润德 第 8 章 (1) 第 15 页研究同一时刻 (t1)t1 时FF1φ (t1) LOGIC FF1 t p,combt1 时FF2输入数据(2)φ (t1)输入数据(1)tclk-q QFF1 输出数据 已达稳定经组合逻辑已 到达FF2 输入端破坏了本应保 持的数据(2)tt1tcdregtcdlogicholdsuD输入数据(2)应保持稳定至 t1F F2t因此要求 := tcd: 污染延时(contamination delay) = 最小延时(minimum delay)2004-12-1清华大学微电子所 《数字大规模集成电路》 周润德 第 8 章 (1) 第 16 页tcdreg + tcdlogic > thold写入(触发)静态 Latch 的方法:以时钟作为隔离信号, 它区分了“透明” (transparent )和“不透明” (opaque)状态CLKCLKQ CLKD CLKDD弱反相器CLKMUX 实现弱反相器实现(强制写入)(控制门可仅用NMOS实现)2004-12-1清华大学微电子所 《数字大规模集成电路》 周润德第 8 章 (1) 第 17 页Latch 的具体实现基于Mux 的 Latch负(电平) latch (CLK= 0 时透明) 正(电平) latch (CLK= 1 时透明)1 D 0Q D0 1QCLKCLKQ = Clk ⋅ Q + Clk ⋅ In2004-12-1Q = Clk ⋅ Q + Clk ⋅ In第 8 章 (1) 第 18 页清华大学微电子所 《数字大规模集成电路》 周润德基于(传输门实现的) Mux 的 LatchCLKQ CLK DCLK(1)尺寸设计容易 (2)晶体管数目多(时钟负载因而功耗大)2004-12-1清华大学微电子所 《数字大规模集成电路》 周润德 第 8 章 (1) 第 19 页基于(传输管实现)Mux 的 Latch(仅NMOS 实现)CLK QM QM CLK CLKCLK仅NMOS 实现不重叠时钟 (Non-overlapping clocks)(1)仅NMOS 实现,电路简单,减少了时钟负载 (2)有电压阈值损失(影响噪声容限和性能,可能引起静态功耗)2004-12-1清华大学微电子所 《数字大规模集成电路》 周润德 第 8 章 (1) 第 20 页Q单元形式的Latch采用串联电压开关逻辑(CVSL)QNon-overlap时间过长,存储在动态节点上的电荷会泄漏掉(故称伪静态)低电压静态Latch双边沿触发寄存器RS Latch?动态Latch 和Register(1)比静态Latch和Register 简单(2)基于在寄生电容上存储电荷,由于漏电需要周期刷新(或经常更新数据)(3)不破坏的读信息:因此需要输入高阻抗的器件传输门构成的动态边沿触发寄存器(只需8 个晶体管,节省功耗和提高性能,甚至可只用NMOS 实现)动态节点。

CMOS数字集成电路:分析与设计(第三版)(中文版)佚名

【期刊名称】《电气电子教学学报》

【年(卷),期】2006(28)3

【摘要】内容简介:本书集中讲述CMOS数字集成电路,反映现代技术的发展水平,提供电路设计的最新资料。

本书共有15章。

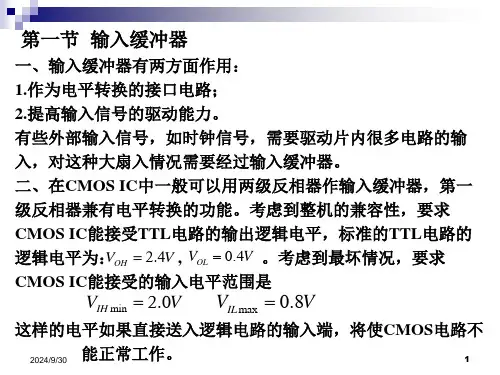

前半部分详细讨论MOS晶体管相关特性和工作原理、基本反相器电路设计、组合逻辑电路及时序逻辑电路的结构与工作原理。

后半部分介绍应用于先进VLSI芯片设计的动态逻辑电路,先进的半导体存储电路,低功耗MCMOS逻辑电路,双极性晶体管基本原理和BiCMOS数字电路设计,芯片的I/O设计,电路的可制造性设计和可测试性设计等问题。

【总页数】1页(P44-44)

【关键词】CMOS数字集成电路;分析与设计;中文版;第三版;数字电路设计;CMOS 逻辑电路;时序逻辑电路;工作原理;MOS晶体管;组合逻辑电路

【正文语种】中文

【中图分类】TN79;TM44

【相关文献】

1.CMOS数字集成电路I/O单元设计分析 [J], 刘艳艳;耿卫东;代永平;孙钟林

2.基于CMOS工艺的中小规模数字集成电路设计浅析 [J], 孙玲;陈海进

3.高温CMOS数字集成电路的瞬态特性分析 [J], 柯导明;柯晓黎

4.《CMOS数字集成电路:分析与设计》课程教学探索 [J], 陈伟中;贺利军;黄义;周

前能;杨虹

5.CMOS数字集成电路的低功耗设计 [J], 陈光胜;张旭;沈力为

因版权原因,仅展示原文概要,查看原文内容请购买。

集成电路设计基础_华中科技大学中国大学mooc课后章节答案期末考试题库2023年1.画小信号等效电路时,恒定电流源视为。

答案:开路2.模拟集成电路设计中可使用小信号分析方法的是。

答案:增益3.模拟集成电路设计中可使用大信号分析方法的是()。

答案:输出摆幅4.题1-1-1 中国高端芯片联盟正式成立时间是:。

答案:2016年7月5.题1-1-2 如下不是集成电路产业特性的是:。

答案:低风险6.题1-1-3 摩尔定律是指集成电路上可容纳的晶体管数目,约每隔:个月便会增加一倍,性能也将提升一倍。

答案:187.MOS管的小信号模型中,体现沟长调制效应的参数是()。

答案:8.工作在饱和区的MOS管,可以被看作是一个。

答案:电压控制电流源9.下图中的MOS管工作在区(假定Vth=0.7V)。

【图片】答案:饱和区10.一个MOS管的本征增益表述错误的是。

答案:与MOS管电流无关11.工作在区的MOS管,其跨导是恒定值。

答案:饱和12.MOS管中相对最大的寄生电容是。

答案:栅极氧化层电容13.MOS管的小信号输出电阻【图片】是由MOS管的效应产生的。

答案:沟长调制14.题1-1-4 摩尔定律之后,集成电路发展有三条主线,以下不是集成电路发展主线的是:。

答案:SoC15.题1-1-5 单个芯片上集成约50万个器件,按照规模划分,该芯片为:。

答案:VLSI16.题1-1-6 年发明了世界上第一个点接触型晶体管。

答案:194717.题1-1-7 年发明了世界上第一块集成电路。

答案:195818.题1-1-8 FinFET等多种新结构器件的发明人是:。

答案:胡正明19.题1-1-9 集成电路代工产业的缔造者:。

答案:张忠谋20.题1-1-10 世界第一块集成电路发明者:。

答案:基尔比21.MOS管一旦出现现象,此时的MOS管将进入饱和区。

答案:夹断22.MOS管从不导通到导通过程中,最先出现的是。

答案:耗尽23.在CMOS模拟集成电路设计中,我们一般让MOS管工作在区。

第一章 数字集成电路介绍第一个晶体管,Bell 实验室,1947第一个集成电路,Jack Kilby ,德州仪器,1958 摩尔定律:1965年,Gordon Moore 预言单个芯片上晶体管的数目每18到24个月翻一番。

(随时间呈指数增长)抽象层次:器件、电路、门、功能模块和系统 抽象即在每一个设计层次上,一个复杂模块的内部细节可以被抽象化并用一个黑匣子或模型来代替。

这一模型含有用来在下一层次上处理这一模块所需要的所有信息。

固定成本(非重复性费用)与销售量无关;设计所花费的时间和人工;受设计复杂性、设计技术难度以及设计人员产出率的影响;对于小批量产品,起主导作用。

可变成本 (重复性费用)与产品的产量成正比;直接用于制造产品的费用;包括产品所用部件的成本、组装费用以及测试费用。

每个集成电路的成本=每个集成电路的可变成本+固定成本/产量。

可变成本=(芯片成本+芯片测试成本+封装成本)/最终测试的成品率。

一个门对噪声的灵敏度是由噪声容限NM L (低电平噪声容限)和NM H (高电平噪声容限)来度量的。

为使一个数字电路能工作,噪声容限应当大于零,并且越大越好。

NM H = V OH - V IH NM L = V IL - V OL 再生性保证一个受干扰的信号在通过若干逻辑级后逐渐收敛回到额定电平中的一个。

一个门的VTC 应当具有一个增益绝对值大于1的过渡区(即不确定区),该过渡区以两个有效的区域为界,合法区域的增益应当小于1。

理想数字门 特性:在过渡区有无限大的增益;门的阈值位于逻辑摆幅的中点;高电平和低电平噪声容限均等于这一摆幅的一半;输入和输出阻抗分别为无穷大和零。

传播延时、上升和下降时间的定义传播延时tp 定义了它对输入端信号变化的响应有多快。

它表示一个信号通过一个门时所经历的延时,定义为输入和输出波形的50%翻转点之间的时间。

上升和下降时间定义为在波形的10%和90%之间。

对于给定的工艺和门的拓扑结构,功耗和延时的乘积一般为一常数。