AD7951 引脚功能中文说明(14Bit,1MSPS)

- 格式:docx

- 大小:21.33 KB

- 文档页数:3

AN-1367应用笔记One Technology Way•P.O.Box9106•Norwood,MA02062-9106,U.S.A.•Tel:781.329.4700•Fax:781.461.3113•图1. 实验室设置1 3 3 3 8 -0 0 1EVAL-ADE7953I2C USB TO UART 1, 2, 3, OR 4 BYTESINTERNAL REGISTER ACCESSEVAL-ADuCM360(Cortex-M3)ADE7953和ADuCM360之间的I2C接口作者:Fermi Lim,Daniel Kim,Hariharan Mani简介本应用笔记说明了如何使用C语言来实现在ADE7953(从机)和ADuCM360(主机)之间实现I2C接口通信。

ADE7953是一个单相电能计量IC,而ADuCM360是一个基于ARM® Cortex®-M3的微控制器。

ADE7953包含8位、16位、24位以及32位长的寄存器。

编写源代码时,必须确保依据寄存器的地址来识别读/写操作的数据大小。

ADE7953数据手册中的寄存器清单包含全部相关信息。

此应用笔记介绍了ARM Cortex-M3内核和ADuCM360微控制器(MCU),接着介绍了需要在ADuCM360中完成的初始化步骤,最后介绍了在ADE7953和ADuCM360之间如何实现I2C接口。

在此应用笔记中所描述的示例代码也可以用在其他基于ARM Cortex-M内核的ADI处理器中。

用于建立I2C接口的完整源代码以可下载文件的形式(AN_1367_I2C_interface.zip)提供,网址为/ ADE7953或www.analogcom/ADuCM360。

本应用笔记说明了如何在Visual C++ 2012集成开发环境(IDE)中实现源代码,并为ADE7953和ADuCM360之间的I2C通讯端口提供了有用的见解。

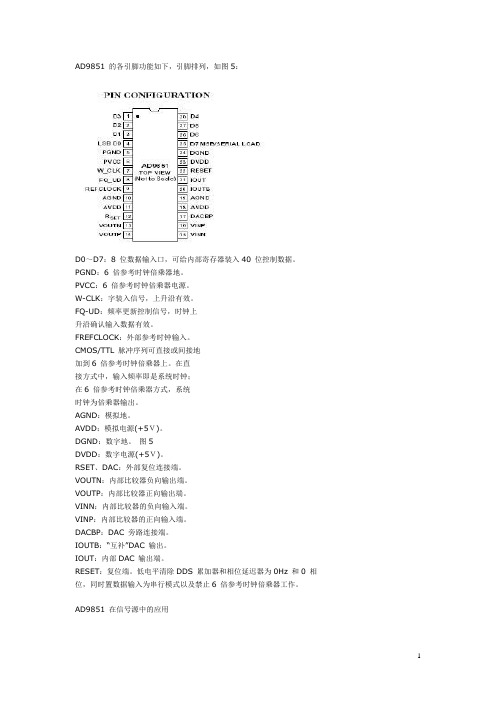

AD9851 的各引脚功能如下,引脚排列,如图5:D0~D7:8 位数据输入口,可给内部寄存器装入40 位控制数据。

PGND:6 倍参考时钟倍乘器地。

PVCC:6 倍参考时钟倍乘器电源。

W-CLK:字装入信号,上升沿有效。

FQ-UD:频率更新控制信号,时钟上升沿确认输入数据有效。

FREFCLOCK:外部参考时钟输入。

CMOS/TTL 脉冲序列可直接或间接地加到6 倍参考时钟倍乘器上。

在直接方式中,输入频率即是系统时钟;在6 倍参考时钟倍乘器方式,系统时钟为倍乘器输出。

AGND:模拟地。

AVDD:模拟电源(+5V)。

DGND:数字地。

图5DVDD:数字电源(+5V)。

RSET、DAC:外部复位连接端。

VOUTN:内部比较器负向输出端。

VOUTP:内部比较器正向输出端。

VINN:内部比较器的负向输入端。

VINP:内部比较器的正向输入端。

DACBP:DAC 旁路连接端。

IOUTB:“互补”DAC 输出。

IOUT:内部DAC 输出端。

RESET:复位端。

低电平清除DDS 累加器和相位延迟器为0Hz 和0 相位,同时置数据输入为串行模式以及禁止6 倍参考时钟倍乘器工作。

AD9851 在信号源中的应用为了能够完成调频、调幅、调相的各种功能,要向AD9851 输入频率/相位控制字,这是通过AD9851 和微处理器相连接来实现。

可以和AD9851 的数据线直接相连接的单片机类型很多,本文中选用的是Atmel公司生产的单片机AT89S5 1,如图6所示,为AT89S51和AD9851的硬件串行接口框图。

当然也可以选用AT89S52、MCS51、AD9851、AD9850 等。

AD9851 在本系统的应用电路由于AD9851 是贴片式的体积非常小,引脚排列比较密,焊接时必须小心,还要防静电,焊接不好就很容易把芯片给烧坏。

还有在使用中数据线、电源等接反或接错都很容易损坏芯片。

所以在AD9851外围采用了电源、输入、输出、数据线的保护电路。

AD9851中文数据手册By Hi_Cracker @whuCMOS180 MHzDDS / DAC合成器---------- AD9851FEATURES180 MHz的时钟速率可选6*参考时钟片上高性能10位DAC和高速滞回比较器无杂散动态范围(SFDR > 43分贝@70 MHzAout。

32bit 频率控制字便捷的编辑控制接口:并行或串行异步加载格式5位相位调制和偏置功能比较器抖动<80 ps的P-P在20兆赫2.7 V至5.25 V单电源供电低功耗:555毫瓦@180 MHz 掉电功能:4 mW@2.7 V 超小28引脚SSOP封装应用:频率/相位灵活可变的正弦波合成数字时钟恢复和锁定电路通信领域数控ADC编码发生器通信领域中灵活地本地振荡器正交振荡器CW,AM,FM,FSK MSK调制发射机GENERAL DESCRIPTIONAD9851是一个高度集成的器件,采用先进的DDS技术,结合内部高速,高性能D / A转换器,比较器,实现了一个数字可编程频率合成器和时钟发生器的功能。

引入一个精确的时钟源,AD9851可以产生一个稳定的,频率和相位可编程的正弦波。

此正弦波可以直接用作频率源或在内部转化为方波,然后作为灵活的时钟发生器使用。

AD9851的创新型高速DDS内核可以接受一个32位频率控制字,从而可以产生一个最大180 MHz的输出时钟,其分辨率约0.04Hz。

AD9851包含一个独特的6 * REFCLK乘法器电路,不再需要一个高速参考振荡器。

6 * REFCLK乘法器对SFDR和相位噪声的影响微乎其微。

AD9851提供分辨率为5位的相位调节,使其输出波形的相位的增量为11.25 °。

AD9851内部包含一个高速比较器,该比较器可以被配置为接受(外部)DAC的滤波输出,从而产生一个低抖动的输出脉冲。

频率的调谐,控制字以及相位调制字是通过并行或串行加载模式异步加载到AD9851中的。

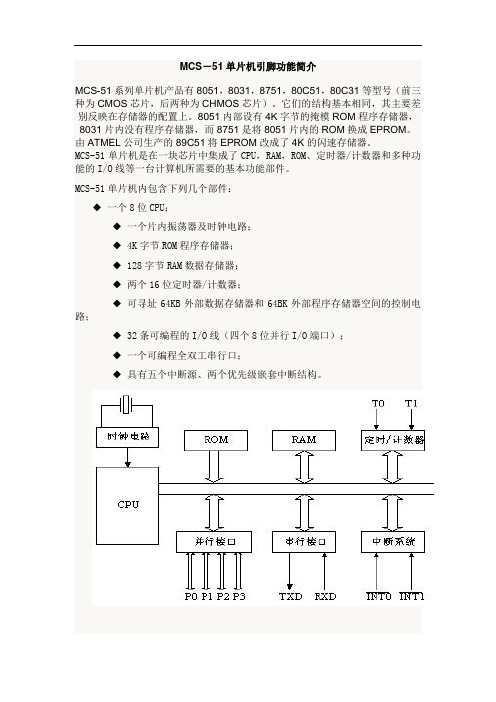

MCS-51单片机引脚功能简介MCS-51系列单片机产品有8051,8031,8751,80C51,80C31等型号(前三种为CMOS芯片,后两种为CHMOS芯片)。

它们的结构基本相同,其主要差别反映在存储器的配置上。

8051内部设有4K字节的掩模ROM程序存储器,8031片内没有程序存储器,而8751是将8051片内的ROM换成EPROM。

由ATMEL公司生产的89C51将EPROM改成了4K的闪速存储器。

MCS-51单片机是在一块芯片中集成了CPU,RAM,ROM、定时器/计数器和多种功能的I/O线等一台计算机所需要的基本功能部件。

MCS-51单片机内包含下列几个部件:◆一个8位CPU;◆一个片内振荡器及时钟电路;◆ 4K字节ROM程序存储器;◆ 128字节RAM数据存储器;◆两个16位定时器/计数器;◆可寻址64KB外部数据存储器和64BK外部程序存储器空间的控制电路;◆ 32条可编程的I/O线(四个8位并行I/O端口);◆一个可编程全双工串行口;◆具有五个中断源、两个优先级嵌套中断结构。

MCS-51单片机内部结构图MCS-51单片机引脚功能:MCS-51单片机引脚图1 电源线:VCC:+5 V电源。

VSS:地线。

2 RST:复位信号线。

当输入的复位信号延续两个机器周期以上的高电平时即为有效,用以完成单片机的复位初始化操作。

3 信号引脚介绍P0.0 ~P0.7:P0口8位双向口线。

P1.0 ~P1.7 :P1口8位双向口线。

P2.0 ~P2.7 :P2口8位双向口线。

P3.0 ~P3.7 :P3口8位双向口线。

4 XTAL1和XTAL2:外接晶振引脚。

当使用外部振荡器时,外部振荡信号应直接加到XTAL1,而XTAL2悬空。

5 控制引脚:ALE/-PROG、-PSEN、-EA/Vpp组成了MSC-51的控制总线。

(1) -EA/Vpp(31脚):外部程序存储器地址允许输入端。

第二功能:固化编程电压输入端。

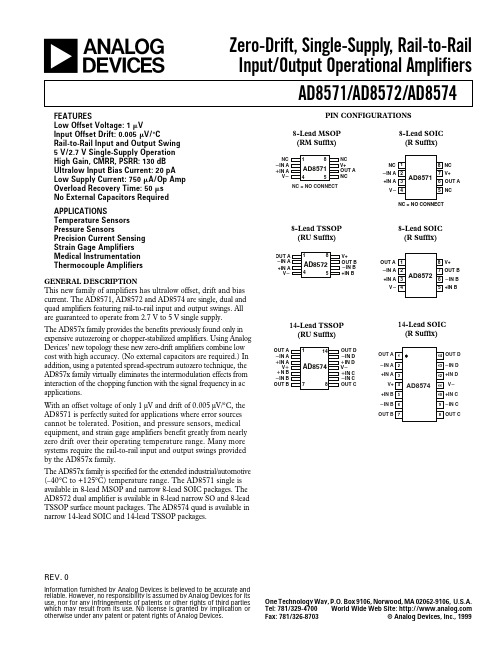

14-Bit, 1 MSPS, Unipolar/BipolarProgrammable Input PulSAR® ADCAD7951 Rev. 0Information furnished by Analog Devices is believed to be accurate and reliable. However, noresponsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. T rademarks and registered trademarks are the property of their respective owners. One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 Fax: 781.461.3113 ©2006 Analog Devices, Inc. All rights reserved.FEATURESMultiple pins/software programmable input ranges:5 V, 10 V, ±5 V, ±10 VPins or serial SPI® compatible input ranges/mode selection Throughput1 MSPS (warp mode)800 kSPS (normal mode)670 kSPS (impulse mode)14-bit resolution with no missing codesINL: ±0.3 LSB typ, ±1 LSB max (±61 ppm of FSR)SNR: 85 dB @ 2 kHzi CMOS® process technology5 V internal reference: typical drift 3 ppm/°C; TEMP output No pipeline delay (SAR architecture)Parallel (14- or 8-bit bus) and serial 5 V/3.3 V interfaceSPI-/QSPI™-/MICROWIRE™-/DSP-compatiblePower dissipation:10 mW @ 100 kSPS235 mW @ 1 MSPS48-lead LQFP and LFCSP (7 mm × 7 mm) packages APPLICATIONSProcess controlMedical instrumentsHigh speed data acquisitionDigital signal processingInstrumentationSpectrum analysisATEGENERAL DESCRIPTIONThe AD7951 is a 14-bit, charge redistribution, successive approximation register (SAR) architecture analog-to-digital converter (ADC) fabricated on Analog Devices, Inc.’s i CMOS high voltage process. The device is configured through hardware or via a dedicated write only serial configuration port for input range and operating mode. The AD7951 contains a high speed 14-bit sampling ADC, an internal conversion clock, an internal reference (and buffer), error correction circuits, and both serial and parallel system interface ports. A falling edge on CNVST samples the analog input on IN+ with respect to a ground sense, IN−. The AD7951 features four different analog input ranges and three different sampling modes: warp mode for the fastest throughput, normal mode for the fastest asynchronous throughput, and impulse mode where power is scaled with throughput. Operation is specified from −40°C to +85°C.FUNCTIONAL BLOCK DIAGRAM6396-1WARP IMPULSE BIPOLAR TENFigure 1.Table 1. 48-Lead 14-/16-/18-Bit PulSAR SelectionType100 kSPS to250 kSPS500 kSPS to570 kSPS570 kSPS to1000 kSPS>1000kSPS PseudoDifferentialAD7651AD7660AD7661AD7650AD7652AD7664AD7666AD7653AD7667True Bipolar AD7610AD7663AD7665 AD7951AD7612AD7671TrueDifferentialAD7675 AD7676 AD7677 AD7621AD7622AD7623 18-Bit, TrueDifferentialAD7678 AD7679 AD7674 AD7641AD7643 Multichannel/SimultaneousAD7654AD7655AD7951Rev. 0 | Page 2 of 32TABLE OF CONTENTSFeatures..............................................................................................1 Applications.......................................................................................1 Functional Block Diagram..............................................................1 General Description.........................................................................1 Revision History...............................................................................2 Specifications.....................................................................................3 Timing Specifications..................................................................5 Absolute Maximum Ratings............................................................7 ESD Caution..................................................................................7 Pin Configuration and Function Descriptions.............................8 Typical Performance Characteristics...........................................12 Terminology....................................................................................16 Theory of Operation......................................................................17 Overview......................................................................................17 Converter Operation..................................................................17 Modes of Operation...................................................................18 Transfer Functions......................................................................18 Typical Connection Diagram...................................................19 Analog Inputs..............................................................................20 Driver Amplifier Choice...........................................................21 Voltage Reference Input/Output..............................................21 Power Supplies............................................................................22 Conversion Control...................................................................23 Interfaces..........................................................................................24 Digital Interface..........................................................................24 Parallel Interface.........................................................................24 Serial Interface............................................................................25 Master Serial Interface...............................................................25 Slave Serial Interface..................................................................27 Hardware Configuration...........................................................29 Software Configuration.............................................................29 Microprocessor Interfacing.......................................................30 Application Information................................................................31 Layout Guidelines.......................................................................31 Evaluating Performance............................................................31 Outline Dimensions.......................................................................32 Ordering Guide.. (32)REVISION HISTORY10/06—Revision 0: Initial VersionAD7951Rev. 0 | Page 3 of 32SPECIFICATIONSAVDD = DVDD = 5 V; OVDD = 2.7 V to 5.5 V; VCC = 15 V; VEE = −15 V; V REF = 5 V; all specifications T MIN to T MAX , unless otherwise noted. Table 2.Parameter Conditions/Comments Min Typ Max Unit RESOLUTION 14 Bits ANALOG INPUT Voltage Range, V IN V IN+ − V IN− = 0 V to 5 V −0.1 +5.1 V V IN+ − V IN− = 0 V to 10 V −0.1 +10.1 V V IN+ − V IN− = ±5 V −5.1 +5.1 V V IN+ − V IN− = ±10 V −10.1 +10.1 V V IN− to AGND −0.1 +0.1 V Analog Input CMRR f IN = 100 kHz 75 dB Input Current V IN = ±5 V, ±10 V @ 1 MSPS 3001 μA Input Impedance See the Analog Inputs section THROUGHPUT SPEED Complete Cycle In warp mode 1 μs Throughput Rate In warp mode 1 1 MSPS Time Between Conversions In warp mode 1 ms Complete Cycle In normal mode 1.25 μs Throughput Rate In normal mode 0 800 kSPS Complete Cycle In impulse mode 1.49 μs Throughput Rate In impulse mode 0 670 kSPS DC ACCURACYIntegral Linearity Error 2−1 ±0.3 +1 LSB 3No Missing Codes 2 14 BitsDifferential Linearity Error 2−1 +1 LSB Transition Noise 0.55 LSB Zero Error (Unipolar or Bipolar) −15 +15 LSB Zero Error Temperature Drift ±1 ppm/°C Full-Scale Error (Unipolar or Bipolar) −20 +20 LSB Full-Scale Error Temperature Drift ±1 ppm/°C Power Supply Sensitivity AVDD = 5 V ± 5% ±0.8 LSB AC ACCURACY Dynamic Range f IN = 2 kHz, −60 dB 84.5 85.5 dB 4Signal-to-Noise Ratio f IN = 2 kHz 84.5 85.5 dB f IN = 20 kHz 85.5 dB Signal-to-(Noise + Distortion) (SINAD) f IN = 2 kHz 83 85.4 dB Total Harmonic Distortion f IN = 2 kHz −105 dB Spurious-Free Dynamic Range f IN = 2 kHz 102 dB –3 dB Input Bandwidth V IN = 0 V to 5 V 45 MHz Aperture Delay 2 ns Aperture Jitter 5 ps rms Transient Response Full-scale step 500 ns INTERNAL REFERENCE PDREF = PDBUF = low Output Voltage REF @ 25°C 4.965 5.000 5.035 V Temperature Drift –40°C to +85°C ±3 ppm/°C Line Regulation AVDD = 5 V ± 5% ±15 ppm/V Long-Term Drift 1000 hours 50 ppm Turn-On Settling Time C REF = 22 μF 10 msAD7951Rev. 0 | Page 4 of 32Parameter Conditions/Comments Min Typ Max Unit REFERENCE BUFFER PDREF = high REFBUFIN Input Voltage Range 2.4 2.5 2.6 V EXTERNAL REFERENCE PDREF = PDBUF = high Voltage Range REF 4.75 5 AVDD + 0.1 V Current Drain 1 MSPS throughput 200 μA TEMPERATURE PIN Voltage Output @ 25°C 311 mV Temperature Sensitivity 1 mV/°C Output Resistance 4.33 kΩ DIGITAL INPUTS Logic Levels V IL −0.3 +0.6 V V IH 2.1 OVDD + 0.3 V I IL −1 +1 μA I IH −1 +1 μA DIGITAL OUTPUTS Data Format Parallel or serial 14-bit Pipeline Delay 5 V OL I SINK = 500 μA 0.4 V V OH I SOURCE = –500 μA OVDD − 0.6 V POWER SUPPLIES Specified Performance AVDD 4.756 5 5.25 V DVDD 4.75 5 5.25 V OVDD 2.7 5.25 V VCC 7 15 15.75 V VEE −15.75 −15 0 V Operating Current 7, 8@ 1 MSPS throughput AVDD With Internal Reference 20 mA With Internal Reference Disabled 18.5 mA DVDD 7 mA OVDD 0.5 mA VCC VCC = 15 V, with internal reference buffer 4 mA VCC = 15 V 3 mA VEE VEE = −15 V 2 mA Power Dissipation @ 1 MSPS throughput With Internal Reference PDREF = PDBUF = low 235 260 mW With Internal Reference Disabled PDREF = PDBUF = high 215 240 mWIn Power-Down Mode 9PD = high 10 μW TEMPERATURE RANGE 10 Specified Performance T MIN to T MAX −40 +85 °C1 With V IN = 0 V to 5 V or 0 V to 10 V ranges, the input current is typically 100 μA. In all input ranges, the input current scales with throughput. See the Analog Inputs section. 2Linearity is tested using endpoints, not best fit. All linearity is tested with an external 5 V reference. 3LSB means least significant bit. All specifications in LSB do not include the error contributed by the reference. 4All specifications in dB are referred to a full-scale range input, FSR. Tested with an input signal at 0.5 dB below full-scale, unless otherwise specified. 5Conversion results are available immediately after completed conversion. 64.75 V or V REF – 0.1 V, whichever is larger. 7Tested in parallel reading mode. 8With internal reference, PDREF = PDBUF = low; with internal reference disabled, PDREF = PDBUF = high. With internal reference buffer, PDBUF = low. 9With all digital inputs forced to OVDD. 10Consult sales for extended temperature range.AD7951TIMING SPECIFICATIONSAVDD = DVDD = 5 V; OVDD = 2.7 V to 5.5 V; VCC = 15 V; VEE = −15 V; V REF = 5 V; all specifications T MIN to T MAX, unless otherwise noted.Rev. 0 | Page 5 of 32AD7951Rev. 0 | Page 6 of 32Parameter Symbol Min Typ Max UnitSLAVE SERIAL/SERIAL CONFIGURATION INTERFACE MODES 2(See Figure 42, Figure 43, and Figure 45) External SDCLK, SCCLK Setup Time t 31 5 ns External SDCLK Active Edge to SDOUT Delay t 32 2 18 ns SDIN/SCIN Setup Time t 33 5 ns SDIN/SCIN Hold Time t 34 5 ns External SDCLK/SCCLK Period t 3525 ns External SDCLK/SCCLK High t 3610 ns External SDCLK/SCCLK Low t 3710 ns1 In warp mode only, the time between conversions is 1 ms; otherwise, there is no required maximum time.2In serial interface modes, the SDSYNC, SDSCLK, and SDOUT timings are defined with a maximum load C L of 10 pF; otherwise, the load is 60 pF maximum. 3In serial master read during convert mode. See Table 4 for serial master read after convert mode.Table 4. Serial Clock Timings in Master Read After Convert ModeDIVSCL K [1] 0 0 1 1DIVSCL K [0]Symbol 0 1 0 1 Unit SYNC to SDCLK First Edge Delay Minimum t 18 3 20 20 20 ns Internal SDCLK Period Minimum t 1930 60 120 240 ns Internal SDCLK Period Maximum t 1945 90 180 360 ns Internal SDCLK High Minimum t 2012 30 60 120ns Internal SDCLK Low Minimum t 2110 25 55 115 ns SDOUT Valid Setup Time Minimum t 22 4 20 20 20 ns SDOUT Valid Hold Time Minimumt 23 5 8 35 90ns SDCLK Last Edge to SYNC Delay Minimum t 24 5 7 35 90 ns BUSY High Width Maximum t 28 Warp Mode 1.60 2.35 3.75 6.75 μs Normal Mode 1.85 2.60 4.00 7.00 μs Impulse Mode2.10 2.85 4.25 7.25 μsNOTES1. IN SERIAL INTERFACE MODES, THE SYNC, SCLK, AND SDOUT ARE DEFINED WITH A MAXIMUM LOADC L OF 10pF; OTHERWISE, THE LOAD IS 60pF MAXIMUM.1.4VTO OUTPUTPIN06396-002Figure 2. Load Circuit for Digital Interface Timing, SDOUT, SYNC, and SCLK Outputs, C L = 10 pF06396-003Figure 3. Voltage Reference Levels for TimingAD7951Rev. 0 | Page 7 of 32ABSOLUTE MAXIMUM RATINGSTable 5.Parameter Rating Analog Inputs/OutputsIN+1, IN−1to AGND VEE − 0.3 V to VCC + 0.3 V REF, REFBUFIN, TEMP , REFGND to AGNDAVDD + 0.3 V toAGND − 0.3 V Ground Voltage Differences AGND, DGND, OGND ±0.3 V Supply Voltages AVDD, DVDD, OVDD −0.3 V to +7 V AVDD to DVDD, AVDD to OVDD ±7 V DVDD to OVDD ±7 V VCC to AGND, DGND –0.3 V to +16.5 V VEE to GND +0.3 V to −16.5 V Digital Inputs −0.3 V to OVDD + 0.3 VPDREF, PDBUF 2±20 mAInternal Power Dissipation 3700 mW Internal Power Dissipation 4 2.5 W Junction Temperature 125°C Storage Temperature Range −65°C to +125°C1 See the Analog Inputs section.2See the Voltage Reference Input section. 3Specification is for the device in free air: 48-Lead LQFP; θJA = 91°C/W, θJC = 30°C/W. 4Specification is for the device in free air: 48-Lead LFCSP; θJA = 26°C/W.Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operationalsection of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.ESD CAUTIONAD7951Rev. 0 | Page 8 of 32PIN CONFIGURATION AND FUNCTION DESCRIPTIONS06396-004D B U FD RE FE F B U F I NE M PV D DI N +G N DE EC C I N –E F G N DE FD 2/E X T /I N TD 3/I N V S Y N CD 4/I N V S C L KD 5/R D C /S D I NO G N DO V D DD V D DD G N DD 6/S D O U TD 7/S D C L KD 8/S Y N CD 9/R DE R R O RAGND AVDD AGND BYTESWAPOB/2C SER/PARNC = NO CONNECTNC NC D0/DIVSCLK[0]D1/DIVSCLK[1]IMPULSE WARP BIPOLAR CNVST PD RESET CS RD TEN BUSY D13/SCCS D12/SCCLK D11/SCIN D10/HW/SWFigure 4. Pin ConfigurationAD7951Rev. 0 | Page 9 of 32AD7951Rev. 0 | Page 10 of 32分销商库存信息:ANALOG-DEVICESAD7951BSTZ AD7951BCPZRL AD7951BSTZRL AD7951BCPZ。

DDS模块使用说明书目录1、DDS模块实物图 (2)2、DDS模块管脚定义 (2)3、与单片机的硬件连接及程序(并行送控制字方式) (3)4、与单片机的硬件连接及程序(串行送控制字方式) (4)5、DDS模块方波的产生 (6)6、输出频率特性 (7)1、DDS模块实物图(正面)DDS模块实物图(反面)该模块系统时钟频率为30MHZ,内部6倍频后时钟可达180MHZ。

支持串行和并行送控制字方式。

最大不失真输出频率可以达70MHZ(该模块测试的实际值)2、各管脚定义(只针对此模块)CLK:系统时钟频率输出(30MHZ)RESET:控制DDS内部DAC的输出电流(当需要控制输出信号的幅度时,可以控制该脚的电压值从而控制DDS信号输出的幅度)Q0A:内部高速比较器的正相输出端(对应AD9851的14管脚)Q0B:内部高速比较器的反相输出端(对应AD9851的13管脚)VIP:内部高速比较器的同相输入端(对应AD9851的16管脚)VIN:内部高速比较器的反相输入端(对应AD9851的15管脚)F0:频率输出端(已经经过了典型低通滤波器后的波形)GND:输入电源地VDD:输入电源正极(+5V)RST:AD9851复位端(高电平,对芯片进行操作前需将该脚置为高电平,复位完成后将其置为低电平RST_AD9851)FQUP:数据更新位(串行/并行数据输入时的输入位FQ_QD_AD9851)WCLK:时钟输入端(串行/并行数据输入时的输入位CLK_AD9851)D0:数据输入端(并行输入数据时的低位)D1:数据输入端D2:数据输入端D3:数据输入端D4:数据输入端D5:数据输入端D6:数据输入端D7:数据输入端(并行输入数据时的高位。

当进行串行送数据时,该位是串行的数据输入位DataIn_AD9851)3、与单片机的硬件连接及程序(串行送控制字方式)串行读写程序:该程序实现的是固定频点的输出1KHZ#include<regx51.h>#include <intrins.h>sbit FQ_QD_AD9851 = P1^0;sbit CLK_AD9851 = P1^1;sbit DataIn_AD9851 = P1^2;sbit RST_AD9851 = P1^3;unsigned long int freq = 0;//unsigned char Control_AD9851 = 0x09; // Phase0 ,power down mode and 6 REFCLK Multiplier enable//unsigned char Control_AD9851 = 0x00; // Phase0 ,power on mode and 6 REFCLK Multiplier disableunsigned char Control_AD9851 = 0x01; // Phase0 ,power on mode and 6 REFCLK Multiplier enablevoid SentFreq(){unsigned char i;unsigned int temp;FQ_QD_AD9851=0;for(i=0;i<32;i++) //串口数据输入频率控制字{CLK_AD9851 = 0;temp=( ( freq >> i ) & 1 );DataIn_AD9851 = temp;CLK_AD9851 = 1;}for(i=0;i<8;i++) //phase-b4 ph-b3 ph-b2 ph-b1 ph-b0 Power-down Logic0* 6*REFCLK Multiplier_En{CLK_AD9851 = 0;temp=( ( Control_AD9851 >> i ) & 1 );DataIn_AD9851 = temp;CLK_AD9851 = 1;}CLK_AD9851 = 0;FQ_QD_AD9851 = 1;FQ_QD_AD9851 = 0;}void Set_Freq(unsigned long int Freqency){freq= (unsigned long int)(23.861*Freqency); // SYSCLK = 180 MHz 2^32/180000000=23.861SentFreq();}void main(){RST_AD9851=1;//复位AD9851RST_AD9851=1;RST_AD9851=0;Set_Freq(1000);(如果单独执行,最好送两次频率控制字较为稳定)Set_Freq(1000);while(1){Set_Freq(1000);//输出1KHZ}}4、与单片机的硬件连接图(并行送控制字方式)并行读写程序:该程序实现的是固定频点的输出1KHZ#include<regx51.h>#include <intrins.h>sbit FQ_UD_AD9851=P1^0;//定义I0口sbit CLK_AD9851=P1^1;sbit RST_AD9851= P1^2;unsigned long int freq = 0;//unsigned char Control_AD9851 = 0x09; // Phase0 ,power down mode and 6 REFCLK Multiplier enable//unsigned char Control_AD9851 = 0x00; // Phase0 ,power on mode and 6 REFCLK Multiplier disableunsigned char Control_AD9851 = 0x01; // Phase0 ,power on mode and 6 REFCLK Multiplier enableunsigned char W1=0X0e;unsigned char W2=0X38;unsigned char W3=0Xe3;unsigned char W4=0X8e;void Parallel2Serial_AD9851(void)//并行写入控制字{ FQ_UD_AD9851=0;CLK_AD9851=0;P0=Control_AD9851;CLK_AD9851=1;CLK_AD9851=0;P0=W1;CLK_AD9851=1;CLK_AD9851=0;P0=W2;CLK_AD9851=1;CLK_AD9851=0;P0=W3;CLK_AD9851=1;CLK_AD9851=0;P0=W4;CLK_AD9851=1;CLK_AD9851=0;FQ_UD_AD9851=1;FQ_UD_AD9851=0;}void Set_Freq(float Freqency)//计算输出频率{freq= (unsigned long int)(23.861*Freqency); // SYSCLK = 180 MHz W4=(unsigned char)freq&0xff;freq=freq>>8;W3=(unsigned char)freq&0xff;freq=freq>>8;W2=(unsigned char)freq&0xff;freq=freq>>8;W1=(unsigned char)freq&0xff;Parallel2Serial_AD9851();}void main(void){RST_AD9851=1;//复位模块电路RST_AD9851=1;RST_AD9851=0;while(1){Set_Freq(1000);//输出1KHZ频率}}5、DDS模块方波的产生利用AD9851内部高速比较器产生方波,实现电路如下:6、输出频率特性(频谱仪测量)10MHZ输出30MHZ输出70MHZ输出。

8Bit Microcontroller with 8bit ADC12007/6/15 Rev.17概述MK7A21P 是带8位A/D 转换器的RISC 高性能8位微控制器。

它内部包含2K 字节的一次性可编程只读存储器、128字节数据存储器、定时器/计数器、捕捉、中断、LVR (低电压复位)、I/O 口和PWM 输出。

1. 基本特性● ROM :2K ×16 bits● RAM :37×8 bits (特殊寄存器)+ 128×8 bits (一般寄存器) ● 椎栈:8级● 一个指令周期由两个系统时钟组成 ● 复位模式:(a) 上电复位 (b) 低电压复位(c) RESETB/PC1(如果设置成复位脚位)输入一个负脉冲 (d) 看门狗定时器计数溢出复位 ● 双时钟模式- 外部RC 或晶振振荡器 - 内部4MHz RC 振荡器 ● 定时器/计数器- TM1:16-bit ,捕捉 & 定时器- TM2:8-bit ,PWM (period )& 定时器 - TM3:8-bit ,PWM (duty )& 定时器 - TO :TM2(PWM )时钟输出● 看门狗定时器:芯片内WTD 是基于一个内部RC 振荡器(仅WDT 使用)。

有8个周期可供选择。

使用者可通过使用预分频器来延长WDT 溢出周期。

● 中断结果:(a) 外部中断(PA7~PA0)(b) 内部定时器/结果计数器中断(TM1~TM3) (c) ADC 结束转换中断 ● I/O 口:16脚位 ● PWM :一个通道● ADC :最多8-bit 及4通道,至少7-bit 精度。

它能在转换模式或比较模式下使用 ● 唤醒模式:A 口(PA7~PA0)脚位变化唤醒8Bit Microcontroller with 8bit ADC2. 图表RESETOSC 1OSC 2PA 0 ~7 PB 0 ~3VDDGNDPWMEXT _CLK TO8Bit Microcontroller with 8bit ADC3. 脚位定义 & 管脚分配封装类型:18脚DIP 或SOPPA4/EXT_CLK PA5OSC2/PC3OSC1/PC2VDDPB2/AN2PB1/AN1PB0/AN0VSS RESETB/PC1PWM/PC0PA3/TOPA2PB3/AN3封装类型:14脚DIP 或SOP8Bit Microcontroller with 8bit ADC4. 脚位说明脚位名称 I/O说 明PA0~2 PA5~7I/O1. I/O 口(输入模式下会有上拉电阻)2. 脚位改变时唤醒(选择)3. 外部中断输入(选择)PA3/TO I/O1. I/O 口(输入模式下会有上拉电阻)2. 脚位改变时唤醒(选择)3. 外部中断输入(选择)4. TO 时钟输出PA4/EXT_CLK I/O1. I/O 口(输入模式下会有上拉电阻)2. EXT_CLK 时钟输入(或捕捉输入)3. 脚位改变时唤醒(选择)4. 外部中断输入(选择)PB3/AN3 I/OPB2/AN2 I/O PB1/AN1 I/O PB0/AN0 I/O1. I/O 口(输入模式下会有上拉电阻)2. 相似体输入 PWM/PC0 I/O1. I/O 口(输入模式下会有上拉电阻)2. PWM 输出 RESETB/PC1 I1. 复位脚位2. 输入口OSC1/PC2 I, I/O1. 振荡器输入2. I/O 口(输入模式下会有上拉电阻) OSC2/PC3 O, I/O1. 振荡器输出2. I/O 口(输入模式下会有上拉电阻) VDD P 电源输入 VSS P 接地输入8Bit Microcontroller with 8bit ADC5. 存储器映象MK7A21P芯片带有两种存储器,分别是程序存储器(ROM)和数据存储器(RAM)。

目录1.lm7815介绍2.实际应用3.引脚序号、引脚功能4.lm7815应用电路5.7815电参数三端稳压集成电路lm7815.电子产物中, 罕见的三端稳压集成电路有正电压输出的lm78 ×× 系列和负电压输出的lm79××系列.顾名思义, 三端IC是指这种稳压用的集成电路, 只有三条引脚输出, 分别是输入端、接地端和输出端.它的样子象是普通的三极管, TO- 220 的标准封装, 也有lm9013样子的TO-92封装. 1.lm7815介绍用lm78/lm79系列三端稳压IC来组成稳压电源所需的外围元件极少, 电路内部还有过流、过热及调整管的呵护电路, 使用起来可靠、方便, 而且价格廉价.该系列集成稳压IC型号中的lm78或lm79后面的数字代表该三端集成稳压电路的输出电压, 如lm7806暗示输出电压为正6V, lm7909暗示输出电压为负9V.因为三端固定集成稳压电路的使用方便, 电子制作中经常采纳.最年夜输出电流, LM78XX系列输出电压分别为5V;6V;8V;9V;10V;12V;15V;18V;24V.2.实际应用在实际应用中, 应在三端集成稳压电路上装置足够年夜的散热器(固然小功率7815IC内部电路图.的条件下不用).当稳压管温渡过高时, 稳压性能将变差, 甚至损坏.当制作中需要一个能输出1.5A以上电流的稳压电源, 通常采纳几块三端稳压电路并联起来, 使其最年夜输出电流为N个1.5A, 但应用时需注意:并联使用的集成稳压电路应采纳同一厂家、同一批号的产物, 以保证参数的一致.另外在输出电流上留有一定的余量, 以防止个别集成稳压电路失效时招致其他电路的连锁烧毁.在lm78 ** 、lm79 ** 系列三端稳压器中最常应用的是TO-220 和TO-202 两种封装.这两种封装的图形以及引脚序号、引脚功能如附图所示.图中的引脚号标注方法是依照引脚电位从高究竟的顺序标注的.这样标注便于记忆.引脚①为最高电位, ③脚为最低电位, ②脚居中.从图中可以看出, 不论正压还是负压, ②脚均为输出端.对lm78**正压系列, 输入是最高电位, 自然是①脚, 地端为最低电位, 即③脚, 如附图所示.对与lm79**负压系列, 输入为最低电位, 自然是③脚, 而地端为最高电位, 即①脚, 如附图所示.3.引脚序号、引脚功能另外, 还应注意, 散热片总是和最低电位的第③脚相连.这样在lm78**系列中, 散热片和地相连接, 而在lm79**系列中, 散热片却和输入端相连接.4.lm7815应用电路lm7815典范应用电路图:lm78XX系列集成稳压器的典范应用电路图, 是一个输出正5V直流电lm7815稳压电路压的稳压电源电路.IC收集成稳压器lm7815, C1、C2分别为输入端和输出端滤波电容, RL为负载电阻.当输出电流较年夜时, lm7815应配上散热板.为提高输出电压的应用电路.稳压二极管VD1串接在lm78XX 稳压器2脚与地之间, 可使输出电压Uo获得一定的提高, 输出电压Uo为78XX稳压器输出电压与稳压二极管VC1稳压值之和.VD2是输出呵护二极管, 一旦输出电压低于VD1稳压值时, VD2导通, 将输出电流旁路, 呵护lm7800稳压器输出级不被损坏.为输出电压可在一定范围内调节的应用电路.由于R1、RP 电阻网络的作用, 使得输出电压被提高, 提高的幅度取决于RP 与R1的比值.调节电位器RP, 即可一定范围内调节输出电压.当RP=0时, 输出电压Uo即是lm78XX稳压器输出电压;当RP 逐步增年夜时, Uo也随之逐步提高.为扩年夜输出电流的应用电路.VT2为外接扩流率管, VT1为推动管, 二者为达林顿连接.R1为偏置电阻.该电路最年夜输出电流取决于VT2的参数.5.7815电参数。