第8章MCS-51单片机并行扩展技术总结

- 格式:pdf

- 大小:3.40 MB

- 文档页数:87

华中科技大学光学与电子信息学院单片机( 2015 -- 2016学年度第一学期)题目:MCS-51单片机并行端口结构与操作院系:光学与电子信息学院班级:学号:学生姓名:指导教师:成绩:日期: 2015年 9月 21日MCS—51单片机并行口的结构与操作一、MCS—51单片机简介MCS—51单片机是美国INTE公司于1980年推出的产品,与MCS-48单片机相比,它的结构更先进,功能更强,在原来的基础上增加了更多的电路单元和指令,指令数达111条,MCS-51单片机可以算是相当成功的产品,一直到现在,MCS-51系列或其兼容的单片机仍是应用的主流产品,各高校及专业学校的培训教材仍与MCS—51单片机作为代表进行理论基础学习.MCS-51系列单片机主要包括8031、8051和8751等通用产品,其主要功能如下:8位CPU、4kbytes 程序存储器(ROM)、128bytes的数据存储器(RAM)、32条I/O口线、111条指令,大部分为单字节指令、21个专用寄存器、2个可编程定时/计数器、5个中断源,2个优先级、一个全双工串行通信口、外部数据存储器寻址空间为64kB、外部程序存储器寻址空间为64kB、逻辑操作位寻址功能、双列直插40PinDIP封装、单一+5V电源供电。

如图所示:1。

结构(1)中央处理单元(8位)数据处理、测试位,置位,复位位操作(2)只读存储器(4KB或8KB)永久性存储应用程序,掩模ROM、EPROM、EEPROM(3)随机存取内存(128B、128B SFR)在程序运行时存储工作变量和资料(4)并行输入/输出口(I / O)(32条)作系统总线、扩展外存、I / O接口芯片(5)串行输入/输出口(2条)串行通信、扩展I / O接口芯片(6)定时/计数器(16位、加1计数)计满溢出、中断标志置位、向CPU提出中断请求,与CPU之间独立工作(7)时钟电路内振、外振。

(8)中断系统五个中断源、2级优先。

第8章单片机系统扩展1. 什么是AT89C51单片机的最小应用系统?答:所谓最小应用系统是指能维持单片机运行的最简单配置系统。

AT89C51芯片外加晶振电路和复位电路就构成了一个简单可靠的最小应用系统。

其在简单应用场合,可满足用户的要求。

2. 在AT89C51扩展系统中,程序存储器与数据存储器共用16位地址线和8位数据线,为什么两个存储空间不会冲突?答:AT89C51在片外扩展RAM的地址空间为0000H~FFFFH,共64KB,与ROM地址空间重叠。

但因各自使用不同的指令和控制信号,因而不会“撞车”。

读ROM时用MOVC指令,由PSEN选通ROM的OE端;读/写片外RAM时用MOVX指令,用RD选通RAM的OE端,用WR选通RAM的WE端。

但扩展RAM与扩展I/O 口是统一编址的,使用相同的指令和控制信号。

这在设计硬件系统和编制软件程序时应注意统筹安排。

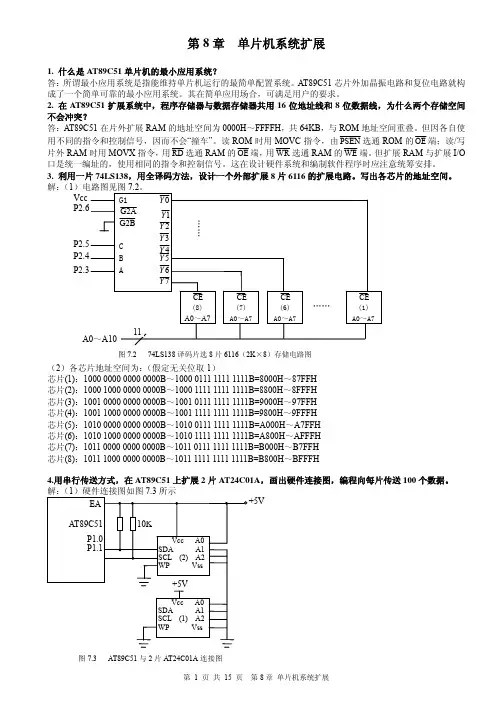

3. 利用一片74LS138,用全译码方法,设计一个外部扩展8片6116的扩展电路。

写出各芯片的地址空间。

解:(图7.2 74LS138译码片选8片6116(2K×8)存储电路图(2)各芯片地址空间为:(假定无关位取1)芯片(1):1000 0000 0000 0000B~1000 0111 1111 1111B=8000H~87FFH芯片(2):1000 1000 0000 0000B~1000 1111 1111 1111B=8800H~8FFFH芯片(3):1001 0000 0000 0000B~1001 0111 1111 1111B=9000H~97FFH芯片(4):1001 1000 0000 0000B~1001 1111 1111 1111B=9800H~9FFFH芯片(5):1010 0000 0000 0000B~1010 0111 1111 1111B=A000H~A7FFH芯片(6):1010 1000 0000 0000B~1010 1111 1111 1111B=A800H~AFFFH芯片(7):1011 0000 0000 0000B~1011 0111 1111 1111B=B000H~B7FFH芯片(8):1011 1000 0000 0000B~1011 1111 1111 1111B=B800H~BFFFH4.用串行传送方式,在AT89C51上扩展2片AT24C01A,画出硬件连接图,编程向每片传送100个数据。

单片机IO口扩展技术] 0 引言在单片机家族的众多成员中,MCS-51系列单片机以其优越的性能、成熟的技术、高可靠性和高性价比,占领了工业测控和自动化工程应用的主要市场,并成为国内单片机应用领域中的主流机型。

MCS-51单片机的并行口有P0、P1、P2和P3,由于P0口是地址/数据总线口,P2口是高8位地址线,P3口具有第二功能,这样,真正可以作为双向I/O口应用的就只有P1口了。

这在大多数应用中是不够的,因此,大部分MCS-51单片机应用系统设计都不可避免的需要对P0口进行扩展。

由于MCS-51单片机的外部RAM和I/O口是统一编址的,因此,可以把单片机外部64K字节RAM空间的一部分作为扩展外围I/O口的地址空间。

这样,单片机就可以像访问外部RAM存储器单元那样访问外部的P0口接口芯片,以对P0口进行读/写操作。

用于P0口扩展的专用芯片很多。

如8255可编程并行P0口扩展芯片、8155可编程并行P0口扩展芯片等。

本文重点介绍采用具有三态缓冲的74HC244芯片和输出带锁存的74HC377芯片对P0口进行的并行扩展的具体方法。

1 输入接口的扩展MCS-51单片机的数据总线是一种公用总线,不能被独占使用,这就要求接在上面的芯片必须具备“三态”功能,因此扩展输入接口实际上就是要找一个能够用于控制且具备三态输出的芯片。

以便在输入设备被选通时,它能使输入设备的数据线和单片机的数据总线直接接通;而当输入设备没有被选通时,它又能隔离数据源和数据总线(即三态缓冲器为高阻抗状态)。

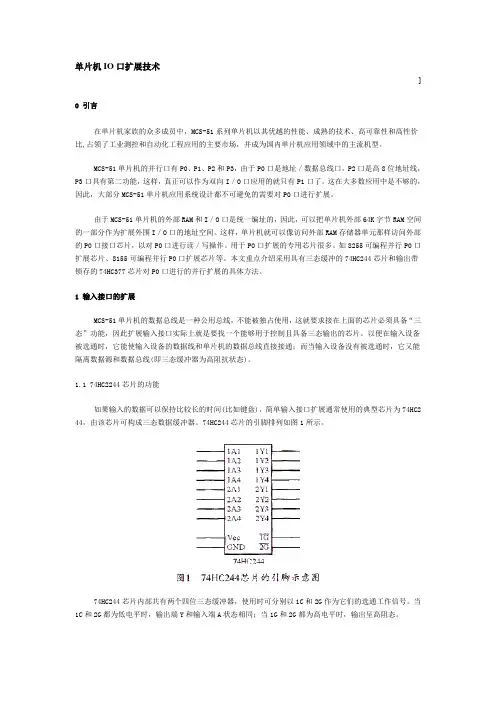

1.1 74HC2244芯片的功能如果输入的数据可以保持比较长的时间(比如键盘),简单输入接口扩展通常使用的典型芯片为74HC244,由该芯片可构成三态数据缓冲器。

74HC244芯片的引脚排列如图1所示。

74HC244芯片内部共有两个四位三态缓冲器,使用时可分别以1C和2G作为它们的选通工作信号。

当1 C和2G都为低电平时,输出端Y和输入端A状态相同;当1G和2G都为高电平时,输出呈高阻态。

大学51系列单片机第八章习题及参考答案一、填空题1、MCS-51外扩ROM、RAM或I/O时,它的地址总线是P0、P2 口。

2、12根地址线可寻址 4 KB存储单元。

3、微机与外设间传送数据有程序传送、中断传送和DMA传送三种传送方式。

4、74LS138是具有3个输入的译码器芯片,其输出作为片选信号时,最多可以选中8 块芯片。

5、74LS273通常用来作简单输出接口扩展;而74LS244则常用来作简单输入接口扩展。

6、并行扩展存储器,产生片选信号的方式有线选法和译码法两种。

7、在存储器扩展中,无论是线选法还是译码法,最终都是为了扩展芯片的片选端提供信号。

8、起止范围为0000H-3FFFH的存储器的容量是16 KB。

9、11根地址线可选2KB 个存储单元,16KB存储单元需要14 根地址线。

10、32KB RAM存储器的首地址若为2000H,则末地址为9FFF H。

11、假定一个存储器有4096个存储单元,其首地址为0,则末地址为0FFFH 。

12、除地线公用外,6根地址线可选64 个地址,11根地址线可选2048 个地址。

13、单片机扩展的内容有程序存储器扩展、数据存储器扩展及I/O口的扩展等。

二、选择题1、当8031外扩程序存储器8KB时,需使用EPROM2716( C )A、2片B、3片C、4片D、5片2、某种存储器芯片是8KB*4/片,那么它的地址线根数是( C )A、11根B、12根C、13根D、14根3、74LS138芯片是( B )A、驱动器B、译码器C、锁存器D、编码器4、MCS-51外扩ROM、RAM和I/O口时,它的数据总线是( A )A、P0B、P1C、P2D、P35、6264芯片是( B )A、E2PROMB、RAMC、Flash ROMD、EPROM6、一个EPROM的地址有A0----A11引脚,它的容量为( B )。

A、2KBB、4KBC、11KBD、12KB7、单片机要扩展一片EPROM2764需占用( C )条P2口线。

欢迎光临阳光大学生网,提供最全面的大学生课后习题答案和复习试题免费下载,/阳光大学生网我们希望呵护您的眼睛,关注您的成长,给您一片绿色的环境,欢迎加入我们,一起分享大学里的学习和生活感悟,免费提供:大学生课后答案,大学考试题及答案,大学生励志书籍。

第一章单片机概述1.2除了单片机这一名称之外,单片机还可称为(微控制器)和(嵌入式控制器)。

1.3单片机与普通计算机的不同之处在于其将(微处理器)、(存储器)和(各种输入输出接口)三部分集成于一块芯片上。

4、单片机的发展大致分为哪几个阶段?答:单片机的发展历史可分为四个阶段:第一阶段(1974年----1976年):单片机初级阶段。

第二阶段(1976年----1978年):低性能单片机阶段。

第三阶段(1978年----现在):高性能单片机阶段。

第四阶段(1982年----现在):8位单片机巩固发展及16位单片机、32位单片机推出阶段1.5单片机根据其基本操作处理的位数可分为哪几种类型?答:单片机根据其基本操作处理的位数可分为:1位单片机、4位单片机、8位单片机、16位单片机和32位单片机。

1.6MCS-51系列单片机的基本芯片分别为哪几种?它们的差别是什么?答:基本芯片为8031、8051、8751。

8031内部包括1个8位cpu、128BRAM,21个特殊功能寄存器(SFR)、4个8位并行I/O 口、1个全双工串行口,2个16位定时器/计数器,但片内无程序存储器,需外扩EPROM芯片。

8051是在8031的基础上,片内又集成有4KBROM,作为程序存储器,是1个程序不超过4KB的小系统。

8751是在8031的基础上,增加了4KB的EPROM,它构成了1个程序小于4KB的小系统。

用户可以将程序固化在EPROM中,可以反复修改程序。

1.7MCS-51系列单片机与80C51系列单片机的异同点是什么?答:共同点为它们的指令系统相互兼容。

不同点在于MCS-51是基本型,而80C51采用CMOS 工艺,功耗很低,有两种掉电工作方式,一种是CPU停止工作,其它部分仍继续工作;另一种是,除片内RAM继续保持数据外,其它部分都停止工作。

第8章思考与练习题解析【8—1】简述单片机系统扩展的基本原则和实现方法。

【答】系统扩展是单片机应用系统硬件设计中最常遇到的问题。

系统扩展是指单片机内部各功能部件不能满足应用系统要求时,在片外连接相应的外围芯片以满足应用系统要求。

80C5 1系列单片机有很强的外部扩展能力,外围扩展电路芯片大多是一些常规芯片,扩展电路及扩展方法较为典型、规范。

用户很容易通过标准扩展电路来构成较大规模的应用系统。

对于单片机系统扩展的基本方法有并行扩展法和串行扩展法两种。

并行扩展法是指利用单片机的三组总线(地址总线AB、数据总线DB和控制总线CB)进行的系统扩展;串行扩展法是指利用SPI三线总线和12C双线总线的串行系统扩展。

1.外部并行扩展单片机是通过芯片的引脚进行系统扩展的。

为了满足系统扩展要求,80C51系列单片机芯片引脚可以构成图8-1所示的三总线结构,即地址总线AB、数据总线DB和控制总线CB。

单片机所有的外部芯片都通过这三组总线进行扩展。

2.外部串行扩展80C51.系列单片机的串行扩展包括:SPI(Serial Peripheral Interface)三线总线和12C双总线两种。

在单片机内部不具有串行总线时,可利用单片机的两根或三根I/O引脚甩软件来虚拟串行总线的功能。

12C总线系统示意图如图8—2所示。

【8—2】如何构造80C51单片机并行扩展的系统总线?【答】80C51并行扩展的系统总线有三组。

①地址总线(A0~A15):由P0口提供低8位地址A0~A7,P0 口输出的低8位地址A0~A7必须用锁存器锁存,锁存器的锁存控制信号为单片机引脚ALE输出的控制信号。

由P2口提供高8位地址A8~A1 5。

②数据总线(DO~D7):由P0 口提供,其宽度为8位,数据总线要连到多个外围芯片上,而在同一时间里只能够有一个是有效的数据传送通道。

哪个芯片的数据通道有效则由地址线控制各个芯片的片选线来选择。

③控制总线(CB):包括片外系统扩展用控制线和片外信号对单片机的控制线。

电子与信息工程学院单片机原理及应用第八章MCS-51单片机并行扩展技术dada哈尔滨工业大学电子与信息工程学院2015 .春季学期2015/1/111第八章MCS-51单片机并行扩展技术MCS-51单片机并行扩展技术【学习目的和要求】•了解MCS-51单片机数据总线、地址总线和控制总线的构成。

•掌握片外扩展程序存储器和数据存储器的方法,及扩展存储单元的地址分析方法。

•掌握MCS-51单片机基本I/O口的应用与扩展,可编程I/O接口芯片8255和8155的性能特点和使用方法。

第八章MCS-51单片机并行扩展技术8.1并行扩展方式8.2程序存储器扩展8.3 数据存储器扩展8.4存储器的综合扩展8.5简单并行I/O接口扩展8.68255A可编程并行接口扩展8.78155可编程并行接口扩展单片机构成的最小应用系统扩展概述典型的单片机应用系统第八章内部数据存储器(a )8031/51系列外部数据存储器(b )MCS-51单片机存储器空间分配特殊功能寄存器00H 1FH 20H2FH30H7FH80HFFH80H 88H 90H 98H A0H A8H B0H B8H D0H E0H F0H 特殊功能寄存器中位寻址外部ROM 内部ROM (EA=1)外部ROM (EA=0)0000H 0000H 0FFFH 0FFFH 1000H FFFFH 外部RAM (I/O 口地址)0000HFFFFH 程序存储器(c )工作寄存器区位寻址区通用RAM 区位寻址区通用RAM 区特殊功能寄存器扩展概述在由单片机构成的实际测控系统中,最小应用系统往往不能满足要求,因此在系统设计时首先要解决系统扩展问题。

系统扩展问题,内容主要有:1 外部存储器的扩展(1)外部程序存储器(ROM)(2)外部数据存储器(RAM)2 I/O接口部件的扩展。

单片机的系统扩展方法主要有:并行扩展和串行扩展按其功能通常把系统总线分为三组: 1.地址总线(Adress Bus,简写AB)2.数据总线(Data Bus,简写DB)3.控制总线(Control Bus,简写CB )系统扩展结构图:单片机的并行扩展是指单片机与外围扩展单元采用并行接口的连接方式,数据传输为并行传送方式。

第八章MCS-51单片机并行扩展技术8.1并行扩展方式11P0.0-0.7:8位数据和低8位地址信号,复用总线AD0-7。

P2.0-2.7:高8位地址信号AB8~15ALE :地址锁存允许控制信号(P0口锁存)EA :片内、片外ROM 选择PSEN :外扩ROM 的读选通控制信号RD :外扩RAM 和I/O的读选通控制信号。

WR :外扩RAM 和I/O的写选通控制信号MCS-51用于扩展存储器的外部总线信号:第八章MCS-51单片机并行扩展技术8.1并行扩展方式8.2程序存储器扩展8.3 数据存储器扩展8.4存储器的综合扩展并行扩展存储器的寻址过程分为两个步骤:1. 存储器芯片的寻址选择存储器2. 芯片内部存储单元的寻址系统地址总线与该存储器芯片的地址总线相连即可。

(1) 线选法(2) 译码法并行扩展的寻址方法0#芯片A0A1A2CS (6000H~7FFFH)A0A1A2A151#芯片A0A1A12CS (0A000H~0BFFFH)A0A1A12A142#芯片A0A1CS (0C000H~0DFFFH)A0A1A13...(1) 线选法:直接采用系统的高位地址线作为存储芯片的片选信号。

特点:连线简单,不需要设计逻辑电路。

但是芯片占用的存储空间不紧凑,地址空间利用率低,一般用于简单的系统扩展。

▪2. 译码法寻址由译码器组成译码电路对系统的高位地址进行译码,译码电路将地址空间划分若干块,其输出作为存储器芯片的片选信号分别选通各芯片通过地址线译码。

▪特点:既充分利用了存储空间,又克服了空间分散的缺点,还可以减少I/O 口线。

▪由于80C51采用不同的控制信号和指令,尽管ROM 与RAM 的地址是重叠的,也不会发生混乱。

▪80C51对片内和片外ROM 的访问使用相同的指令,两者的选择是由硬件实现的。

存储器的并行扩展并行扩展: ROM 最大容量为64KBRAM 最大容量为64KB当扩展64KB 时外部ROM 和RAM 地址均为0000H ~0FFFFH第八章MCS-51单片机并行扩展技术8.2~8.4存储器扩展1存储器扩展常用芯片常用的存储器芯片外部扩展常用程序存储器芯片有EPROM:2764A/ 27128A/ 27256A/ 27512A外部扩展常用数据存储器芯片有静态RAM(SRAM):6264 / 62128 / 62256 / 62512第八章MCS-51单片机并行扩展技术 1. 地址锁存器/并口输出芯片地址锁存器常用的有带三态缓冲输出的8D锁存器74LS373(74LS374)、74LS573、8282,带有清除端的74LS273等。

WR OECLK第八章MCS-51单片机并行扩展技术2. 译码器-地址译码常用的译码器芯片有74LS138(3-8译码器)、74LS139(2-4译码器)和74LS154(4-16译码器)RD 1G2G 3.总线缓冲器扩展并行输入口常用的单向总线缓冲器74LS244,双向驱动器74LS24574LS244内部有两组4位三态缓冲器,具有数据缓冲隔离和驱动作用第八章MCS-51单片机并行扩展技术2 存储器扩展方法外部存储器扩展需要注意以下几个问题:(1)选择合适类型的存储器芯片(2)工作速度匹配(3)选择合适的存储容量(4)合理分配存储器地址空间(5)合理选择地址译码方式第八章MCS-51单片机并行扩展技术3 典型的存储器扩展1.单片存储器的扩展EPROMEAPSENCEOE单片机与外部EPROM的连接图ALE:地址锁存允许控制信号,下降沿锁存PSEN:片外程序存储器读控制信号EA:程序存储器选择第八章MCS-51单片机并行扩展技术单片存储器的扩展RAMCEOE单片机与外部RAM的连接图RD:外扩RAM和I/O的读选通控制信号。

WR:外扩RAM和I/O的写选通控制信号第八章MCS-51单片机并行扩展技术单片机与外部RAM的连接图单片存储器的扩展RAM第八章MCS-51单片机并行扩展技术源程序:ORG 1000H MOV R0, #50H ;数据指针指向片内50H 单元MOV R7, #16;传送数据个数送计数寄存器MOV DPTR, #0000H ;数据指针指向RAM 的0000H 单元LOOP :MOV A, @R0;输出数据送累加器A MOVX @DPTR, A ;数据输出至片外RAM INC R0;修改片内数据指针INC DPTR ;修改片外数据指针DJNZ R7, LOOP ;未传送完循环END单芯片存储器扩展/IO 口扩展读:MOVX A,@Ri 写:MOVX @Ri,A 读:MOVX A,@DPTR 写:MOVX@DPTR ,A第八章MCS-51单片机并行扩展技术2. 多片存储器的扩展EPROM(1)采用线性选择法,即用剩余的地址线连接片选信号PSENCEOEEACEOECEOEMOVC A,@A+DPTR第八章MCS-51单片机并行扩展技术CEOEEACEOECEOE W R W R WR WRRD(1)采用线性选择法,即用剩余的地址线连接片选信号2. 多片存储器的扩展RAMMOVX A,@DPTRMOVX@DPTR, A第八章MCS-51单片机并行扩展技术(1)采用线性选择法,即用剩余的地址线连接片选信号综合扩展2. 多片存储器的扩展RAM &EPROMCEOEEACEOECEOE W R W R WR WRRDPSEN第八章MCS-51单片机并行扩展技术综合扩展扩展一片62256 RAM和一片27256 ROM。

EACEOECEOE WRWRRDP S E N(1)采用线性选择法,即用剩余的地址线连接片选信号为什么不发生冲突2. 多片存储器的扩展RAM &EPROM第八章MCS-51单片机并行扩展技术(2)采用全地址译码,即所有的地址线都参与译码。

PSENCEOEEACEOECEOEG0Y1Y2Y2. 多片存储器的扩展EPROMMOVC A,@A+DPTR第八章MCS-51单片机并行扩展技术CEOEEACEOECEOEG0Y1Y2YWR WR WR WRRD2. 多片存储器的扩展RAM(2)采用全地址译码,即所有的地址线都参与译码。

MOVX A,@DPTRMOVX@DPTR, ACE OE EACEOE CEOEGY 1Y 2Y WRWRWRRD PSEN第八章MCS-51单片机并行扩展技术(2)采用全地址译码,即所有的地址线都参与译码。

综合扩展2. 多片存储器的扩展RAM &EPROM第八章MCS-51单片机并行扩展技术4存储器的操作时序访问外部数据存储器MOVC A,@A+DPTR MOVC A, @A+PC访问外部数据存储器有两组指令,它们的寻址空间不同。

1. 8位寻址指令读数据:MOVX A,@Ri 写数据:MOVX @Ri,A只访问外部RAM的低256字节空间,使用低8位地址线寻址,将高8位地址线(P2口线)清0。

2. 16位寻址指令读数据:MOVX A,@DPTR 写数据:MOVX @DPTR ,A要访问的外部RAM空间大于256字节时,使用这组指令。

由于DPTR 为16位地址指针,故可寻址空间为64KB。

第八章MCS-51单片机并行扩展技术PSEN访问外部程序存储器的操作时序EPROM操作时序ALE:地址锁存允许控制信号,下降沿锁存PSEN:片外程序存储器读控制信号EA:程序存储器选择第八章MCS-51单片机并行扩展技术RAM 操作时序访问外部数据存储器的操作时序第八章MCS-51单片机并行扩展技术存储器的综合扩展1. 采用线性选择法扩展一片62256 RAM和一片27256 ROM。

逻辑电路如图8-15所示。

EACEOECEOE WRWRRDP S E N第八章MCS-51单片机并行扩展技术2.采用全地址译码法扩展16KB程序存储器和32KB数据存储器。

逻辑电路如图8-16所示。

CEOEEACEOECEOEG0Y1Y2YWR WR WRRDPSEN第八章MCS-51单片机并行扩展技术3.程序存储空间和数据存储空间的混合第八章MCS-51单片机并行扩展技术8.1并行扩展方式8.2程序存储器扩展8.3数据存储器扩展8.4存储器的综合扩展8.5简单并行I/O接口扩展I/O (输入/输出)接口是MCS-51与外设交换数字信息的桥梁。

I/O扩展也属于系统扩展的一部分。

MCS-51真正用作I/O口线的只有P1口的8位I/O线和P3口的某些位线。