短波扩频猝发通信系统的DSP+FPGA实现方案

- 格式:doc

- 大小:214.00 KB

- 文档页数:5

基于FPGA的猝发多脉冲产生系统设计与实现冯传均;何泱;戴文峰【摘要】脉冲功率装置在猝发工作方式下各个子系统需要按照一定的脉冲时序协调工作,其控制系统需要实现较好的时刻控制功能.介绍了一种基于FPGA的猝发多脉冲产生系统,可以通过上位机监控界面设定猝发脉冲参数,经由RS232串口通信协议将数据下载到FPGA控制器进行解析存储,并可以产生对应的猝发脉冲信号.系统可输出2路猝发多脉冲信号,猝发脉冲串个数1~5个可调,猝发脉冲串间隔1~200 s可调,猝发脉冲串内部脉冲个数1~5个可调,猝发脉冲串内部脉冲频率1~100 Hz可调,猝发脉冲串内部脉冲宽度等参数可以调节.【期刊名称】《微型机与应用》【年(卷),期】2018(037)008【总页数】3页(P70-72)【关键词】FPGA;上位机监控;猝发脉冲;VerilogHDL;串口通信【作者】冯传均;何泱;戴文峰【作者单位】中国工程物理研究院流体物理研究所脉冲功率科学与技术重点实验室,四川绵阳621900;中国工程物理研究院流体物理研究所脉冲功率科学与技术重点实验室,四川绵阳621900;中国工程物理研究院流体物理研究所脉冲功率科学与技术重点实验室,四川绵阳621900【正文语种】中文【中图分类】TP230 引言脉冲功率技术是一种功率压缩技术,以较低的输入功率将能量缓慢存储起来,随后在极短时间内释放,以获得极高的峰值输出功率。

该技术是应国防科技需要而发展起来的一门新兴科学技术,是获得高电压、大电流等极端电磁参数的重要手段,被广泛应用在科学研究和工业生产等诸多领域中[1-3]。

脉冲功率装置一般由初级能源系统、中间储能系统、脉冲形成系统、开关转换系统和负载系统5个子系统组成。

工作时,初级能源系统用于为脉冲功率装置供能,将能量输送至中间储能系统中;中间储能系统常见远重频或猝发脉冲功率装置,通过初步功率压缩为脉冲形成系统供能;脉冲形成系统充电完成后,通过开关转换系统将能量快速传递给负载系统,实现脉冲功率输出。

短波扩频通信系统中数字相关器的FPGA设计与实现摘要基于设计的数字相关器,对前端模数/转换器在384采样率下采得的数据进行希尔波特变换,再与本地序列做相关运算,最后将相关结果送给,供做进一步的处理。

介绍了所选用的芯片,阐述了内部子模块的功能和设计实现方法,对所设计的数字相关器进行了仿真和校验,结果达到了设计要求。

关键词数字相关器希尔波特变换采用FPGA器件可以将原来的电路板级产品集成为芯片级产品,从而降低了功耗、提高了可靠性,同时还可以很方便地对设计进行在线修改。

电路设计者可以通过软件编程,经过设计输入、仿真、测试和校验,用硬件实现特定的数字信号处理算法。

这种方法由于具有通用性强的特点并可以实现算法的并行运算,因此无论是作为独立的数字信号处理器,还是作为DSP芯片的协处理器,目前都是比较活跃的研究领域。

短波通信具有设备简单、通信距离远、机动灵活、价格低廉和抗毁性强的特点,有着重要的应用价值。

在短波通信系统中,接收方在信号检测、同步的过程中,要进行大量的乘加操作来做相关运算。

在传输速率较高、样点间隔较小的情况下,完全由系统中央DSP处理器进行运算,很难实现实时处理。

利用FPGA的特点,把信号同步数字相关部分分离出来,设计一个专用的数字相关器,作为中央DSP处理器的协处理器,来分担这部分工作,是一个很好的解决方案。

本文阐述的就是这样一个应用在短波扩频通信系统的接收方中,完成数字相关功能的基于FPGA设计的相关器。

1Stratix系列芯片简介本文采用Stratix系列芯片实现数字相关器。

Stratix系列是著名的可编程逻辑器件供应商Altera公司于2002年新推出的FPGA产品。

其主要特点是采用1.5V内核,0.13μm全铜工艺,容量为10570~114140个逻辑单元,内嵌多达10Mbit的三种RAM块,即512bit容量的小型RAM,4KB容量的标准RAM,512KB的大容量RAM;具有True-LVDStm电路,支持LVDS、LVPECL、PCML和HyperTranporttm差分I/O电气标准,且有高速通信接口;增加了片内终端匹配电阻,提高了信号完整性,简化了PCB布线;提供了完整的时钟管理方案,具有层次化的结构和多达12个锁相环PLL。

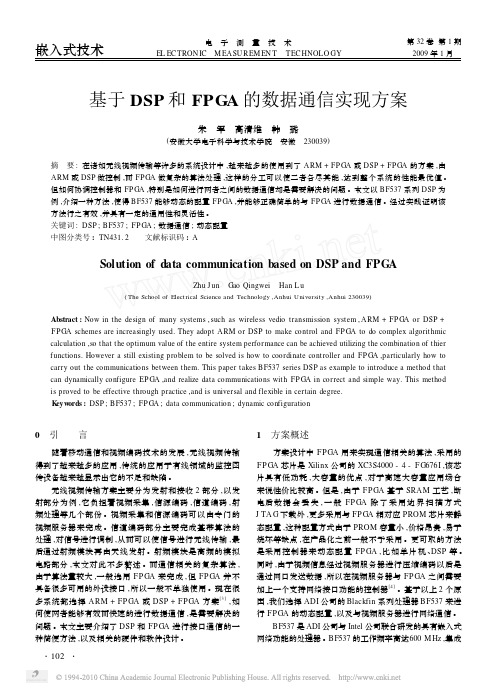

嵌入式技术 电 子 测 量 技 术 EL ECTRON IC M EASU REM EN T TECHNOLO GY 第32卷第1期2009年1月 基于DSP和FPGA的数据通信实现方案朱 军 高清维 韩 璐(安徽大学电子科学与技术学院 安徽 230039)摘 要:在诸如无线视频传输等许多的系统设计中,越来越多的使用到了ARM+FP GA或DSP+FP GA的方案,由ARM或DSP做控制,而FP GA做复杂的算法处理,这样的分工可以使二者各尽其能,达到整个系统的性能最优值。

但如何协调控制器和FP GA,特别是如何进行两者之间的数据通信却是需要解决的问题。

本文以BF537系列DSP为例,介绍一种方法,使得BF537能够动态的配置FP GA,并能够正确简单的与FP GA进行数据通信。

经过实践证明该方法行之有效,并具有一定的通用性和灵活性。

关键词:DSP;BF537;FP GA;数据通信;动态配置中图分类号:TN431.2 文献标识码:ASolution of data communication based on DSP and FPGAZhu J un Gao Qingwei Han L u(The School of Electrical Science and Technology,Anhui University,Anhui230039)Abstract:Now in the design of many systems,such as wireless vedio transmission system,ARM+FP GA or DSP+ FP GA schemes are increasingly used.They adopt ARM or DSP to make control and FP GA to do complex algorithmic calculation,so that the optimum value of the entire system performance can be achieved utilizing the combination of thier functions.However a still existing problem to be solved is how to coordinate controller and FP GA,particularly how to carry out the communications between them.This paper takes BF537series DSP as example to introduce a method that can dynamically configure EP GA,and realize data communications with FP GA in correct and simple way.This method is proved to be effective through practice,and is universal and flexible in certain degree.K eyw ords:DSP;BF537;FP GA;data communication;dynamic configuration0 引 言随着移动通信和视频编码技术的发展,无线视频传输得到了越来越多的应用,传统的应用于有线领域的监控图传设备越来越显示出它的不足和缺陷。

扩频通信FPGA设计概述:扩频通信技术是指通过将信号的带宽扩展到原信号的数十倍甚至数百倍,然后传输到接收端,在接收端通过相关的算法恢复出原信号。

FPGA (Field Programmable Gate Array)是一种可编程逻辑器件,适用于高速、大规模数字逻辑设计,广泛应用于通信、图像处理等领域。

本文将介绍扩频通信系统中FPGA的设计。

扩频通信的原理:扩频通信的核心技术是采用扩频序列进行信号调制和解调。

在传输端,原始信号经过扩频序列调制后变为扩频信号,在接收端通过相关的扩频序列解调,恢复出原始信号。

扩频序列的选择和设计是关键,常用的扩频序列有PN序列、Gold序列等。

FPGA在扩频通信中的作用:FPGA在扩频通信系统中扮演着非常重要的角色。

FPGA可以实现扩频信号的调制和解调,同时也可以实现其他相关功能,如同步检测、误码率测量、通道编码解码等。

通过使用FPGA,可以提高系统的灵活性和可扩展性,同时也可以实现高性能的处理和运算。

FPGA的设计要点:1.系统架构设计:在进行FPGA设计时,需要首先确定系统的整体架构。

包括选择合适的FPGA器件、确定FPGA与其他硬件模块的接口和数据传输方式等。

2.扩频调制与解调:扩频调制和解调是扩频通信系统中最关键的部分。

在FPGA中,可以使用特定的模块进行扩频序列的生成和调制,同时也可以使用相关的模块进行扩频信号的解调和原信号的恢复。

3.时钟和同步控制:扩频通信系统中的时钟和同步控制非常重要。

FPGA可以通过内部时钟管理模块实现对时钟的生成和管理,同时也可以使用同步控制模块确保系统各部分之间的同步和通信。

4.误码率测量与纠错编码解码:在扩频通信系统中,误码率的测量和纠错编码解码是保证系统可靠性的重要环节。

FPGA可以实现对误码率的测量和纠错编码解码的功能,提高系统的抗干扰和容错性能。

5.数据接口和处理:扩频通信系统中需要进行数据的收发和处理。

FPGA可以通过外部接口模块实现与其他设备的数据交换,同时通过内部数据处理模块实现对数据的加工和处理。

基于DSP和FPGA的嵌入式数字直接序列扩频系统的研制王甲池;江太辉

【期刊名称】《电讯技术》

【年(卷),期】2003(043)006

【摘要】介绍了一种基于Xilinx公司的FPGA (Spartan2 XC2S200)和TI公司的DSP TMS320VC5410设计的直接序列扩频收发机,其下变频后的部分,如PN码的捕获、跟踪、基带解调(去掉剩余频差)等全部采用FPGA数字实现.对PN码的捕获,采取了一种门限自适应控制的双积分滑动相关捕获方法,既大大节省了FPGA的硬件设计资源,又能使PN码的平均捕获时间足够小.经实验测试,该系统各参数完全达到设计要求.

【总页数】5页(P99-103)

【作者】王甲池;江太辉

【作者单位】五邑大学,信息学院,广东,江门,529020;五邑大学,信息学院,广东,江门,529020

【正文语种】中文

【中图分类】TN914.4

【相关文献】

1.一种基于FPGA的直接序列扩频通信系统发射端的设计 [J], 冯雪;庞尚珍

2.基于FPGA直接序列扩频系统的设计 [J], 张波涛;赵榉云;李剑;姚金杰

3.基于FPGA直接序列扩频系统的设计 [J], 张丽山;王建华

4.一种基于 FPGA 的直接序列扩频通信系统接收端的设计 [J], 冯雪;庞尚珍

5.基于FPGA的直接序列扩频发射系统研究 [J], 祝炎明;何加铭;金宁

因版权原因,仅展示原文概要,查看原文内容请购买。

基于C语言在FPGA上实现DSP的解决方案硬件设计者已经开始在高性能DSP的设计中采用FPGA技术,因为它可以提供比基于PC或者单片机的解决方法快上10-100倍的运算量。

以前,对硬件设计不熟悉的软件开发者们很难发挥出FPGA的优势,而如今基于C语言的方法可以让软件开发者毫不费力的将FPGA的优势发挥得淋漓尽致。

这些基于C 语言的开发工具可以比基于HDL语言的硬件设计更节省设计时间,同时不需要太多的硬件知识。

由于具有这些优势,FPGA技术不仅可使这些器件作为I/O 器件的前端,FPGA还可实现大量的高带宽和运算密集型应用的实时处理。

此外,FPGA还可很紧密地与板上存储器结合,并在一块电路板上集成多个器件。

更好的是,FPGA电路板可通过新兴的串口通讯标准进行通讯,如RapidI/O或者PCIX。

这些最新技术可让基于FPGA的系统比现有的多CPU和DSP系统的性价比高出一个数量级。

因此,在用CPU和DSP解决高带宽和算法密集问题的场合中,例如医疗成像、工业应用以及军用声纳和雷达等,经常使用FPGA。

设计者利用这些新型的基于C语言的开发工具来开发DSP(在一块PCI 板上安装单块或多块FPGA处理器),就可以实现前面提到的改进性能以及更短的面世时间。

这篇文章向设计者展示了如何利用C语言工具在基于FPGA的系统中实现信号处理,并一步一步向开发者说明在多FPGA系统中实现算法密集型信号处理程序的过程。

利用C语言对FPGA计算解决方案进行编程,能将把程序的执行时间从12分钟减少到仅为2秒。

1通过C语言与硬件进行接口假设您在设计一个算法密集的信号处理程序,例如分析上千公里长公路的裂缝。

这种应用需要用到正/逆向霍夫变换的算法,该算法还可对航拍图片中的河流和街道以及半导体表面的瑕疵进行定位。

如果你正使用基于奔腾4和WindowsXP 的PC、带有多个FPGA的PCI板(例如Tsunami板)、C语言开发环境和Handel-C(Celoxica开发环境)来进行设计,并假设你对HDL硬件语言所知甚少,却熟悉基于FPGA设计的一些基础知识。

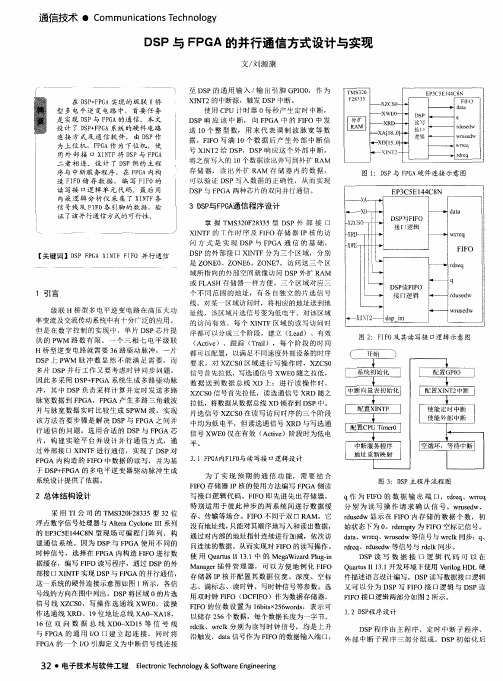

信息技术电子测量技术ELECTRONICMEASUREMENTTECHNOLOGY第31卷第10期200810DSP和FPGA并行通信方法研究姜楠马迎建冯翔(北京航空航天大学仪器科学与光电工程学院北京100083)摘要:本文介绍了一种DSP与FPGA之间的并口通信方法,它实际应用于陀螺数字检测电路。

此方法使用TMS320F2812芯片的外部数据总线接口(XINTF)与FPGA相连接,利用它的中断和读写选通信号(XRD与XWE)作为判断位与使能位完成通信。

文中给出了它们的硬件连接方式和通信部分的软件程序,并用modelsim对FPGA通信程序进行了仿真。

通过仿真结果以及在实际电路中的实验调试,表明此方法可以实现DSP与FPGA之间的并行通信,能有效提高通信速度。

关键词:DSP;FPGA;外部接口;并行通信;modelsim中图分类号:TP2文献标识码:AResearchonandFPGAMaYingjian FengXiang(ofScience&Opto2ElectronicEngineering,BeihangUniversity,Beijing100083) Abstract:MethodofcommunicationbetweenDSPandFPGAwasintroduced,whichusedinthe gyroscopedigitaldetectioncircuit.Theexternalinterface(XINTF)databusoftheTMS320F28 12chipisconnectedwithFPGAinthemethod.TheinterruptsignalsoftheDSPareusedasjudgm entsignals,andtheread2writeselect(XRDandXWE)signalsareusedasenablesignalstocompl etecommunication.ThehardwareinterfacecircuitbetweenDSPandFPGAandthesoftwarepr ogramofcommunicationpartareintroduced.ThentheFPGAcommunicationprogramissimul atedbymodelsim.Throughtheresultofthesimulationandtheexperimentdebuggingintherealc ircuit,itisindicatedthatthemethodcanachievecommunicationbetweenDSPandFPGA,andth espeedofcommunicationisimprovedavailably.Keywords:DSP;FPGA;ExternalInterface;p arallelcommunication;modelsim0引言在航空领域中,陀螺在导航中起着重要作用。

引言短波通信是一种能进行远距离传输,而对电台的要求相对较低的通信系统。

短波具有的远距离通信能力和电台具有的较高机动性等特点,使其在军事通信领域中具有重要的应用价值。

然而,短波信道频带窄,传播特性不稳定,干扰严重,信号易被敌人截获、测向和干扰。

一种有效的抗干扰措施就是将扩展频谱通信技术及猝发通信技术应用于短波通信中,进行短波超快速扩频猝发通信。

随着现代通信技术的飞速发展,特别是扩频技术在第三代移动通信中的成功应用,为实现短波扩频通信和猝发扩频数据传输奠定了技术基础。

超大规模集成电路和高速信号处理器高效的处理能力和处理速度也为实现短波猝发扩频数据传输提供了良好的硬件平台。

本文首先给出了一种DS-QPSK短波扩频猝发通信的系统方案,着重对其中的同步捕获技术进行了研究,采用滑动相关法来实现序列的同步,并运用Matlab工具对其进行了仿真。

然后采用TMS320VC33、TMS320VC5509和ALTERA公司的Cyclone系列FPGA构建了硬件平台,给出了DSP+FPGA的混合硬件实现方案。

短波扩频猝发通信系统方案系统构成本系统采用了直接序列扩频技术来实现无线短波数据的发送和接收。

具体实现是用32位的沃尔什序列对信息速率为2.4Kbps的数据进行直接序列扩频。

在接收端利用扩频码的正交性对数据进行相关解扩,恢复出原始信息,并且由于QPSK调制技术抗噪声性能强,频谱利用率高,结构简单,所以这里采用它作为数据调制方式。

数据传输采用超快速猝发通信方式,即每次通信的时隙限定在100ms左右,发送时隙随机分布,难以被捕获和干扰。

每个时隙的数据发送前要发送一段同步头,用来完成扩频码的识别、扩频码的同步、帧同步和频差估计等任务,接收端根据同步头获得的信息对数据进行解扩恢复。

为了改善性能,运用RAKE接收技术来接收数据,为了进一步提高系统的抗干扰能力,还对信息进行了1/2卷积编码,接收端采用Viterbi译码。

系统的基本框图组成如图1所示,分成发射和接收两部分,分别完成数据的发送和接收功能。

系统同步方案对于扩频系统,接收机要从接收信号中恢复发送的数据信息,必须对接收信号进行解扩。

解扩的实现依靠本地产生与发送端相同的扩频序列,并且要求与接收信号扩频序列同步,这是扩频系统中非常重要的环节。

扩频序列的同步分为捕获和跟踪两个阶段。

捕获阶段完成扩频序列的粗同步,将收、发端扩频序列的相位差限制在一个码片或更小的范围内;跟踪阶段实现收、发端扩频序列的精确同步,让本地参考信号精确跟踪接收信号的相位变化。

如何可靠的实现扩频序列的快速捕获是影响系统性能的关键。

常用的同步捕获方法有滑动相关法、同步头法、跳频同步法、发射参考信号法、匹配滤波器同步法等,而滑动相关法是一种最简单、最实用的捕获方法。

本文采用的就是这种方法。

确定信号捕获和完成码元同步,要求同时满足以下三个准则:①在连续4个接收码元中至少有3个与预定同步码的顺序相吻合;②接收到的单音功率谱峰值高过门限;③各单音出现峰值间隔连续且次序正确。

在本系统中,由于采用的是猝发通信形式,时隙较短,仅为100ms左右,因此可以认为信道短时平稳,发送数据的同步信息也可以一次确定,而且也可认为多径的每条路径上的时延也基本是恒定,因此只需由前导序列一次确定相关同步信息。

由于发送的前导序列是双方约定好的正交码序列集,接收端利用码字的正交性,用本地序列与接收序列滑动相关,相关峰最大值所对应的位置即为同步点。

如表1所示为发送数据帧结构。

同步序列由48个32位Walsh序列构成,采用了级联编码。

第一层编码为沃尔什序列加扰码。

对于沃尔什序列来说,同步情况下的自相关和互相关性能很好。

但是在非同步的情况下,沃尔什序列的正交性变差,相关函数有较大的旁瓣值,造成信号间的干扰。

为减小旁瓣值,改善Walsh码的特性,用扰码乘以沃尔什序列,得到的新码作为前导序列的内码,则相关性能得到改善。

第二层是对Walsh序列与48个相位组合的相乘,其中48个相位组合为/4,3 /4,- /4,-3 /4的排列组合。

经Matlab仿真取一组使所得到的相关峰较为理想,如图2所示。

基于DSP+FPGA的硬件平台本系统采用TI公司的高性能浮点数字信号处理器TMS320VC33和定点的TMS320VC5509两片DSP芯片作为系统的中央CPU,并采用ALTERA公司的Cyclone系列FPGA设计出高速数字相关器,用于前端的信号同步与捕获,三个芯片协同工作,并以此为主体架构系统的整个硬件工作平台。

主要芯片介绍TMS320VC33是TI公司推出的高性能浮点运算DSP芯片。

由于其较高的性能价格比,使其应用较为广泛。

它的结构允许它以定点的速率完成浮点操作,因此非常适合于做高速高精度的浮点运算,这一优点对于像短波信道快速估值等实时性精确度要求特别高的数字信号处理应用显得尤为重要。

TMS320VC5509处理器是TI公司最新推出的高性能低功耗定点数字信号处理器TMS320C55x系列中的一员。

TMS320C55x系列是在C54x系列的基础上发展起来的,能与C54x兼容,不仅增加了硬件资源,也优化了资源管理。

TMS320VC5509运行速度快,还可以进行多种并行操作,片内外设资源也比较丰富,与外围设备的连接很方便,所以非常适合用来作控制用。

根据上述两种处理器的特点,综合考虑系统的设计要求,我们把TMS320VC5509作为系统的主处理器,而TMS320VC33作为其协处理器。

本文是采用Cyclone系列芯片来实现数字相关器对采样点值进行一次相关,将相关结果送给中央处理器DSP,进行下一步的同步和解扩等处理。

ALTERA公司的Cyclone器件具有专用电路,可以实现双数据率(DDR)SDRAM和FCRAM接口。

Cyclone器件最多有两个锁相环(PLL),共有六个输出和四种层次化结构,为复杂设计提供了强大的时钟管理电路。

系统硬件模型框图及概述首先从电台接收过来的基带扩频信号是差分输入的,先经过一个1:1的隔离变压器变为单端输出,再经过运放将其抬高到直流电平以上,低通滤波后送到模数转换器AD7492 进行采样处理,采样结果在FPGA中锁存,并在FPGA内部进行希尔伯特变换和相关处理。

在一个样点间隔内,进行当前样点值的希尔伯特变换,同时并行地进行前一个样点的相关运算。

将相关结果分成四个部分,锁存在对应的四个地址中,由TMS320VC5509分四次依次读取。

由TMS320VC5509和TMS320VC33完成信号的捕获和码元的判决。

将处理好的数据通过TMS320VC5509送到数模转换器TLV5619中进行数模转换,转换得到的模拟信号经过低通滤波和运放放大以后,再通过同样的一个1:1的隔离变压器变为差分输出送到扩频电台。

如图3所示为系统的核心部分。

TMS320VC5509 和TMS320VC33的互通本方案采用的是用DSP串口来实现TMS320VC5509和TMS320VC33之间的通信。

由于TMS320VC5509的多通道缓冲串口远比TMS320VC33的串行口功能强大,设置灵活,所以在设计的时候我们就考虑将TMS320VC5509的串口设为主方,TMS320VC33的串口设为从方,连接图如图4所示。

将TMS320VC5509内部采样速率发生器的输入参考时钟设置为CPU时钟,通过对CPU时钟的分频来得到串口移位时钟和帧同步信号,并由TMS320VC5509提供收发双方的移位时钟,而帧同步信号则由发送方提供。

同时将TMS320VC33设置为标准模式、固定速率的工作方式,与TMS320VC5509的串口匹配。

通过双方设置可以进行每帧16bit或32bit 的传输。

这样双方DSP可以通过握手,采用中断或查询方式来进行数据的高速收发,并且还可以灵活地对双方串口的工作方式进行改进。

下面给出TMS320VC5509多通道缓冲串口及TMS320VC33串行口通信的关键程序段。

TMS320VC5509多通道缓冲串口初始化程序:MOV #0x0000,PORT(#SPCR2_1) ;采用多通道缓冲模式MOV #0x0000,PORT(#SPCR1_1)MOV #0x0040,PORT(#RCR1_1) ;接收每帧1个阶段,每阶段1个字,字长MOV #0X0001,PORT(#RCR2_1) ;16比特,不压扩,1比特延迟MOV #0x0040,PORT(#XCR1_1) ;发送每帧1个阶段,每阶段1个字,字长MOV #0X0001,PORT(#XCR2_1) ;16比特,不压扩,1比特延迟MOV #0x0003,PORT(#SRGR1_1) ;脉宽1个clkr/x,clkr/x为4分频(最大)MOV #0x200f,PORT(#SRGR2_1)MOV #0x0B00,PORT(#PCR1) ;fsr设为输入MOV #0x0040,PORT(#SPCR2_1) ;GRST=1,启动采样速率发生器MOV #0x00c0,PORT(#SPCR2_1) ;FRST=1,启动帧同步MOV #0x00c1,PORT(#SPCR2_1) ;XRST=1,启动发送器MOV #0x0001,PORT(#SPCR1_1) ;RRST=1,启动接收器TMS320VC33串行口初始化程序:LDI @p0_addr,ar0 ;p0_addr=808040h 总体控制寄存器LDI 331h,r1 ;FSX/DX 设定为输出CLKX设定为输入STI r1,*+ar0(2) ;FSX/DX/CLKX串口控制寄存器LDI 111h,r1 ;FSR/DR/CLKR设定为输入STI r1,*+ar0(3) ;FSR/DR/CLKR串口控制寄存器LDI @p0_global,r1 ;00e940004h 固定速率标准模式16bit STI r1,*ar0LDI @buff_rec,ar7 ;接收缓冲区LDI 020h,ie ;CPU串行端口0接收中断启用STIR1,*+AR0(8);AR0指向串行端口总体控制寄存器(00808040h)结束语现代通信技术和超大规模集成电路以及高速信号处理器的高速发展,使得短波猝发扩频通信在军事通信中极具潜力。

本文给出了一种DS-QPSK短波扩频猝发通信的系统实现方案,并运用TMS320VC33、TMS320VC5509和ALTERA公司的Cyclone系列FPGA构建的硬件平台进行了DSP+FPGA的混合硬件实现,得到的系统性能已达到预期的要求,实现了数据的有效实时处理。