spectraverilog数模混合仿真

- 格式:doc

- 大小:152.50 KB

- 文档页数:6

verilog和VHDL混合编译仿真在实际项⽬中,由于项⽬经历了较多的版本更迭或者设计⼈员的技术⽔平限制,有些时候难免有使⽤到verilog的代码和VHDL代码共同存在⼀个项⽬中的情况,那这个时候我们要怎样进⾏混合编译仿真验证呢?这⾥以使⽤vcs⼯具编译verdi查看波形为例:如果我们设计代码是vhdl版本的,但是还想使⽤更⾼级的代码verilog或者systemverilog作为它的顶层tb,并且还想使⽤uvm的组件来搭建更⽅便的验证环境,那么整个环境的编译和执⾏过程如下:1.需要准备的软件vcs-mx和verdi,其中vcs-mx版本会有vlogan和vhdlan两个编译程序2.开始编译编译vhdl的代码,dut_src.f是vhdl的⽂件列表:vhdlan -nc dut_src.f -l cmp_vhdl.log编译uvm库的sv代码:vlogan -full64 -timescale=1ns/1ps +v2k -sverilog -ntb_opts uvm -l cmp_uvm.log编译我们⾃⼰设计的sv代码和⾃⼰设计的uvm各个组件部分的代码,tb.f是⽂件列表:vlogan -full64 -timescale=1ns/1ps +v2k -sverilog tb.f -ntb_opts uvm -l cmp_verilog.log编译vhdl和verilog各⾃的库⽣成可执⾏⽂件simv:vcs -timescale=1ns/1ps -ntb_opts uvm -top tb_top -debug_access+pp -fsdb -j56 -cm line+fsm+tgl+cond -lint=TFIPC-L +nbaopt +rad +notimingchecks +nospecify +error+30run起来,⽣成波形,其中TC_NAME是传⼊的tc参数:./simv -cm line+fsm+tgl+cond +fsdb+force +fsdbfile+../wave/tb_top.fsdb +UVM_TESTNAME=$(TC_NAME)3.查看波形编译出verdi可以查看的库,使⽤vhdlcom是编译vhdl⽂件的库,vericom是编译verilog⽂件的库vhdlcom -lib my_work dut_src.fvericom -lib my_work -sv tb_top.sv使⽤verdi打开波形⽂件:verdi -lib my_work -top tb_top -ssf tb_top.fsdb。

混合仿真是指数字与模拟部分混合仿真,模拟部分采用Cadence电路图,数字部分可以采用版图提取网表(如文档前部分所述),也可以直接采用verilog代码生成数字部分symbol。

下面说明采用verilog代码生成数字symbol的过程。

1、首先在工程库中新建一个cell,名字取为DIGIT,tool选用verilog-editor,view取名为functional,确定后会打开默认的文本编辑器(vi),需要在其中编写verilog代码,文件名默认为verilog.v。

vi被自动打开时,module已经自动被起为DIGIT,但输出端口未定义,要自己加进去),退出vi 时,CIW会提示为这个cell建一个symbol,按提示建好后保存。

2、在工程库中新建一个cell,取名为SIM_MM,tool选用composer-schematic,view取名为schematic。

在SIM_MM中,就可以像调用模拟单元一样,把数字部分DIGIT作为一个symbol 引入,将模拟部分连接完毕后保存。

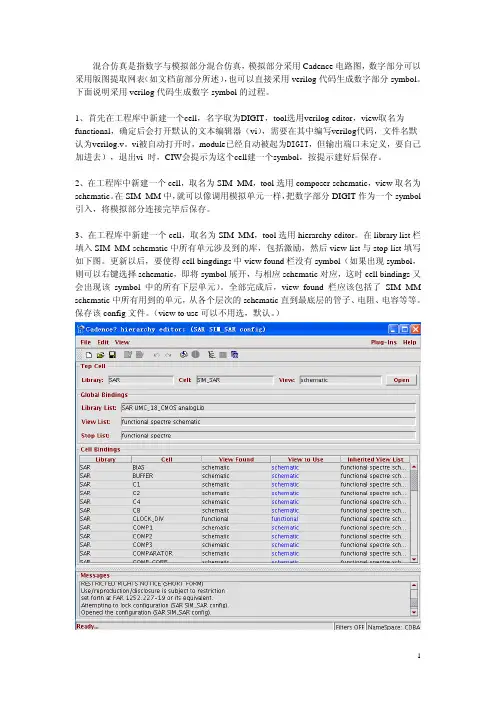

3、在工程库中新建一个cell,取名为SIM_MM,tool选用hierarchy-editor。

在library list栏填入SIM_MM schematic中所有单元涉及到的库,包括激励,然后view list与stop list填写如下图。

更新以后,要使得cell bingdings中view found栏没有symbol(如果出现symbol,则可以右键选择schematic,即将symbol展开,与相应schematic对应,这时cell bindings又会出现该symbol中的所有下层单元)。

全部完成后,view found栏应该包括了SIM_MM schematic中所有用到的单元,从各个层次的schematic直到最底层的管子、电阻、电容等等。

保存该config文件。

(view to use可以不用选,默认。

数模混合ic-概述说明以及解释1.引言1.1 概述数模混合IC是指在一个芯片内集成了模数混合信号电路的集成电路,它将数字电路与模拟电路有机地结合在一起。

随着电子技术的快速发展和市场需求的不断增加,数模混合IC的应用逐渐得到了广泛关注和应用。

数模混合IC主要用于将模拟信号转换为数字信号或将数字信号转换为模拟信号的过程中。

它可以实现模拟信号的采样、滤波、放大、调制、解调等功能,同时能够进行数字信号的处理、编解码、调制解调等操作。

因此,数模混合IC被广泛应用于通信、音视频处理、传感器接口等领域。

数模混合IC的设计流程主要包括需求分析、系统设计、电路设计、电路仿真、布局布线、验证测试等多个环节。

在设计过程中,需要考虑电路的性能指标、功耗、面积、成本等因素,以确保设计出满足实际应用需求的芯片。

数模混合IC相比于传统的模拟电路和数字电路独立设计的方式,具有一定的优势和挑战。

它可以减少电路间的接口,简化系统设计,提高集成度和性能。

然而,由于数字和模拟电路之间的互相影响和干扰,数模混合IC的设计和验证相对较为复杂,对设计人员的技术水平要求较高。

总之,数模混合IC作为一种集成度高、功能强大的芯片设计技术,具有广泛的应用前景。

随着科技的不断进步和市场需求的不断变化,数模混合IC的应用将得到进一步的推广和发展。

未来,数模混合IC设计将更加注重低功耗、高性能、高集成度和低成本等方面的探索,为各个领域的应用提供更加优越的解决方案。

1.2文章结构文章结构部分的内容可以按照以下方式进行编写:2. 文章结构本文分为引言、正文和结论三个部分。

每个部分包含多个小节,具体的结构如下:2.1 引言2.1.1 概述2.1.2 文章结构2.1.3 目的2.1.4 总结2.2 正文2.2.1 数模混合IC的定义2.2.2 数模混合IC的应用领域2.2.3 数模混合IC的设计流程2.2.4 数模混合IC的优势和挑战2.3 结论2.3.1 数模混合IC的发展前景2.3.2 数模混合IC的应用推广2.3.3 数模混合IC的未来发展方向2.3.4 总结在引言部分,我们将概述整篇文章的主要内容、目的以及总结。

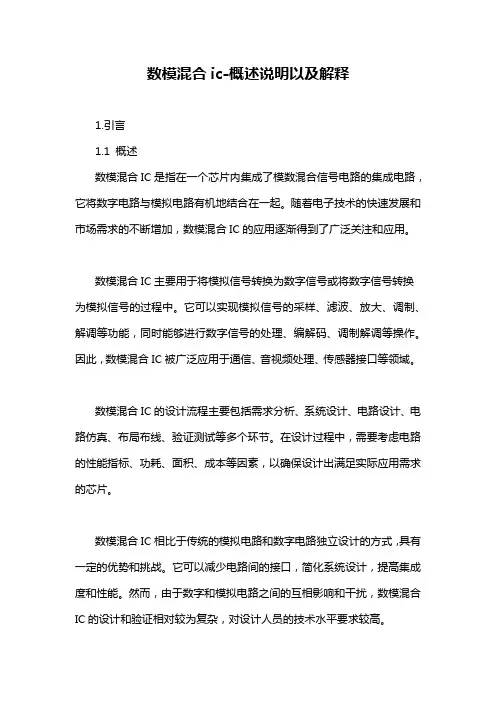

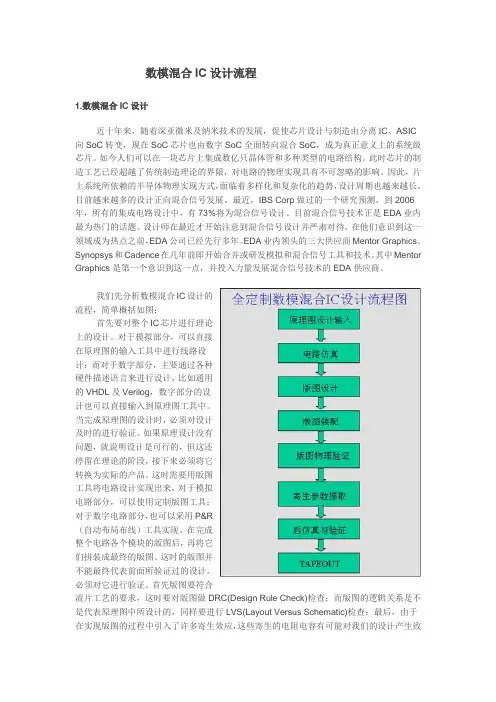

用SpectreVerilog进行模数混仿,以Sigma-Delta ADC为例loghereloghere@SpectreVerilog模数混仿, 模拟部分用Spectre, 数字部分用Verilog-XL. 所以还需要安装Cadence LDV软件, 其内含Verilog-XL仿真器.这里以自行设计的二阶全差分Sigma-Delta ADC为例, 详细介绍用SpectreVerilog的仿真过程. 所用工艺库为TSMC 0.18u,电源电压:1.8V.1. 准备Sigma-Delta ADC分模拟和数字部分两块, 其中模拟部分为调制器, 数字部分为数字滤波器. 如下图. 其中out为调制器的输出, 这里是1位0,1数据流. 数字滤波器为Verilog RTL级代码.Schematic:Symbol:Verilog Code:module DigitalFilter (in2out, out, clk, clr, in);output in2out;output [`wordsize-1:0] out;input clk;input clr;input in;reg in2out;wire clk_half1, clk_half2;……Endmodule同时为了直观的观看输出结果,因此把输出的数字字转化为模拟量,这里用Verilog-A做一个理想的DA转换器。

因此最好事先用Spectre仿真模拟部分, 用ModelSim或Verilog-XL等仿真数字部分. 这里假定我们已有:1) 模拟部分的原理图(包括Symbol);2) 数字部分的Verilog代码,DigitalFilter.v, 模块名:DigitalFilter(in2out,out,clk,clr,in);3) 数字部分的TestBench代码, DigitalFilter_TB.v, 模块名: DigitalFilter_TB.下图为最终的系统图:2. 创建数字模块的Symbol1) 新建一个Cell, View Name为symbol, Tool: Composer-Symbol.2) 画Symbol. 简单地, 画一个矩形框, 添加几个Lable, 然后添加Pin.3) 添加Pin. 左边输入, 右边输出. 对于多位的pin可以用如out<7:0>的样式作为pin的名字. 注意: 与模拟部分相连的多位Pin最好不要用一个pin, 而要用多个. 如下图.4) 创建对应的Verilog文件. 在symbol编辑器中, Design菜单->CreatCellView->From CellView.会弹出的对话框, Tool/Data Type一栏选择Verilog-Editor, 则To View Name会变为functional.点击OK, 会弹出错误对话框, 点No. 自动弹出VI编辑器, 可以看到已经生成Verilog代码的空壳.代码文件的路径在VI编辑器的标题栏上. 下面要做的就是把我们的数字模块(不是TestBench)的代码填进去. 如果不想用VI编辑器, 也可以用其他文本编辑器. 复制代码时最好不要动自动生成的代码. 经测试, 所有代码最好放在一个文件中.这一步之后,数字部分就会有functional和symbol两个View。

数模混合IC设计流程1.数模混合IC设计近十年来,随着深亚微米及纳米技术的发展,促使芯片设计与制造由分离IC、ASIC 向SoC转变,现在SoC芯片也由数字SoC全面转向混合SoC,成为真正意义上的系统级芯片。

如今人们可以在一块芯片上集成数亿只晶体管和多种类型的电路结构。

此时芯片的制造工艺已经超越了传统制造理论的界限,对电路的物理实现具有不可忽略的影响。

因此,片上系统所依赖的半导体物理实现方式,面临着多样化和复杂化的趋势,设计周期也越来越长。

目前越来越多的设计正向混合信号发展。

最近,IBS Corp做过的一个研究预测,到2006年,所有的集成电路设计中,有73%将为混合信号设计。

目前混合信号技术正是EDA业内最为热门的话题。

设计师在最近才开始注意到混合信号设计并严肃对待,在他们意识到这一领域成为热点之前,EDA公司已经先行多年。

EDA业内领头的三大供应商Mentor Graphics、Synopsys和Cadence在几年前即开始合并或研发模拟和混合信号工具和技术。

其中Mentor Graphics是第一个意识到这一点,并投入力量发展混合信号技术的EDA供应商。

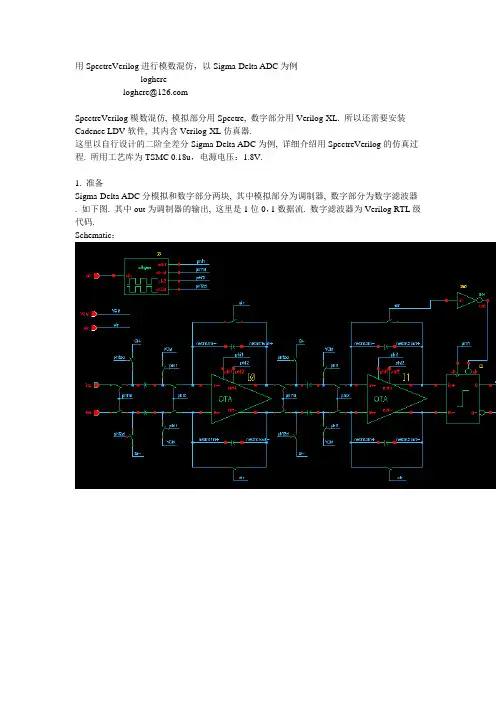

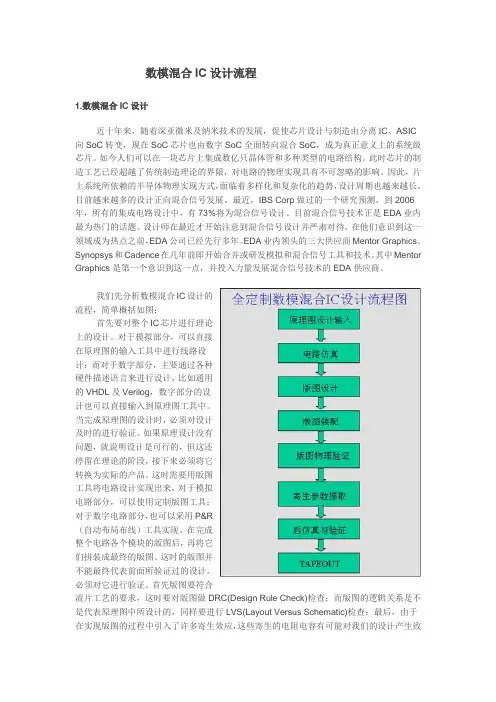

我们先分析数模混合IC设计的流程,简单概括如图:首先要对整个IC芯片进行理论上的设计。

对于模拟部分,可以直接在原理图的输入工具中进行线路设计;而对于数字部分,主要通过各种硬件描述语言来进行设计,比如通用的VHDL及Verilog,数字部分的设计也可以直接输入到原理图工具中。

当完成原理图的设计时,必须对设计及时的进行验证。

如果原理设计没有问题,就说明设计是可行的,但这还停留在理论的阶段,接下来必须将它转换为实际的产品。

这时需要用版图工具将电路设计实现出来,对于模拟电路部分,可以使用定制版图工具;对于数字电路部分,也可以采用P&R(自动布局布线)工具实现。

在完成整个电路各个模块的版图后,再将它们拼装成最终的版图。

这时的版图并不能最终代表前面所验证过的设计,必须对它进行验证。

数模混合IC设计流程1.数模混合IC设计近十年来,随着深亚微米及纳米技术的发展,促使芯片设计与制造由分离IC、ASIC 向SoC转变,现在SoC芯片也由数字SoC全面转向混合SoC,成为真正意义上的系统级芯片。

如今人们可以在一块芯片上集成数亿只晶体管和多种类型的电路结构。

此时芯片的制造工艺已经超越了传统制造理论的界限,对电路的物理实现具有不可忽略的影响。

因此,片上系统所依赖的半导体物理实现方式,面临着多样化和复杂化的趋势,设计周期也越来越长。

目前越来越多的设计正向混合信号发展。

最近,IBS Corp做过的一个研究预测,到2006年,所有的集成电路设计中,有73%将为混合信号设计。

目前混合信号技术正是EDA业内最为热门的话题。

设计师在最近才开始注意到混合信号设计并严肃对待,在他们意识到这一领域成为热点之前,EDA公司已经先行多年。

EDA业内领头的三大供应商Mentor Graphics、Synopsys和Cadence在几年前即开始合并或研发模拟和混合信号工具和技术。

其中Mentor Graphics是第一个意识到这一点,并投入力量发展混合信号技术的EDA供应商。

我们先分析数模混合IC设计的流程,简单概括如图:首先要对整个IC芯片进行理论上的设计。

对于模拟部分,可以直接在原理图的输入工具中进行线路设计;而对于数字部分,主要通过各种硬件描述语言来进行设计,比如通用的VHDL及Verilog,数字部分的设计也可以直接输入到原理图工具中。

当完成原理图的设计时,必须对设计及时的进行验证。

如果原理设计没有问题,就说明设计是可行的,但这还停留在理论的阶段,接下来必须将它转换为实际的产品。

这时需要用版图工具将电路设计实现出来,对于模拟电路部分,可以使用定制版图工具;对于数字电路部分,也可以采用P&R(自动布局布线)工具实现。

在完成整个电路各个模块的版图后,再将它们拼装成最终的版图。

这时的版图并不能最终代表前面所验证过的设计,必须对它进行验证。

以DAC为例介绍SpectreVerilog数模混合电路仿真方法来源:EETOP BBS 作者:真我个性(eetop id名)1.先谈下cadence IUS 和cadence ic,nc-verilog,spectre的关系cadence ic用于模拟仿真的软件,cadence IUS用于数字仿真的软件。

如果只做模拟,那用ic就够了。

同理,如果只做数字,那用IUS 也就够了。

但如果做数模混合,既有数字又有模拟,那两个软件都需要安装。

cadence ic cadence IUS如同spectre是cadence ic的模拟仿真器,nc-verilog是IUS的数字仿真器。

因此,如同装上cadence ic就能用spectre一样,装上cadence IUS就能用nc-verilog。

2. 数模混合电路中数字和模拟的实现数模混合电路中的模拟部分包括运放,开关电容等,数字部分包括开关电容中的控制信号等。

本文模拟部分就是DAC,但是例程中的DAC并不是用实际的电路实现的,而是采用verilog A代码来描述其行为模型的。

代码如下:数字部分就是给DAC提供一些列的数字输入信号,采用的是数字语言verilog实现的,代码如下:所有代码,其中DAC8bit_spectreverilog.tar.gz是cadencelibrary,解压后可直接在cadence中仿真运行。

DAC8bit_spectreverilog.zip (24.61 KB) (本文最后的压缩包中也有该文件)数模混合电路仿真时数字电路采用nc-verilog仿真器,模拟电路用spectre仿真器,最后把结果合在一起。

具体的设置步骤参考下文:VerilogA_Creating & simulating an 8-bit D-A Converter (DAC)_spectreverilog.pdf (605.61 KB) (本文最后的压缩包中也有该文件)总电路仿真结果3. 参考资料“数模混合电路设计流程_中科大”:介绍很完整,很严谨。

数模混合仿真设计流程详解

数模很合仿真可以提高cadence仿真的速度,使用spectreverilog进行仿真。

首先需要安装IUS9.2数字电路的仿真器,verilogXL。

否则不会启动的!!!!!我一开始用的是ic514后来发现我没有安装IUS,同时虚拟机没有空间了,于是我就把IUS装到了ic615上,所以前面的界面是514后边会有615的界面,大同小异。

按照步骤来,我相信大家都会学会的。

1.建立一个设计库:

2.建立一个数字单元functional cell,输入verilog代码

输入代码完成后创建符号图

3.创建模拟电路

5.建立config文件

6.建立spectreverilog模板

进入mix模式,打开simu的config文件后再进入mix模式

ic6151

仿真器改成spectreVerilog

设置数字电路和模拟电路的仿真激励

编辑测试激励语句

设置仿真时长与步长

仿真结果如下

需要注意的是数字和模拟电路的接口电平设置,何为1何为0。

需要在下图所示中设置

输入输出都需要设置,高电平何为1低电平何为0。

一般情况下是默认值,如果默认值不太合适的话,会导致逻辑错误。

所以需要手工设置一下。

这个地方我还没有研究明白,应该会

选择 一下针对CELL或者lib或者pin。

IC设计软件有哪些IC设计软件有哪些IC设计工具很多,其中按市场所占份额排行为Cadence、Mentor Graphics和Synopsys。

店铺下面为你整理了一些IC设计软件,希望对你有所帮助。

(1)设计输入工具:像Cadence的composer,viewlogic的viewdraw,硬件描述语言VHDL、Verilog HDL是主要设计语言,许多设计输入工具都支持HDL。

另外像Active—HDL和其它的设计输入方法,包括原理和状态机输入方法,设计FPGA/CPLD的工具大都可作为IC设计的输入手段,如Xilinx、Altera等公司提供的开发工具,Modelsim FPGA等。

(2)设计仿真工作:EDA工具的一个最大好处是可以验证设计是否正确,几乎每个公司的EDA 产品都有仿真工具。

Verilog—XL、NC—verilog用于Verilog仿真,Leapfrog 用于VHDL仿真,Analog Artist用于模拟电路仿真。

Viewlogic的仿真器有:viewsim门级电路仿真器,speedwaveVHDL仿真器,VCS— verilog仿真器。

Mentor Graphics 有其子公司Model Tech 出品的VHDL和Verilog双仿真器:Model Sim。

Cadence、Synopsys用的是VSS(VHDL仿真器)。

现在的趋势是各大EDA公司都逐渐用HDL仿真器作为电路验证的工具。

(3)综合工具综合工具可以把HDL变成门级网表。

这方面Synopsys工具占有较大的优势,它的Design Compile是作综合的工业标准,它还有另外一个产品叫Behavior Compiler,可以提供更高级的综合。

另外最近美国又出了一家软件叫Ambit,说是比Synopsys的软件更有效,可以综合50万门的电路,速度更快。

今年初Ambit被Cadence公司收购,为此Cadence放弃了它原来的综合软件Synergy。

数/模混合仿真基本步骤1、输入命令“ which verilog.vmx” ,参看仿真所需的“ verilog.vmx ”文件是否存在, “ which icfb” ,查看所需的系统文件是否存在;2、在需要进行仿真的文件目录下启动 icfb ,将系统中模拟电路部分电路结构做成 symbol , 数字电路部分用 verilog 编写,做成 view 名称为“ functional ”的模块;3、除了有 schematic view之外,增加 config view :library manager → file → new → cell view →如图填写后,点击 ok弹出对话框点击 use template ,弹出对话框在 name 选项中选择 spectreVerilog ,点击 ok ,关闭 new configuration 对话框,在new configuration 对话框中,将 view 名称改为 schematic ,如图保存后关闭对话框;4、开始仿真时关闭双击 config ,弹出对话框一般按照默认值,只显示 schematic ,不显示 config ,点击ok5、在弹出的 schematic 对话框中, tool → analog environment→ set up→simulator/directory/host,弹出对话框将 simulator 改为如图, ok ; schematic 中将出现 mixed signal选项,点击该选项,下拉菜单中出现三个选项, 其中 display partition选项中可选择显示模拟信号线, 数字信号线、或混合信号线;interface elements选项中的 library 选项,应根据工艺条件与设计要求填写相关的A → D 、D → A 相关信息,如信号上升、下降时间,模拟信号向数字信号转换的高低电平等;6、填写完毕后关闭该对话框,在 design environment对话框中, set up → model library中填写工艺模型文件(与模拟电路仿真相同 ,开始进行仿真(后与模拟电路仿真相同。

verilog仿真流程一、环境搭建在进行Verilog仿真前,首先需要搭建仿真环境。

常用的Verilog仿真工具有ModelSim、VCS等。

这里以ModelSim为例来介绍环境搭建步骤。

1. 下载ModelSim软件并安装到电脑中,根据软件的安装向导逐步操作即可。

2. 创建一个新的工程,选择File -> New -> Project来创建一个新的工程。

3. 在工程中添加需要仿真的Verilog文件,选择File -> Add to Project -> Existing File来添加Verilog文件。

4. 配置仿真波形,选择Simulate -> Start Simulation来开始仿真。

二、编写Verilog代码在搭建好仿真环境后,接下来就是编写Verilog代码。

Verilog是一种硬件描述语言,通常用来描述数字电路的行为。

Verilog代码由模块、端口和信号等组成,下面是一个简单的Verilog模块示例:```verilogmodule adder(input [7:0] a,input [7:0] b,output [8:0] sum);assign sum = a + b;endmodule```在这个示例中,我们定义了一个名为adder的模块,它有两个8位输入端口a和b,以及一个9位输出端口sum。

在模块体中,我们使用assign语句来实现a和b的加法运算,并将结果赋给sum。

三、编译Verilog代码在编写好Verilog代码后,需要对代码进行编译。

编译的目的是将Verilog代码转换成仿真可执行的二进制文件。

在ModelSim中,可以通过点击Compile按钮或者在命令行中输入vlog命令来进行编译。

```verilogvlog adder.v```这样就会生成一个adder.v文件,里面包含了编译后的二进制代码。

四、仿真测试在编译成功后,接下来就是对设计的Verilog模块进行仿真测试。

数模混合仿真基本流程数模混合仿真(Mixed-Signal Simulation)是一种结合了模拟和数字仿真的方法,用于对整个电子系统进行系统级和电路级的验证。

它可以模拟数字信号和模拟信号之间的相互作用,包括时钟、数据传输、电源和噪声等因素。

下面我将介绍数模混合仿真的基本流程,并详细解释每个步骤。

1.确定系统规格和需求:首先需要明确系统的功能和性能要求。

这包括确定系统的输入和输出,以及技术指标如速度、功耗和面积等。

这些信息对于后续的设计和验证非常重要。

2. 设计系统仿真模型:在进行实际电路设计之前,需要建立系统的仿真模型。

这包括创建系统级模型(如Verilog或VHDL)和模拟模型(如SPICE)等。

系统级模型用于模拟数字部分,而模拟模型用于模拟模拟部分。

3. 实现数字电路设计:根据系统规格和需求,开始进行数字电路设计。

这通常涉及使用FPGA工具、电路设计工具和IP(Intellectual Property)库等。

设计完成后,将数字部分的设计与系统级模型连接起来。

4.验证数字电路设计:进行数字电路设计的验证,以确保其符合系统规格和功能要求。

验证方法可以包括模拟仿真、时序仿真和功能仿真等。

5.实现模拟电路设计:开始进行模拟电路设计。

这包括选择和设计模拟电路的各个组成部分,如放大器、滤波器、模数转换器(ADC)和数模转换器(DAC)等。

设计完成后,将模拟部分的设计与模拟模型连接起来。

6.验证模拟电路设计:进行模拟电路设计的验证,以确保其符合系统规格和功能要求。

验证方法包括使用SPICE仿真,通过模拟信号作用于模拟模型来验证设计中的模拟电路。

7.库模型与接口验证:对所用到的模块和库进行验证,包括芯片设计中采用的各种标准元件和功能模块。

这些库模型可以是已经经过验证的标准模型,也可以是自定义模型。

同时,库模型的接口也需要进行验证,以确保其与被集成的其他模块或芯片的相互连接正确。

8.进行系统级仿真:将数字部分和模拟部分的设计相互连接,进行系统级仿真。

Cadence 的数模混合仿真工具spectraverilog能够实现数字模拟电路联仿的功能,对于模拟电路的输入信号可以利用数字接口很方便的进行设置。

主要用来进行功能仿真。

步骤:

1.准备schematic,如电路单元mix

2.从库管理器中建立mix单元的config view.

在use template中选择spectraverilog,然后ok

将top cell中的myview改为实际的schemtic,然后ok

正确的结果如下图

保存,点击open打开config后的schematic,在tools中选择mix signal opts.

在mix-signal菜单中,尝试第二项的每一个小项,可以看到模拟和数字的相关划分。

由于数字部分默认的电压为5V,转换电平为1.5V和3.5V,因此,如果电路的电源电压不同的与5V,需要对于数模混合接口部分进行设置,在mix-signal菜单中的第三项中进行设置。

对于模拟部分来讲,其按照模型进行计算,无需在数模接口部分进行端口设置,对于数字接口来讲,需要将默认的5V电平以及1.5V,3.5V转换电平变为与模拟部分相符的电压

值,比如电源3V,转换电平为1.5V和3.5V。

设置如下,

对于与模拟器件相连接的数字输出端,将高电平由5V改为3V

对于与模拟器件相连接的数字输入端,将转换电平由1.5V改为3.5V改为1V和2V

所有数模混合接口的相关的数字端口都需要改动,如下图所示的数模接口部分

3.调出analog仿真工具,并设置为spectreverilog

4.编写端口的输入激励文件

设置传输分析的时间长度

5.其余步骤同模拟信号仿真一样,run。