科星F107开发板—底板原理图

- 格式:pdf

- 大小:118.98 KB

- 文档页数:1

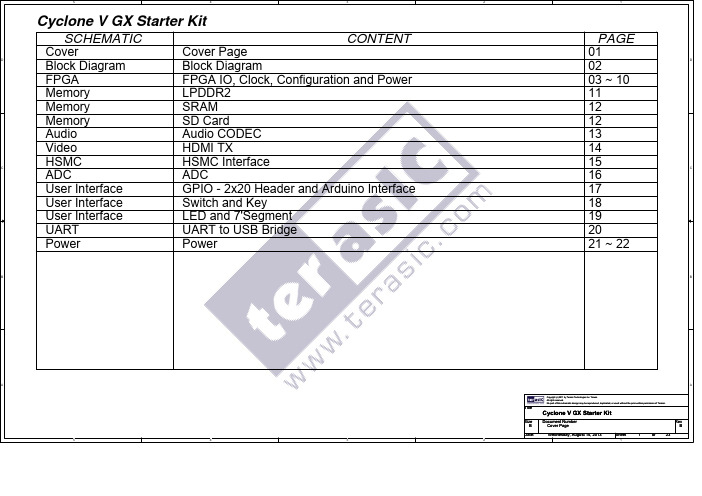

SRAMSD CardAudio CODECHDMI TXHSMC InterfaceADCGPIO - 2x20 Header and Arduino InterfaceSwitch and KeyLED and 7'SegmentUART to USB BridgePowerCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.All rights reserved.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.Title5432TitleSize Document Number Date:Copyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.Block DiagramCyclone V GX Starter KitB Friday, November 15, 2013SWITCH7-SEGMENTADC InterfaceDDR2LP_DQ7DDR2LP_DM0DDR2LP_DQ4DDR2LP_DQ5DDR2LP_DQ14DDR2LP_DQ15DDR2LP_CKE0DDR2LP_DM1DDR2LP_DQ12DDR2LP_DQ13DDR2LP_DQ11DDR2LP_CKE1DDR2LP_DQS_n1DDR2LP_DQS_p1DDR2LP_DQ8DDR2LP_DQ9GNDDDR2LP_DQ10DDR2LP_CA0DDR2LP_CA1SW[9..0]HEX0_D[6..0]HEX1_D[6..0]ADC_CONVST ADC_SCK ADC_SDO ADC_SDITitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.IO_4A/DIFFIO_RX_B30N/DQ4B/B_DQ_4Y13IO_4A/DIFFIO_RX_B30P/DQ4B/B_DQ_5W12IO_4A/DIFFIO_TX_B32N/DQ4B/B_DQ_7AF12IO_4A/DIFFIO_TX_B32P/DQ4B/B_DM_0AF11IO_4A/DIFFIO_TX_B33N/GND AC13IO_4A/DIFFIO_RX_B34N/DQ5B/B_DQ_8AC15IO_4A/DIFFIO_TX_B33P/DQ5B/B_DQ_10AC14IO_4A/DIFFIO_RX_B34P/DQ5B/B_DQ_9AB15IO_4A/DIFFIO_RX_B35N/DQSN5B/B_DQSN_1V14IO_4A/DIFFIO_TX_B36N/DQ5B/B_DQ_11AF13IO_4A/DIFFIO_RX_B35P/DQS5B/B_DQS_1U14IO_4A/DIFFIO_TX_B36P/B_CKE_1AE13IO_4A/DIFFIO_TX_B37N/DQ5B/B_CKE_0AF14IO_4A/DIFFIO_RX_B38N/DQ5B/B_DQ_12AB16IO_4A/DIFFIO_TX_B37P/DQ5B/B_DQ_14AE14IO_4A/DIFFIO_RX_B38P/DQ5B/B_DQ_13AA16IO_4A/DIFFIO_TX_B40N/DQ5B/B_DQ_15AF18IO_4A/DIFFIO_TX_B40P/DQ5B/B_DM_1AE18IO_4A/DIFFIO_RX_B46N/DQ6B/B_DQ_20IO_4A/DIFFIO_RX_B46P/DQ6B/B_DQ_21IO_4A/DIFFIO_TX_B48N/DQ6B/B_DQ_23IO_4A/DIFFIO_TX_B48P/DQ6B/B_DM_2IO_4A/DIFFIO_RX_B50N/DQ7B/B_DQ_24IO_4A/DIFFIO_TX_B49P/DQ7B/B_DQ_26IO_4A/DIFFIO_RX_B50P/DQ7B/B_DQ_25IO_4A/DIFFIO_RX_B51N/DQSN7B/B_DQSN_3IO_4A/DIFFIO_TX_B52N/DQ7B/B_DQ_27IO_4A/DIFFIO_RX_B51P/DQS7B/B_DQS_3IO_4A/DIFFIO_RX_B54N/DQ7B/B_DQ_28IO_4A/DIFFIO_TX_B53P/DQ7B/B_DQ_30IO_4A/DIFFIO_RX_B54P/DQ7B/B_DQ_29IO_4A/DIFFIO_TX_B56N/DQ7B/B_DQ_31IO_4A/DIFFIO_TX_B56P/DQ7B/B_DM_3IO_4A/DIFFIO_RX_B58N/DQ8B/B_DQ_32IO_4A/DIFFIO_TX_B57P/DQ8B/B_DQ_34IO_4A/DIFFIO_RX_B58P/DQ8B/B_DQ_33IO_4A/DIFFIO_RX_B59N/DQSN8B/B_DQSN_4IO_4A/DIFFIO_TX_B60N/DQ8B/B_DQ_35IO_4A/DIFFIO_RX_B59P/DQS8B/B_DQS_4IO_4A/DIFFIO_RX_B62N/DQ8B/B_DQ_36IO_4A/DIFFIO_TX_B61P/DQ8B/B_DQ_38IO_4A/DIFFIO_RX_B62P/DQ8B/B_DQ_37IO_4A/DIFFIO_TX_B64N/DQ8B/B_DQ_39IO_4A/DIFFIO_TX_B64P/DQ8B/B_DM_4IO_3B/DIFFIO_TX_B24N/DQ3B/B_CA_1AF6IO_3B/DIFFIO_TX_B24P/DQ3B/B_CA_0AE6SRAM_D0SRAM_D1SRAM_D2SRAM_D3SRAM_D4SRAM_D5SRAM_D6SRAM_D7SRAM_D8SRAM_D9SRAM_D10SRAM_D11SRAM_D12SRAM_D13SRAM_D14SRAM_D15HDMI_TX_VS HDMI_TX_HSHDMI_TX_D19HDMI_TX_D1HDMI_TX_D2HDMI_TX_D3HDMI_TX_D5HDMI_TX_D6HDMI_TX_D9HDMI_TX_D11HDMI_TX_D18HDMI_TX_D17HDMI_TX_D16HDMI_TX_D15HDMI_TX_D12HDMI_TX_D14TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.5CGXFC5C6F27C7NIO_6A/DIFFIO_TX_R34P/DQ5R E24IO_6A/DIFFIO_TX_R34N/DQ5R E25IO_6A/DIFFIO_RX_R35P/DQ5R K24IO_6A/DIFFIO_TX_R36P/DQ5R F24IO_6A/DIFFIO_RX_R35N/DQ5R K23IO_6A/DIFFIO_TX_R36N/DQ5R G24IO_6A/DIFFIO_RX_R37P/DQS5R L23IO_6A/DIFFIO_TX_R38PH23IO_6A/DIFFIO_RX_R37N/DQSN5R L24IO_6A/DIFFIO_TX_R38N/DQ5R H24IO_6A/DIFFIO_RX_R39P/DQ5R H22IO_6A/DIFFIO_TX_R40P/DQ5R F23IO_6A/DIFFIO_RX_R39N/DQ5R J23IO_6A/DIFFIO_TX_R40N G22IO_6A/DIFFIO_RX_R41P L22IO_6A/DIFFIO_RX_R41NK21IO_5B/DIFFIO_RX_R15P/DQ2R R24IO_5B/DIFFIO_TX_R16P/DQ2RU24IO_5B/DIFFIO_RX_R15N/DQ2R R25IO_5B/DIFFIO_TX_R16NV25IO_5B/DIFFIO_TX_R18P/DQ3R AB26IO_5B/DIFFIO_TX_R18N/DQ3R AA26IO_5B/DIFFIO_RX_R19P/DQ3R T26IO_5B/DIFFIO_RX_R19N/DQ3RR26IO_5B/DIFFIO_RX_R21P/DQS3R P21IO_5B/DIFFIO_TX_R22PW25IO_5B/DIFFIO_RX_R21N/DQSN3RP22IO_5B/DIFFIO_TX_R22N/DQ3R W26IO_5B/DIFFIO_RX_R23P/DQ3R N25IO_5B/DIFFIO_TX_R24P/DQ3RU25IO_5B/DIFFIO_RX_R23N/DQ3R P26IO_5B/DIFFIO_TX_R24NU26Audio CODECHSMC_D0HSMC_RX_n0HSMC_RX_p0HSMC_RX_n10HSMC_RX_p10HSMC_RX_p9HSMC_RX_n9HSMC_RX_p11HSMC_RX_n11HSMC_RX_n12HSMC_RX_p12HSMC_RX_p1HSMC_RX_n1HSMC_RX_n7HSMC_RX_p7HSMC_TX_n8HSMC_TX_p8HSMC_TX_p9HSMC_TX_n9HSMC_TX_p10HSMC_TX_n10HSMC_TX_p0HSMC_TX_n0HSMC_TX_p2HSMC_TX_n2HSMC_TX_n1HSMC_TX_p1HSMC_TX_n4HSMC_TX_p4HSMC_TX_n3HSMC_TX_p3HSMC_TX_n6HSMC_TX_p6AUD_XCK 13AUD_DACDAT 13AUD_ADCDAT 13AUD_DACLRCK 13AUD_ADCLRCK13AUD_BCLK 13TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.5CGXFC5C6F27C7NIO_7A/DIFFIO_TX_T6N/DQ1T/T_DQ_35IO_7A/DIFFIO_RX_T7P/DQ1T/T_DQ_33IO_7A/DIFFIO_TX_T8P/DQ1T/T_DQ_34IO_7A/DIFFIO_RX_T7N/DQ1T/T_DQ_32IO_7A/DIFFIO_TX_T10P/DQ2T/T_DM_3IO_7A/DIFFIO_TX_T10N/DQ2T/T_DQ_31IO_7A/DIFFIO_RX_T11P/DQ2T/T_DQ_29IO_7A/DIFFIO_TX_T12P/DQ2T/T_DQ_30IO_7A/DIFFIO_RX_T11N/DQ2T/T_DQ_28IO_7A/DIFFIO_RX_T13P/DQS2T/T_DQS_3IO_7A/DIFFIO_RX_T13N/DQSN2T/T_DQSN_3IO_7A/DIFFIO_TX_T14N/DQ2T/T_DQ_27IO_7A/DIFFIO_RX_T15P/DQ2T/T_DQ_25IO_7A/DIFFIO_TX_T16P/DQ2T/T_DQ_26IO_7A/DIFFIO_RX_T15N/DQ2T/T_DQ_24IO_7A/DIFFIO_TX_T22P/T_RESETN B15IO_7A/DIFFIO_TX_T22N/DQ3T/T_DQ_19C15IO_7A/DIFFIO_RX_T23P/DQ3T/T_DQ_17C14IO_7A/DIFFIO_TX_T24P/DQ3T/T_DQ_18A8IO_7A/DIFFIO_RX_T23N/DQ3T/T_DQ_16D15IO_7A/DIFFIO_TX_T24N/GNDA9IO_7A/DIFFIO_TX_T26P/DQ4T/T_DM_1C9IO_7A/DIFFIO_TX_T26N/DQ4T/T_DQ_15B9IO_7A/DIFFIO_RX_T27P/DQ4T/T_DQ_13E16IO_7A/DIFFIO_TX_T28P/DQ4T/T_DQ_14D10IO_7A/DIFFIO_RX_T27N/DQ4T/T_DQ_12D16IO_7A/DIFFIO_TX_T28N/DQ4T/T_CKE_0C10IO_7A/DIFFIO_RX_T29P/DQS4T/T_DQS_1N12IO_7A/DIFFIO_TX_T30P/T_CKE_1B10IO_7A/DIFFIO_RX_T29N/DQSN4T/T_DQSN_1M12IO_7A/DIFFIO_TX_T30N/DQ4T/T_DQ_11A11IO_7A/DIFFIO_RX_T31P/DQ4T/T_DQ_9F16IO_7A/DIFFIO_TX_T32P/DQ4T/T_DQ_10E10IO_7A/DIFFIO_RX_T31N/DQ4T/T_DQ_8E15IO_7A/DIFFIO_TX_T32N/GNDE11IO_7A/DIFFIO_TX_T34P/DQ5T/T_DM_0B12IO_7A/DIFFIO_TX_T34N/DQ5T/T_DQ_7A13IO_7A/DIFFIO_RX_T35P/DQ5T/T_DQ_5G12IO_7A/DIFFIO_TX_T36P/DQ5T/T_DQ_6A12IO_7A/DIFFIO_RX_T35N/DQ5T/T_DQ_4F12IO_7A/DIFFIO_TX_T36N/DQ5T/T_ODT_1B11IO_7A/DIFFIO_RX_T37P/DQS5T/T_DQS_0M11IO_7A/DIFFIO_TX_T38P/T_ODT_0C13IO_7A/DIFFIO_RX_T37N/DQSN5T/T_DQSN_0L11IO_7A/DIFFIO_TX_T38N/DQ5T/T_DQ_3C12IO_7A/DIFFIO_RX_T39P/DQ5T/T_DQ_1E13IO_7A/DIFFIO_TX_T40P/DQ5T/T_DQ_2D11IO_7A/DIFFIO_RX_T39N/DQ5T/T_DQ_0D13GXB L2 is C7 FPGA onlyHSMC_GXB_RX_p3HSMC_GXB_RX_n3HSMC_GXB_TX_p3HSMC_GXB_TX_n3SMA_GXB_TX_pSMA_GXB_RX_pREFCLK_p1REFCLK_n1SMA_GXB_RX_p SMA_GXB_RX_nSMA_GXB_TX_p SMA_GXB_TX_n TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.GXB_L1GXB_L25CGXFC5C6F27C7NREFCLK1LNP6REFCLK1LP N7GXB_TX_L5NK1GXB_TX_L5P K2GXB_RX_L5P,GXB_REFCLK_L5P M2GXB_RX_L5N,GXB_REFCLK_L5N M1GXB_TX_L4N P1GXB_TX_L4P P2GXB_RX_L4P,GXB_REFCLK_L4P T2GXB_RX_L4N,GXB_REFCLK_L4N T1GXB_TX_L3N W3GXB_TX_L3P W4GXB_RX_L3P,GXB_REFCLK_L3P V2GXB_RX_L3N,GXB_REFCLK_L3N V1RREF_TLB1GXB_RX_L8n,GXB_REFCLK_L8n D1GXB_RX_L8p,GXB_REFCLK_L8p D2GXB_RX_L7n,GXB_REFCLK_L7n F1GXB_RX_L7p,GXB_REFCLK_L7p F2GXB_RX_L6n,GXB_REFCLK_L6n H1GXB_RX_L6p,GXB_REFCLK_L6p H2GXB_TX_L6p G4GXB_TX_L6n G3GXB_TX_L7p E4GXB_TX_L7n E3GXB_TX_L8p C4GXB_TX_L8nC3REFCLK2Lp M6REFCLK2LnL5R1990R2042KJ12J7R1980C1360.01uVCCIO = 3.3VVCCIO = 3.3VVCCIO = 2.5VVCCIO = 2.5VHSMC_CLKIN_p1HSMC_CLKIN_n1CLOCK_50_B7A HSMC_CLKIN_n1HSMC_CLKIN_n2CLOCK_50_B5B CLOCK_50_B6A GPIO0GPIO2I2C_SDACLOCK_125_n GPIO8GPIO7GPIO6GPIO4CLOCK_50_B8A HSMC_CLKIN0HSMC_CLKIN_p2HSMC_CLKIN_n2VCC2P5VCC2P5VCC2P5VCC3P3VCC2P5TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.C2690.1u 10V C2680.1u 10VC1110.1u 10VR188100R197100R200100R11220KC2670.1u 10V Bank 5BBank 6ABank 7ABank 8A5CGXFC5C6F27C7NIO_5B/CLK7P,FPLL_BR_FBP/DIFFIO_RX_R9P T21IO_5B/CLK7N,FPLL_BR_FBN/DIFFIO_RX_R9NT22IO_5B/CLK6P/DIFFIO_RX_R17P R20IO_5B/CLK6N/DIFFIO_RX_R17NP20IO_5B/FPLL_BR_CLKOUT0,FPLL_BR_CLKOUTP,FPLL_BR_FB/DIFFIO_TX_R20P/DQ3RIO_5B/FPLL_BR_CLKOUT1,FPLL_BR_CLKOUTN/DIFFIO_TX_R20N/DQ3RIO_6A/CLK5P/DIFFIO_RX_R25P N20IO_6A/CLK5N/DIFFIO_RX_R25NM21IO_6A/FPLL_TR_CLKOUT0,FPLL_TR_CLKOUTP,FPLL_TR_FB/DIFFIO_TX_R28P/DQ4RIO_6A/FPLL_TR_CLKOUT1,FPLL_TR_CLKOUTN/DIFFIO_TX_R28N/DQ4RIO_6A/CLK4P,FPLL_TR_FBP/DIFFIO_RX_R33P K25IO_6A/CLK4N,FPLL_TR_FBN/DIFFIO_RX_R33NK26IO_7A/CLK11P/DIFFIO_RX_T25P G15IO_7A/CLK11N/DIFFIO_RX_T25NG14IO_7A/CLK10P/DIFFIO_RX_T33P H12IO_7A/CLK10N/DIFFIO_RX_T33N G11IO_8A/CLK9P/DIFFIO_RX_T41P N9IO_8A/CLK9N/DIFFIO_RX_T41NM10IO_8A/FPLL_TL_CLKOUT0,FPLL_TL_CLKOUTP,FPLL_TL_FB/DIFFIO_TX_T44P/DQ6T/T_CA_2IO_8A/FPLL_TL_CLKOUT1,FPLL_TL_CLKOUTN/DIFFIO_TX_T44N/DQ6T/T_CA_3IO_8A/CLK8P,FPLL_TL_FBP/DIFFIO_RX_T49P L8IO_8A/CLK8N,FPLL_TL_FBN/DIFFIO_RX_T49N K9U20MSEL Settings : MSEL[4:0] = 10010 Active serial (AS)(x1 and x4),no compression, no security, fast PORFPGAHSMCSD_DAT0SD_DAT1SD_DAT2SD_DAT3SD_CMD SD_CLK MSEL0MSEL1MSEL3MSEL2MSEL4BST_TDI BST_TDO JTAG_FPGA_TDI FPGA_CONF_DONE FPGA_nSTATUS FPGA_nCONFIGHSMC_JTAG_TDI HSMC_JTAG_TDO JTAG_FPGA_TDO FPGA_nCEGPIO34GPIO11GPIO23GPIO22GPIO21GPIO20GPIO19GPIO17GPIO15GPIO14GPIO13GPIO12GPIO31VCC3P3VCC3P3TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.R1730DNI R520R1770DNI RN2210K12345678Bank 9A5CGXFC5C6F27C7NIO_3A/DATA6/DIFFIO_RX_B1N/DQ1B T7IO_3A/DATA5/DIFFIO_TX_B2NU7IO_3A/DATA8/DIFFIO_RX_B1P/DQ1B T8IO_3A/DATA7/DIFFIO_TX_B2P/DQ1B V8IO_3A/DATA10/DIFFIO_RX_B3N/DQSN1B W8IO_3A/DATA9/DIFFIO_TX_B4N/DQ1BAB6IO_3A/DATA12/DIFFIO_RX_B3P/DQS1B Y9IO_3A/DATA11/DIFFIO_TX_B4PAA6IO_3A/DATA14/DIFFIO_RX_B5N/DQ1B R10IO_3A/DATA13/DIFFIO_TX_B6N/DQ1B AA7IO_3A/CLKUSR/DIFFIO_RX_B5P/DQ1B R9IO_3A/DATA15/DIFFIO_TX_B6P/DQ1B Y8IO_5A/PR_REQUEST/DIFFIO_TX_R1N/DQ1RAC23IO_5A/CVP_CONFDONE/DIFFIO_TX_R3N/DQ1RAA23IO_5A/nPERSTL1/DIFFIO_RX_R6N/DQSN1R U22MSEL0M7CONF_DONE A6MSEL1L6nSTATUS B5nCED5MSEL2A2MSEL3K5nCONFIG F5MSEL4J5IO_3A/PR_DONE/DIFFIO_RX_B7NR8IO_3A/PR_READY/DIFFIO_TX_B8N/DQ1BAD6IO_3A/PR_ERROR/DIFFIO_RX_B7P P8IO_3A/DIFFIO_TX_B8P/DQ1BAD7R530VCCAUX_VCCA_FPLLVCC2P5VCC3P3VREF_3P3_VCCIOTitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.5CGXFC5C6F27C7NVCC VCC VCC VCC VCC VCCVCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCCPGM AA9VCCPGM W22VCCPGM F8VCCBATVCCPD5B R21VCCPD6A J22VCCPD6A L21VCCPD7A8AF19VCCPD7A8A F17VCCPD7A8A F13VCCPD7A8A F11VCCPD7A8A F9VCCA_FPLL W7VCCA_FPLL J6VCCA_FPLLY21VCCA_FPLL G21VCC_AUX G9VCC_AUX E14VCC_AUX G19VCC_AUXAB20VCC_AUX AB14VCC_AUX AA85CGXFC5C6F27C7NVCCIO4A U18VCCIO4A AE22VCCIO4A AA20VCCIO4A AD19VCCIO4A Y17VCCIO4A W14VCCIO4A AC16VCCIO4A AF15VCCIO4A AB13VCCIO4A AE12VCCIO5A V21VCCIO5A AB23VCCIO5B N26VCCIO5B T25VCCIO5B W24VCCIO5B R22VREFB4AN0AD15VREFB5AN0W23VREFB5BN0P25CYCLONE V GX XCVR PowerU14-122.5V2.5Vfor VCCIO_VCCPD 2.5Vfor VCCIO_VCCPD 3.3Vfor VCCIO 1.2VVCCH_GXBL VCCAUX_VCCA_FPLLVCC1P2VCC3P3VCC2P5TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.C2204.7n 50VC25522n 16VC1674.7u 6.3VC2510.01u 50VC1830.01u 50VC2320.47u 10VC1804.7n 50VC1782.2n 50VC1940.01u 50VC1701u 10VC1720.47u 10VC2504.7n 50VC1764.7u 6.3VC10510u 6.3VC2492.2n 50VC1910.01u 50VC1044.7u 6.3VC1820.1u 10VC2460.01u 50VC1900.1u 10VC25322n 16VC1851u 10VC2590.1u 10VC2130.01u 50VC25247n 25VNote:Place decoupling caps near LPDDR2 power pins place close to DDR2 chipDDR2LP_CKE0DDR2LP_CS_n0DDR2LP_DM0DDR2LP_DM1DDR2LP_DQ2DDR2LP_DQ3DDR2LP_DQ4DDR2LP_DQ5DDR2LP_DQ6DDR2LP_DQ7DDR2LP_DQ8DDR2LP_DQ9DDR2LP_DQ10DDR2LP_DQ11DDR2LP_DQ12DDR2LP_DQ13DDR2LP_DQ14DDR2LP_DQ15DDR2LP_DM3DDR2LP_DQ31DDR2LP_DQ24DDR2LP_DQ25DDR2LP_DQ26DDR2LP_DQ27DDR2LP_DQ28DDR2LP_DQ29DDR2LP_DQ30DDR2LP_DM2DDR2LP_DQ16DDR2LP_DQ17DDR2LP_DQ19DDR2LP_DQ18DDR2LP_DQ20DDR2LP_DQ22DDR2LP_DQ21DDR2LP_DQ23DDR2LP_ZQ0DDR2LP_ZQ1DDR2LP_CKE1DDR2LP_CS_n1DDR2LP_CK_nVCC1P2TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.C1450.1u 10V240DNIC1580.1u 10VR169 4.7K R1684.7K DNIC15510u 10VDNU0A1DNU1A2NC0A3NC1A4NC2A5NC3A6NC4A7NC5A8NC6A9NC7A10DNU2A22DNU3A23DM2AB20DNU10AB22DNU8AB1DNU9AB2CS#0AB3CS#1AB4NC/ZQ AC11CKE0AC3CKE1AC4DNU4B1DNU5B2DM3B20DNU6B22DNU7B23NC8B4NC9B6NC10B7NC11B9NC12D1NC13D2NC14E1NC15E2NC16F1NC17G1NC18G2NC19H1NC20H2NC21J1NC22K1NC23K2NC24L1DM1L23DM0N23ZQ P1DQ30A13DQ29A14DQ26A16DQ25A17DQ16AB12DQ18AB14DQ20AB15DQ22AB17DQ17AC13DQ19AC14DQ21AC16DQ23AC17DQ31B12DQ28B14DQ27B15DQ24B17DQ15C22DQ14D23DQ12E22DQ13E23DQ11F22DQ10G23DQ8H22DQ9H23DQ6T22DQ7T23DQ5U22DQ4V23DQ2W22DQ3W23240C4010u 10VC14622n 16VMT42L128M32D1LF-25WTVSS A21VSS AA1VDD2AA2VDD2AB10VSS AB11VDD2AB21VSS AC21VSS AC5VSS/NC AC9VSS B10VDD2B21VSS/NC B5VSS/NC B8VSS C1VDD2C2VSS/NC F2VSS/NCJ2VDD2L22VSS M2VSS M23VSS R1VDD2R2VSSQ A12VSSQ A15VSSQ A18VDDQ AA22VDDQ AB13VDDQ AB16VDDQ AB19VSSCA AB7VSSQ AC12VSSQ AC15VSSQAC18VSSQ C23VDDQ D22VSSQ F23VDDQ G22VSSQ J23VDDQ K22VSSQ P23VDDQ R22VSSQ U23VSSCA V1VDDQ V22VSSQ Y23C1594.7u 6.3VC16222n 16VC1530.1u 10VSD_DAT1SD_DAT0SD_DAT3SD_DAT2SD_CMDSD_DAT2SD_DAT3SD_CMD SRAM_CE_n SRAM_OE_n SRAM_WE_n SRAM_LB_n SRAM_UB_nSRAM_D11SRAM_D12SRAM_D15SRAM_D13SRAM_D9SRAM_D10SRAM_D14SRAM_CE_nSRAM_A14SRAM_A16SRAM_A15SRAM_A17SRAM_A13VCC3P3_SDVCC3P3_SDTitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.R185RN1010K 12345678L2130ohm, 3ASRAM 256Kx16nCE 6G N D 12nWE 17A1326A1427A1828D930D1031D1132G N D34D1235D1336D1437D1538nLB 39nUB40nOE 41A1542A1643A1744123J6c k e tDAT3CMD DAT2R11710KDefault :I2C Address 0x34/35AUD_XCKAUD_BCLKAUD_DACDAT AUD_DACLRCK AUD_ADCDATAUD_ADCLRCK I2C_SDA_3P3I2C_SCL_3P3AUD_MUTEAUD_CSBAUD_I2C_SDAT AUD_I2C_SCLK AGND AGNDVCC_AUDDVCC_AUDDTitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.R18680R1502K DNIC22100u C13410u 6.3VU7SSM2603BCLK 7H P V D D 12XTO 2D C V D D 3MICBIAS21MICIN22RLINEIN 23LLINEIN24MUTE25CSB26SDIN27SCLK28ROUT 17A V D D18A G N D19VMID 20LOUT16P G N D 15RHPOUT 14LHPOUT13XTI/MCLK 1D G N D4RECLRC11RECDAT 10D B V D D5CLKOUT6PBDAT 8PBLRCK 9E P _G N D 29C1390.1u 10V DNIR2822R20330R3022R1512K DNIR174.7KC151u 10VDefault :I2C Address 0x72/0x73Pull-high to FPGA bank I/O powerNote:Place Capacitor near ADV7513 DVDD pinsHDMI_TX_CLK HDMI_TX_DE HDMI_TX_VS HDMI_TX_HS HDMI_HPD CEC_CLKHDMI_SPDIF HDMI_MCLK HDMI_I2S0HDMI_I2S1HDMI_I2S2HDMI_I2S3HDMI_SCLK HDMI_LRCLKHDMI_TX_D17HDMI_TX_D18HDMI_TX_D19HDMI_TX_D20HDMI_TX_D21HDMI_TX_D22HDMI_TX_D23CLK_12MHz VCC1P8VCC1P8_DVDDVCC1P8VCC1P8_AVDDVCC1P8_DVDDVCC1P8_PVDDVCC1P8_AVDDVCC3P3_DVDD VCC3P3_DVDDVCC1P8_AVDDVCC1P2VCC1P8_DVDDTitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.C3510u 6.3VR15349.9DNI R12822DNIR1242K X312MHZDNIVCC 4OUT 3GND2EN1C1490.1u 10VL910uH74479887310AC1520.1u 10VC1380.1u 10VR129R1252K DNIC1290.1u 10VDNIC1300.1u 10VL410uHR80R138887ADV7513BSWZD1743D1842D1941D2040D2139D2238D2337CLK 53DE63HSYNC 64VSYNC 2R_EXT 14HPD 16SPDIF 3MCLK 4I2S05I2S16I2S27I2S38SCLK 9LRCLK 10PD22DVDD_3V 29DVDD11DVDD211DVDD331DVDD451PVDD 12BGVDD 13AVDD115AVDD219AVDD325EPAD_GND65R130R127TX_n TX_p RX_p RX_nDefaultJumper OpenHSMC_RX_p5HSMC_RX_n5HSMC_TX_p5HSMC_TX_n5HSMC_CLKIN_p1HSMC_CLKIN_n1NET_HSMC_GXB_TX_p0NET_HSMC_GXB_TX_n0HSMC_TX_n0HSMC_CLKOUT_n1HSMC_CLKOUT_p1HSMC_RX_p6HSMC_RX_n6HSMC_TX_n6HSMC_TX_p6HSMC_RX_n1HSMC_RX_p1HSMC_RX_p7HSMC_RX_n7HSMC_TX_p7HSMC_TX_n7HSMC_TX_p1HSMC_TX_n1HSMC_RX_p2HSMC_RX_n2HSMC_CLKOUT0HSMC_JTAG_TCKHSMC_CLKIN0HSMC_JTAG_TDI HSMC_JTAG_TMS HSMC_JTAG_TDO HSMC_D1HSMC_TX_p2HSMC_TX_n2HSMC_GXB_TX_p0HSMC_GXB_TX_n0HSMC_D2HSMC_RX_p3HSMC_RX_n3HSMC_RX_p0HSMC_GXB_RX_n0HSMC_GXB_RX_p0HSMC_RX_n0HSMC_TX_n3HSMC_TX_p3HSMC_D3HSMC_RX_n4HSMC_RX_p4HSMC_TX_p4HSMC_TX_n4HSMC_TX_p0HSMC_D0HSMC_SDAHSMC_SCLI2C_SDA I2C_SCLHSMC_SDA HSMC_SCLVCC12_HSMCVCC12_HSMCVCC3P3_HSMCVCC3P3_HSMCVCC12_HSMCVCC3P3VCC3P3_HSMCTitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.R460C12010u 35V C2650.1u 25VTP1Dummy PinC2660.1u 25V R18722R49JP13HEADER 212C11510u 6.3V C24822u 25V 116416816516616729293131333335353737393930303232343436363838404041414343454547474949515153535555575759596161636365656767696971717373757577777979818183838585878789899191939395959797999942424444464648485050525254545656585860606262646466666868707072727474767678788080828284848686888890909292949496969898100100161161162162163163164164R18622XJ1Jumper-2.54mmVREF ADC_IN1ADC_IN2ADC_IN3ADC_IN5ADC_IN6ADC_IN7ADC_IN0ADC_IN4ex_ADC_SDO ADC_VREFADC_REFCOMP ex_ADC_CONVST ex_ADC_SDIex_ADC_SCK TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.C7810u 10V C800.1u 10VCH0CH1CH2CH3CH4CH5CH6CH7COMG N DG N D G N DG N DG N D G N DVREFREFCOMP SDISCKSDOCONVD V D DO V D DA V D D 1A V D D 1U17LTC2308CUF22232412345625910112018781516171412131921C1021n 50VC981n 50V C8210u 10VC991n 50V C1001n 50V TP13TP_YELLOWC790.1u 10VR8649.9C872.2u 10VC1011n 50V C840.1u 10VGPIO_D0GPIO_D2GPIO_D4GPIO_D6GPIO_D8GPIO_D1GPIO_D3GPIO_D5GPIO_D7GPIO_D9GPIO_D14GPIO_D12GPIO_D10GPIO_D18GPIO_D16GPIO_D22GPIO_D20GPIO_D24GPIO_D15GPIO_D13GPIO_D11GPIO_D19GPIO_D17GPIO_D23GPIO_D21GPIO_D25GPIO_D26GPIO_D28GPIO_D30GPIO_D32GPIO_D34GPIO_D33GPIO_D31GPIO_D29GPIO_D27GPIO_D35GPIO_D7GPIO_D11GPIO_D15GPIO_D19GPIO_D23GPIO_D27GPIO3GPIO20GPIO_D20Arduino_IO0CPU_RESET_n Arduino_Reset_nAnalog_In1Analog_In2Analog_In3Arduino_Reset_nAnalog_In0Arduino_AD4_IO14Arduino_AD5_IO15Analog_In6Analog_In7Arduino_IO11Arduino_IO12Arduino_IO13Arduino_Reset_nArduino_IO15Arduino_IO14GNDVCC5VCC12VCC3P3VCC3P3VCC5TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.BAT54S D15BAT54S123JP14HEADER 2x3123456D38BAT54S123BAT54S D13BAT54S123R22222R2242.2K DNIRN418BAT54S BAT54S RN1118BAT54S D45BAT54S123BAT54S 3BAT54S R2252.2K DNID43BAT54S123JP9BOX Header 2X20M 12345678910111312141618202224262715171921232528293133353739303234363840Reserved 6x6mm tact switchSW1SW0SW2SW3BTN3BTN1BTN2BTN0VCC1P2VCC1P2TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.RN2318BUTTON1TACT SW DNI4321SW0SLIDE SW12345BUTTON3TACT SW DNI4321SW2SLIDE SW12345SW1SLIDE SW12345RN311RN2610K12345678BUTTON2TACT SW DNI4321RN2412012345678B2A2E1G0F0E0B1C1D1F1G1C0B0A0D0A1C2D2E2F2HEX0_D0HEX0_D1HEX0_D2HEX0_D3HEX0_D4HEX0_D5HEX0_D6HEX1_D0HEX1_D1HEX1_D3HEX1_D4HEX1_D2HEX1_D5HEX1_D6HEX2_D0HEX2_D1HEX2_D2HEX2_D3HEX2_D4HEX2_D5GPIO22GPIO23GPIO24GPIO25GPIO26GPIO27GPIO28GPIO30GPIO29HEX2_D0HEX3_D0HEX2_D1HEX3_D1HEX2_D2HEX2_D3HEX2_D4HEX2_D5HEX2_D6LEDR0LEDG1LEDG2LEDG3LEDG4LEDG5LEDG6LEDG7LEDR1LEDR2LEDR3LEDR4LEDR5LEDR6LEDR7VCC_HEX2VCC_HEXVCC_HEXVCC_HEX2VCC_HEXTitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.e d dpc g b f a CA1CA2HEX07Segment Display12345610987ON1S2121615RN1868012345678e d c b f a CA1CA2HEX2124561098RN1668012345678RN1568012345678ON1S1SW DIP-812345678161514131211109RN1912345678e d dpc g b f a CA1CA2HEX17Segment Display12345610987R2010R20510kRN1768012345678Self Powered and Internal OSCUSB to UARTUART_CTSRX_LEDTX_LEDUART_RTSFT232_DP FT232_DM UART_RX UART_TX UART_RESET_nUART_RXLED UART_TXLED UART_CTS UART_RTSUART_CTSUART_RTSUART_PW_ENVCC5_UARTVCC3P3_UARTVCC5_UARTVCC5_USB_UARTVCCIO_UART VCC2P5VCC5TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.DNITP_YELLOWU4FT232R VCC19VCCIO 1G N D 4RESET 183V3OUT16USBDP 14USBDM15TXD 30RXD 2CTS#8RTS#32DSR#6DTR#31DCD#7RI#3CBUS022NC15A G N D 24NC212NC313NC525NC629NC423OSCI 27OSCO 28G N D 17G N D 20TEST26CBUS121CBUS311CBUS210CBUS49E P _G N D33R71M R14310kC140.1u 25VTPD2E001DRLRU2VCC 1NC2IO13GND4IO25D9LEDR21R220DNIC314.7u 6.3VL24321R142 4.7K C60.1u 25VR23R15733C330.1u 25VC80.1u 25V DNITP_YELLOWD8LEDG21R15633C254.7u 6.3VC270.1u 25VL2230ohm, 3A10kC184.7u 6.3VRamp TimeTsoft-start = 0.99 msec3.3V / 5AVCC1P1_PGOOD VCC3P3_PGOOD VCC3P3_INTVCCVCC3P3_INTVCCVCC12VCC1P1_INTVCCVCC3P3_INTVCCTitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.LTC3605EUF#PBFITH 6CLKIN24S G N D22P G N D 110E P _P G N D 225SW616FB4RT 1CLKOUT23R66316K R6910KC623.3n 50VR471050VU11PHMODE 2MODE 3TRACK/SS 5P V I N 117P V I N 218BOOST20PGOOD8SW111SW212SW313SW414SW515SW616RUN 7VON 9SVIN19I N T V C C21C4822u 25V C570.1u 25VD12CMDSH-3C17339p 50V 12.4K DNIC721n 50VR182100K+C656.3V330u 1239p 50V DNIR1940DNIPOWER SWC5022u 25VXJ3Jumper-2.54mmC58 2.2u 6.3VC7168p 50V2.5VTantalum330u 2L121uH 744311100R6715KR18411.5K DNIC510.1u 25VRamp Time = 1.2 msecVCC3P3VCC3P3TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.R109200KC561u 10VC532.2u 10VLT3080-1U10OUT11OUT22OUT33SET 4IN28IN17NC6V_CONTROL 5OUT49DNIC494.7n 50VC521u 10VR44180KC5422u 6.3VC1124.7n 50V6.3VXJ6Jumper-2.54mmGND13URXFOSC_24BST_TMS URD UTXE UWR URXFSI_WU UD7EEPDATA EEPCSEEPCLK USB_RESETnBST_TDI BST_TDO ISP_TCK ISP_TMS ISP_TDI ISP_TDOUSB_RESETn TRGNST TRGNCSO TRGASDO TRGDCLK TRGNCE TRGTDO TRGTMSTRGOE TRGOEFPGA_nCEUART_RESET_nPWRONPWRON BST_TCK VCC5_USBVCC3P3TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.FT245BLLQFP-32TEST31RXF#12EEDATA 2XTIN 27XTOUT 28G N D17D718RD#16WR 15TXE#14A G N D 29EECS 32EESK 1RESET#4SI/WU 11PWREN#10USBDM 8G N D 9R14110KR2070DNIR13310KR1480DNIC14347p 50VBAT54SDW 123R13027EPM240M100C4N IO-B1-10G1IO-B1-11G2IO-B1-12F3IO-B1-13H1IO-B1-14H3IO-B1-15H2IO-B1-16L1IO-B1-17L2IO-B1-18K3IO-B1-19L3IO-B1-20K4IO-B1-21L4IO-B1-22K5IO-B1-23L5IO-B1-24L6IO-B1-25K6IO-B1-26J6IO-B1-27L7IO-B1-28K7IO-B1-29/DEV_OE L8IO-B1-30/DEV_CLRn K8IO-B1-31L9IO-B1-32K9IO-B1-33L10IO-B1-34K10IO-B1-35L11IO-B1-8/GCLK1E1IO-B1-9F1TCK K1TDI J2TDO K2TMS J1G N D I N TG 4G N D I N T E 8IO-B1-36J5IO-B1-37J7R14422。

旺宝-金龙107开发板用户手册1、第一章 硬件篇1.1.金龙STM32F107VCT6开发板简介金龙107嵌入式开发板采用STM32F107VC,是意法半导体推出全新STM32互连型(connectivity)系列微控制器中的一款性能较强产品,此芯片集成了各种高性能工业标准接口,且STM32不同型号产品在引脚和软件上具有完美的兼容性,可以轻松适应更多的应用。

新STM32标准外设包括 10个定时器、两个12位 1 M sample/s AD(模数转换器)(快速交替模式下 2M sample/s)、两个12位DA(数模转换器)、两个I2C接口、五个USART接口和三个SPI端口和高质量数字音频接口IIS ,另外STM32F107拥有全速USB(OTG)接口,两路CAN2.0B 接口,以及以太网 10/100 MAC模块。

此芯片可以满足工业、医疗、楼宇自动化、家庭音响和家电市场多种产品需求!1.2.开发板板载资源STM32F107VCT6,ARM Cortex-M3内核,主频72MHz,内部含有256K字节的FLASH和64K字节的SRAM1个10M/100M以太网接口,标准RJ45接口,支持平行交叉网线自适应1个USB 2.0 OTG全速接口,可以作为USB SLA VE,也可以作为USB HOST 1个标准的3.2/4.3/5/7寸TFT LCD接口,带触摸功能1个I2S音频解码芯片WM8978,支持MP3软解,高品质音乐播放1个FM收音机芯片TEA57672个耳机接口1个SD卡接口1个2.4G无线通信模块接口1个红外接收头1个摄像头接口,选配OV7670模块1个温度传感器接口,选配DS18B202个CAN总线接口1个RS485接口1个RS232串口,DB9母头1个USB转串口芯片PL2303,笔记本使用更加方便1个SPI FLASH芯片,W25Q16,存储字库更加方便1个IIC接口的EEPROM芯片,24C02,容量2K1个小喇叭1个复位按钮,控制整板硬件复位4个功能按钮,其中包括WAKEUP唤醒功能和TEMPER入侵功能1个五向按键1个电源指示灯,LD2,红色4个用户状态指示灯,LD1,LD3,LD4,LD5红色2个启动模式选择配置端口1个RTC实时时钟后备电池座1个标准的JTAG/SWD仿真调试下载接口1路电位器可调电阻模拟输入,可以做模数转换实验1个DAC数模转换接口连接到接线端子1个ADC模数转换接口连接到接线端子1个PWM接口连接到接线端子1个DC5V电源接口1个电源开关,控制整个板子的电源除晶振占用的IO管脚,其余所有IO口全部引出到扩展双排插针2、第二章 专题讲解2.1专题一:MDK安装及下载请在网页搜索“红龙开发板 第一讲”注意几个不同点:1.红龙用的是104脚的 stm32f103ze,金龙用的是stm32f107vc因此选芯片有以下几方面不同a.选芯片,选stm32f107vcb.宏定义(关于库的,如果不用库,可以忽略),主要是*_CL,和*_HD的区别c.flashFlash选256k的2.2专题二:JFLASH的使用提示:如果你使用此方式下载,请断电上电后再测试,涉及到中断的程序必须重 新上电。

北京智嵌物联网电子技术ISTM32F107网络互联开发板3.0实验例程操作手册版本号:A拟制人:赵工时间:2013年7月1日目录1本文档编写目的 (1)2实验例程操作说明 (1)2.1LED闪烁实验 (1)2.2KEY_LED实验 (1)2.3RS232通讯实验 (1)2.4RS485通讯实验 (2)2.5CAN1通讯实验 (2)2.6CAN1与CAN2通讯实验 (3)2.7I2C实验—读写24c04 (4)2.8SPI通讯实验--读写SST2508B (5)2.9TCP服务器收发数据实验 (5)2.10动态IP实验 (7)2.11HTTP网页服务器实验 (7)2.12USB数据存储实验1(读写STM32F107片内flash) (9)2.13USB数据存储实验2(读写板载SST25F08B) (9)2.14U盘读写实验 (9)2.15USB鼠标实验 (11)2.16USB_JoyStickMouse实验 (11)2.17 2.4G无线模块NRF24l01通信实验 (12)2.18基于NRF24L01的无线RS232通讯实验 (12)2.19DS18B20温度试验 (13)2.20UDP客户端发送数据实验 (14)2.21UDP服务器收发数据实验 (15)2.22TCP客户端收发数据实验 (18)2.2316通道ADC采集实验 (21)2.24UDP与RS232RS485双向数据透明传输例程---开发板做服务器 (23)2.25TCP与RS232RS485双向数据透明传输实验 (23)2.26TCP与CAN双向数据透明传输实验 (23)1本文档编写目的本手册是针对STM32F107网络互联开发板V2.2的例程而编写的,包括每个实验例程的实验原理、实验步骤、注意事项等。

2实验例程操作说明2.1LED闪烁实验实验原理:通过控制PE2/PE3/PE4/PE5的电平变化实现LED灯的亮灭。

实验步骤:(1)用Keil uVision4打开LED灯闪烁实验工程,并编译。

在此首先说明,限于本人水平有限,以下说明可能会有错误,如果发现错误的地方,请及时向我反映,本人邮箱772113229@,本人经过校对确认之后,会及时的作出修改。

本文档只作参考使用,具体的实验现象与实际条件有关,所以难免会有所出入。

本实验说明是在实验者对keil设置和对STM32的库有一定的了解的基础上所作的说明,如果对keil的设置和STM32的库文件一点都不了解,请先学习用keil建立一个工程以及对外设固件库使用说明。

第一章金龙107——LED实验实验目的:1、熟悉金龙107的LED硬件设计,2、熟悉STM32的IO使用实验器材:金龙107开发板V1.0一块,J-linkV8,keil4.23,STM3.2库文件V3.5.0,USB数据线一根实验说明:在本实验中,主要使用到开发板上的LED灯,实现跑马灯,主要跳线帽:JP4和JP7都接在2-3上硬件说明:端口输出高电平,LED灯亮,端口输出低电平,LED灯灭。

程序说明:首先说明一点,STM32的启动过程,并不是从main开始的,而是从启动文件里面开始,然后又跳转到main(详细说明可以参见STM32启动文件说明),并且在启动文件中,跳转到main之前,已经调用了SystemInit();,实现对STM32的时钟配置。

然后从main函数开始说明,第一步SystemInit();这个函数官方已经写好,其主要配置了STM32的时钟,该函数,在启动文件中已经被调用了(详见STM32启动文件的说明),所以这里可以去掉。

接下来是对LED的初始化,其中该函数在hw_config.h中,首先是对端口的初始化,对端口的初始化,要注意的是首先要声明定义结构体,然后开启对应端口的时钟,然后对端口的结构体进行配置(配置说明详见固件库说明)。

下面就是对四个LED灯的初始化,在本例程中我们采用了宏定义,如下图,详见hw_config.h。

在while循环中,实现LED灯的循环亮灭。

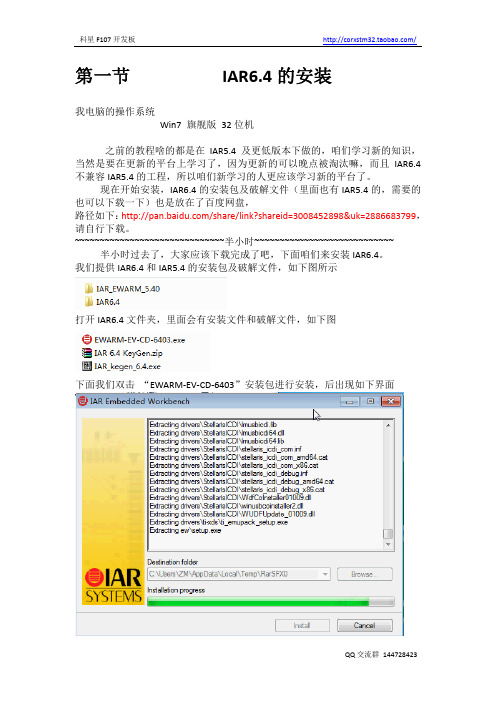

第一节 IAR6.4的安装我电脑的操作系统Win7 旗舰版 32位机之前的教程啥的都是在IAR5.4及更低版本下做的,咱们学习新的知识,当然是要在更新的平台上学习了,因为更新的可以晚点被淘汰嘛,而且IAR6.4不兼容IAR5.4的工程,所以咱们新学习的人更应该学习新的平台了。

现在开始安装,IAR6.4的安装包及破解文件(里面也有IAR5.4的,需要的也可以下载一下)也是放在了百度网盘,路径如下:/share/link?shareid=3008452898&uk=2886683799,请自行下载。

~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~半小时~~~~~~~~~~~~~~~~~~~~~~~~~~~~半小时过去了,大家应该下载完成了吧,下面咱们来安装IAR6.4。

我们提供IAR6.4和IAR5.4的安装包及破解文件,如下图所示打开IAR6.4文件夹,里面会有安装文件和破解文件,如下图下面我们双击 “EWARM‐EV‐CD‐6403”安装包进行安装,后出现如下界面之后会出现安装的一个选项,如下图这里我们点击图中红色部分的选项“Install IAR Embedded Workbench”,之后出现安装的一个进度条,如下图所示之后弹出一个安装向导的对话框,如下图然后点击图中的“Next”,进入到下一个安装界面,如下图这个是一个注册的界面,不用管那个“Register”,直接点下一步,进入到同意协议的一个界面,点“I accept……..”,也就是同意它的协议,之后点下一步“Next”点击下一步,会进入输入注册信息的对话框,如下图Name和Company可自己随意填写,下面的License的话,需要用到咱们的破解文件生成,下面运行安装包下面的破解程序也就是,如果你电脑的杀毒软件要干掉它的话,请暂时关掉杀毒软件,我电脑的AVAST和360对它还是比较友好的,没干掉他。

运行后出出现下图的程序之后在第一行“Product”栏内选择“Embedded Workbench For ARM v6.4”,如下图所示然后点击下面的“Get ID”,如下图之后就会出现新的License number和License key,如下图然后将新获取的License number粘贴到下图的License里面之后点下一步“Next”,会进入到下图的对话框,然后将前面获取的License key 复制粘贴过来,如下图所示下面的Read License Key From File的路径不用管,直接点“Next”,进入到下图所示的对话框这里,可以在“Change”按键那里修改下安装的路径,可以改在D盘,或者E 盘,看你电脑的程序安装在哪里了,其实C盘空间足够大,安装在C盘也是没问题的,然后点击“Next”,出现如下图所示的对话框直接点“Next”进入到下一个对话框进行程序的安装,如下图直接点击“Install”进行安装,这里的安装需要比较长的时间,请耐心等待,其实可以做些别的事情了,时间真的有点长,经过很长时间的安装后,会出现下图所示的界面然后去掉那两个对勾点“Finish”就安装完成了,其实不去掉对勾也是没问题的,就是打开程序了,再关掉就好了,安装完成了,安装完了,但是不一定是安装成功,下面我们打开IAR6.4,看一下是否是安装成功了,我电脑装的是WIN7系统,就以win7为例了,点击电脑左下角“开始”,如下图然后在自己安装的众多程序中找到IAR Systems点开“IAR Systems”,找到里面的“IAR Embedded Workbench”,也就是,点一下就可以打开IAR6.4了,具体路径如下图科星F107开发板/QQ 交流群 144728423打开后就出现下图的界面好的,大工告成了,再不放心,咱再弄个工程,编译一下嘛,新建IAR6.4的工程,请看下一章节!!!O(∩_∩)O 哈哈~。