延时可控高压脉冲发生器的设计

- 格式:pdf

- 大小:97.33 KB

- 文档页数:7

高压皮秒脉冲发生器的设计与实现高压皮秒脉冲发生器是一种用于产生高能量、高压、短脉冲的装置。

它在科学研究、工业应用和医疗领域都有重要的应用价值。

本文将介绍高压皮秒脉冲发生器的设计与实现,以及其在不同领域的应用。

高压皮秒脉冲发生器主要由高压电源、充电电路、储能电容、脉冲发生电路和输出负载等组成。

首先,高压电源是整个系统的核心组件,用于提供高压电源稳定可靠的电源。

其次,充电电路将电源输出的直流电压转化为脉冲电压,并通过控制充电时间和电流来实现对储能电容的快速充电。

储能电容是存储电能的装置,其容量越大,蓄能能力越强。

脉冲发生电路控制储能电容的放电过程,使得电容的电能以短脉冲的形式释放出来。

最后,输出负载是将脉冲能量传递给被测对象或其他设备的载体。

高压皮秒脉冲发生器的实现需要考虑以下几个关键问题。

首先,电源的选择和设计是非常重要的,需要满足高压、高能量、高稳定性等要求。

其次,充电电路的设计需要考虑充电速度和充电电流的控制,以保证储能电容能够快速充电并保持稳定。

第三,脉冲发生电路的设计需要考虑脉冲宽度、重复频率和输出电压的控制,以满足不同应用场景的需求。

最后,输出负载的选择和匹配需要根据具体应用来确定,以确保脉冲能量能够有效传递到被测对象或其他设备上。

高压皮秒脉冲发生器在科学研究领域有广泛的应用。

例如,在物理学中,它可以用于产生高能量的电子束或离子束,用于材料表面改性、微纳加工和材料分析等研究。

在化学领域,它可以用于产生高能量的化学反应,用于催化剂的制备和新材料的合成等研究。

在生物医学领域,它可以用于产生高能量的激光脉冲,用于皮肤美容、纹身去除和眼科手术等治疗。

高压皮秒脉冲发生器在工业应用中也有重要的作用。

例如,在电子器件制造中,它可以用于产生高能量的离子束,用于清洗、刻蚀和改性等工艺。

在材料加工中,它可以用于产生高能量的激光脉冲,用于焊接、切割和打孔等加工。

在电力系统中,它可以用于产生高能量的电磁脉冲,用于保护电力设备和系统。

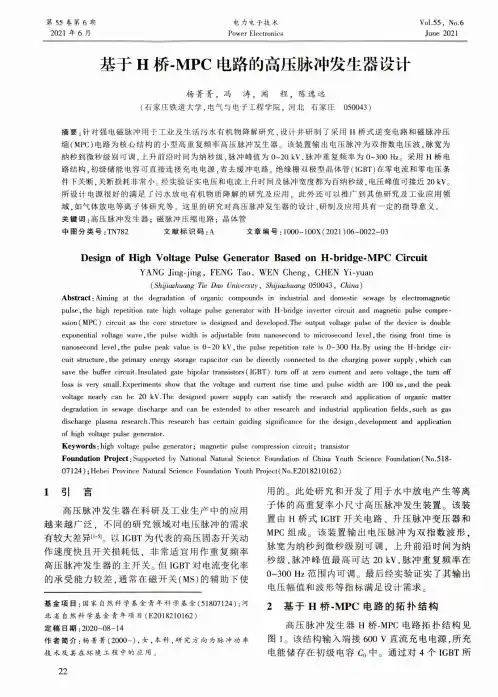

PLC用于智能控制高压脉冲发生器设计李巨;冯莉;张志强;邓云华【摘要】为了更好地满足复杂试验系统中对仪器智能化控制的要求,设计了一种基于PLC(可编程逻辑控制器)控制的智能化高压脉冲发生器.采用模块化设计结构,使用VB、Easy-Builder和STEP 7 MicroWIN作为编程语言,开发了PLC与触摸屏和上位机之间的控制程序,利用可编程逻辑控制器调节高压脉冲发生器的输出脉冲幅度,控制高压脉冲发生器实现触发、复位等功能.可通过触摸屏和上位机对仪器进行本地和远程操作,实时调节和读取仪器的状态,高压脉冲发生器具有较好的操控性和人机交互性,实现了仪器的智能化.【期刊名称】《自动化与仪表》【年(卷),期】2014(029)009【总页数】4页(P10-13)【关键词】可编程逻辑控制器;高压脉冲发生器;智能控制【作者】李巨;冯莉;张志强;邓云华【作者单位】中国工程物理研究院流体物理研究所,绵阳 621900;中国工程物理研究院流体物理研究所,绵阳 621900;中国工程物理研究院流体物理研究所,绵阳621900;中国工程物理研究院流体物理研究所,绵阳 621900【正文语种】中文【中图分类】TP23高压脉冲发生器作为一种常用的仪器,被广泛应用于科学研究及生产的各个领域。

由于高压脉冲发生器在使用过程中伴随着高压脉冲输出(通常为几千伏到几十千伏,甚至上百千伏)会存在很强的的电磁干扰,常规的单片机类智能控制器件较难适应这种强电磁干扰的场合,运用时需要采取比较复杂的抗电磁干扰措施。

因此,一直以来多数高压脉冲发生器仍为独立运行方式,没有采用自动控制技术。

而另一方面,经常可以看到,在进行某些科学研究、试验时往往是许多仪器协同工作,如要提高效率和准确性,实现测控的自动化,就必须对仪器的智能化提出要求。

本文介绍一种采用可编程逻辑控制器PLC作为智能控制部件的高压脉冲发生器的设计方法,其相应的控制技术也具有广泛的适用性。

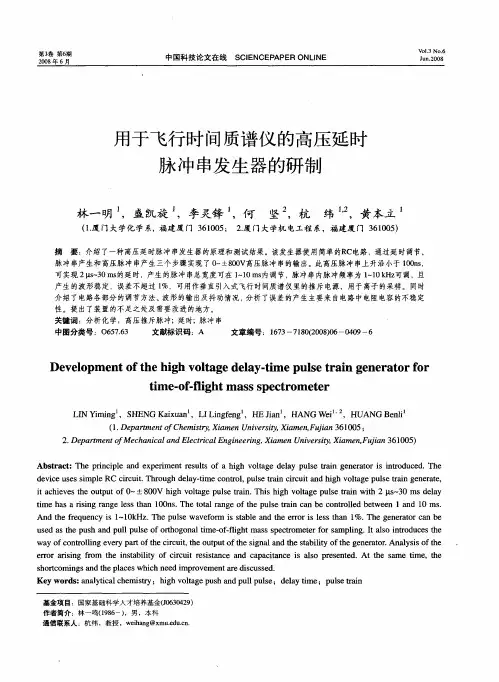

敬请登录网站在线投稿(t o u g a o.m e s n e t.c o m.c n)2021年第2期79F PG A的数字脉冲延时发生器设计陈泽洋(天津大学理学院,天津300072)摘要:本文主要介绍了一种数字式脉冲延时发生器的设计方法,该方案是基于A l t e r a(被I n t e l收购)的C y c l o n e I V系列F P G A实现的,为了同时满足高延时分辨率与大的可调范围,采用了粗细结合的延时方法,粗延时通过计数器法实现,细延时通过A D9501专用延时芯片实现;为了让用户与系统进行通信,在F P G A内部构建了N i o s I I软核处理器,并且编写软件程序实现人机交互㊂对系统的关键模块进行了仿真,仿真结果显示模块设计符合需求,最终延时系统可以实现精度为16.5p s㊁可调范围约为1.1s的延时㊂关键词:F P G A;A D9501;延脉冲发生时器;N i o s I I中图分类号:T N7文献标识码:AD e s i g n o f D i g i t a l P u l s e D e l a y G e n e r a t o r B a s e d o n F P G AC h e n Z e y a n g(S c h o o l o f S c i e n c e,T i a n j i n U n i v e r s i t y,T i a n j i n300072,C h i n a)A b s t r a c t:I n t h e p a p e r,a d e s i g n m e t h o d o f d i g i t a l p u l s e d e l a y g e n e r a t o r i s d e s i g n e d,w h i c h i s b a s e d o n A l t e r a's c y c l o n e I V s e r i e s F P G A.I n o r d e r t o m e e t t h e r e q u i r e m e n t s o f h i g h d e l a y r e s o l u t i o n a n d l a r g e a d j u s t a b l e r a n g e,c o m b i n e t h e c o a r s e d e l a y a n d f i n e d e l a y,t h e c o a r s e d e-l a y i s r e a l i z e d b y c o u n t e r m e t h o d,a n d t h e f i n e d e l a y i s r e a l i z e d b y A D9501s p e c i a l d e l a y c h i p.I n o r d e r t o e n a b l e u s e r s t o c o mm u n i c a t e w i t h t h e s y s t e m,N i o s I I s o f t c o r e p r o c e s s o r i s b u i l t i n F P G A,a n d s o f t w a r e p r o g r a m i s w r i t t e n t o r e a l i z e h u m a n-c o m p u t e r i n t e r a c t i o n.T h e k e y m o d u l e s o f t h e s y s t e m a r e s i m u l a t e d,a n d t h e s i m u l a t i o n r e s u l t s s h o w t h a t t h e m o d u l e d e s i g n m e e t s t h e r e q u i r e m e n t s.T h e f i n a l d e l a y s y s t e m c a n a c h i e v e a d e l a y a c c u r a c y o f16.5p s a n d a d y n a m i c r a n g e o f1.1s.K e y w o r d s:F P G A;A D9501;p u l s e d e l a y g e n e r a t o r;N i o s I I0引言脉冲延时发生器作为一种时序同步装置在激光系统[1-2]㊁雷达系统[3]㊁飞行时间质谱仪[4-5]等领域应用广泛,它可以对触发信号进行延时后输出脉冲信号,用户可以设定延时的大小㊂延时的分辨率与延时的可调范围是衡量其性能的两个重要参数,可以实现脉冲延时的方法有计数器法㊁存储器法[6]㊁专用延时芯片[7]等方法㊂计数器法与存储器法可以实现可调范围比较大的延时,不过延时精度由于受到时钟频率的限制只能做到纳秒量级,专用延时芯片法的延时精度可以做到皮秒量级,不过可调范围在微秒量级㊂F P G A是一种可编程逻辑器件,用户可以通过V e r i l o g H D L等设计文件在F P G A内部设计所需要的逻辑电路,与A S I C相比具有设计周期短㊁设计灵活等优点㊂本文介绍的延时脉冲发生器以A l t e r a(被I n t e l收购)的C y c l o n e I V系列F P G A为核心,采用粗细结合的延时方案,并且利用N i o s I I软核处理器用于系统控制,实现了脉冲延时发生器的设计㊂1基于F P G A的脉冲延时发生器整体设计延时系统的工作模式分为内触发模式与外触发模式㊂系统的设计框图如图1所示㊂工作在内触发模式时,触发信号由系统内部产生,用户可以设定触发信号的频率大小㊂工作在外触发模式时,触发信号由外部提供㊂整个延时系统的延时由粗延时部分和细延时部分组成,粗延时利用计数器法实现㊂计数器法的延时分辨率由采样时钟决定,本系统的采样时钟通过将外部50MH z晶振倍频得到,最终倍频数由系统能运行的最大时钟频率决定㊂细延时是利用A D9501实现的,A D9501通过8位控制字对单位粗延时进一步细分,得到16.5p s延时分辨率㊂P C机通过C P2102串口桥接芯片将设定的延时信息发送给N i o s I I软核处理器,延时信息包含用户设定的粗延时以及细延时,N i o s I I将粗延时信息经由P I O I P核传递到粗延时模块,细延时信息被转换成8位控制字,输出80M i c r o c o n t r o l l e r s &E m b e d d e d S ys t e m s 2021年第2期w w w .m e s n e t .c o m .c n图1 脉冲延时发生器的整体设计框图到A D 9501对其细延时进行控制㊂触发信号依次经过粗延时模块与A D 9501模块最终实现脉冲延时㊂其中内触发源模块㊁粗延时模块㊁N i o s I I 模块是在一块F P G A 内部㊂2 内触发源模块设计内触发源模块的作用是在内触发模式下提供触发信号㊂该模块的时序图如图2所示㊂图2 内触发源模块时序图c l k 为输入模块的时钟信号,d i v 为用户设定的分频数,c o u n t e r 为对时钟信号进行计数的计数器,o u t p u t 为最终输出的触发信号㊂当时钟信号到来时,启动计数器对时钟信号进行计数㊂当计数器计数的值等于d i v 时,将输出信号取反,同时计数器置零;当计数器的值不等于分频数时,输出保持不变,计数器持续对时钟信号进行计数㊂用户通过设置d i v 的值改变计数器的计数值,进而控制输出信号的跳变,从而达到对时钟信号进行分频的目的㊂3 粗延时模块设计粗延时模块负责对外部触发信号进行粗略延时,然后将延时后的脉冲输出到A D 9501进行细延时㊂该模块由输入时钟信号c l k ㊁触发信号t r i ㊁两个计数器p u l s e 1和pu l s e 2㊁两个计数器c o u n t e r 1和c o u n t e r 2组成㊂A D 9501的内部有一个斜波发生器,每次触发信号到来之后斜波发生器电压从0开始上升,当斜波发生器电压值与D A C 设定值相等时,拉高延时输出引脚电平,该斜波电压的置零是通过复位引脚实现的,拉复位引脚时,斜波发生器进行复位,如果不对其进行复位,则当下一个脉冲到来时,斜波发生器的电压是大于D A C 电压的,延时输出一直处于高电平状态,所以不能输出延时脉冲㊂由此可知,粗延时模块应该输出两个脉冲给A D 9501,分别为pu l s e 1和p u l s e 2,一个用于触发细延时,另一个用于将A D 9501斜波发生器置零㊂通过设定p u l s e 1与p u l s e 2之间的时间间隔就可以控制延时脉冲的脉宽大小㊂c o u n t -e r 1和c o u n t e r 2分别是延时计数器和脉宽计数器,通过延时控制字d e l a y 和脉宽控制字w i d t h 控制计数器计数到多少时输出脉冲信号,该模块的时序如图3所示㊂经过实验得知粗延时模块能够运行的最大时钟为240MH z,则粗延时分辨率为1/240MH z =4.2n s ,c o u n t e r 的位数设为28位,则最大延时为4.2n s ˑ228ʈ1.1s㊂图3 粗延时模块时序图4 细延时模块设计细延时模块是以A D 9501为核心实现的,它是在粗延时的分辨率基础上进一步细分实现更高分辨率的延时,A D 9501通过8位控制字对4.2n s 进行细分,则细分后的延时分辨率为4.2n s /28-1=16.5n s ㊂A D 9501的最小延迟(t P D )是触发电路延迟㊁斜坡发生器延迟和比较器延迟的总和㊂触发电路延迟和比较器延迟是固定的,斜坡发生器延迟是受线性斜坡变化率和偏移电压值影响的㊂最大延迟是t P D 和满量程(t D F S )的总和㊂斜坡发生器延迟是斜坡从其重置电压转换到D A C 电压所需的时间,D A C 电压由用户通过数字输入进行编程㊂满量程延迟(t D F S )由电容C e x t 和电阻R s e t 决定,范围为2.5n s ~10μs ,它们的关系如下:t D F S =R s e t ˑ(C e x t +8.5p F )ˑ3.84当满量程延时小于等于326n s 时,接C e x t 的引脚应当悬空;当满量程延时超过326n s 时,C e x t 引脚与电源之间可以最大加500p F 的电容㊂R s e t 的取值范围为50Ω~10k Ω㊂本设计想要实现满量程4.2n s 的延时,R s e t 大小应设置为128Ω,接C e x t 的引脚悬空㊂5 N i o s I I 控制模块设计从经济与系统复杂程度方面考虑,选用N i o s I I 软核处理器来实现P C 机对于系统的控制㊂N i o s I I 需要实现的功能为从P C 接收用户设定的延时值,然后将延时值发送给延时模块㊂利用Q s ys 自带I P 核可以实现加速设计,敬请登录网站在线投稿(t o u ga o .m e s n e t .c o m.c n )2021年第2期81图4 控制模块程序流程图实现数据接收与传输所需添加的主要I P 核有U A R T 与P I O ㊂P C 通过C P 2102将数据发送到U A R T I P 核的读寄存器,U A R T I P 核的r x d a t a寄存器接收到数据,使能读取中断,并将读取的数据在中断服务子程序中赋值给P I O ,就实现了P C 对延时系统的控制,图4为控制模块的程序流程图㊂6 关键模块仿真结果本设计的两个关键模块为内触发源模块与粗延时模块,编写测试文件对两个模块分别进行仿真,内触发源模块的仿真结果如图5所示㊂图5中信号从上到下依次是时钟信号c l k㊁复位信号r s t ㊁分频数d i v ㊁计数器c o u n t e r ㊁输出信号o u t ㊂可以看出,当分频数依次为0㊁1㊁2㊁3时,输出信号o u t 分别经过1个时钟周期㊁2个时钟周期㊁3个时钟周期㊁4个时钟周期发生电平的跳变,因此仿真结果表明,可以通过分频控制字d i v 来控制输出信号的分频数㊂粗延时模块的仿真结果如图6所示㊂图中信号从上到下依次是时钟信号c l k ㊁复位信号r s t ㊁触发信号t r㊁延时计数器c o u n t ㊁脉宽计数器c o u n t 1㊁延时控制字d e l a y㊁脉宽控制字w i d t h ㊁延时脉冲信号p u l s e 1㊁脉宽控制信号pu l s e 2㊂从仿真结果可以看出,当延时控制字为13㊁脉宽控制字为4时,触发信号到来之后的13个时钟信号输出p u l s e 1,pu l s e 1之后4个时钟信号输出p u l s e 2,该模块的设计符合需求㊂图5内触发源模块仿真结果图6 粗延时模块仿真结果7 性能比较将计数器法㊁专用延时芯片法㊁本设计的方法从可调范围㊁延时分辨率㊁功能扩展三个方面进行比较,结果如表1所列㊂表1 三种延时方法比较延时方法可调范围延时分辨率功能扩展计数器法m s ,s 量级n s 量级无法功能扩展专用延时芯片μs 量级ps 量级无法功能扩展本设计s 量级ps 量级便于功能扩展由表1中可知,本设计方法在保持计数器法与专用延时芯片方法优点的同时弥补了两种方法各自的不足,并且基于F P G A 灵活的特点,可以通过设计逻辑电路与编写N i o s I I 软核模块程序进行再次开发,以满足其他系统集成或者功能升级的需求㊂8 结 语目前国内的商用脉冲延时发生器主要依赖国外进口,价格一般在几万元到十几万元不等,价格昂贵并且性价比不高,本设计的脉冲延时发生器在满足高精度与大的可调范围的同时,成本方面也有很大的优势,整个系统制作成本仅为400元左右㊂在当今环境下,自主设计的脉冲延时发生器在商业与科技领域均具有重要意义㊂参考文献[1]蒋军敏,刘进元,刘百玉,等.用于激光打靶装置中的85敬请登录网站在线投稿(t o u ga o .m e s n e t .c o m.c n )2021年第2期85节的非线性特性耗费时间,无论系统的非线性多严重,均能按特定的关系进行转换㊂经数值分析将优化后的数据代入式(1)及联立式(1)和式(7),线性补偿前后物体位移y 和像点位移x 的关系如图6所示㊂y =270192x14216.256-398.32x+e d(8)图6 线性补偿前后物体位移y 和像点位移x 的关系5 结 语本文从反射式激光三角法测量原理公式㊁测量范围㊁分辨率及结构参数优化出发,用工程软件MA T L A B 对系统的各个参数之间的约束关系进行了分析与优化,使得参数优化过程得以简化,同时在实际中可根据器件因素和测量范围的要求不同随时改变,提高了设计的灵活性,降低了设计初期的费用,最后通过数值分析了造成物体位移与像点位移呈非线性的原因,并用线性补偿的方法使物体位移与像点位移线性输出,从而提高了测距传感器线性度与精度,降低了系统误差,实现了高精度大位移的测量㊂参考文献[1]王晓嘉,高隽,王磊.激光三角法综述[J ].仪器仪表学报,2004(S 2):601604,608.[2]L a r s L i n d n e r ,O l e g S e r g i y e n k o ,J u l i o C R o d r ígu e z Q u i ño n e z ,e t a l .M o b i l e r o b o t v i s i o n s y s t e m u s i n g c o n t i n u o u s l a s e r s c a n n i n gf o r i n d u s t r i a l a p pl i c a t i o n [J ].T h e I n d u s t r i a l R o b o t ,2016,43(4):360369.[3]S u Z h i q i ,H e Q i n g,X i e Z h i .I n d i r e c t m e a s u r e m e n t o f m o l t e n s t e e l l e v e l i n t u n d i s h b a s e d o n l a s e r t r i a n g u l a t i o n [J ].T h e R e -v i e w o f s c i e n t i f i c i n s t r u m e n t s ,2016,87(3):035117.[4]宋腾,张凤生,任锦霞.直射式激光位移传感器光束入射角对测量精度的影响[J ].机械,2017,44(2):3741.[5]Z h u a n g B H.N o n c o n t a c t m e a s u r e m e n t o f s c r a t c h o n a i r c r a f t s k i n s [J ].A p p l i e d l a s e r ,1997(2):4936.[6]任伟明,孙培懋,王亚雷,等.一种标定三角测量法激光位移计的方法[J ].光学技术,1997(3):1113,16.[7]赵景海,孙飞显.基于残差补偿的激光位移传感器测距方法[J ].计算机工程,2018,44(10):298302.[8]曹红超,陈磊,王波,等.一种改进型高精度激光三角位移传感器的结构设计研究[J ].激光杂志,2007(6):1415.[9]X u e l i H a o ,A i m i n S h a ,Z h a o yu n S u n ,e t a l .L a s e r b a s e d m e a s u r i n g m e t h o d f o r m e a n j o i n t f a u l t i n g va l u e o f c o n c r e t e p a v e m e n t [J ].O p t i k I n t e r n a t i o n a l J o u r n a l f o r L i gh t a n d E -l e c t r o n O pt i c s ,2016,127(1):274278.[10]胡纪五,史雪飞.仪表线性化优化设计[J ].电测与仪表,2000(2):58.[11]卢治功,贺鹏,职连杰,等.基于最小二乘法多项式拟合三角测量模型研究[J ].应用光学,2019,40(5):853858.[12]姜庆胜,计时鸣,张利.基于计算机视觉的机械零件平面曲线检测和识别研究[J ].机电工程,2005(7):47.樊鹏辉(硕士研究生),主要研究方向为传感器技术;杨光永(副教授),主要研究方向为传感器技术㊁机器人技术;程满(硕士研究生),主要研究方向为A G V 路径规划;刘叶(硕士研究生),主要研究方向为电机控制;徐天奇(教授),主要研究方向为传感器技术㊁自动化㊂(责任编辑:薛士然 收稿日期:2020-09-11) 新型同步系统的研究[J ].光子学报,2002(3):381383.[2]D T i a n ,G Y a n g .D e s i g n a n d d e v e l o p m e n t o f a m i n i a t u r e d i gi t a l d e l a y g e n e r a t o r f o r l a s e r i n d u c e d b r e a k d o w n s p e c t r o s c o p y[J ].I n s t r u m e n t a t i o n s c i e n c e &t e c h n o l o g y,2015(43):115124.[3]S Z h a o l i n ,L N a n ,W Y i n a n .H i g h r e s o l u t i o n p r o gr a mm a b l e d i g i t a l d e l a y g e n e r a t o r d e s i gn a n d r e a l i z a t i o n [C ]//2010I n -t e r n a t i o n a l C o n f e r e n c e o n I n t e l l i g e n t S y s t e m D e s i gn a n d E n -g i n e e r i n g A p p l i c a t i o n I E E E C o m p u t e r S o c i e t y,2010.[4]C L F e n g ,L G a o ,J H L i u .L a s e r m a s s s p e c t r o m e t r yf o r o n -l i n e d i ag n o s i s o f r e a c t i v e p l a s m a s w i th m a n y s p e ci e s [J ].R e -v i e w o f S c i e n t i f i c I n s t r u m e n t s ,2011(6):261434.[5]S V K o v t o u n ,R D E n gl i s h ,R J C o t t e r .M a s s c o r r e l a t e d a c c e l -e r a t i o n i n a r e f l e c t r o n MA L D I T O F m a s s s pe c t r o m e t e r :A n a p p r o a c hf o r e n h a n c e d r e s o l u t i o n o v e r a b r o a d m a s s r a ng e [J ].J o u r n a l o f th e A m e ri c a n S o c i e t y f o r M a s s S p e c t r o m e t r y,2002(13):135143.[6]邱有刚,黄建国,李力.基于F P G A 数字延迟单元的实现和比较[J ].电子测量技术,2011,34(9):6568.[7]马艳喜.数字延时器A D 9501的性能及其应用[J ].电子元器件应用,2002,4(11):2728.陈泽洋,主要研究方向为快点子学与离子光学㊂(责任编辑:薛士然 收稿日期:2020-08-19)。

1llO仪器仪表学报第3l卷3高压纳秒脉冲发生器的研制高压纳秒脉冲发生器的原理框图如图3所示,该装置主要由高压直流电源、纳秒脉冲形成系统和脉冲整形及计数系统三大部分组成。

纳秒脉冲形成系统…………….企…………….钮刮里h—习■刭一传:感厶畸器ry t图3高压纳秒脉冲发生器基本原理框图Fig.3The basic principles of the hish—voltagenanosecond pulse generator高压纳秒脉冲发生器基本原理:高压直流电源通过限流保护电阻向LC形成线网络充电,在达到自击穿开关阈值电压时,自击穿开关瞬间击穿并在匹配负载(50Q处产生幅值为充电电压一半的高压纳秒方波脉冲。

电流传感器在放电回路中采集脉冲电流,经过滤波、脉冲整形处理电路引入脉冲计数器,在脉冲输出重复频率一定时,通过计数器内置继电器控制整个装置的电源输入,从而实现本装置治疗时间窗口可控。

3.1高压直流电源为减小装置的体积和重量,满足医用设备便携、简单可靠特性,高压直流电源采用高压恒流源(天津东文DW—IX303.1FlD。

输出电压:DC O一+30kV;最大输出电流:l mA,电源配有电流、电压显示模块和调节电位器,并具有过压、过流保护模块。

通过调节电源输出电流来控制LC形成线网络的充电速度,进而控制自击穿开关的闭合频率,最终实现装置输出脉冲重复频率可调,便于寻找最佳肿瘤细胞治疗剂量。

3.2纳秒脉冲形成系统纳秒脉冲形成系统主要由LC网络、自击穿开关和负载电阻组成。

高陡度方波脉冲所包含的高频分量将有助于肿瘤细胞内电处理效应,进一步提高肿瘤细胞凋亡率及治疗效果,因此如何提高输出脉冲上升沿陡度是本装置的关键技术之一。

根据电路理论¨…,脉冲的上升时间与杂散电感成正比,因此本装置主要从两个方面提高方波前沿的陡度。

一方面在设计过程中,选择优质无感电容、电阻;合理布线,尽量减小回路所包含的面积,以减小回路杂散电感。

可控脉冲发生器的设计一、 实验目的1、 了解可控脉冲发生器的实现机理。

2、 学会用示波器观察FPGA 产生的信号。

3、 学习用VHDL 编写复杂功能的代码。

二、 实验原理脉冲发生器就是要产生一个脉冲波形,而可控脉冲发生器则是要产生一个周期和占空比可变的脉冲波形。

可控脉冲发生器的实现原理比较简单,可以简单的理解为一个计数器对输入的时钟信号进行分频的过程。

通过改变计数器的上限值来达到改变周期的目的,通过改变电平翻转的阈值来达到改变占空比的目的。

下面举个简单的例子来说明其工作原理。

假如有一个计数器T 对时钟分频,其计数的范围是从0~N ,另取一个M (0≤M ≤N ),若输出为Q ,那么Q 只要满足条件时,通过改变N 值,即可改变输出的脉冲波的周期;改变M 值,即可改变脉冲波的占空比。

这样输出的脉冲波的周期和占空比分别为:三、 实验内容编写实现可控脉冲发生器程序,通过脉冲周期和占空比改变实现不同脉冲的输出。

用Quartu s 软件对设计进行编译、综合、仿真,给出相应的时序仿真波形和硬件电路图。

四、 实验程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity exp10 isport( Clk : in std_logic; --时钟输入Rst : in std_logic; --复位输入⎩⎨⎧≤≤<≤=N T M M T Q 001%1001)1(⨯+=+=N M T N CLOCK占空比周期NU,ND : in std_logic; --输入:控制频率的改变MU,MD : in std_logic; --输入:控制占空比的改变Fout : out std_logic --波形输出);end exp10;architecture behave of exp10 issignal N_Buffer,M_Buffer : std_logic_vector(10 downto 0);signal N_Count :std_logic_vector(10 downto 0);signal clkin : std_logic;signal Clk_Count : std_logic_vector(12 downto 0); --产生一个低速时钟,用于按键判断beginprocess(Clk) --计数器累加beginif(Clk'event and Clk='1') thenif(N_Count=N_Buffer) thenN_Count<="00000000000";elseN_Count<=N_Count+1;end if;end if;end process;process(Clk) --波形判断beginif(Clk'event and Clk='1') thenif(N_Count<M_Buffer) thenFout<='1';elsif(N_Count>M_Buffer and N_Count<N_Buffer) thenFout<='0';end if;end if;end process;process(Clk)beginif(Clk'event and Clk='1') thenClk_Count<=Clk_Count+1;end if;clkin<=Clk_Count(12);end process;process(clkin) --频率及占空比的改变1beginif(clkin'event and clkin='0') thenif(Rst='0') thenM_Buffer<="010********";N_Buffer<="10000000000";elsif(NU='0') thenN_Buffer<=N_Buffer+1;elsif(ND='0') thenN_Buffer<=N_Buffer-1;elsif(MU='0') thenM_Buffer<=M_Buffer+1;elsif(MD='0') thenM_Buffer<=M_Buffer-1;end if;end if;end process;end behave;五、时序仿真图。

延时可控高压脉冲发生器的设计延时可控高压脉冲发生器的设计延时可控高压脉冲发生器的设计1引言以往研制的高压脉冲发生器采用V型管作为高压脉冲形成级,该管为冷阴极结构形式,一般工作电压在10~15kV范围内,输出高压脉冲相对外触发的延时随直流供电电压的不同而有较大变化,抖动也较大,且长时间工作后,延时和抖动都要增大。

用于触发Marx发生器及高电压脉冲触发装置需要更高的高压触发脉冲,且需在5~30kV范围内连续可调,具有前沿快、延时准确稳定、抖动小、抗干扰能力强等性能。

设计高压脉冲形成级是本机的重点,关键是选择能满足本机各项技术指标要求的高电压、大电流、快速开关管。

为了提高触发系统的延时精度,采用精度为10ns的数字延时单元,延时在10ns~99μs范围,步进10ns,以CPU8031为控制核心的集成电路实现人机对话,增强可靠性和先进性。

直流高压供电采用DC/DC变换技术,封装在金属盒内,实现了电源小型化,增强了抗干扰能力。

2发生器的构成及其工作原理2.1高压脉冲发生器结构延时可控高压脉冲发生器结构框图,是由外触发控制电路、单片机控制电路、延时电路、驱动电路、直流高压电路及高压脉冲形成及输出电路等组成。

图1高压脉冲发生器组成框图外触发控制电路是将外触发信号通过内部的比较器进行电压比较,再通过光电隔离器使外触发信号的地与控制线路的地分开,以屏蔽和减弱外界的电磁干扰及地干扰,增强本机的抗干扰能力。

单片机控制电路、延时电路是通过单片机实现人机对话,来预置延时电路的延时时间,达到延时可控目的。

驱动电路是将延时电路输出幅度较低的脉冲信号变为较高幅度的脉冲信号,用以驱动后级高压脉冲形成电路。

直流高压电路采用DC/DC变换,低压24V经振荡电路产生频率较高交流信号,再经高频脉冲变压器升压及多级倍压输出5~30kV连续可调的直流高压,为高压脉冲形成电路供电。

高压脉冲形成输出电路是本机重要部分,主要是形成和输出负高压脉冲。

脉冲发生器一.设计题目脉冲发生器的设计二.主要技术指标脉冲信号发生器:频率2K-20K可调三.方案论证与选择NE555构成的单稳态电路(触发时间为一秒)单稳工作方式,它可分为3种。

见图示。

第1种(图1)是人工启动单稳,又因为定时电阻定时电容位置不同而分为2个不同的单元,并分别以1.1.1 和1.1.2为代号。

他们的输入端的形式,也就是电路的结构特点是:“RT-6.2-CT”和“CT-6.2-RT”。

图2-1 555人工启动单稳第2种(图2)是脉冲启动型单稳,也可以分为2个不同的单元。

他们的输入特点都是“RT-7.6-CT”,都是从2端输入。

1.2.1电路的2端不带任何元件,具有最简单的形式;1.2.2电路则带有一个RC微分电路。

图2-2 555脉冲启动单稳第3种(图3)是压控振荡器。

单稳型压控振荡器电路有很多,都比较复杂。

为简单起见,我们只把它分为2个不同单元。

不带任何辅助器件的电路为1.3.1;使用晶体管、运放放大器等辅助器件的电路为1.3.2。

图中列出了2个常用电路。

图2-3单稳型压控振荡电路四.系统总图图2-4 总体电路图波形发生器一、设计题目波形发生器的设计与制作二.主要技术指标输出频率为160Hz的正弦波、方波、三角波。

正弦波幅度10V;方波幅度6V;三角波幅度为4V。

三.方案论证及选择:正弦波:方案一、由R、C振荡电路产生,其中包括R、C串并联电路和R、C移相电路两种。

方案二、由L、C振荡电路产生。

方案三、由集成运放构成的RC桥式振荡电路产生。

包括放大、反馈、选频和稳幅等基本部分。

输出波形稳定性良好。

方波:方案一、方波可由NE555构成多谐振荡器来产生。

方案二、由运放构成的电压比较器,在运放的输出端引入限流电阻和两个背靠背的稳压管组成双向限幅方波产生电路。

三角波:方案一、由方波来产生:可以由NE555电路产生的方波或是集成运放产生的通过R、C积分来得到。

方案二、由同相输入迟滞比较器和积分器产生方案选择:通过对以上方案进行比较,我们选择的方案是:正弦波是由集成运放构成的RC 桥式振荡电路产生。

高压强脉冲电源的设计西安兆福电子史平君—中国兵器工业第二0六研究所特种电源部主任、高级工程师,IEEE会员,中国电源学会常务理事、中国电源学会特种电源专业委员会主任委员,陕西省电源学会副理事长,西安市电源学会副理事长,陕西省笫五届科协委员。

专业特长为高压电源、高压脉冲电源,军用特种电源,雷达发射机及导航发射机电源,高能物理及加速器电源,高压充电电源等。

摘要:本文提出了一种强脉冲发生器电源的设计方案,应用此方案设计了高压电源、IGBT控制充电、可控硅控制放电,可以自动运行的脉冲磁场发生设备。

最大直流电压到达3KV且连续可调,放电脉冲电流高达10000A。

该设备由一片AT89C52单片机控制,可实现与电脑的连接。

关键词:高压电源; IGBT ;可控硅The Design of High Voltage Pulsed Power SupplyAbstract: This paper presents a strong pulse generator power supply design, applications for this program designed high-voltage power supply, IGBT control the charging and SCR controlled discharge, can be run automatically pulse magnetic field equipment. Maximum DC voltage 3KV and continuously adjustable discharge pulse currents up to 10000A. The device is controlled by an AT89C52 microcontroller can be realized with the computer.Key words: high voltage power supply;IGBT;SCR,引言:强脉冲磁场对工业装置及医疗的作用[1],强脉冲磁场对金属形成时的影响[2]以及脉冲磁场刺激对生物体的效应等已经越来越引起人们的关注。

高压陡脉冲发生器的设计与实现陈穗;郭蒙召;张建勋【摘要】According to the requirements of high voltage electrical pulse ablation, a high-voltage and steep pulse generator is designed and built. The whole frame of the high-voltage and steep pulse generator is introduced and the work process of generator is illustrated. The structure and principle of charge module and pulse generation module are introduced in detail. According to way of working of the main circuit, a controller with DSP+CPLD architecture is designed. The controller contains DSP module, CPLD module, communication interface between DSP and CPLD and interface circuit in that different anti-interference designs are used to guarantee transmission quality according to analog signal and digital signal and different frequency of signal. The discharge experiment indicates that performance of the circuit meet the requirements of high voltage electrical pulse ablation.%根据高压电脉冲消融的条件, 设计并搭建了高压陡脉冲发生器.介绍了高压陡脉冲发生器的整体结构, 阐述了脉冲发生器的工作过程, 详细介绍了充电模块和脉冲发生模块的结构组成和工作原理.针对主电路的工作方式, 设计了高压陡脉冲发生器控制器, 控制器采用DSP+CPLD的主控架构, 包括DSP模块、CPLD模块、通讯接口以及底层接口电路的设计.在底层接口电路中, 针对模拟信号和数字信号特性以及信号频率等采取了不同抗干扰措施, 以提高信号传输质量.放电试验表明, 电路性能满足高压电脉冲消融的治疗要求.【期刊名称】《自动化与仪表》【年(卷),期】2019(034)002【总页数】6页(P5-10)【关键词】高压陡脉冲发生器;IGBT;控制器;抗干扰设计【作者】陈穗;郭蒙召;张建勋【作者单位】南开大学人工智能学院,天津 300350;天津市智能机器人技术重点试验室,天津 300350;南开大学人工智能学院,天津 300350;天津市智能机器人技术重点试验室,天津 300350;南开大学人工智能学院,天津 300350;天津市智能机器人技术重点试验室,天津 300350【正文语种】中文【中图分类】TN782目前,全球癌症负担不断加重,癌症已经成为威胁人类生命和健康的主要疾病之一[1]。

基于DDS 芯片AD9851的高压脉冲发生器设计肖 珊,鲁五一(中南大学信息科学与工程学院 湖南长沙 410075)摘 要:设计了一种基于DDS (直接数字频率合成)芯片AD9851的可调高压脉冲发生器,该发生器主要由脉冲形成控制部分、信号放大部分及隔离3部分组成。

通过单片机、DDS 芯片及控制电路可以产生脉宽可调的脉冲信号,通过电阻分压调节器、高压变压器等外围电路来实现幅度可调的高压脉冲,不仅提高了脉冲发生器工作的稳定性,而且能方便、实时地实现脉冲宽度与幅度的在线调节。

关键词:脉冲;AD9851;频率;高压中图分类号:TN782 文献标识码:B 文章编号:1004373X (2007)0201703Design of High Voltage Pulse G enerator B ased on DDS ChipAD9851XIAO Shan ,L U Wuyi(Information Science &Engineering College ,Central South University ,Changsha ,China )Abstract :The paper introduces the design of an adjusting high voltage pulse generator based on the chip of AD9851(DDS ).The high voltage pulse generator is mainly composed of the pulse generation ,signal amplification and isolation unit.Pulse width is adjustable by single chip ,DDS and control circuit.By voltage adapter and high voltage transformer ,it generates high voltage pulse whose amplitude is adjustable.It can improve the stability of high voltage pulse generator and adapt the pulse width and amplitude conveniently.K eywords :pulse ;AD9851;f requency ;high voltage收稿日期:20060711 当代脉冲发生器里的脉冲形成器件,大部分是用火花气隙(spark gap )和高压电子开关(high voltage switch )。

Supertex inc.HV738DB1Designing a Pulser with HV738This demoboard data sheet describes how to use the HV738DB1 to generate the basic high voltage pulse waveform as an ultrasound transmitting pulser.The HV738 circuit uses the DC coupling method in all level translators. There are no external coupling capacitors needed. The V PP and V NN rail voltages can be changed rather quickly, compared to a high voltage capacitor gate coupled driving pulser. This direct coupling topology of the gate drivers not only saves two high voltage capacitors per channel, but also makes the PCB layout easier.The input stage of the HV738 has high-speed level translators that are able to operate with logic signals of 1.2 to 5.0V and are optimized at 2.5 to 3.3V. In this demoboard, the control logic signals are connected to a high-speed ribbon cable connector. The control signal logic-high voltage should be the same as the V CC voltage of the demoboard, and the logic-low should be reference to GND.The HV738DB1 output waveforms can be displayed by using an oscilloscope probe directly connected to the test point TX1~4 and GND. The soldering jumper can select whether or not to connect the on-board equivalent-load, a 330pF, 200V capacitor, parallel with a 2.5kΩ, 1W resistor. Also, a coaxial cable can be used to connect the user’s transducer to easily drive and evaluate the HV738 transmitter pulser.Typical Application CircuitHV738 ±65V 0.75AUltrasound Pulser DemoboardIntroductionThe HV738 is a monolithic four channel, high speed, high voltage, ultrasound transmitter pulser. This integrated, high performance circuit is in a single 7x7mm, 48-lead QFN package.The HV738 can deliver up to ±0.75A source and sink current to a capacitive transducer. It is designed for medical ultrasound imaging and ultrasound material NDT applications. It can also be used as a high voltage driver for other piezoelectric or capacitive MEMS transducers, or for ATE systems and pulse signal generators as a signal source.HV738’s circuitry consists of controller logic circuits, level translators, gate driving buffers and a high current and high voltage MOSFET output stage. The output stages of each channel are designed to provide peak output currents over ±1.1A for pulsing, when MC0 = 1 and MC1 = 1, with up to ±65V swings. When in mode 1, all the output stages drop the peak current to ±140mA for low-voltage CW mode operation to save power. Two floating 8.0VDC power supplies, referenced to V PP and V NN , supply the P- and N-type power FET gate drivers. This pulser waveform’s frequency upper limit is 20MHz depending on the load capacitance. One HV738 can also be used as four damping circuits to generate fast return-to-zero waveforms by working with another HV738 as four pulsing circuits. It also has built-in under-voltage and over-temperature protection functions.V -8VThe PCB Layout TechniquesThe large thermal pad at the bottom of the HV738 packageis connected to the VSUB pins to ensure that it always hasthe highest potential of the chip, in any condition. VSUB isthe connection of the IC’s substrate. PCB designers need to pay attention to the connecting traces as the output TXP1~4, TXN1~4 high-voltage and high-speed traces. In particular, low capacitance to the ground plane and more trace spacing need to be applied in this situation.High-speed PCB trace design practices that are compatible with about 50 to 100MHz operating speeds are used for the demoboard PCB layout. The internal circuitry of the HV738 can operate at quite a high frequency, with the primary speed limitation being load capacitance. Because of this high speed and the high transient currents that result when driving capacitive loads, the supply voltage bypass capacitors and the driver to the FET’s gate-coupling capacitors should beas close to the pins as possible. The VSS pin pads shouldhave low inductance feed-through connections that areconnected directly to a solid ground plane. The VDD , VPP, VPF,V NF and VNNsupplies can draw fast transient currents of upto ±1.5A, so they should be provided with a low-impedance bypass capacitor at the chip’s pins. A ceramic capacitor of up to 0.22 to 1.0µF may be used. Minimize the trace length to the ground plane, and insert a ferrite bead in the power supply lead to the capacitor to prevent resonance in the power supply lines. For applications that are sensitive to jitter and noise and using multiple HV738 ICs, insert anotherferrite bead between VDD and decouple each chip supplyseparately.Pay particular attention to minimizing trace lengths and using sufficient trace width to reduce inductance. Surface mount components are highly recommended. Since the output impedance of HV738’s high voltage power stages are very low, in some cases it may be desirable to add a small value resistor in series with the output TXP1~4 and TXN1~4 to obtain better waveform integrity at the load terminals. This will, of course, reduce the output voltage slew rate at the terminals of a capacitive load. Be aware of the parasitic coupling from the outputs to the input signal terminals of HV738. This feedback may cause oscillations or spurious waveform shapes on the edges of signal transitions. Since the input operates with signals down to 1.2V, even small coupling voltages may cause problems. Use of a solid ground plane and good power and signal layout practices will prevent this problem. Also ensure that the circulating ground return current from a capacitive load cannot react with common inductance to create noise voltages in the input logic circuitry.Testing the Integrated PulserThis HV738 pulser demoboard should be powered up with multiple lab DC power supplies with current limiting functions. The following power supply voltages and current limits have been used in the testing: VPP= 0 to +65V 5.0mA, VNN= 0 to -65V 5.0mA, VDD= +8.0V 10mA, (VPP- VPF) = +8.0V 10mA, (VNF- VNN) = +8.0V 10mA. VCC= +2.5V 5.0mA for HV738 VLL does not include the user’s logic circuits.The power-up or down sequences of the voltage supply ensure that the HV738 chip substrate VSUBis always at the highest potential of all the voltages supplied to the IC.The (VPP- VPF) and (VNF- VNN) are the two floating power supplies. They are only 8.0V, but floating with VPPand VNN. The floating voltages can be trimmed within the range of +7.5 to +10V to match the rising and falling time of the output pulses for the best HD2. Do not exceed the maximum voltage of +10V. The VPPand VNNare the positive and negative high voltages. They can be varied from 0 to +/-65V maximum. Note when the VPP= VNN=0, the VPFand VNFin respect to the ground voltage is -8.0V and +8.0V.The on-board dummy load 330pF//2.5kΩ should be connected to the high voltage pulser output through the solder jumper when using an oscilloscope’s high impedance probe to meet the typical loading conditions. To evaluate different loading conditions, one may change the values of RC within the current and power limit of the device.In order to drive piezo transducers with a cable, one should match the output load impendence properly to avoid cable and transducer reflections. A 70 to 75Ω coaxial cable is recommended. The coaxial cable end should be soldered to the TX1~4 and GND directly with very short leads. If a user’s load is being used, the on board dummy load should be disconnected by cutting the small shorting copper trace in between the zero ohm resistors R7, R8, R9 or R10 pads. They are shorted by factory default.All the on-board test points are designed to work with the high impedance probe of the oscilloscope. Some probes may have limited input voltage. When using the probe on these high voltage test-points, make sure that VPP/VNN voltages do not exceed the probe limit. Using the highimpendence oscilloscope probe for the on-board test points, it is important to have short ground leads to the circuit board ground plane.Precautions need to be applied to not overlap the logic-high time periods of the control signals. Otherwise, permanent damage to the device may occur when cross-conduction or shoot-through current exceed the device’s maximum limits.SchematicBoard LayoutD1Note:(1). Overlap control signals logic-high periods of PIN and NIN may cause the device permanent damage.(2). Due to the speed of logic control signal, every GND wire in the ribbon cable must connect to signal source ground.(3). (V PP -V PF ) and (V NF -V NN ) floating voltage can be trimmed from +7.5V to +10V for tr/tf time matching. Do not exceed the maximum +10V.HV738DB1 WaveformsFigure 1: Output waveform of 20MHz, V LL = 2.5V, V DD = +8.0V, (V PP - V PF ) = +8.0V, (V NF - V NN ) = +8.0V, V PP /V NN = +/-65V, MC0=MC1=1, HV738 TX4 via 200Ω and 20dB Attenuator & SMA-BNC RG316 cable to Ch4 50Ω oscilloscope input.Figure 2: Output waveform of 10MHz V LL = 2.5V, V DD = +8.0V, (V PP - V PF ) = +8.0V, (V NF -V NN ) = +8.0V, V PP /V NN = +/-65V, MC0=MC1=1, TX4 via 200Ω and 20dB Attenuator & SMA-BNC RG316 cable to Ch4 50Ω oscilloscope input.Figure 3: Input to output propagation delay on rise is 17.6ns V LL = 2.5V, V DD =+8.0V, (V PP - V PF ) = +8.0V, (V NF - V NN ) = +8.0V, V PP /V NN = +/-65V, MC0=MC1=1, TX4 via 200Ω and 20dB Attenuator & SMA-BNC RG316 cable to Ch4 50Ω oscilloscope input.Figure 4: Input to output propagation delay on fall is 17.6ns. V LL = 2.5V, V DD = +8.0V, (V PP - V PF ) = +8.0V, (V NF - V NN ) = +8.0V, V PP /V NN = +/-65V, MC0=MC1=1, TX4 via 200Ω and 20dB Attenuator & SMA-BNC RG316 cable to Ch4 50Ω oscilloscope input.Figure 5: Output rise and fall time is 31ns and 40ns. V LL = 2.5V, V DD = +8.0V, (V PP - V PF ) = +8.0V, (V NF - V NN ) = +8.0V, V PP /V NN = +/-65V, MC0=MC1=1, with load of 330pF//2.5kΩ. TX1 via 200Ω and 20dB Attenuator & SMA-BNC RG316 cable to Ch4 50Ω oscilloscope input.Figure 6: Output waveform of 5.0MHz, V LL = 2.5V, V DD = +8.0V, (V PP - V PF ) = +8.0V, (V NF - V NN ) = +8.0V, V PP /V NN = +/-5.0V, MC0=MC1=1, with load of 330pF//2.5kΩ. HV738 TX1 via 200Ω and 20dB Attenuator & SMA-BNC RG316 cable to Ch4 50Ω oscilloscope input.Figure 7: Output waveform of 5.0MHz, V LL = 2.5V, V DD = +8.0V, (V PP - V PF ) = +8.0V, (V NF -V NN ) = +8.0V, V PP /V NN = +/-5.0V, MC0=0, MC1=1, with load of 330pF//2.5kΩ. TX1 via 200Ω and 20dB Attenuator & SMA-BNC RG316 cable to Ch4 50Ω oscilloscope input.Figure 8: Output waveform of 5.0MHz, V LL = 2.5V, V DD = +8.0V, (V PP - V PF ) = +8.0V, (V NF - V NN ) = +8.0V, V PP /V NN = +/-5.0V, MC0=1, MC1=0, with load of 330pF//2.5kΩ. TX1 via 200Ω and 20dB Attenuator & SMA-BNC RG316 cable to Ch4 50Ω oscilloscope input.Figure 9: Output waveform of 5.0MHz, V LL = 2.5V, V DD = +8.0V, (V PP - V PF ) = +8.0V, (V NF - V NN ) = +8.0V, V PP /V NN = +/-5.0V, MC0=0, MC1=0, with load of 330pF//2.5kΩ. TX1 via 200Ω and 20dB attenuator & SMA-BNC RG316 cable to Ch4 50Ω oscilloscope input.Figure 10: Output waveform of 20MHz, V LL = 2.5V, V DD = +8.0V, (V PP - V PF ) = +8.0V, (V NF - V NN ) = +8.0V, V PP /V NN = +/-5.0V, MC0=1, MC1=1, with load of 330pF//2.5kΩ. TX1 via 200Ω and 20dB Attenuator & SMA-BNC RG316 cable to Ch4 50Ω oscilloscope input.Supertex inc. does not recommend the use of its products in life support applications, and will not knowingly sell them for use in such applications unless it receives an adequate “product liability indemnification insurance agreement.” Supertex inc. does not assume responsibility for use of devices described, and limits its liability to the replacement of the devices determined defective due to workmanship. No responsibility is assumed for possible omissions and inaccuracies. Circuitry and specifications are subject to change without notice. For the latest product specifications refer to the Supertex inc. (website: http//)©2014 Supertex inc.All rights reserved. Unauthorized use or reproduction is prohibited.Supertex inc.。

延时可控高压脉冲发生器的设计

延时可控高压脉冲发生器的设计

1引言

以往研制的高压脉冲发生器采用V型管作为高压脉冲形成级,该管为冷阴极结构形式,一般工作电压在10~15kV范围内,输出高压脉冲相对外触发的延时随直流供电电压的不同而有较大变化,抖动也较大,且长时间工作后,延时和抖动都要增大。

用于触发Marx发生器及高电压脉冲触发装置需要更高的高压触发脉冲,且需在5~30kV范围内连续可调,具有前沿快、延时准确稳定、抖动小、抗干扰能力强等性能。

设计高压脉冲形成级是本机的重点,关键是选择能满足本机各项技术指标要求的高电压、大电流、快速开关管。

为了提高触发系统的延时精度,采用精度为10ns的数字延时单元,延时在10ns~99μs范围,步进10ns,以CPU8031为控制核心的集成电路实现人机对话,增强可靠性和先进性。

直流高压供电采用DC/DC变换技术,封装在金属盒内,实现了电源小型化,增强了抗干扰能力。

2发生器的构成及其工作原理

2.1高压脉冲发生器结构

延时可控高压脉冲发生器结构框图,是由外触发控制电路、单片机控制电路、延时电路、驱动电路、直流高压电路及高压脉冲形成及

输出电路等组成。

图1高压脉冲发生器组成框图

外触发控制电路是将外触发信号通过内部的比较器进行电压比较,再通过光电隔离器使外触发信号的地与控制线路的地分开,以屏蔽和减弱外界的电磁干扰及地干扰,增强本机的抗干扰能力。

单片机控制电路、延时电路是通过单片机实现人机对话,来预置延时电路的延时时间,达到延时可控目的。

驱动电路是将延时电路输出幅度较低的脉冲信号变为较高幅度的脉冲信号,用以驱动后级高压脉冲形成电路。

直流高压电路采用DC/DC变换,低压24V经振荡电路产生频率较高交流信号,再经高频脉冲变压器升压及多级倍压输出5~30kV连续可调的直流高压,为高压脉冲形成电路供电。

高压脉冲形成输出电路是本机重要部分,主要是形成和输出负高压脉冲。

2.2工作原理

由键盘键入所要求的延时时间,通过8031芯片内部程序控制延时器所要求的动作时间。

当外触发信号输入时,外触发控制电路开始工作,输出一个脉冲信号触发延时电路,延时器开始计数,当达到所设定的时间时,延时器停止工作,同时输出一个脉冲信号,触发驱动电路,使驱动电路输出一个正脉冲信号,使开关管S导通,储能电容C经S向负载电阻放电(见图2),从而在与同轴电缆相匹配的负载

上获得与直流高压幅度相同,极性相反的高电压脉冲。

图2高压脉冲形成电路

3电路的设计

3.1高压脉冲形成电路设计

根据指标要求,在负载电阻75Ω上,输出最大幅度Vomax为30kV,前沿tr≤16ns,脉宽T1/2≥300ns的高压脉冲,则选择高压脉冲形成器件是本机设计的重点。

该器件需具有耐压高、电流大、开关速度快、抖动小等特点。

美国EG&G公司生产的GP-12B管,工作电压、电流、前沿均可满足要求,但抖动较大。

国产V型管,耐压达不到要求,且延迟、抖动较大。

国产氢闸流管VE4137A阳极峰值电压33kV,峰值电流1.5kA,前沿≤10ns,抖动≤5ns,是较理想的高压脉冲形成器件。

高压脉冲形成电路。

图中VH为高压脉冲形成电路的直流供电电源,5~30kV,极性为正、连续可调、组件式。

脉宽主要取决于储能电容C的大小,按式(1)

V1/2=Vo(1)

式中:Vo为输出高压脉冲幅度;

V1/2为Vo的50%,即,V1/2=Vo;

T1/2为半高宽,即幅度为V1/2时波形的宽度,取T1/2=0.3×10-6s;

R为负载电阻,75Ω;

C为放电电容。

将数据代入式(1)并整理得:

C==5.8nF

实取C=6.6nF用两只3300pF/35kV陶瓷电容并联。

3.2单片机延时电路设计

仪器的控制核心由CPU8031、大规模集成电路8155和EPROM2732组成。

CPU8031是单片机的核心,它实现人机对话并完成对EPLD(可编程逻辑器件)的初始化和数据装入。

8155用作键盘和显示器接口。

EPROM2732用于存储延时同步单元的全部程序,开机后CPU从EPROM2732中读取指令进行程序控制。

延迟时间的输入,显示以及EPLD器件初始化的完成在CPU8031的控制下进行。

根据仪器指标,要求延时脉冲时间为10ns~99μs,延时精度为10ns,抖动小于10ns。

为了解决通道之间的窜扰,时间精度及传送数据要求高等问题,在线路的设计中选用了Aterla公司的7000系列EPLD,将全部的逻辑电路做在一块器件中。

通过单片机的控制对它进行初始化和数据装入。

当触发信号到来时触发EPLD发出设定的延时信号,经过模拟放大输出以驱动后级电路。

3.3触发电路的设计及对高压回窜干扰的抑制

由于开关管S导通放电时,产生了高电压对触发电路的反窜干扰及空间电磁波的干扰,使触发电路很难正常工作。

根据氢闸流管S导通时反窜到其触发控制极上的电压来设计氢闸流管触发电路,。

图3开关管触发电路

氢闸流管触发电路由触发延时控制、脉冲变压器T、高频阻断硅堆D、π型滤波器(C2、L、C1)、开关管的偏置电阻R2及开关管S等组成。

外触发信号触发光电隔离器,经触发延时控制电路后,输出约400V的脉冲信号,加到脉冲变压器T的初级,经脉冲变压器升压产生1kV以上的脉冲信号,脉宽大于2μs。

经D、L触发S导通后,储能电容C经S向负载电阻R放电,输出负的高压脉冲。

S导通瞬间,在其触发控制端产生约(2/3)Uc的高压脉冲,此信号包含多种频率成分,既有高频,又有中频和低频。

高频干扰信号通过C1小电容旁路和经L大电感来衰减;中频和低频干扰信号则由高压硅堆反向阻断。

这样通过旁路、衰减及阻断后到脉冲变压器T 的次级约为百伏的干扰电压,再经T的降压也就只有几十伏的电压,从而解决了S开关导通反窜到控制电路的干扰。

4性能指标测试

4.1高压脉冲波形

高压脉冲发生器输出高压脉冲波形。

图4高压脉冲发生器输出高压脉冲波形高压脉冲输出经TekP6015A1/1000高压探头衰减,由TDS774A数字示波器测量,测试数据自动读出显示。

由图4可知,

高压脉冲波形光滑无振荡,下降沿15.7ns,脉宽约300ns。

4.2主要技术指标

表1列出了本机及以往研制的同类产品对应的主要技术性能指标,以对二者进行比较。

表1高压脉冲发生器主要性能指标输出高压脉冲Vo/kV相对外触发延时tedl/ns抖动Δt/ns前沿tr/ns可预置延时tp/ns本机5~30400~10101610~99000以往研制同类产品10~152500~5008025——

从表1所列数据可以看出,本机的性能指标先进,较以往研制的同类产品有较大的改进和提高。

1)高压脉冲幅度提高1倍且调节范围宽,在5~30kV连续可调;

2)对不同的高压脉冲相对外触发延时基本固定不变;

3)增加可预置延时功能,延时10ns~99μs,具有较高的精度;

4)抖动是高压脉冲发生器一个重要指标,本机的抖动很小,而以往研制的抖动很大。

5结语

本机输出高压脉冲调节范围宽,从5kV至30kV连续可调,可预置,前沿快、抖动小、延时准确,又增加了可预置延时,从而拓宽了应用范围,提高了测量精度。

可控延时采用了先进技术,应用单片

机,实现了人机对话,操作简便,增加了可靠性,且具有先进性。

高压脉冲形成级采用高压大电流,快前沿、低抖动、长寿命快速氢闸流管,在设计上留有较大余量,确保运行可靠。

采用光耦、变压器隔离、地隔离、多层金属屏蔽等措施,对抑制高压放电产生的电磁干扰以及地电流干扰有明显效果;对高压开关管导通瞬间在触发驱动级产生的多种频率成分的高压回窜强干扰,采用旁路、衰减、阻断等相应的有效方法,保证了触发电路的正常工作。

该机已交付使用,所有技术指标均符合和满足设计规定的指标及使用要求,长期运行工作稳定可靠。