51单片机中断系统程序实例

- 格式:docx

- 大小:107.15 KB

- 文档页数:8

实验五、中断实验

1、实验目的:了解单片机的中断系统,学习汇编语言中断程序的编程方法与调试技巧。

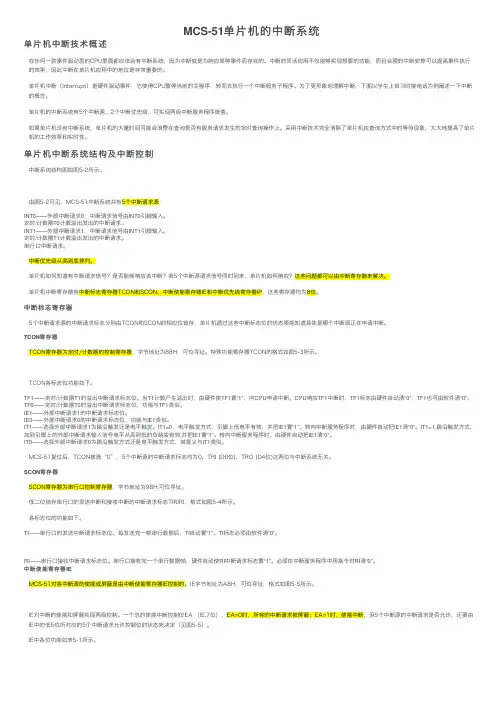

2、实验内容:单片机的INT0和INT1分别接了两个外部中断,当INT0引脚有中断时,点亮发光二极管D1,当INT1引脚有中断时,点亮发光二极管D2。

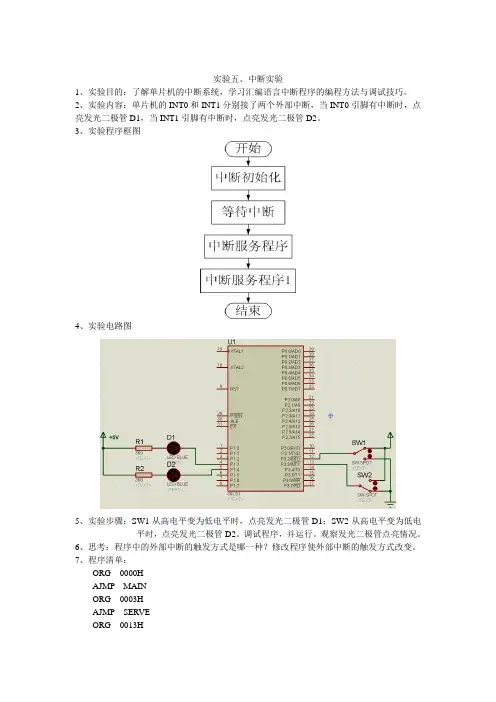

3、实验程序框图

4、实验电路图

5、实验步骤:SW1从高电平变为低电平时,点亮发光二极管D1;SW2从高电平变为低电

平时,点亮发光二极管D2。

调试程序,并运行。

观察发光二极管点亮情况。

6、思考:程序中的外部中断的触发方式是哪一种?修改程序使外部中断的触发方式改变。

7、程序清单:

ORG 0000H

AJMP MAIN

ORG 0003H

AJMP SERVE

ORG 0013H

AJMP SERVE1

MAIN: ORL P1 , #0FFH ;;灯全灭,准备读入SETB IT0; ;选择边沿触发方式

SETB EX0; ;允许INT0中断

SETB IT1; ;选择边沿触发方式SETB EX1; ;允许INT0中断

SETB EA ;;CPU开中断

AJMP $ ;;等待中断

;中断服务子程序为:

SERVE: MOV A,#0F7H

MOV P1,A

RETI

SERVE1: MOV A,#0EFH

MOV P1,A

RETI。

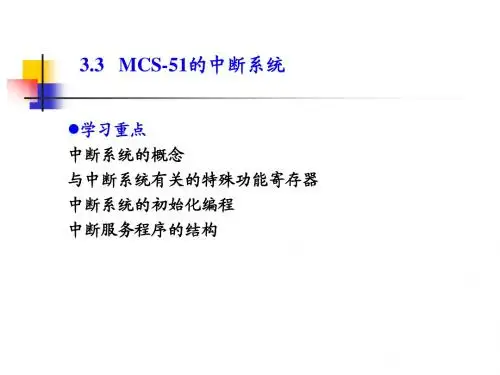

MCS-51单⽚机的中断系统单⽚机中断技术概述在任何⼀款事件驱动型的CPU⾥⾯都应该会有中断系统,因为中断就是为响应某种事件⽽存在的。

中断的灵活应⽤不仅能够实现想要的功能,⽽且合理的中断安排可以提⾼事件执⾏的效率,因此中断在单⽚机应⽤中的地位是⾮常重要的。

单⽚机中断(Interrupt)是硬件驱动事件,它使得CPU暂停当前的主程序,转⽽去执⾏⼀个中断服务⼦程序。

为了更形象地理解中断,下⾯以学⽣上⾃习时接电话为例阐述⼀下中断的概念。

单⽚机的中断系统有5个中断源、2个中断优先级,可实现两级中断服务程序嵌套。

如果单⽚机没有中断系统,单⽚机的⼤量时间可能会浪费在查询是否有服务请求发⽣的定时査询操作上。

采⽤中断技术完全消除了单⽚机在査询⽅式中的等待现象,⼤⼤地提⾼了单⽚机的⼯作效率和实时性。

单⽚机中断系统结构及中断控制中断系统结构图如图5-2所⽰。

由图5-2可见,MCS-51中断系统共有5个中断请求源:INT0——外部中断请求0,中断请求信号由INT0引脚输⼊。

定时/计数器T0计数溢出发出的中断请求。

INT1——外部中断请求1,中断请求信号由INT1引脚输⼊。

定时/计数器T1计数溢出发出的中断请求。

串⾏⼝中断请求。

中断优先级从⾼到底排列。

单⽚机如何知道有中断请求信号?是否能够响应该中断?若5个中断源请求信号同时到来,单⽚机如何响应?这些问题都可以由中断寄存器来解决。

单⽚机中断寄存器有中断标志寄存器TCON和SCON、中断使能寄存器IE和中断优先级寄存器IP,这些寄存器均为8位。

中断标志寄存器5个中断请求源的中断请求标志分别由TCON和SCON的相应位锁存,单⽚机通过这些中断标志位的状态便能知道具体是哪个中断源正在申请中断。

TCON寄存器TCON寄存器为定时/计数器的控制寄存器,字节地址为88H,可位寻址。

特殊功能寄存器TCON的格式如图5-3所⽰。

TCON各标志位功能如下。

TF1——定时/计数器T1的溢出中断请求标志位。

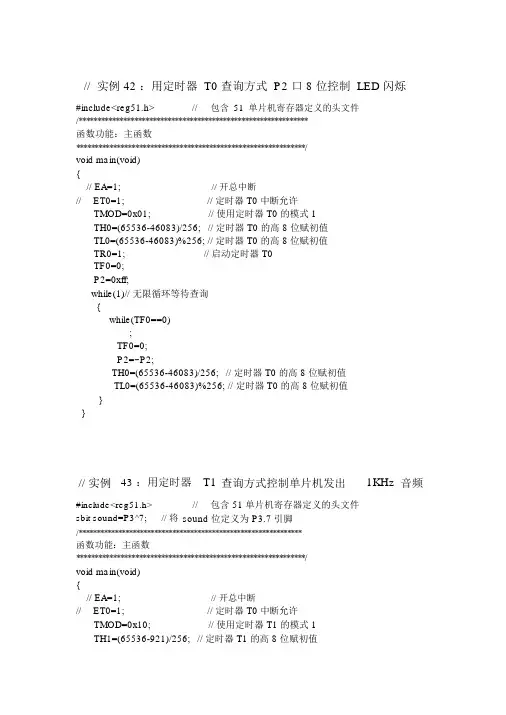

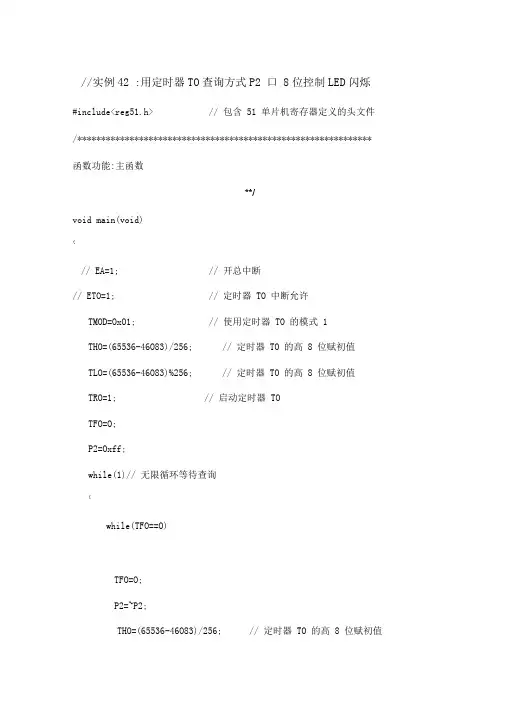

//实例 42 :用定时器 T0 查询方式 P2 口 8 位控制 LED 闪烁#include<reg51.h>//包含51单片机寄存器定义的头文件/**************************************************************函数功能:主函数**************************************************************/void main(void){// EA=1;// 开总中断// ET0=1;// 定时器 T0 中断允许TMOD=0x01;// 使用定时器 T0 的模式 1TH0=(65536-46083)/256; // 定时器 T0 的高 8 位赋初值TL0=(65536-46083)%256; // 定时器 T0 的高 8 位赋初值TR0=1;// 启动定时器 T0TF0=0;P2=0xff;while(1)// 无限循环等待查询{while(TF0==0);TF0=0;P2=~P2;TH0=(65536-46083)/256; // 定时器 T0 的高 8 位赋初值TL0=(65536-46083)%256; // 定时器 T0 的高 8 位赋初值}}// 实例43 :用定时器T1查询方式控制单片机发出1KHz音频#include<reg51.h>sbit sound=P3^7;// 将// 包含 51 单片机寄存器定义的头文件sound 位定义为 P3.7 引脚/**************************************************************函数功能:主函数**************************************************************/ void main(void){// EA=1;// 开总中断// ET0=1;// 定时器 T0 中断允许TMOD=0x10;// 使用定时器 T1 的模式 1 TH1=(65536-921)/256; // 定时器 T1 的高 8 位赋初值TL1=(65536-921)%256; // 定时器 T1 的高 8 位赋初值TR1=1;// 启动定时器 T1TF1=0;while(1)// 无限循环等待查询{while(TF1==0);TF1=0;sound=~sound; // 将 P3.7 引脚输出电平取反TH1=(65536-921)/256; // 定时器 T0 的高 8 位赋初值TL1=(65536-921)%256; // 定时器 T0 的高 8 位赋初值}}//实例 44 :将计数器 T0 计数的结果送 P1 口 8 位 LED 显示#include<reg51.h> // 包含 51 单片机寄存器定义的头文件 sbitS=P3^4; // 将 S位定义为 P3.4 引脚/**************************************************************函数功能:主函数**************************************************************/void main(void){// EA=1;// 开总中断// ET0=1;// 定时器 T0 中断允许2TMOD=0x02;// 使用定时器 T0 的模式TH0=256-156; // 定时器 T0 的高 8 位赋初值TL0=256-156; // 定时器 T0 的高 8 位赋初值TR0=1;// 启动定时器 T0while(1)// 无限循环等待查询{while(TF0==0)// 如果未计满就等待{if(S==0)// 按键S 按下接地,电平为0P1=TL0; //计数器 TL0 加 1 后送 P1 口显示}TF0=0; // 计数器溢出后,将TF0清 0}}//实例 45 :用定时器 T0 的中断控制 1 位 LED 闪烁#include<reg51.h> // 包含 51 单片机寄存器定义的头文件sbit D1=P2^0; // 将 D1 位定义为 P2.0 引脚/**************************************************************函数功能:主函数**************************************************************/void main(void){EA=1;// 开总中断ET0=1;// 定时器 T0 中断允许TMOD=0x01;// 使用定时器 T0 的模式 2TH0=(65536-46083)/256; //定时器 T0 的高 8 位赋初值TL0=(65536-46083)%256; //定时器 T0 的高 8 位赋初值TR0=1;// 启动定时器 T0while(1)// 无限循环等待中断;}/**************************************************************函数功能:定时器T0 的中断服务程序**************************************************************/void Time0(void) interrupt 1 using 0 // “interrupt ”声明函数为中断服务函数// 其后的 1 为定时器 T0 的中断编号; 0 表示使用第 0 组工作寄存器{D1=~D1; // 按位取反操作,将P2.0 引脚输出电平取反TH0=(65536-46083)/256; //定时器 T0 的高 8 位重新赋初值TL0=(65536-46083)%256; //定时器 T0 的高 8 位重新赋初值}//实例 46 :用定时器 T0 的中断实现长时间定时#include<reg51.h> //包含51单片机寄存器定义的头文件sbit D1=P2^0; // 将 D1 位定义为 P2.0 引脚unsigned char Countor; //设置全局变量,储存定时器T0 中断次数/**************************************************************函数功能:主函数**************************************************************/void main(void){EA=1;// 开总中断ET0=1;// 定时器 T0 中断允许TMOD=0x01;// 使用定时器 T0 的模式 2 TH0=(65536-46083)/256; //定时器 T0 的高 8 位赋初值TL0=(65536-46083)%256; //定时器 T0 的高 8 位赋初值TR0=1; Countor=0;// 启动定时器 T0// 从 0 开始累计中断次数while(1)// 无限循环等待中断;}/**************************************************************函数功能:定时器T0 的中断服务程序**************************************************************/void Time0(void) interrupt 1 using 0 // “interrupt ”声明函数为中断服务函数// 其后的 1 为定时器 T0 的中断编号; 0 表示使用第 0 组工作寄存器{Countor++; // 中断次数自加 1if(Countor==20)// 若累计满20 次,即计时满1s{D1=~D1; Countor=0;// 按位取反操作,将P2.0 引脚输出电平取反// 将 Countor 清 0,重新从 0 开始计数}TH0=(65536-46083)/256; //定时器 T0 的高 8 位重新赋初值TL0=(65536-46083)%256; //定时器 T0 的高 8 位重新赋初值}//实例 47 :用定时器 T1 中断控制两个 LED 以不同周期闪烁#include<reg51.h> //包含51单片机寄存器定义的头文件sbit D1=P2^0; // 将 D1 位定义为 P2.0 引脚sbit D2=P2^1; // 将 D2 位定义为 P2.1 引脚unsigned char Countor1; //设置全局变量,储存定时器unsigned char Countor2; //设置全局变量,储存定时器T1 中断次数T1 中断次数/**************************************************************函数功能:主函数**************************************************************/ void main(void){EA=1;// 开总中断ET1=1;// 定时器 T1 中断允许TMOD=0x10;// 使用定时器 T1 的模式 1TH1=(65536-46083)/256; //定时器 T1 的高 8 位赋初值TL1=(65536-46083)%256; //定时器 T1 的高 8 位赋初值TR1=1;// 启动定时器 T1Countor1=0;// 从 0 开始累计中断次数Countor2=0;// 从 0 开始累计中断次数while(1)// 无限循环等待中断;}/**************************************************************函数功能:定时器T1 的中断服务程序**************************************************************/void Time1(void) interrupt 3 using 0 // “interrupt ”声明函数为中断服务函数// 其后的 3 为定时器 T1 的中断编号; 0 表示使用第 0 组工作寄存器{Countor1++; //Countor1 自加 1Countor2++; //Countor2 自加 1if(Countor1==2) // 若累计满 2 次,即计时满{100msD1=~D1; Countor1=0;// 按位取反操作,将P2.0引脚输出电平取反// 将 Countor1 清 0,重新从 0 开始计数}if(Countor2==8) // 若累计满 8 次,即计时满 400ms {D2=~D2; Countor2=0;// 按位取反操作,将P2.1引脚输出电平取反// 将 Countor1 清 0,重新从 0 开始计数}TH1=(65536-46083)/256; //定时器 T1 的高 8 位重新赋初值TL1=(65536-46083)%256; //定时器 T1 的高 8 位重新赋初值}//实例 50-1 :输出 50 个矩形脉冲#include<reg51.h> // 包含 51 单片机寄存器定义的头文件sbit u=P1^4;// 将 u 位定义为 P1.4/*************************************************函数功能:延时约30ms (3*100*100=30 000μs =30m*************************************************/void delay30ms(void){unsigned char m,n;for(m=0;m<100;m++)for(n=0;n<100;n++);}/*******************************************函数功能:主函数******************************************/void main(void){unsigned char i;u=1;// 初始化输出高电平for(i=0;i<50;i++) // 输出 50 个矩形脉冲{u=1;delay30ms();u=0;delay30ms();}while(1);// 无限循环,防止程序“跑飞”}//实例 50-2 :计数器 T0 统计外部脉冲数#include<reg51.h> // 包含 51 单片机寄存器定义的头文件/*******************************************函数功能:主函数******************************************/void main(void){TMOD=0x06;// TMOD=0000 0110B,使用计数器 T0 的模式 2EA=1; ET0=0; TR0=1;// 开总中断// 不使用定时器// 启动 T0T0 的中断TH0=0; TL0=0; while(1)// 计数器 T0 高 8 位赋初值// 计数器 T0 低 8 位赋初值// 无限循环,不停地将TL0 计数结果送P1 口P1=TL0; }//实例 51-2 :定时器 T0 的模式 2 测量正脉冲宽度#include<reg51.h> // 包含 51 单片机寄存器定义的头文件sbit ui=P3^2;// 将 ui 位定义为 P3.0( INT0)引脚,表示输入电压/*******************************************函数功能:主函数******************************************/void main(void){TMOD=0x0a;// TMOD=0000 1010B,使用定时器T0 的模式2, GATE置 1EA=1; ET0=0; TR0=1; TH0=0; TL0=0; while(1)// 开总中断// 不使用定时器 T0 的中断// 启动 T0// 计数器 T0 高 8 位赋初值// 计数器 T0 低 8 位赋初值// 无限循环,不停地将TL0 计数结果送P1 口{while(ui==0)//INT0为低电平,T0 不能启动;TL0=0;//INT0 为高电平,启动T0 计时,所以将while(ui==1) // 在 INT0 高电平期间,等待,计时TL0清;P1=TL0;// 将计时结果送P1 口显示}}//实例 53 :用外中断 0 的中断方式进行数据采集#include<reg51.h> sbit S=P3^2;// 包含 51 单片机寄存器定义的头文件// 将 S位定义为 P3.2,/*******************************************函数功能:主函数******************************************/ void main(void){EA=1; // 开放总中断EX0=1; // 允许使用外中断IT0=1;// 选择负跳变来触发外中断P1=0xff;while(1);// 无限循环,防止程序跑飞}/**************************************************************函数功能:外中断T0 的中断服务程序**************************************************************/void int0(void) interrupt 0 using 0 // 外中断 0 的中断编号为 0{P1=~P1; // 每产生一次中断请求,P1 取反一次。

51单片机的中断系统8031单片机的中断系统简单实用,其基本特点是:有5个固定的可屏蔽中断源,3个在片内,2个在片外,它们在程序存储器中各有固定的中断入口地址,由此进入中断服务程序;5个中断源有两级中断优先级,可形成中断嵌套;2个特殊功能寄存器用于中断控制和条件设置的编程。

中断系统的结构:5个中断源的符号、名称及产生的条件如下。

INT0:外部中断0,由P3.2端口线引入,低电平或下跳沿引起。

INT1:外部中断1,由P3.3端口线引入,低电平或下跳沿引起。

T0:定时器/计数器0中断,由T0计满回零引起。

T1:定时器/计数器l中断,由T1计满回零引起。

TI/RI:串行I/O中断,串行端口完成一帧字符发送/接收后引起。

整个中断系统的结构框图见下图一所示。

由图一可见,外部中断有下跳沿引起和低电平引起的选择;串行中断有发送(TI)相接收(R1)的区别;各个中断源打开与否,受中断自身的允许位和全局允许位的控制,并具有高优先级和低优先级的选择。

中断系统的控制寄存器:中断系统有两个控制寄存器IE和IP,它们分别用来设定各个中断源的打开/关闭和中断优先级。

此外,在TCON中另有4位用于选择引起外部中断的条件并作为标志位。

中断允许寄存器—IEIE在特殊功能寄存器中,字节地址为A8H,位地址(由低位到高位)分别是A8H-AFH。

IE用来打开或关断各中断源的中断请求,基本格式如下图二所示:EA:全局中断允许位。

EA=0,关闭全部中断;EA=1,打开全局中断控制,在此条件下,由各个中断控制位确定相应中断的打开或关闭。

×:无效位。

ES:串行I/O中断允许位。

ES=1,打开串行I/O中断;ES=0,关闭串行I/O中断。

ETl;定时器/计数器1中断允许位。

ETl=1,打开T1中断;ETl=O,关闭T1中断。

EXl:外部中断l中断允许位。

EXl=1,打开INT1;EXl=0,关闭INT1。

ET0:定时器/计数器0中断允许位。

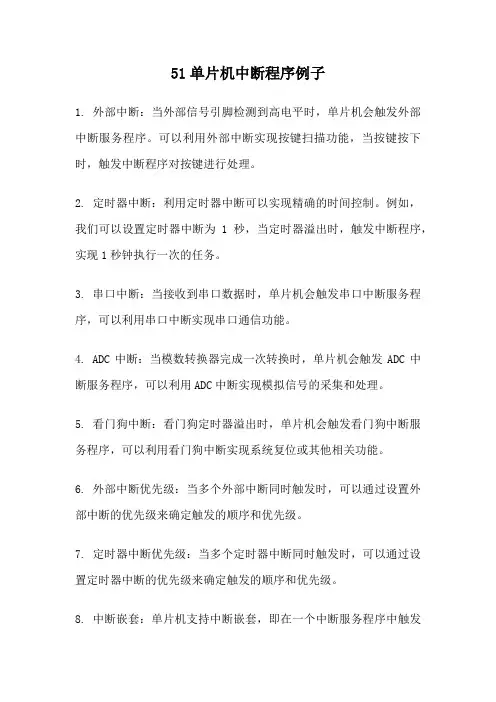

51单片机中断程序例子

1. 外部中断:当外部信号引脚检测到高电平时,单片机会触发外部中断服务程序。

可以利用外部中断实现按键扫描功能,当按键按下时,触发中断程序对按键进行处理。

2. 定时器中断:利用定时器中断可以实现精确的时间控制。

例如,我们可以设置定时器中断为1秒,当定时器溢出时,触发中断程序,实现1秒钟执行一次的任务。

3. 串口中断:当接收到串口数据时,单片机会触发串口中断服务程序,可以利用串口中断实现串口通信功能。

4. ADC中断:当模数转换器完成一次转换时,单片机会触发ADC中断服务程序,可以利用ADC中断实现模拟信号的采集和处理。

5. 看门狗中断:看门狗定时器溢出时,单片机会触发看门狗中断服务程序,可以利用看门狗中断实现系统复位或其他相关功能。

6. 外部中断优先级:当多个外部中断同时触发时,可以通过设置外部中断的优先级来确定触发的顺序和优先级。

7. 定时器中断优先级:当多个定时器中断同时触发时,可以通过设置定时器中断的优先级来确定触发的顺序和优先级。

8. 中断嵌套:单片机支持中断嵌套,即在一个中断服务程序中触发

另一个中断服务程序,可以通过中断嵌套实现复杂的任务处理。

9. 中断屏蔽:单片机支持对中断的屏蔽,即可以通过设置中断屏蔽标志位来屏蔽某些中断,使其暂时不被触发。

10. 中断标志位:单片机提供中断标志位,用于标识中断是否被触发。

在中断服务程序中,可以通过读取和清除中断标志位来判断中断是否发生。

以上是根据51单片机中断程序的例子进行的描述,这些例子涵盖了常见的中断类型和相关功能。

通过学习和理解这些例子,可以更好地掌握51单片机中断编程的原理和方法。

//实例42 :用定时器TO查询方式P2 口8位控制LED闪烁#include<reg51.h> // 包含 51 单片机寄存器定义的头文件/************************************************************** 函数功能:主函数void main(void){// EA=1; // 开总中断// ETO=1; // 定时器 TO 中断允许TMOD=OxO1; // 使用定时器 TO 的模式 1THO=(65536-46O83)/256; // 定时器 TO 的高 8 位赋初值TLO=(65536-46O83)%256; // 定时器 TO 的高 8 位赋初值TRO=1; // 启动定时器 TOTFO=O;P2=Oxff;while(1)// 无限循环等待查询{while(TFO==O)TFO=O;P2=~P2;THO=(65536-46O83)/256; // 定时器 TO 的高 8 位赋初值TL0=(65536-46083)%256; // 定时器 T0 的高 8 位赋初值}// 实例43 :用定时器T1 查询方式控制单片机发出1KHz 音频#include<reg51.h> // 包含 51 单片机寄存器定义的头文件sbit sou nd=P3^7; // 将 sound 位定义为 P3.7 引脚/**************************************************************函数功能:主函数**************************************************************/void main(void){// EA=1; // 开总中断// ET0=1; // 定时器 T0 中断允许TMOD=0x10; // 使用定时器 T1 的模式 1TH1=(65536-921)/256; // 定时器 T1 的高 8 位赋初值TL1=(65536-921)%256; // 定时器 T1 的高 8 位赋初值TR1=1; // 启动定时器 T1TF1=0;while(1)// 无限循环等待查询{while(TF1==0)TF1=0;sound=~sound; // 将 P3.7 引脚输出电平取反TH1=(65536-921)/256; // 定时器 T0 的高 8 位赋初值TL1=(65536-921)%256; // 定时器 T0 的高 8 位赋初值}}// 实例44 :将计数器T0 计数的结果送P1 口8 位LED 显示#include<reg51.h> // 包含 51 单片机寄存器定义的头文件sbit S=P3A4; //将S位定义为P3.4引脚/************************************************************** 函数功能:主函数**************************************************************/void main(void){// EA=1; // 开总中断// ET0=1; // 定时器 T0 中断允许TMOD=0x02; // 使用定时器 T0 的模式 2TH0=256-156; // 定时器 T0 的高 8 位赋初值TL0=256-156; // 定时器 T0 的高 8 位赋初值TR0=1; // 启动定时器 T0while(1)// 无限循环等待查询{while(TF0==0) // 如果未计满就等待{if(S==0) // 按键 S 按下接地,电平为 0P1=TL0; // 计数器 TL0 加 1 后送 P1 口显示}TFO=O; //计数器溢出后,将TFO清0}}// 实例45 :用定时器TO 的中断控制1 位LED 闪烁#include<reg51.h> // 包含 51 单片机寄存器定义的头文件sbit D仁P2A0; //将D1位定义为P2.0引脚/************************************************************** 函数功能:主函数**************************************************************/void main(void)ET0=1; // 定时器 T0 中断允许TMOD=0x01; // 使用定时器 T0 的模式 2TH0=(65536-46083)/256; // 定时器 T0 的高 8 位赋初值TL0=(65536-46083)%256; // 定时器 T0 的高 8 位赋初值TR0=1; // 启动定时器 T0while(1)// 无限循环等待中断J}/**************************************************************函数功能:定时器 T0 的中断服务程序**************************************************************/ void Time0(void) interrupt 1 using 0 // “ interrupt ”声明函数为中断服务函数// 其后的 1 为定时器 T0 的中断编号;0 表示使用第 0 组工作寄存器{D1=~D1; // 按位取反操作,将 P2.0 引脚输出电平取反TH0=(65536-46083)/256; // 定时器 T0 的高 8 位重新赋初值TL0=(65536-46083)%256; // 定时器 T0 的高 8 位重新赋初值}// 实例46 :用定时器T0 的中断实现长时间定时#include<reg51.h> // 包含 51 单片机寄存器定义的头文件sbit D仁P2P; //将D1位定义为P2.0引脚unsigned char Countor; 设置全局变量,储存定时器 T0 中断次数/**************************************************************函数功能:主函数**************************************************************/void main(void){EA=1; // 开总中断ET0=1; // 定时器 T0 中断允许TMOD=0x01; // 使用定时器 T0 的模式 2TH0=(65536-46083)/256; // 定时器 T0 的高 8 位赋初值TL0=(65536-46083)%256; // 定时器 T0 的高 8 位赋初值TR0=1; // 启动定时器 T0Countor=0; //从0开始累计中断次数while(1)// 无限循环等待中断J}函数功能:定时器 T0 的中断服务程序void Time0(void) interrupt 1 using 0 // “ interrupt ”声明函数为中断服务函数// 其后的 1 为定时器 T0 的中断编号;0 表示使用第 0 组工作寄存器{Countor++; // 中断次数自加 1if(Countor==20) // 若累计满 20 次,即计时满 1s{D1=~D1; // 按位取反操作,将 P2.0 引脚输出电平取反Countor=0; // 将 Countor 清 0 ,重新从 0 开始计数}TH0=(65536-46083)/256; // 定时器 T0 的高 8 位重新赋初值TL0=(65536-46083)%256; // 定时器 T0 的高 8 位重新赋初值}// 实例47 :用定时器T1 中断控制两个LED 以不同周期闪烁#include<reg51.h> // 包含 51 单片机寄存器定义的头文件sbit D仁P2P; //将D1位定义为P2.0引脚sbit D2=P2A1; //将D2位定义为P2.1引脚unsigned char Countor1; // 设置全局变量,储存定时器 T1 中断次数unsigned char Countor2; // 设置全局变量,储存定时器 T1 中断次数函数功能:主函数void main(void){EA=1; // 开总中断ET1=1; // 定时器 T1 中断允许TMOD=0x10; // 使用定时器 T1 的模式 1TH1=(65536-46083)/256; // 定时器 T1 的高 8 位赋初值TL1=(65536-46083)%256; // 定时器 T1 的高 8 位赋初值TR1=1; // 启动定时器 T1Countor1=0; // 从0 开始累计中断次数Countor2=0; // 从0 开始累计中断次数while(1)// 无限循环等待中断}函数功能:定时器 T1 的中断服务程序**************************************************************/void Time1(void) interrupt 3 using 0 // “ interrupt ”声明函数为中断服务函// 其后的 3 为定时器 T1 的中断编号;0 表示使用第 0 组工作寄存器g =30m {Countor1++;//Countor1 自加 1 Countor2++; //Countor2 自加 1if(Countor1==2) // 若累计满 2 次,即计时满 100ms{D1=~D1; // 按位取反操作,将 P2.0 引脚输出电平取反Countor1=0; // 将 Countor1 清 0 ,重新从 0 开始计数 }if(Countor2==8) // 若累计满 8 次,即计时满 400ms{D2=~D2; // 按位取反操作,将 P2.1 引脚输出电平取反Countor2=0; // 将 Countor1 清 0 ,重新从 0 开始计数 }TH1=(65536-46083)/256; // 定时器 T1 的高 8 位重新赋初值 TL1=(65536-46083)%256; // 定时器 T1 的高 8 位重新赋初值 }// 实例 50-1 :输出 50 个矩形脉冲#include<reg51.h> // 包含 51 单片机寄存器定义的头文件 sbit u=P1A 4; // 将 u 位定义为 P1.4***********************************************函数功能:延时约 30ms (3*100*100=30 000*************************************************/ void delay30ms(void) {unsigned char m,n;for(m=0;m<100;m++)for(n=0;n<100;n++)J}/*******************************************函数功能:主函数******************************************/void main(void){unsigned char i;u=1; // 初始化输出高电平for(i=0;i<50;i++) // 输出 50 个矩形脉冲{u=1;delay30ms();u=0;delay30ms();while(1); // 无限循环,防止程序“跑飞”}// 实例50-2 :计数器T0 统计外部脉冲数#include<reg51.h> // 包含 51 单片机寄存器定义的头文件/*******************************************函数功能:主函数******************************************/ void main(void) {TMOD=0x06; // TMOD=0000 0110B, 使用计数器 T0 的模式 2 EA=1; // 开总中断ET0=0; // 不使用定时器 T0 的中断TR0=1; // 启动 T0TH0=0; // 计数器 T0 高 8 位赋初值TL0=0; // 计数器 T0 低 8 位赋初值while(1) // 无限循环,不停地将 TL0 计数结果送 P1 口P1=TL0;// 实例51-2 :定时器T0 的模式2 测量正脉冲宽度#include<reg51.h> // 包含 51 单片机寄存器定义的头文件sbit ui=P3A2; //将ui位定义为P3.0 (INTO )引脚,表示输入电压/*******************************************函数功能:主函数******************************************/ void main(void) {TMOD=0x0a; // TMOD=0000 1010B, 使用定时器 TO 的模式 2 , GATE 置1EA=1; //开总中断ET0=0; // 不使用定时器 T0 的中断TR0=1; // 启动 T0TH0=0; // 计数器 T0 高8 位赋初值TL0=0; // 计数器 T0 低8 位赋初值while(1) //无限循环,不停地将TL0计数结果送P1 口{while(ui==0) //INT0为低电平,T0不能启动TL0=0; //INT0 为高电平,启动 T0 计时,所以将 TL0 清 0 while(ui==1)// 在 INT0 高电平期间,等待,计时JP1=TL0; // 将计时结果送 P1 口显示}}// 实例53 :用外中断0 的中断方式进行数据采集#include<reg51.h> // 包含 51 单片机寄存器定义的头文件sbit S=P3A2; // 将 S 位定义为 P3.2 ,/*******************************************函数功能:主函数******************************************/void main(void){EA=1; // 开放总中断EX0=1;// 允许使用外中断IT0=1; // 选择负跳变来触发外中断P1=0xff;while(1); // 无限循环,防止程序跑飞函数功能:外中断 T0 的中断服务程序**************************************************************/ void int0(void) interrupt 0 using 0 // 外中断 0 的中断编号为 0 {P1=~P1; // 每产生一次中断请求, P1 取反一次。

单片机中断系统详细教程一、中断系统的原理中断系统是一种异步事件响应机制,它允许设备在正常程序运行的过程中插入一个特殊事件,中断请求触发后,处理器即刻中断当前程序的执行,执行特定的中断服务程序,完成对事件的处理。

其流程如下:1.当外设需要处理器响应时,会向处理器发送中断请求信号,通常为一个引脚的高电平触发。

2.处理器在接收到中断请求信号后,暂停当前的程序执行,保存当前现场(保存中断发生时的CPU状态),并进入中断服务程序执行,执行完成后再返回到原来的程序继续执行。

二、中断系统的使用方法1.初始化中断控制器:对中断向量表进行初始化,设置中断优先级等。

2.配置外设的中断请求触发方式:设置外设的中断触发方式,包括电平触发和边沿触发。

3.编写中断服务程序:根据需要,编写中断服务程序来处理中断事件。

4.启动中断系统:启动中断系统,使处理器能够响应外设的中断请求。

三、中断系统的实例下面以8051单片机为例,演示如何使用中断系统。

1.初始化中断控制器使用8051单片机的中断系统,首先需要初始化中断控制器,设置中断向量表和中断优先级。

具体步骤如下:```cvoid init_interrup//设置中断向量表EA=1;//打开总中断使能ET0=1;//打开定时器0中断EX0=1;//打开外部中断0EX1=1;//打开外部中断1//设置中断优先级IP=0x10;//设置定时器0中断为高优先级P3=0x0F;//设置外部中断0和中断1为低优先级```2.配置外设的中断请求触发方式在8051单片机中,外部中断0和中断1的触发方式可由用户进行配置,可以选择为低电平触发或上升沿触发。

例如,将外部中断0配置为上升沿触发:```cvoid init_external_interrupIT0=1;//设置外部中断0为边沿触发方式(上升沿触发)EX0=1;//打开外部中断0使能```3.编写中断服务程序根据需要,编写相应的中断服务程序来处理中断事件。

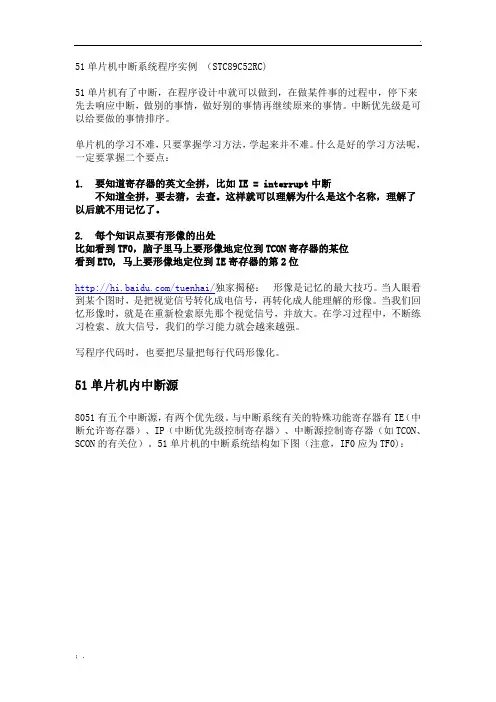

51单片机中断系统程序实例(STC89C52RC)51单片机有了中断,在程序设计中就可以做到,在做某件事的过程中,停下来先去响应中断,做别的事情,做好别的事情再继续原来的事情。

中断优先级是可以给要做的事情排序。

单片机的学习不难,只要掌握学习方法,学起来并不难。

什么是好的学习方法呢,一定要掌握二个要点:1. 要知道寄存器的英文全拼,比如IE = interrupt中断不知道全拼,要去猜,去查。

这样就可以理解为什么是这个名称,理解了以后就不用记忆了。

2. 每个知识点要有形像的出处比如看到TF0,脑子里马上要形像地定位到TCON寄存器的某位看到ET0, 马上要形像地定位到IE寄存器的第2位/tuenhai/独家揭秘:形像是记忆的最大技巧。

当人眼看到某个图时,是把视觉信号转化成电信号,再转化成人能理解的形像。

当我们回忆形像时,就是在重新检索原先那个视觉信号,并放大。

在学习过程中,不断练习检索、放大信号,我们的学习能力就会越来越强。

写程序代码时,也要把尽量把每行代码形像化。

51单片机内中断源8051有五个中断源,有两个优先级。

与中断系统有关的特殊功能寄存器有IE(中断允许寄存器)、IP(中断优先级控制寄存器)、中断源控制寄存器(如TCON、SCON的有关位)。

51单片机的中断系统结构如下图(注意,IF0应为TF0):8052有6个中断源,它比8051多一个定时器/计数器T2中断源。

8051五个中断源分别是:(1)51单片机外部中断源8051有两个外部中断源,分别是INT0和INT1,分别从P3.2和P3.3两个引脚引入中断请求信号,两个中断源的中断触发允许由TCON的低4位控制,TCON的高4位控制运行和溢出标志。

INT0也就是Interrupt 0。

在这里应该看一下你的51单片机开发板的电路原理图。

离开形像的记忆是没有意义的。

读到上面这句,你应该回忆起原理图上的连接。

任何记忆都转化为形像,这是学习的根本原理,我们通过学习单片机要学会这种学习方法,会让你一辈子受益无穷。

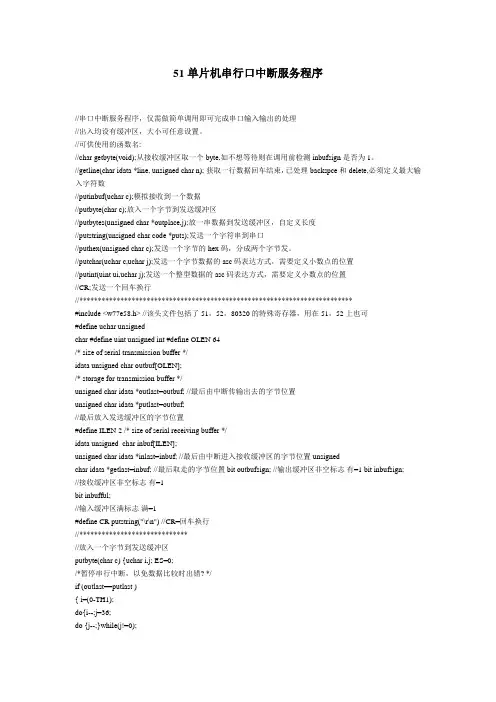

51单片机串行口中断服务程序//串口中断服务程序,仅需做简单调用即可完成串口输入输出的处理//出入均设有缓冲区,大小可任意设置。

//可供使用的函数名://char getbyte(void);从接收缓冲区取一个byte,如不想等待则在调用前检测inbufsign是否为1。

//getline(char idata *line, unsigned char n); 获取一行数据回车结束,已处理backspce和delete,必须定义最大输入字符数//putinbuf(uchar c);模拟接收到一个数据//putbyte(char c);放入一个字节到发送缓冲区//putbytes(unsigned char *outplace,j);放一串数据到发送缓冲区,自定义长度//putstring(unsigned char code *puts);发送一个字符串到串口//puthex(unsigned char c);发送一个字节的hex码,分成两个字节发。

//putchar(uchar c,uchar j);发送一个字节数据的asc码表达方式,需要定义小数点的位置//putint(uint ui,uchar j);发送一个整型数据的asc码表达方式,需要定义小数点的位置//CR;发送一个回车换行//*************************************************************************#include <w77e58.h> //该头文件包括了51,52,80320的特殊寄存器,用在51,52上也可#define uchar unsignedchar #define uint unsigned int #define OLEN 64/* size of serial transmission buffer */idata unsigned char outbuf[OLEN];/* storage for transmission buffer */unsigned char idata *outlast=outbuf; //最后由中断传输出去的字节位置unsigned char idata *putlast=outbuf;//最后放入发送缓冲区的字节位置#define ILEN 2 /* size of serial receiving buffer */idata unsigned char inbuf[ILEN];unsigned char idata *inlast=inbuf; //最后由中断进入接收缓冲区的字节位置 unsignedchar idata *getlast=inbuf; //最后取走的字节位置 bit outbufsign; //输出缓冲区非空标志有=1 bit inbufsign;//接收缓冲区非空标志有=1bit inbufful;//输入缓冲区满标志满=1#define CR putstring("\r\n") //CR=回车换行//*****************************//放入一个字节到发送缓冲区putbyte(char c) {uchar i,j; ES=0;/*暂停串行中断,以免数据比较时出错? */if (outlast==putlast ){ i=(0-TH1);do{i--;j=36;do {j--;}while(j!=0);}while(i!=0);//延时一个字节发送时间}*putlast=c; //放字节进入缓冲区putlast++; //发送缓冲区指针加一 if(putlast==outbuf+OLEN) putlast=outbuf; //指针到了顶部换到底部if (!outbufsign){outbufsign=1;TI=1;} //缓冲区开始为空置为有,启动发送ES=1; }//****************************** //放一串数据到发送缓冲区putbytes(unsigned char *outplace,unsigned char j){ int i; for(i=0;i<j;i++){putbyte(*outplace);outplace++;}}//******************************//putchar(uchar c,uchar j);发送一个字节数据的asc码表达方式,需要定义小数点的位置putchar(uchar c,uchar j){uchar idata free[4];uchar data i;i=0;free[i++]=(c/100+0x30);if (j==3) free[i++]=‘.‘;free[i++]=(c%100)/10+0x30;if (j==2) free[i++]=‘.‘;if (j==2 && free[i-3]==0x30) free[i-3]=0x20;free[i++]=(c%10)+0x30;if (j==1 && free[i-3]==0x30) free[i-3]=0x20;if (j==1 && free[i-3]==0x20 && free[i-2]==0x30) free[i-2]=0x20;putbytes(free,i);}//******************************//putint(uint ui,uchar j);发送一个整型数据的asc码表达方式,需要定义小数点的位置putint(uint ui,uchar j){uchar idata free[6];uchar data i;//i=0;free[i++]=(ui/10000+0x30);if (j==5) free[i++]=‘.‘;free[i++]=((ui%10000)/1000+0x30);if (j==4) free[i++]=‘.‘;if (j==4 && free[i-3]==0x30) free[i-3]=0x20;free[i++]=((ui%1000)/100+0x30);if (j==3) free[i++]=‘.‘;if (j==3 && free[i-4]==0x30) free[i-4]=0x20;if (j==3 && free[i-4]==0x20 && free[i-3]==0x30) free[i-3]=0x20;free[i++]=((ui%100)/10+0x30);if (j==2) free[i++]=‘.‘;if (j==2 && free[i-5]==0x30) free[i-5]=0x20;if (j==2 && free[i-5]==0x20 && free[i-4]==0x30) free[i-4]=0x20;if (j==2 && free[i-5]==0x20 && free[i-4]==0x20 && free[i-3]==0x30) free[i-3]=0x20;free[i++]=(ui%10+0x30);if (j==1 && free[i-5]==0x30) free[i-5]=0x20;if (j==1 && free[i-5]==0x20 && free[i-4]==0x30) free[i-4]=0x20;if (j==1 && free[i-5]==0x20 && free[i-4]==0x20 && free[i-3]==0x30) free[i-3]=0x20;if (j==1 && free[i-5]==0x20 && free[i-4]==0x20 && free[i-3]==0x20 && free[i-2]==0x30) free[i-2]=0x20; putbytes(free,i);}//***************************************//发送一个字符串到串口putstring(unsigned char *puts){for (;*puts!=0;puts++) //遇到停止符0结束putbyte(*puts);}//*************************************//发送一个字节的hex码,分成两个字节发。

实验二外部中断实验实验报告

一、实验内容

单片机外部中断0(P3.2)已与独立式键盘中KEY0连接,外部中断1(P3.3)已与KEY1连接,要求在无外部中断时最上面一位发光二极管(LED10)点亮。

请编程实现:当KEY0按下,外部中断0请求中断,控制发光二极管从上到下循环点亮3圈;当KEY1按下,外部中断1请求中断,控制发光二极管闪烁3次。

(要求外部中断1优先级高于外部中断0,即KEY1按下后能够打断流水灯的动作,当外中断1处理完后,恢复外中断0的处理,并且能从上次打断的那个LED开始循环)。

单片机与发光二极管的连接如图2-1所示,独立式键盘原理图如图2-2所示。

图2-1 单片机与发光二极管的连接原理图

2-2 独立式键盘原理图

三、硬件电路分析

1、阅读电路2-1简要分析如何使发光二极管点亮?

当LEDS0 为高电平时,三极管Q6导通,发光二极管的阳极为高电平,此时,当给发光二极管的阴极为低电平时,发光二极管两端存在电位差,发光二极管导通,则发光二极管点亮。

2、简要画出独立式按键电路(一个键),并分析其如何工作?

如图所示,当按键按下时,单片机IO处会由高电平变为低电平,单片机IO口在经过消抖处理之后仍然检测为低电平,则表明按键被按下。

四、程序设计

画出主程序流程图:

画出外部中断0流程图;

五、思考题

六、收获和体会。

51单片机中断程序例子1. 外部中断程序:外部中断是指由外部设备或外部信号触发的中断。

在51单片机中,通过设置中断允许位和中断优先级来实现对外部中断的响应。

例如,当外部设备发出一个信号时,单片机可以立即停止当前任务,转而执行外部中断程序。

外部中断程序的编写需要根据具体的外部设备和信号进行相应的处理,如读取设备状态、处理数据等。

通过外部中断程序,可以实现单片机与外部设备的互动和数据交换。

2. 定时器中断程序:定时器中断是指通过设置定时器的计数值和中断允许位,使得在指定的时间间隔内触发中断。

在51单片机中,可以通过定时器中断来实现定时任务的执行。

例如,可以设置一个定时器,在每隔一定的时间就触发中断,然后在中断程序中执行相应的任务,如数据采集、数据处理等。

通过定时器中断程序,可以实现定时任务的自动执行,提高系统的实时性和可靠性。

3.串口中断程序:串口中断是指通过串口通信接口接收或发送数据时触发的中断。

在51单片机中,可以通过设置串口中断允许位和中断优先级来实现对串口数据的中断处理。

例如,当接收到一个完整的数据包时,单片机可以立即停止当前任务,转而执行串口中断程序,对接收到的数据进行处理。

通过串口中断程序,可以实现单片机与外部设备的数据交换和通信。

4. ADC中断程序:ADC(模数转换器)中断是指在进行模数转换时触发的中断。

在51单片机中,可以通过设置ADC中断允许位和中断优先级来实现对模数转换结果的中断处理。

例如,当模数转换完成后,单片机可以立即停止当前任务,转而执行ADC中断程序,对转换结果进行处理和分析。

通过ADC中断程序,可以实现对模拟信号的采集和处理,用于实时监测和控制。

5. 外部中断优先级设置:在51单片机中,可以通过设置外部中断的中断优先级来确定中断的响应顺序。

中断优先级越高,优先级越高的中断会先被响应。

通过合理设置中断优先级,可以确保关键任务的及时响应和执行。

例如,当多个外部设备同时发出中断信号时,可以通过设置优先级,确保先响应优先级高的设备,保证系统的正常运行。

51单片机串行口中断服务程序单片机串行口中断服务程序是指在单片机进行串行通信时,当接收到数据时会触发中断,然后执行相应的中断服务程序。

下面是一个示例的单片机串行口中断服务程序,共计1200字以上。

#include <reg51.h> // 引入reg51.h头文件//定义串行口中断标志sbit RI_FLAG = P3^0; // 数据接收中断标志sbit TI_FLAG = P3^1; // 数据发送中断标志//定义串行口接收数据缓冲区unsigned char receiveBuffer[10];unsigned char receiveCount = 0;//定义串行口发送数据缓冲区unsigned char sendBuffer[10];unsigned char sendCount = 0;//串行口中断服务函数void serialInterrupt( interrupt 4if(RI_FLAG) // 判断是否是数据接收中断receiveBuffer[receiveCount] = SBUF; // 读取串行口接收数据receiveCount++; // 接收计数加1RI_FLAG=0;//清除中断标志位}if(TI_FLAG) // 判断是否是数据发送中断if(sendCount < 10) // 判断是否还有数据需要发送SBUF = sendBuffer[sendCount]; // 发送串行口数据sendCount++; // 发送计数加1}elsesendCount = 0; // 重置发送计数TI_FLAG=0;//清除中断标志位}}//主函数void mainES=1;//允许串行口中断TMOD=0x20;//设置定时器1为模式2,串行口使用定时器1 TH1=0xFD;//设置波特率为9600,定时器初值为0xFDTL1=0xFD;//定时器初值为0xFDSCON=0x50;//设置串行口工作在方式1,允许接收TR1=1;//启动定时器1while(1)//主程序逻辑//将数据存入发送缓冲区sendBuffer[0] = 'H';sendBuffer[1] = 'e';sendBuffer[2] = 'l';sendBuffer[3] = 'l';sendBuffer[4] = 'o';sendBuffer[5] = '\r'; // 发送回车符sendBuffer[6] = '\n'; // 发送换行符while(sendCount != 0) //等待数据发送完毕//主程序逻辑}}。

单片机定时器中断程序实例在单片机编程中,定时器是一种非常重要的功能模块。

它可以用来产生精确的时间延迟,实现定时触发事件等功能。

而定时器中断则是利用定时器来实现中断功能的一种方式。

下面是一个单片机定时器中断程序实例,供大家参考。

首先,我们需要初始化定时器。

以51单片机为例,定时器的初始化函数如下所示:void Init_Timer0(void){TMOD |= 0x01; //设置为模式1TH0 = (65536 - 50000) / 256; //设置初值TL0 = (65536 - 50000) % 256;EA = 1; //打开总中断ET0 = 1; //打开定时器0中断TR0 = 1; //启动定时器0}其中,TMOD寄存器用于设置定时器的工作模式。

这里设置为模式1,即16位定时器模式。

TH0和TL0寄存器则是定时器的计数器。

我们需要通过初值来设置定时时间。

在这个例子中,我们设置的定时时间为50ms。

接下来,我们需要编写定时器中断服务程序。

定时器中断服务程序是由中断向量表中的相应位置调用的,用于响应定时器中断。

在这个例子中,我们将定时器中断服务程序命名为Timer0_isr,定义如下:void Timer0_isr(void) interrupt 1{TH0 = (65536 - 50000) / 256;TL0 = (65536 - 50000) % 256;//定时器中断处理代码}在定时器中断服务程序中,我们需要重新设置计数器的初值,以实现定时器的循环工作。

同时,在这个例子中,我们需要在定时器中断处理代码中实现某些功能,例如周期性的输出一个信号、更新某个计数值等等。

最后,在主程序中,我们只需要调用Init_Timer0函数即可开始定时器的工作。

当定时器中断发生时,定时器中断服务程序会被自动调用。

这样,我们就实现了一个简单的单片机定时器中断程序。

51单片机内部定时器和中断系统以及编写第一个简单的定时器实验程序上讲通过讲述用单片机控制一个外部的LED闪烁实验来向读者介绍了单片机的工作原理与开发流程。

这一讲将介绍单片机内部非常重要的两个资源——定时/ 计数器和中断系统。

通过该讲,读者可以掌握定时器的工作原理和单片机的中断系统。

从而设计定时器计数程序和中断服务程序。

一、原理简介首先让我们举闹钟为例,将它定时在一分钟后闹铃,这就需要秒针走一圈(60 次)。

即一分钟时间转化为秒针走的次数,也就是计数的次数,计数到了60 次然后闹铃,而每一次计数的时间是1 秒。

单片机内部的定时/ 计数器跟闹钟类似,可以通过编程来设定要定时的时间、定时时间到了进行相应的操作。

那么在单片机内部计数一次的时间是多少呢,51 单片机输入的时钟脉冲是由晶体振荡器的输出经12 分频后得到的,所以定时器也可看作是对计算机机器周期的计数器。

因为每个机器周期包含12 个振荡周期,故每一个机器周期定时器加1,可以把输入的时钟脉冲看成机器周期信号。

故其频率为晶振频率的1/12。

如果晶振频率为12MHz,则定时器每接收一个输入脉冲的时间刚好为1μs。

在本实验套件中采用的是11.0592M 的晶振,故每接收一个输入脉冲的时间约为1.085μs。

实现精确定时在实际项目应用中非常重要,因为往往需要用到精确定时一段时间,然后定时时间到的时刻做相应的任务。

那如何编程实现定时时间呢?首先先简单介绍下本实验板上单片机(STC89C52)内的定时器资源。

STC89C52 内有三个定时/ 计数器,分别为T0、T1 和T2。

其中T0、T1 工作方式一样,一并介绍。

T2 的工作方式稍有区别,这里不做介绍,实验套件光盘中有实际应用程序。

同时,单片机中的定时器和计数器是复用的,计数器是记录外部脉冲的个数,而定时器则是由单片机内部时钟提供的一个非常稳定的计数源。

本讲中,以T0、T1 作为定时器来进行实例介绍使用。

单片机串口通信在嵌入式系统中具有非常重要的作用,而其中串口中断的编写方式更是至关重要。

今天我们来讨论一下51单片机串口中断的两种写法。

1. 外部中断写法在51单片机中,串口通信一般使用串口中断来实现。

外部中断写法是一种常见的串口中断编写方式。

其具体步骤如下:1)需要设置串口工作参数,包括波特率、数据位、停止位和校验位等。

2)在主程序中使能串口中断,并设置中断优先级。

3)在中断服务函数中进行接收数据的处理,可以通过接收缓冲区、中断标志位等来判断接收数据的情况,并进行相应的处理。

2. 定时器中断写法除了外部中断写法,定时器中断也是一种常见的串口中断编写方式。

其具体步骤如下:1)同样需要设置串口工作参数,包括波特率、数据位、停止位和校验位等。

2)在主程序中初始化定时器,并使能定时器中断。

3)在定时器中断服务函数中进行接收数据的处理,同样可以通过接收缓冲区、中断标志位等来判断接收数据的情况,并进行相应的处理。

总结无论是外部中断写法还是定时器中断写法,都是实现51单片机串口通信的常见方式。

在选择具体的编写方式时,需要根据具体的应用场景和需求来进行选择。

在实际应用中,可以根据具体情况来灵活选择合适的串口中断编写方式,以便更好地满足系统的需求。

在实际编写中断服务函数时,需要注意以下几点:1)处理数据时需要考虑数据的完整性和准确性,可以通过校验位等手段来验证数据的正确性。

2)在中断服务函数中应尽量减少对全局变量的访问,以避免出现数据冲突和竞争的情况。

3)合理设置中断优先级,避免产生中断嵌套和冲突。

通过合理的中断编写方式和注意事项,可以更好地实现串口通信功能,提高系统的稳定性和可靠性,为嵌入式系统的应用提供良好的技术支持。

对于外部中断写法和定时器中断写法,两者各有优缺点。

外部中断写法在串口数据到达时能够即刻响应中断、处理数据。

但是,如果数据传输速率较快或需要高精度的数据处理,外部中断写法可能无法满足要求。

在这种情况下,定时器中断写法显得更加合适。

51单片机中断系统程序实例(STC89C52RC)51单片机有了中断,在程序设计中就可以做到,在做某件事的过程中,停下来先去响应中断,做别的事情,做好别的事情再继续原来的事情。

中断优先级是可以给要做的事情排序。

单片机的学习不难,只要掌握学习方法,学起来并不难。

什么是好的学习方法呢,一定要掌握二个要点:1. 要知道寄存器的英文全拼,比如IE = interrupt中断不知道全拼,要去猜,去查。

这样就可以理解为什么是这个名称,理解了以后就不用记忆了。

2. 每个知识点要有形像的出处比如看到TF0,脑子里马上要形像地定位到TCON寄存器的某位看到ET0, 马上要形像地定位到IE寄存器的第2位/tuenhai/独家揭秘:形像是记忆的最大技巧。

当人眼看到某个图时,是把视觉信号转化成电信号,再转化成人能理解的形像。

当我们回忆形像时,就是在重新检索原先那个视觉信号,并放大。

在学习过程中,不断练习检索、放大信号,我们的学习能力就会越来越强。

写程序代码时,也要把尽量把每行代码形像化。

51单片机内中断源8051有五个中断源,有两个优先级。

与中断系统有关的特殊功能寄存器有IE(中断允许寄存器)、IP(中断优先级控制寄存器)、中断源控制寄存器(如TCON、SCON的有关位)。

51单片机的中断系统结构如下图(注意,IF0应为TF0):8052有6个中断源,它比8051多一个定时器/计数器T2中断源。

8051五个中断源分别是:(1)51单片机外部中断源8051有两个外部中断源,分别是INT0和INT1,分别从P3.2和P3.3两个引脚引入中断请求信号,两个中断源的中断触发允许由TCON的低4位控制,TCON的高4位控制运行和溢出标志。

INT0也就是Interrupt 0。

在这里应该看一下你的51单片机开发板的电路原理图。

离开形像的记忆是没有意义的。

读到上面这句,你应该回忆起原理图上的连接。

任何记忆都转化为形像,这是学习的根本原理,我们通过学习单片机要学会这种学习方法,会让你一辈子受益无穷。

TCON的结构如下图:(a)定时器T0的运行控制位TR0TR0由软件置位或者清0。

当门控位GATE=0时,TO计数器仅由TR0控制,TR0=1启动计数,TR0=0时停止。

当门控位GATE=1时,T0计数器由INT0和TR0共同控制,当INT0=1且TR0=1时启动T0计数器。

(b)定时器T0溢出标志位TF0当T0溢出时TF0=1,并向CPU申请中断,CPU响应中断后由硬件将TF0清0,也可以由软件查询方式将TF0清0。

c)定时器T1的运行控制位TR1功能同TR0。

(d)定时器T1溢出标志为TF1功能同TF1。

(e)外部中断源1(INT1、P3.3)中断请求标志IE1IE1=1时外部中断源1正在向CPU请求中断,当CPU响应该中断时由硬件将IE1清0(下降沿触发方式)。

(f)外部中断源1触发方式选择位IT1IT1=0时外部中断源1选择电平触发方式,当输入低电平时置位IE1;IT1=1时外部中断源1选择下降沿触发方式,当中断源由高电平变低电平时置位 IE1,向CPU请求中断。

(g)外部中断源0(INT0、P3.2)中断请求标志IE0功能类同IE1。

(h)外部中断源0触发方式选择位IT0功能类同IT1。

CPU在每个机器周期采样INT0和INT1引脚的输入电平。

i、电平触发方式当CPU采样到低电平时,置位IE0和IE1,采样到高电平时,将IE0和IE1清零。

在电平触发方式下,外部中断源必须一直保持低电平(至少保持1个以上的机器周期)直到CPU响应中断请求,否则中断请求将丢失,同时在中断处理程序结束之前必须,外部中断源必须变为高电平,否则将产生另一次中断。

ii、下降沿触发方式CPU每个机器周期采样中断输入引脚,如果相续的两次采样,第一次是高电平,第二次是低电平,则置位相应的IE,响应中断后,硬件自动将IE清0。

采样下降沿触发方式,中断源的高、低电平都必须保持12个振荡周期(即1个机器周期)以上,这样CPU才能有效检测到下降沿,并引发CPU中断。

(2)51单片机内部中断源8051有3个内部中断源,分别是定时器T0、T1和串行口中断。

8052增加了一个T2定时器中断。

2、51单片机中断使能控制中断的允许和禁止由中断使能控制寄存器IE控制,其字节地址为0A8H,可以位寻址,其结构如下图所示:EX0:外部中断0中断允许位;ET0:定时器/计数器T0中断允许位;EX1:外部中断1中断允许位;ET1:定时器/计数器T1中断允许位;ES:串行口中断允许位;ET2:定时器/计数器T2中断允许位;(只要8052具有)EA:CPU中断总允许位,EA=1时所有的中断开放,EA=0时禁止所有的中断。

3、51单片机中断优先级51有两个优先级:高、低。

通过IP(中断优先级寄存器)来设置优先级,其字节地址为0B8H,可位寻址,其结构如下图:IP中各位值为0时表示低优先级中断,为1时表示高优先级中断。

CPU复位后IP=0。

高优先级中断可以中断低优先级中断,同优先级中断不能相互中断。

当CPU同时接到同优先级的几个中断请求时,CPU按照如下硬件顺序进行中断响应:4、51单片机中断请求的撤除CPU响应中断请求,执行中断服务程序,但在中断返回指令(RETI)之前必须撤除中断信号,否则将可能再次引起中断而发生错误。

中断请求撤销的方法有三种:a、单片机内部硬件自动复位:对于定时器/计数器T0、T1及采用边沿触发方式的外部中断请求,CPU在响应中断后,由内部硬件自动撤销中断请求;b、应用软件清除响应标志:对串口发送/接收中断请求及定时器T2的溢出和捕获中断请求,CPU响应中断后,内部无硬件自动复位RI、TI、TF2及EXF2,必须在中断服务程序中清除这些标志,才能撤除中断;c、既无软件清除也无硬件撤除:对于采用电平方式的外部中断请求,CPU对引脚上的中断请求信号既无控制能力,也无应答信号,为保障CPU响应中断请求中断后,执行返回指令前撤除中断请求,必须考虑另外的措施。

5、51单片机中断响应过程51单片机在每个机器周期的S5P2状态顺序检查每个中断源的中断请求标志,若有中断源发送中断请求,CPU在下个机器周期的S5P2状态按优先级顺序查询各中断标志,并且取高优先级的中断进行响应。

响应中断后置位相应的中断优先级状态触发器,标明当前中断服务的优先级别,执行硬件调用程序,将程序计数器PC的内容压入堆栈进行保护。

对于中断源的中断入口地址装入程序计数器PC,使程序转入该中断入口处执行中断服务程序,直到遇到RETI指令。

执行RETI 指令,撤销中断优先级触发器,弹出断点地址至程序计数器PC,继续源程序的执行过程。

在接收中断申请时,如遇到下列情况之一,硬件调用子程序将被封锁:a、正在执行同级或高一级的中断服务程序;b、当前指令周期不是该指令的最后一个周期(或一条指令未执行完);c、当前正在执行的指令是RETI或对IE、IP的读写操作。

6、中断入口地址各中断源的中断入口地址为:STC86C52RC 51单片机中断示例程序#include <reg52.h>typedef unsigned char uint8;typedef unsigned int uint16;typedef unsigned long uint32;sbit enableG1 = P1^3; sbit enableG2 = P1^4;sbit selectC = P1^2; sbit selectB = P1^1; sbit selectA = P1^0; code uint16 num16[16] = { 0xC0, 0xF9, 0xA4, 0xB0,0x99, 0x92, 0x82, 0xF8,0x80, 0x90, 0x88, 0x83,0xC6, 0xA1, 0x86, 0x8E };//共阳数码管真极表uint8 num6[6] = {0};//储存秒,0-5对应于个位...10万位上各位上的值void enable138(void); //启用138译码器切换IO口void refresh_led(void);void thtl_init(void);void timer1_init(void);void et1_init(void);// by /tuenhai/void main(void){enable138();timer1_init();et1_init();while(1);}void interrupt_timer1(void) interrupt 3{static uint16 counter = 0;static uint32 sec = 0;counter++;thtl_init();if(counter == 1000){counter = 0;sec++;num6[0] = sec % 10;num6[1] = sec/10%10;num6[2] = sec/100%10;num6[3] = sec/1000%10;num6[4] = sec/10000%10;num6[5] = sec/100000%10;}refresh_led();//更新num6数组后再刷新数码管}void enable138(void) { enableG1 = 1; enableG2 = 0; }//刷新数码管,只显示有效值void refresh_led(void){static uint8 i = 0;switch(i){case 0: selectC = 0; selectB = 0; selectA = 0; P0 = num16[ num6[0] ]; break; case 1: selectC = 0; selectB = 0; selectA = 1; P0 = num6[5] == 0 && num6[4] == 0 && num6[3] == 0 && num6[2] == 0 && num6[1] == 0 ? 0xFF : num16[ num6[1] ]; break;case 2: selectC = 0; selectB = 1; selectA = 0; P0 = num6[5] == 0 && num6[4] == 0 && num6[3] == 0 && num6[2] == 0 ? 0xFF : num16[ num6[2] ]; break; case 3: selectC = 0; selectB = 1; selectA = 1; P0 = num6[5] == 0 && num6[4] == 0 && num6[3] == 0 ? 0xFF : num16[ num6[3] ]; break;case 4: selectC = 1; selectB = 0; selectA = 0; P0 = num6[5] == 0 && num6[4] == 0 ? 0xFF : num16[ num6[4] ]; break;case 5: selectC = 1; selectB = 0; selectA = 1; P0 = num6[5] == 0 ? 0xFF :num16[ num6[5] ]; break;default: break;}i = ++i % 6;}//设置计数器初数值,重用的内容都应该写成独立函数出来方便维护void thtl_init(void){TH1 = (65536 - 922) / 256;TL1 = (65536 - 922) % 256;}void timer1_init(void){TMOD |= 0X10;TMOD &= 0xDF;thtl_init();TR1 = 1;}void et1_init(void) { ET1 = 1; EA = 1; }。