第05章触发器习题解N

- 格式:ppt

- 大小:3.96 MB

- 文档页数:31

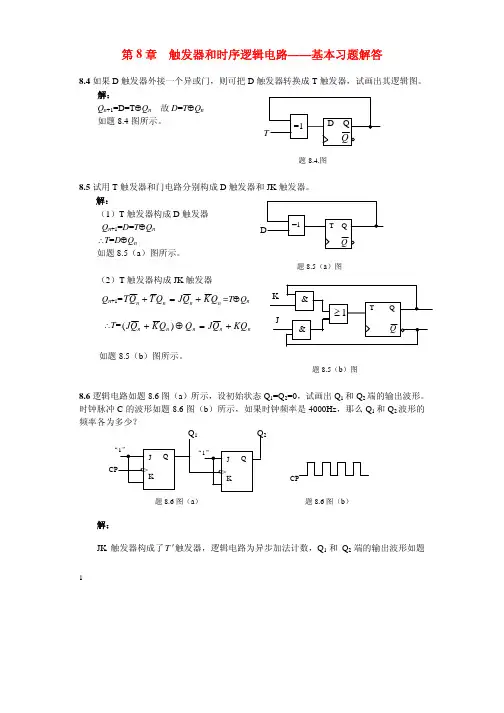

1第8章 触发器和时序逻辑电路——基本习题解答8.4如果D 触发器外接一个异或门,则可把D 触发器转换成T 触发器,试画出其逻辑图。

解:Q n +1=D=T ⊕Q n 故D =T ⊕Q n 如题8.4图所示。

题8.4.图8.5试用T 触发器和门电路分别构成D 触发器和JK 触发器。

解:(1)T 触发器构成D 触发器Q n +1=D =T ⊕Q n ∴T =D ⊕Q n 如题8.5(a )图所示。

题8.5(a )图(2)T 触发器构成JK 触发器Q n +1=n n n n Q K Q J Q T Q T +=+=T ⊕Q n ∴T =n n n n n KQ Q J Q Q K Q J +=⊕+)(如题8.5(b )图所示。

题8.5(b )图8.6逻辑电路如题8.6图(a )所示,设初始状态Q 1=Q 2=0,试画出Q 1和Q 2端的输出波形。

时钟脉冲C 的波形如题8.6图(b )所示,如果时钟频率是4000Hz ,那么Q 1和Q 2波形的频率各为多少?题8.6图(a ) 题8.6图(b )解:JK 触发器构成了T ′触发器,逻辑电路为异步加法计数,Q 1和Q 2端的输出波形如题CP228.6图(c )所示。

Q 1输出波形为CP 脉冲的二分频,Q 2输出波形为CP 脉冲的四分频。

如果CP 脉冲频率为4000Hz ,则Q 1波形的频率是2000Hz ;Q 2波形的频率是1000Hz 。

题8.6图(c )8.8试列出题8.8图所示计数器的状态表,从而说明它是一个几进制计数器。

题8.8图解:F 0:J 0=21Q Q ,K 0=1F 1:J 1=Q 0,K 1=20=Q 0+Q 2 F 2:QJ 2=K 2=1假设初态均为0,分析结果如题8.8图(a )所示,Q 2Q 1Q 0经历了000-001-010-011-100-101-110七种状态,因此构成七进制异步加法计数器。

题8.8图(a )8.9试用主从型JK 触发器组成两位二进制减法计数器,即输出状态为“11”、“10”、“01”、Q Q Q3“00”。

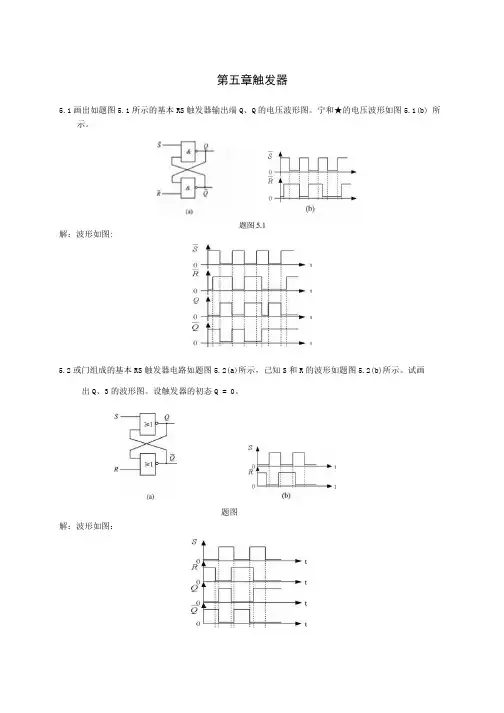

第五章触发器5.1画出如题图5.1所示的基本RS触发器输出端Q、Q的电压波形图。

宁和★的电压波形如图5.1(b) 所示。

解:波形如图:5.2或门组成的基本RS触发器电路如题图5.2(a)所示,己知S和R的波形如题图5.2(b)所示。

试画出Q、3的波形图。

设触发器的初态Q = 0。

题图解:波形如图:5.3题图5.3所示为一个防抖动输出开关电路。

当拨动开关K 时,由于开关接通瞬间发生振颤,R 和S 的波形如图中所示,请画出Q 和Q 端的对应波形。

解:波形如图: 5.4有一时钟RS 触发器如题图5.4所示,试画出它的输出端。

的波形。

初态Q =0-解:波形如图:(b题图(a) (b)题图5.45.5设具有异步端的主从JK 触发器的初始状态Q =0,输入波形如题图5.5所示,试画出输出端Q 的波形。

CLKk题图5.5解:波形如图:CLK5.6设题图5.6的初始状态为0 21 Qo =000,在脉冲CLK 作用下,画出0、0、0的波形(所用 器件都是CD4013)o S D 、R D 分别是CD4013高电平有效的异步置1端,置。

端。

题图5.6解:波形如图:I II I I II I I I(-1__L-. I I --I_L-I I —I__L-1 1 1 1 1 1 0 1 1 1 Illi 1 -J_L- 1 Illi Illi —r i i H — i i i 1(-J__L- 1 1 1 1 1 1 -Hi i /III K I 1 1 1 1 1 1 1 1 o : | | IIII IIII i -i―i - i IIII i i i U_ i i i i i ii -i —i — i i i i i i t; ; 1 1 1 1 1 01 I IIII i [ i i i i —i i—i i ii i.1 1」 1 1 1 IIII IIII IIII1 1 11 1 1 1 1 1 oljiiii i i i i iiiii i ! i i i , 1 1 1——1tnmjwwi.,r -: ~: ~: : ~: ~: ~: ~: ~: ~: ~: ~: ~: ~~: ~: t5.7设题图5.7电路两触发器初态均为0,试画出0、0波形图。

第五章 触发器5.1习题类型1.给定触发器输入信号的波形,求对应的输出波形2. 触发器的应用。

包括触发器存储功能的应用,触发器分频/计数功能的应用。

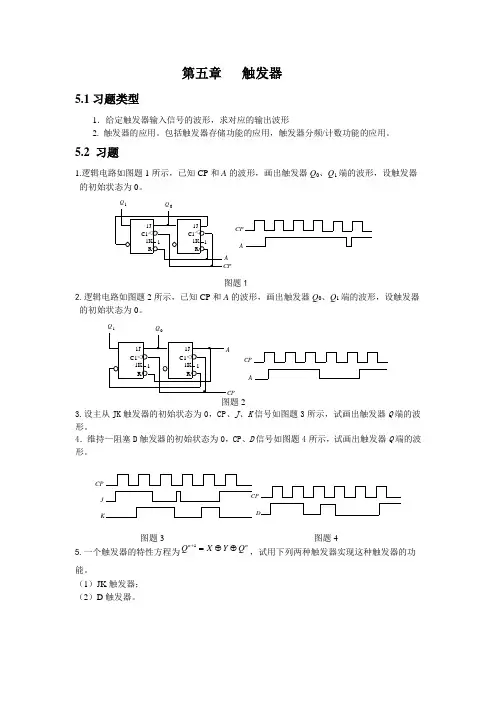

5.2 习题1.逻辑电路如图题1所示,已知CP 和A 的波形,画出触发器Q 0、Q 1端的波形,设触发器的初始状态为0。

图题12.逻辑电路如图题2所示,已知CP 和A 的波形,画出触发器Q 0、Q 1端的波形,设触发器的初始状态为0。

图题23.设主从JK 触发器的初始状态为0,CP 、J 、K 信号如图题3所示,试画出触发器Q 端的波形。

4.维持—阻塞D 触发器的初始状态为0,CP 、D 信号如图题4所示,试画出触发器Q 端的波形。

CP J K5.一个触发器的特性方程为nn Q Y X Q ⊕⊕=+1,试用下列两种触发器实现这种触发器的功能。

(1)JK 触发器; (2)D 触发器。

1Q Q CPAAQ CP A图题3CPD图题45.3 习题答案1. Q 0、Q 1端的波形见图解1。

CP A Q Q 1A CP Q1Q 0图解1 图解22. Q 0、Q 1端的波形见图解2。

3. Q 端的波形见图解3。

J K CP Q图解3 图解4 4. Q 端的波形见图解4。

5. 解:(1)JK 触发器:将JK 触发器的J 、K 端相并,再由输入端T 加以控制,则可以构成T 触发器,其特性方程为:nn Q T Q ⊕=+1。

若要实现特性方程为n n Q Y X Q⊕⊕=+1的功能,只要使:Y X T ⊕=,对应的逻辑电路见图解5(a )。

XYQQ(a ) (b )图解5(2)D 触发器:先将D 触发器转变成T 触发器,其特性方程为:n n Q T Q⊕=+1。

若要实现特性方程n n Q Y X Q ⊕⊕=+1的功能,只要使:Y X T ⊕=,对应的逻辑电路见图解5(b )。

CP D Q。

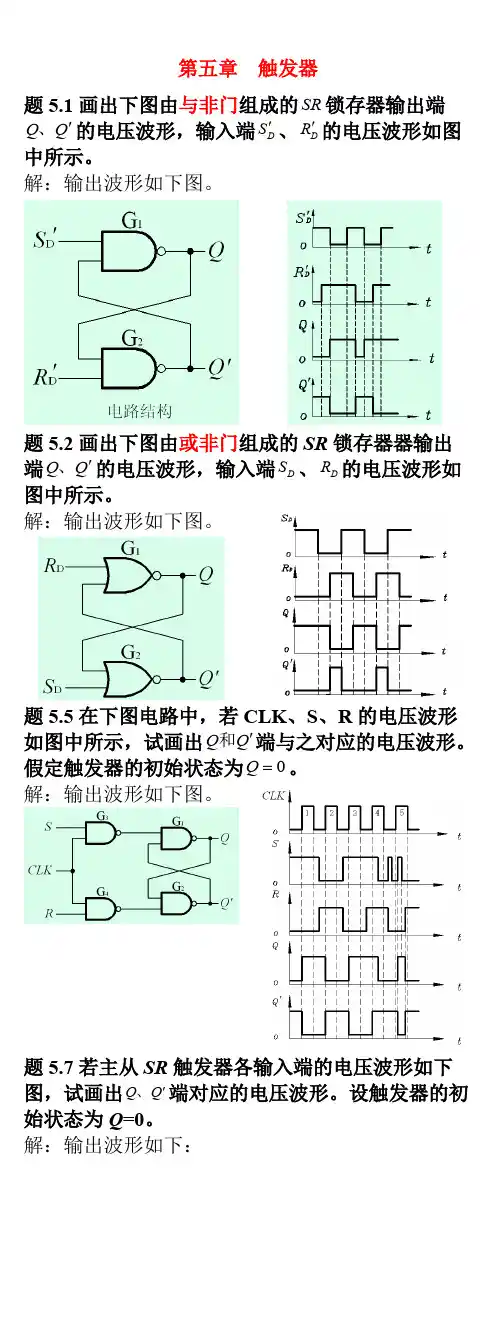

第五章 触发器题5.1画出下图由与非门组成的锁存器输出端SR 的电压波形,输入端、的电压波形如图Q Q '、DS 'D R '中所示。

解:输出波形如下图。

题5.2画出下图由或非门组成的SR 锁存器器输出端的电压波形,输入端、的电压波形如Q Q '、D S D R 图中所示。

解:输出波形如下图。

题5.5在下图电路中,若CLK 、S 、R 的电压波形如图中所示,试画出端与之对应的电压波形。

Q Q '和假定触发器的初始状态为。

0Q =解:输出波形如下图。

题5.7若主从SR 触发器各输入端的电压波形如下图,试画出端对应的电压波形。

设触发器的初Q Q '、始状态为Q =0。

解:输出波形如下:题5.9若主从结构SR触发器的各输DCLK S R R'、、、入端的电压波形如下图,,试画出端对1DS'=Q Q'、应的电压波形。

解:输出波形如下:题5.12若主从结构JK触发器的端的电压波形如下图所示,画出D DCLK R S J K''、、、、端对应的电压波形。

Q Q'、解:输出波形如下:在第三个CLK=1期间,输入信号J发生了跳变,此时,只接受置0信号,1Q=出现了,因此置0。

1K=第四个CLK=1期间,,只接受置1信号,Q=出现过J=1的尖峰,故有置1信号,那么次态置1。

题5.18设图中各触发器的初始状态皆为,试Q=画出在CLK信号连续作用下各触发器输出端的电压波形。

解:(1)JK 触发器的状态方程为:*Q JQ K Q''=+由题意知:1J K ==故有:;状态翻转*11Q Q '=(2)JK 触发器的状态方程为:*Q JQ K Q''=+由题意知:0J K ==故有:;状态保持*22Q Q =(3)JK 触发器的状态方程为:*Q JQ K Q''=+由题意知:,J Q K Q'==故有:;状态翻转*33Q Q '=(4)T 触发器的状态方程为:*Q TQ T Q''=+由题意知:1T =故有:;状态翻转*44Q Q '=(5)JK 触发器的状态方程为:*Q JQ K Q''=+由题意知:;J Q K Q '==故有:;状态保持*55Q Q =(6)JK 触发器的状态方程为:*Q JQ K Q''=+由题意知:;1J Q K ==故有:;保持0状态*60Q =(7)JK 触发器的状态方程为:*Q JQ K Q''=+由题意知:;1J Q K '==故有:;状态翻转*77Q Q '=(8)SR 触发器的状态方程为:*;0()Q S R Q SR '=+=约束条件由题意知:;S Q R Q'==故有:;状态翻转*88Q Q '=(9)D 触发器的状态方程为:*Q D=由题意知:1D =故有:;保持1状态*91Q =(10)D 触发器的状态方程为:*Q D=由题意知:D Q '=故有:;状态翻转*1010Q Q '=(11)D 触发器的状态方程为:*Q D=由题意知:D Q=故有:;状态保持*1111Q Q =(12)T 触发器的状态方程为:*Q TQ T Q''=+由题意知:T Q '=故有:;保持1状态*121Q =因此,输出电压波形图为:题5.24试画出下图电路输出端Y 、Z 的电压波形。

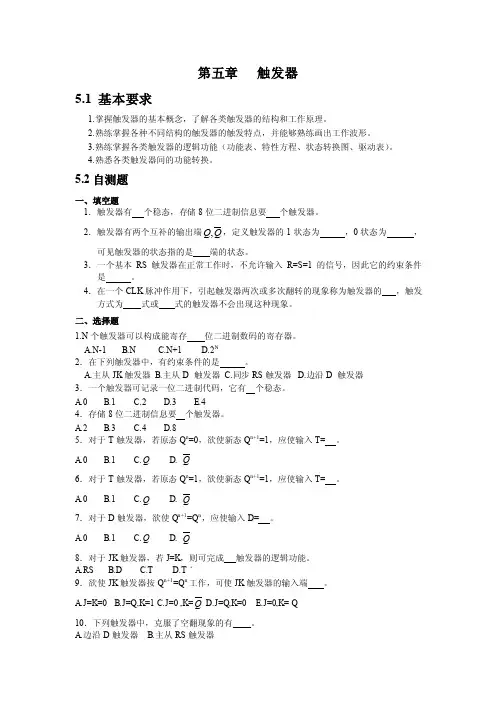

第五章触发器5.1 基本要求1.掌握触发器的基本概念,了解各类触发器的结构和工作原理。

2.熟练掌握各种不同结构的触发器的触发特点,并能够熟练画出工作波形。

3.熟练掌握各类触发器的逻辑功能(功能表、特性方程、状态转换图、驱动表)。

4.熟悉各类触发器间的功能转换。

5.2自测题一、填空题1.触发器有个稳态,存储8位二进制信息要个触发器。

Q,,定义触发器的1状态为,0状态为,2.触发器有两个互补的输出端Q可见触发器的状态指的是端的状态。

3.一个基本RS触发器在正常工作时,不允许输入R=S=1的信号,因此它的约束条件是。

4.在一个CLK脉冲作用下,引起触发器两次或多次翻转的现象称为触发器的,触发方式为式或式的触发器不会出现这种现象。

二、选择题1.N个触发器可以构成能寄存位二进制数码的寄存器。

A.N-1B.NC.N+1D.2N2.在下列触发器中,有约束条件的是。

A.主从JK触发器B.主从D 触发器C.同步RS触发器D.边沿D 触发器3.一个触发器可记录一位二进制代码,它有个稳态。

A.0B.1C.2D.3E.44.存储8位二进制信息要个触发器。

A.2B.3C.4D.85.对于T触发器,若原态Q n=0,欲使新态Q n+1=1,应使输入T= 。

A.0B.1C.QD. Q6.对于T触发器,若原态Q n=1,欲使新态Q n+1=1,应使输入T= 。

A.0B.1C.QD. Q7.对于D触发器,欲使Q n+1=Q n,应使输入D= 。

A.0B.1C.QD. Q8.对于JK触发器,若J=K,则可完成触发器的逻辑功能。

A.RSB.DC.TD.Tˊ9.欲使JK触发器按Q n+1=Q n工作,可使JK触发器的输入端。

A.J=K=0B.J=Q,K=1C.J=0 ,K=QD.J=Q,K=0E.J=0,K= Q10.下列触发器中,克服了空翻现象的有。

A.边沿D触发器B.主从RS触发器C.同步RS 触发器D.主从JK 触发器11.描述触发器的逻辑功能的方法有 。

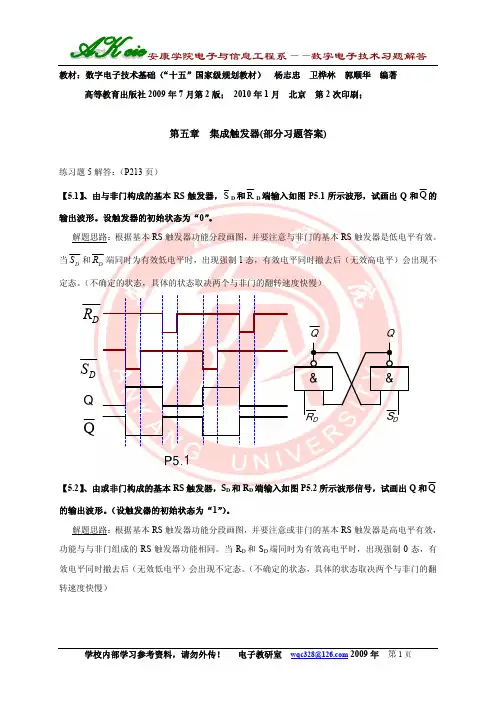

教材:数字电子技术基础(“十五”国家级规划教材) 杨志忠 卫桦林 郭顺华 编著高等教育出版社2009年7月第2版; 2010年1月 北京 第2次印刷;第五章 集成触发器(部分习题答案)练习题5解答:(P213页)【5.1】、由与非门构成的基本RS 触发器,S D 和R D 端输入如图P5.1所示波形,试画出Q 和Q 的输出波形。

设触发器的初始状态为“0”。

解题思路:根据基本RS 触发器功能分段画图,并要注意与非门的基本RS 触发器是低电平有效。

当D S 和D R 端同时为有效低电平时,出现强制1态,有效电平同时撤去后(无效高电平)会出现不定态。

(不确定的状态,具体的状态取决两个与非门的翻转速度快慢)DS D RQ【5.2】、由或非门构成的基本RS 触发器,S D 和R D 端输入如图P5.2所示波形信号,试画出Q 和Q 的输出波形。

(设触发器的初始状态为“1”)。

解题思路:根据基本RS 触发器功能分段画图,并要注意或非门的基本RS 触发器是高电平有效,功能与与非门组成的RS 触发器功能相同。

当R D 和S D 端同时为有效高电平时,出现强制0态,有效电平同时撤去后(无效低电平)会出现不定态。

(不确定的状态,具体的状态取决两个与非门的翻转速度快慢)DS D RQ1≥1≥【5.4】、已知同步RS 触发器的输入CP,R 和S 的电压波形如题P5-4图所示的波形,试画出Q 和Q 的输出波形。

(设触发器的初始状态nQ =0)解题思路:同步钟控RS 触发器是电位型触发器(高电平敏感CP=1),在CP 有效触发期间的状态随输入信号发生变化,n 1n Q R S Q+=+,约束条件:RS=0,R=S=1时出现1Q Q 1n 1n ==++。

CPSQR【5.5】、已知同步D 触发器CP 和D 端的输入电压波形如P5.5图所示,试画出Q 端的输出波形。

(设触发器的初始状态nQ =0)解题思路:同步式触发器是电位型触发器(假定高电平敏感CP=1),在CP 有效触发期间的状态随输入信号发生变化,D Q1n =+。

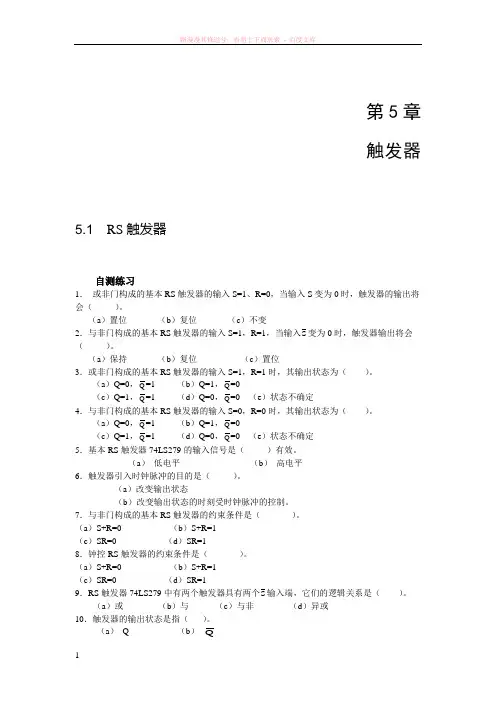

第5章触发器5.1 RS触发器自测练习1.或非门构成的基本RS触发器的输入S=1、R=0,当输入S变为0时,触发器的输出将会()。

(a)置位(b)复位(c)不变2.与非门构成的基本RS触发器的输入S=1,R=1,当输入S变为0时,触发器输出将会()。

(a)保持(b)复位(c)置位3.或非门构成的基本RS触发器的输入S=1,R=1时,其输出状态为()。

(a)Q=0,Q=1 (b)Q=1,Q=0(c)Q=1,Q=1 (d)Q=0,Q=0 (e)状态不确定4.与非门构成的基本RS触发器的输入S=0,R=0时,其输出状态为()。

(a)Q=0,Q=1 (b)Q=1,Q=0(c)Q=1,Q=1 (d)Q=0,Q=0 (e)状态不确定5.基本RS触发器74LS279的输入信号是()有效。

(a)低电平(b)高电平6.触发器引入时钟脉冲的目的是()。

(a)改变输出状态(b)改变输出状态的时刻受时钟脉冲的控制。

7.与非门构成的基本RS触发器的约束条件是()。

(a)S+R=0 (b)S+R=1(c)SR=0 (d)SR=18.钟控RS触发器的约束条件是()。

(a)S+R=0 (b)S+R=1(c)SR=0 (d)SR=19.RS触发器74LS279中有两个触发器具有两个S输入端,它们的逻辑关系是()。

(a)或(b)与(c)与非(d)异或10.触发器的输出状态是指()。

(a)Q (b)Q答案:1.c 2.c 3.d 4.c 5.A 6.b 7.b 8.c 9.b10.a5.2 D 触发器自测练习1.要使电平触发D 触发器置1,必须使D=( )、CP=( )。

2.要使边沿触发D 触发器直接置1,只要使S D =( )、R D =( )即可。

3.对于电平触发的D 触发器或D 锁存器,( )情况下Q 输出总是等于D 输入。

4.对于边沿触发的D 触发器,下面( )是正确的。

(a )输出状态的改变发生在时钟脉冲的边沿 (b )要进入的状态取决于D 输入 (c )输出跟随每一个时钟脉冲的输入 (d )(a )(b )和(c ) 5.“空翻”是指( )。

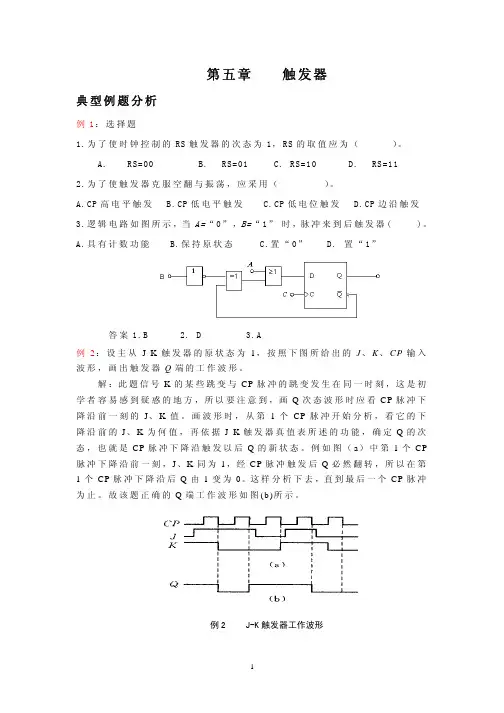

第五章触发器典型例题分析例1:选择题1.为了使时钟控制的RS触发器的次态为1,RS的取值应为()。

A. RS=00B. RS=01C. RS=10D. RS=112.为了使触发器克服空翻与振荡,应采用()。

A.CP高电平触发B.CP低电平触发C.CP低电位触发D.CP边沿触发3.逻辑电路如图所示,当A=“0”,B=“1”时,脉冲来到后触发器( )。

A.具有计数功能B.保持原状态C.置“0”D. 置“1”答案 1.B 2. D 3.A例2:设主从J-K触发器的原状态为1,按照下图所给出的J、K、CP输入波形,画出触发器Q端的工作波形。

解:此题信号K的某些跳变与CP脉冲的跳变发生在同一时刻,这是初学者容易感到疑惑的地方,所以要注意到,画Q次态波形时应看CP脉冲下降沿前一刻的J、K值。

画波形时,从第1个CP脉冲开始分析,看它的下降沿前的J、K为何值,再依据J-K触发器真值表所述的功能,确定Q的次态,也就是CP脉冲下降沿触发以后Q的新状态。

例如图(a)中第1个CP 脉冲下降沿前一刻,J、K同为1,经CP脉冲触发后Q必然翻转,所以在第1个CP脉冲下降沿后Q由1变为0。

这样分析下去,直到最后一个CP脉冲为止。

故该题正确的Q端工作波形如图(b)所示。

例2 J-K触发器工作波形例3:设主从J-K 触发器的原状态为0,输入波形如下图所示,试画出Q 端的工作波形。

解:该例题增加了难度。

要求读者不但熟悉J-K 触发器的真值表,还应熟悉D R 、D R 的异步置0、置1的作用。

画波形时,应首先考虑D R 、D S 的值。

它们对触发器是属于一种电平触发,即不像CP 脉冲那样有上升沿与下降沿的区分。

只要D R (或D S )为0,无论是由0→1,还是由1→0,附近的CP 脉冲都不能起作用,视为无效,同样J 、K 也视为无效。

一旦D R =0(D =1),触发器Q 就为0;而只要D =0(D R =1),触发器Q 就为1。

只有当D R =D S =1时,才分析CP 、J 、K 对触发器Q 的作用。

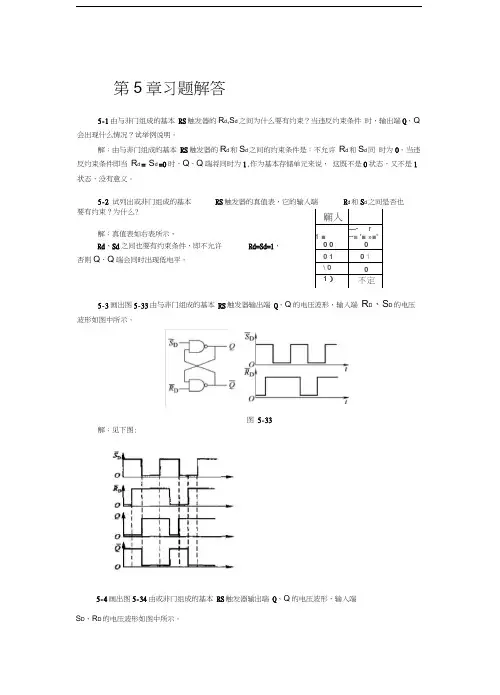

第5章习题解答5-1由与非门组成的基本RS触发器的R d,S d之间为什么要有约束?当违反约束条件时,输出端Q、Q 会出现什么情况?试举例说明。

解:由与非门组成的基本RS触发器的R d和S d之间的约束条件是:不允许R d和S d同时为0。

当违反约束条件即当R d = S d =0时,Q、Q端将同时为1,作为基本存储单元来说,这既不是0状态,又不是1状态,没有意义。

5-2 试列出或非门组成的基本RS触发器的真值表,它的输入端R d和S d之间是否也要有约束?为什么?解:真值表如右表所示、Rd、Sd之同也要有约束条件,即不允许Rd=Sd=1,否则Q、Q端会同时出现低电平。

5-3画出图5-33由与非门组成的基本RS触发器输出端Q、Q的电压波形,输入端R D、S D的电压波形如图中所示。

解:见下图:5-4画出图5-34由或非门组成的基本RS触发器输出端Q、Q的电压波形,输入端S D、R D的电压波形如图中所示。

廟人1 ■0 0—-r--■ '■ »■'0 10 1\ 001 )」不定图5-335-5图5-35所示为一个防抖动输出的开关电路。

当拨动开关S时,由于开关触点接通瞬间发生振颤,R D、S D的电压波形如图中所示。

试画出Q、Q端对应的电压波形。

图5-35解:见下图:图5-34解:见下图:5-6 在图5-36电路中、若CP、S、R的电压波形如图中所示,试画出Q、Q端与之对应的电压波形。

假定触发器的初始状态为Q = 0。

图解:见下图:5-7在图5-37(a)所示的主从RS触发器中,CP、R、S的波形如图5-37(b)所示,试画出相应的Q m、Q m、Q和Q的波形图。

图5-37解:主从RS触发器的工作过程是:在CP= I期间主触发器接收输入信号,但输出端并不改变状态,只有当CP下降沿到来时从触发器甚才翻转,称为下降沿触发。

根据主从RS 触发器状态转换图可画出波形图如下图所示。

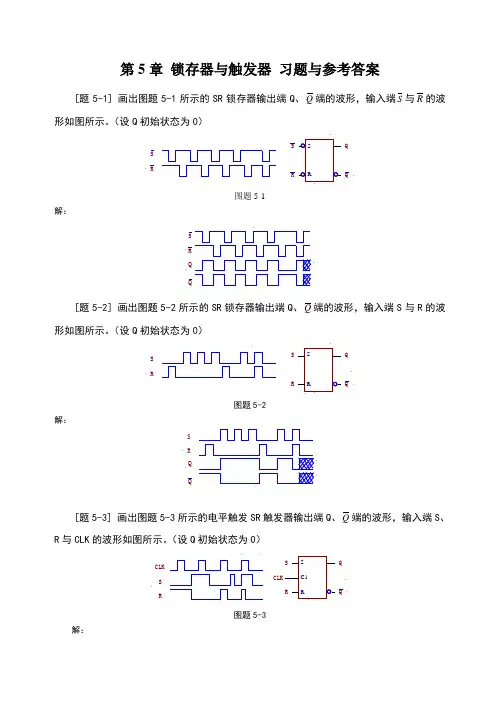

第5章 锁存器与触发器 习题与参考答案[题5-1] 画出图题5-1所示的SR 锁存器输出端Q 、Q 端的波形,输入端S 与R 的波形如图所示。

(设Q 初始状态为0)S RSRSRQQ....图题5-1解:SR.QQ....[题5-2] 画出图题5-2所示的SR 锁存器输出端Q 、Q 端的波形,输入端S 与R 的波形如图所示。

(设Q 初始状态为0)S RS RQQ...SR....图题5-2解:SR.Q Q......[题5-3] 画出图题5-3所示的电平触发SR 触发器输出端Q 、Q 端的波形,输入端S 、R 与CLK 的波形如图所示。

(设Q 初始状态为0)C1S RSRQQ....CLKS RCLK...图题5-3解:S RCLK..Q Q..[题5-4] 画出图题5-4所示的电平触发D 触发器输出Q 端的波形,输入端D 与CLK 的波形如图所示。

(设Q 初始状态为0)C1D DQQ....CLKDCLK..图题5-4解:DCLK..QQ....[题5-5] 画出图题5-5所示的边沿触发D 触发器输出端Q 端的波形,输入端D 与CLK 的波形如图所示。

(设Q 初始状态为0)C11DD QQ....CLKDCLK ...DQQ....CLKDCLK...C11D (1)(2)图题5-5解:DCLK ...DCLK...(1)(2)QQ....[题5-6] 画出图题5-6所示的边沿D 触发器输出Q 端的波形,CLK 的波形如图所示。

(设Q 初始状态为0)C11D Q 1CLK....CLK.1C11D Q 2CLK .CLK .图题5-6解:CLK....Q1Q2Q3...[题5-7] 试画出图题5-7所示电路输出端Q 1、Q 0端的波形,CLK 的波形如图所示。

(设Q 初始状态为0)CLK.....图题5-7解:..CLK...Q0Q1[题5-8] 画出图题5-8所示的JK 触发器输出Q 端的波形,输入端J 、K 与CLK 的波形如图所示。

第5章 习题解答5-1 由与非门组成的基本RS 触发器的d d S ,R 之间为什么要有约束?当违反约束条件时,输出端Q 、Q 会出现什么情况?试举例说明。

解:由与非门组成的基本RS 触发器的d R 和d S 之间的约束条件是:不允许d R 和d S 同时为0。

当违反约束条件即当d R =d S =0时,Q 、Q 端将同时为1,作为基本存储单元来说,这既不是0状态,又不是1状态,没有意义。

5-2 试列出或非门组成的基本RS 触发器的真值表,它的输入端R d 和S d 之间是否也要有约束?为什么?解:真值表如右表所示、Rd 、Sd 之同也要有约束条件,即不允许Rd=Sd=1,否则Q 、Q 端会同时出现低电平。

Q 、Q 的5-3 画出图5-33由与非门组成的基本RS 触发器输出端电压波形,输入端D D S R 、的电压波形如图中所示。

图5-33解:见下图:5-4 画出图5-34由或非门组成的基本RS 触发器输出端Q 、Q 的电压波形,输入端S D 、R D 的电压波形如图中所示。

图5-34解:见下图:5-5 图5-35所示为一个防抖动输出的开关电路。

当拨动开关S时,由于开关触点接通R S、的电压波形如图中所示。

试画出Q、Q端对应的电压波形。

瞬间发生振颤,D D图5-35解:见下图:5-6 在图5-36电路中、若CP、S、R的电压波形如图中所示,试画出Q、Q端与之对应的电压波形。

假定触发器的初始状态为Q=0。

图5-36解:见下图:5-7 在图5-37(a)所示的主从RS触发器中,CP、R、S的波形如图5-37(b)所示,试画Q、Q和Q的波形图。

出相应的Q m、m图5-37解:主从RS触发器的工作过程是:在CP=l期间主触发器接收输入信号,但输出端并不改变状态,只有当CP下降沿到来时从触发器甚才翻转,称为下降沿触发。

根据主从RS 触发器状态转换图可画出波形图如下图所示。

5-8 在图5-38(a)所示的主从JK 触发器中,CP 、J 、K 的波形如图5-38(b)所示,试画出相应的Q m 、m Q 、Q 和Q 的波形图。

第五章触发器5-1由或非门构成的基本RS触发器的特性表:S R Q Q* 功能0 0 Q Q 保持0 1 X 0 复位1 0 X 1 置位1 1 X 0* 约束Q端波形:5-2这是一个门控RS触发器,CP=1期间R、S控制触发器的状态;CP=0期间,触发器的状态保持不变门控RS触发器的特性表:CP R S Q* 功能0 X X Q 保持1 1 0 0 复位1 0 1 1 置位1 1 1 1* 约束5-3(a) RS触发器的输入S=AQ,R=BQ,代入RS触发器的特性方程Q*=S+R Q 中,得:Q*=S+R Q=AQ+(BQ) Q=AQ+(B+Q)Q=AQ+B Q(b) RS触发器的输入S=CQ,R=DQ,代入RS触发器的特性方程Q*=S+R Q 中,得:Q*=S+R Q=CQ+(DQ) Q=CQ+(B+Q)Q=CQ+Q=C+Q5-4与非门构成的基本RS触发器的特性表:R S Q* 功能0 0 1* 约束0 1 0 复位1 0 1 置位1 1 Q 保持5-5根据主从结构同步RS触发器的特性表,可画出波形如下(设正脉冲有效)5-6将S=A,R=A代入RS触发器的特性方程Q*=S+R Q中,得:Q*=A+AQ=A——该电路实现的是D触发器5-7RS触发器的输入S=(AQ),R=(BQ),代入RS触发器的特性方程,图中的RS触发器的R、S为低有效,故特性方程为:Q*=S+RQ中,代入后得:Q*=S+RQ=((AQ))+(BQ)Q=AQ+(B+Q)Q=AQ+B Q5-8由图中可知,当R D=0时,Q1*=Q2*=0;当R D=1时,在时钟脉冲的下降沿,Q1*=D,Q2*=JQ2+K Q2= Q1Q2,画出波形图:5-9主从结构和边沿触发的触发器都是无空翻现象的触发器,这里选用边沿触发的RS触发器。

T触发器的特性方程为Q*= TQ+ T Q,与RS触发器的特性方程Q*=S+R Q,并考虑RS触发器的约束条件RS=0,将T触发器的特性方程化为:Q*= TQ+ (T+Q)Q,故S= TQ,R=(T+Q)=TQ,逻辑电路图如下:5-10触发器上升沿触发,特性方程:Q1*=D1=A,Q2*=D2= Q1,B=( Q2Q1),C=( Q2Q1),波形如下:5-11R D=0时,两个触发器的异步复位端都有效,即:Q1=Q2=0;R D=1时,Q1*=J1Q1+K1Q1= Q1+ Q1Q1=1,下降沿触发Q2*=J2Q2+K2Q2= Q2+ Q2Q2=1,CP上升沿时,触发器的时钟输入端有下降沿出现,即:CP上升沿时触发器有动作波形如下:5-12两个触发器的J=K=1,且都是下降沿触发;故:触发器(1)在CP下降沿翻转;触发器(2)在Q1的下降沿时翻转;输出F=Q1Q2,波形如下(设初态为0):5-13R D=0时,两个触发器的异步复位端都有效,即:Q1=Q2=0;R D=1时:Q1*=D1=Q2,A的上升沿触发Q2*=D2=Q1,B的上升沿触发波形如下:5-14JK触发器的特性方程Q*= JQ+K Q,与T触发器的特性方程Q*= TQ+T Q 进行比较,得:J=K=T,即可构成T触发器。

第五章触发器习题解答【题5.4】画出图 P5.4(a) 中电平触发SR触发器Q和Q’ 端的电压波形。

时钟脉冲CLK和输入S、R的电压波形如图P5.4(b) 所示。

设触发器的初始状态为Q=0。

解:由电平触发器的特性表,可得如上图所示的电压波形。

注意:有不符合SR触发器约束条件的情况,故Q和Q’有一处并不相反!【题5.7】画出图P5.7(a) 中脉冲触发JK触发器输出端Q和Q’的电压波形。

时钟脉冲CLK和输入J、K的电压波形如图P5.7(b) 所示。

设触发器的初始状态为Q=0。

解:由脉冲触发JK触发器的特性表,可得如上图所示的电压波形。

【题5.8】画出图P5.8(a) 中脉冲触发JK触发器输出端Q和Q’的电压波形。

时钟脉冲CLK和输入J、K的电压波如图P5.8(b) 所示。

设触发器的初始状态为Q=0。

解:同脉冲触发JK触发器特性表,可得如上图所示的电压波形。

【题5.11】图P5.11(a) 是带有异步清零端的上升沿触发D触发器,CLK和D 端的电压波形如图P5.11(b) 中所给出。

试画出触发器输出端Q对应的电压波形。

解:Rd=1时,触发器被置0,即Q=0时,由边沿触发D触发器的特性表,可得如上图所示的电压波形。

【题5.13】画出图P5.13(a) 中两个D触发器FF1和FF2的输出端Q1’和Q2’的电压波形。

时钟脉冲CLK和输入端D的电压波形如图P5.13(b)所示。

设触发器的初始状态均为Q=0。

解:FF1触发器发生在CLK下降沿触发;FF2触发器发生在CLK上升沿触发,则电压波形如上图所示。

【题5.14】画出图P5.14(a) 中两个JK触发器FF1和FF2的输出端Q1和Q2的电压波形。

时钟脉冲CLK和输入端J、K的电压波形如图P5.14(a) 所示。

设触发器的的初始状态均为Q=0。

解:FF1触发器发生在CLK下降沿触发;FF2触发器发生在CLK上升沿触发,则Q1、Q2的电压波形如上图所示。

第五章触发器一、填空题1、触发器具有个稳定状态,它可存储位二进制信息。

若要存储8位二进制信息时,需要个触发器。

2、触发器有两个互补输出端Q 和Q ,当0,1Q Q ==时,触发器处于状态;当1,0Q Q ==时,触发器处于状态;可见,触发器的状态是指端的状态。

3、同步RS 触发器的特性方程中,约束条件为RS=0,说明这两个输入信号不能同时为。

4、D 触发器的次态由时钟脉冲CP 上升沿到达时刻D 的状态决定,所以它是。

5、边沿JK 触发器的次态由时钟脉冲CP 下降沿到达时刻输入信号决定。

6、在基本RS 触发器暗中,输入端D R 或D R 能使触发器处于状态,输入端D S 或D S 能使触发器处于状态。

7、同步RS 触发器状态的改变是与信号同步的。

8、同步D 触发器的特性方程为。

9、在CP 脉冲和输入信号作用下,JK 触发器能够具有、、和的逻辑功能。

10、在CP 脉冲有效期间,D 触发器的次态方程1n Q+=,JK 触发器的次态方程1n Q +=。

11、对于JK 触发器,当CP 脉冲有效期间,若0J K ==时,触发器状态;若J K =时,触发器或;若1J K ==时,触发器状态。

12、对于JK 触发器,若J K =,则可完成触发器的逻辑功能。

13、对于JK 触发器,若J K =,则可完成触发器的逻辑功能。

14、将D 触发器的D 端与Q 端直接相连时,D 触发器可转换成触发器。

15、触发器具有稳定状态,其输出状态由触发器的和状态决定。

16、基本RS 触发器有、、三种可使用的功能,对于由与非门组成的基本RS 触发器,在1,0==D D R S 时,触发器;在1,1==D D R S 时,触发器;在0,1==D D R S 时,触发器;不允许时0,0==D D R S 存在,排除这种情况出现的约束条件是。

17、触发器的特性方程是用以表示与、之间关系的方程式。

18、边沿JK 触发器具有、、、功能,其特性方程为。