数字锁相环与位同步提取

- 格式:pptx

- 大小:355.08 KB

- 文档页数:53

一种基于FPGA的锁相环位同步提取电路设计概述同步是通信系统中一个重要的问题。

在数字通信中,除了获取相干载波的载波同步外,位同步的提取是更为重要的一个环节。

因为只有确定了每一个码元的起始时刻,才能对数字信息作出正确的判决。

利用全数字锁相环可直接从接收到的单极性不归零码中提取位同步信号。

一般的位同步电路大多采用标准逻辑器件按传统数字系统设计方法构成,具有功耗大,可靠性低的缺点。

用FPGA设计电路具有很高的灵活性和可靠性,可以提高集成度和设计速度,增强系统的整体性能。

本文给出了一种基于fpga 的数字锁相环位同步提取电路。

数字锁相环位同步提取电路的原理数字锁相环位同步提取电路框本地时钟产生两路相位相差p的脉冲,其频率为fo=mrb,rb为输入单极性不归零码的速率。

输入信码的正、负跳变经过过零检测电路后变成了窄脉冲序列,它含有信码中的位同步信息,该位同步窄脉冲序列与分频器输出脉冲进行鉴相,分频比为m。

若分频后的脉冲相位超前于窄脉冲序列,则在1端有输出,并通过控制器将加到分频器的脉冲序列扣除一个脉冲,使分频后的脉冲相位退后;若分频后的脉冲相位滞后窄脉冲序列,则在2端有输出,并通过控制器将加到分频器的脉冲序列附加一个脉冲,使分频后的脉冲相位提前。

直到鉴相器的1、2端无输出,环路锁定。

基于fpga的锁相环位同步提取电路该电路如该电路由d触发器组成的二分频器和两个与门组成,它将fpga 的高频时钟信号clk_xm变换成两路相位相反的时钟信号,由e、f输出,然后送给控制电路的常开门g3和常闭门g4。

其中f路信号还作为控制器中的d1和。

实验十位同步信号提取实验一、实验目的1、掌握用数字锁相环提取位同步信号的原理与实现方法。

2、了解位同步系统的性能分析。

二、实验内容1、观察数字锁相环提取位同步信号的过程。

2、提取信号源模块NRZ码的位同步信号。

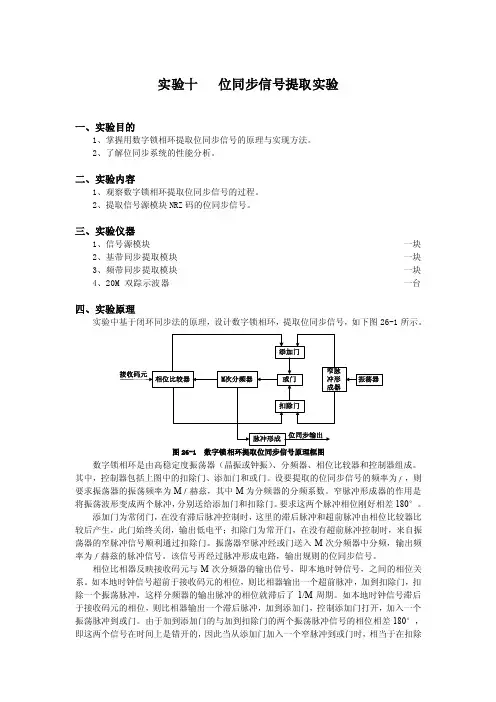

三、实验仪器1、信号源模块一块2、基带同步提取模块一块3、频带同步提取模块一块4、20M双踪示波器一台四、实验原理实验中基于闭环同步法的原理,设计数字锁相环,提取位同步信号,如下图26-1所示。

图26-1 数字锁相环提取位同步信号原理框图数字锁相环是由高稳定度振荡器(晶振或钟振)、分频器、相位比较器和控制器组成。

其中,控制器包括上图中的扣除门、添加门和或门。

设要提取的位同步信号的频率为f,则要求振荡器的振荡频率为M f赫兹,其中M为分频器的分频系数。

窄脉冲形成器的作用是将振荡波形变成两个脉冲,分别送给添加门和扣除门。

要求这两个脉冲相位刚好相差180°。

添加门为常闭门,在没有滞后脉冲控制时,这里的滞后脉冲和超前脉冲由相位比较器比较后产生,此门始终关闭,输出低电平;扣除门为常开门,在没有超前脉冲控制时,来自振荡器的窄脉冲信号顺利通过扣除门。

振荡器窄脉冲经或门送入M次分频器中分频,输出频率为f赫兹的脉冲信号。

该信号再经过脉冲形成电路,输出规则的位同步信号。

相位比相器反映接收码元与M次分频器的输出信号,即本地时钟信号,之间的相位关系。

如本地时钟信号超前于接收码元的相位,则比相器输出一个超前脉冲,加到扣除门,扣除一个振荡脉冲,这样分频器的输出脉冲的相位就滞后了1/M周期。

如本地时钟信号滞后于接收码元的相位,则比相器输出一个滞后脉冲,加到添加门,控制添加门打开,加入一个振荡脉冲到或门。

由于加到添加门的与加到扣除门的两个振荡脉冲信号的相位相差180°,即这两个信号在时间上是错开的,因此当从添加门加入一个窄脉冲到或门时,相当于在扣除门输出的振荡信号中间插入了一个窄脉冲,也就使分频器输入端添加了一个脉冲,这样分频器输出相位就提前了1/M周期。

滤波法及数字锁相环法位同步提取实验和帧同步提取实验滤波法及数字锁相环法位同步提取实验和帧同步提取实验一、实验目的1、掌握滤波法提取位同步信号的原理及其对信息码的要求;2、掌握用数字锁相环提取位同步信号的原理及其对信息代码的要求;3、掌握位同步器的同步建立时间、同步保持时间、位同步信号同步抖动等概念;4、掌握巴克码识别原理;5、掌握同步保护原理;6、掌握假同步、漏同步、捕捉态、维持态的概念。

二、实验内容1、熟悉实验箱2、滤波法位同步带通滤波器幅频特性测量;3、滤波法位同步恢复观测;4、数字锁相环位同步观测;5、帧同步提取实验。

三、实验条件/器材滤波法及数字锁相环法位同步提取实验:1、主控&信号源、8号(基带传输编译码)、13号(载波同步及位同步)模块2、双踪示波器(模拟/数字)3、连接线若干帧同步提取实验:1、主控&信号源、7号模块2、双踪示波器(模拟/数字)3、连接线若干四、实验原理滤波法及数字锁相环法位同步提取实验原理见通信原理综合实验指导书P129-P134;帧同步提取实验原理见通信原理综合实验指导书P141。

五、实验过程及结果分析(一)熟悉实验箱(二)滤波法位同步带通滤波器幅频特性测量1、连线及相关设置(1)关电,连线。

(2)开电,设置主控,选择【信号源】→【输出波形】。

设置输出波形为正弦波,调节相应旋钮,使其输出频率为200Khz,峰峰值3V。

(3)此时系统初始状态为:输入信号为频率200KHz、幅度为3V的正弦波。

2、实验操作及波形观测分别观测13号模块的“滤波法位同步输入”和“BPF-Out”,改变信号源的频率,测量“BPF-Out”的幅度填入下表,并绘制幅频特性曲线。

(三)滤波法位同步恢复观测1、连线及相关设置(1)关电,连线。

(2)开电,设置主控菜单,选择【主菜单】→【通信原理】→【滤波法及数字锁相环位同步法提取】。

将13号模块S2拨上。

将S4拨为1000.(3)此时系统初始状态为:输入PN为256K。

基于FPGA的锁相环位同步提取电路设计锁相环(Phase-Locked Loop,PLL)是一种广泛应用于通信、控制及信号处理等领域的电路,能够实现频率同步和相位同步。

在本文中,我们将讨论基于FPGA的锁相环位同步提取电路设计。

首先,我们将介绍锁相环的基本原理。

锁相环由相位比较器、低通滤波器、VCO(Voltage-Controlled Oscillator)和分频器组成。

相位比较器用于比较参考信号和反馈信号的相位差,将相位差转换为电压差。

低通滤波器将电压差平滑处理,得到控制电压,用于控制VCO的频率。

VCO产生与输入信号频率相同的输出信号,通过分频器将输出信号分频后与参考信号进行比较,实现频率同步。

在基于FPGA的锁相环位同步提取电路设计中,我们的目标是实现一个能够提取输入信号的位同步信息的电路,其中输入信号可能包含多个周期不同的位同步序列。

首先,我们需要设计一个相位比较器,用于比较参考信号和输入信号的相位差。

可以使用FPGA中的数字时钟管理模块来实现相位比较器,将输入信号与参考信号都映射到固定的时钟边沿上,并通过计数器测量输入信号和参考信号之间的相位差。

然后,我们需要设计一个低通滤波器,用于平滑处理相位差。

可以使用FPGA中的滑动平均滤波器来实现低通滤波器,通过对相位差进行滑动平均运算,得到平滑的控制电压。

接下来,我们需要设计一个VCO,用于产生与输入信号频率相同的输出信号。

可以使用FPGA中的数字控制模块来实现VCO,通过调节VCO的控制电压来控制输出频率。

最后,我们需要设计一个分频器,将VCO的输出信号分频后与参考信号进行比较。

可以使用FPGA中的计数器来实现分频器,通过设置分频器的计数值来实现对VCO输出信号的分频。

在整个电路设计过程中,我们需要注意以下几点:1.选择合适的时钟频率和分辨率。

时钟频率要足够高,以满足输入信号的高速采样需求。

分辨率要足够高,以保证位同步信息的精确提取。

2.选择合适的滤波器参数。

实验11 位同步提取实验通信1301王少丹201308030104 一、实验目的1.掌握数字基带信号的传输过程;2.熟悉位定时产生与提取位同步信号的方法。

二、实验仪器1.复接/解复接、同步技术模块,位号I2.时钟与基带数据发生模块,位号:G3.信道编码与ASK、FSK、PSK、QPSK调制,位号:A、B位4.PSK QPSK解调模块,位号C5.100M双踪示波器1台三、实验原理数字通信系统能否有效地工作,在相当大的程度上依赖于发端和收端正确地同步。

同步的不良将会导致通信质量的下降,甚至完全不能工作。

通常有三种同步方式:即载波同步、位同步和群同步。

在本实验中主要分析位同步。

实现位同步的方法有多种,但可分为两大类型:一类是外同步法;另一类是自同步法。

所谓外同步法,就是在发端除了要发送有用的数字信息外,还要专门传送位同步信号,到了接收端得用窄带滤波器或锁相环进行滤波提取出该信号作为位同步之用。

所谓自同步法,就是在发端不专门向收端发送位同步信号,而收端所需要的码元同步信号是设法从接收信号中或从解调后的数字基带信号中提取出来。

这种方法大致可分为滤波法和锁相法。

滤波法是利用窄带滤波器对含定时信息的归零二进制序列(通常占空比为50%)进行滤波,从中滤出所要的位同步分量,并整形、移相等处理,即可得到规则的位同步脉冲信号,但对于无定时信息的非归零二进制序列,则先要进行微分和整流等变换,使之含有定时信息后,才能用窄带滤波器实施滤波。

锁相法是指利用锁相环来提取位同步信号的方法,本实验平台选用锁相法进行位同步提取的。

锁相法的基本原理是,在接收端采用鉴相器比较接收码元和本地产生的位同步信号的相位,如两者相位不一致,则鉴相器输出误差信号去控制本地位同步信号的相位,直至本地的位同步信号的相位与接收信号的相位一致为止。

数字锁相环是一个相位反馈控制系统,在数字锁相环中,由于误差控制信号是离散的数字信号不是模拟信号,因而受控的输出相位的改变是离散的而不是连续的;常用的数字锁相环的原理方框图如图11-1所示。

数字锁相位同步提取的VHDL实现

詹鹏;郭勇;赖武刚;蔡顺燕

【期刊名称】《微计算机信息》

【年(卷),期】2007(023)020

【摘要】本文设计了一种在数字通信系统中的数字锁相位同步提取方案,详细介绍了本设计的位同步提取原理及其各个组成功能模块的VHDL语言实现.并在Quartus Ⅱ开发平台上仿真验证通过.本设计采用VHDL语言编程且在FPGA芯片上实现.具有可移植性好、体积小、低功耗、可靠性高、方便维护和升级等优点,增强了系统的可靠性和稳定性.经验证该位同步提取设计方案能够快速的提取位同步时钟,稳定性好.

【总页数】3页(P180-181,167)

【作者】詹鹏;郭勇;赖武刚;蔡顺燕

【作者单位】610059,四川成都,成都理工大学;610059,四川成都,成都理工大学;610059,四川成都,成都理工大学;610059,四川成都,成都理工大学

【正文语种】中文

【中图分类】TP311;TN919

【相关文献】

1.数字锁相法实现位同步 [J], 殷明

2.数字锁相环在位同步提取中的应用 [J], 伍建辉;李雅梅;苏小敏

3.数字锁相环提取位同步信号的改进与实现 [J], 何文青;宋春林;董航;周英华

4.一种快速位同步的VHDL实现 [J], 麦文;鲍景富

5.一种快速提取位同步的全数字锁相环 [J], 竺南直;刘琪

因版权原因,仅展示原文概要,查看原文内容请购买。

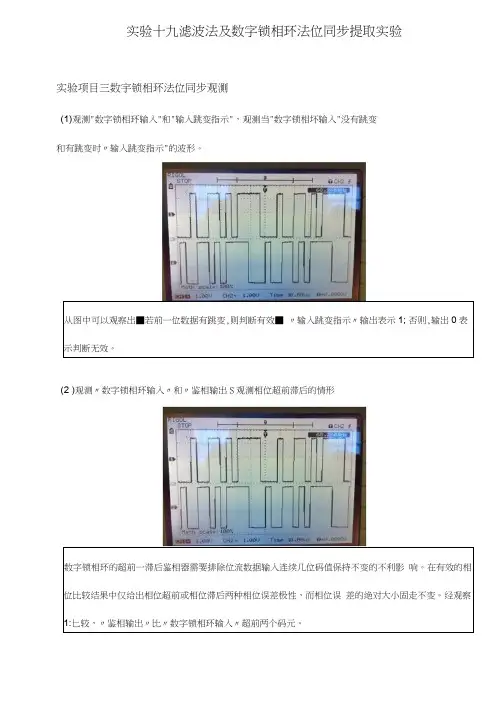

实验十九滤波法及数字锁相环法位同步提取实验实验项目三数宇锁相环法位同步观测(1)观测"数字锁相环输入"和"输入跳变指示",观测当"数字锁相坏输入"没有跳变和有跳变时〃输入跳变指示"的波形。

(2 )观测〃数字锁相环输入〃和〃鉴相输出S观测相位超前滞后的情形(3 )观测"插入指示"和"扣除指示"。

(4 )以信号源模块"CLK"为触发,观测13号模块的"BS2"。

实验二十模拟锁相环实验实验项目一 VCO 自由振荡观测(1)示波器CH1接TH8r CH2接TH4输出,对比观测输入及输出波形。

对比波形可以发现TH8与TH4信号输入与输 出错位半个周期实验项目二同步带测量(1)示波器CH1接13号模块TH8模拟锁相坏输入,CH2接TH4输出BS1 f 观察TH4输出处于锁走状态。

将正弦波频率调小直到输出波形失锁,现在的频率大小fl 为 400Hz ;将孵调大f 直SJ TH4输出处于失锁状态,记下现在频率f2为如右图所示,方波抖动‘说明 处于失锁状态。

记下两次波形失锁的频率,可 计算出同步带仕已实验项目三捕捉带测量0CH1nLfailCa W CHE KOU Tlr.s It.JPC.OOQQ^。

只寸j 蚤田吕K 旧•炮奖設^扫斂刃霹寸工一「_股・M 皋二德8联、ZH7002只槪眾羽鋼慝血地IP 婴・b o o r 只密寸s悴-Z H O O ' 只 W K 槪暴«図$尽、J 009 只摄寸 S弊。

頤奖独¥±仪曲溺寸Hl1•羽傅寸H1型0HY8H112HH U 噩怒低址 (I )(1 )调节信号源使输出波形为方波,设置分频器的分频比,测呈锁相环的锁相环输出频率, 观察上图从图(1 )到(4)可以发现,下面的波形输出频率逐渐变大,这是将分频器的分 频比调大的结果。

滤波法及数字锁相环法位同步提取实验和帧同步提取实验滤波法及数字锁相环法位同步提取实验和帧同步提取实验一、实验目的1、掌握滤波法提取位同步信号的原理及其对信息码的要求;2、掌握用数字锁相环提取位同步信号的原理及其对信息代码的要求;3、掌握位同步器的同步建立时间、同步保持时间、位同步信号同步抖动等概念;4、掌握巴克码识别原理;5、掌握同步保护原理;6、掌握假同步、漏同步、捕捉态、维持态的概念。

二、实验内容1、熟悉实验箱2、滤波法位同步带通滤波器幅频特性测量;3、滤波法位同步恢复观测;4、数字锁相环位同步观测;5、帧同步提取实验。

三、实验条件/器材滤波法及数字锁相环法位同步提取实验:1、主控&信号源、8号(基带传输编译码)、13号(载波同步及位同步)模块2、双踪示波器(模拟/数字)3、连接线若干帧同步提取实验:1、主控&信号源、7号模块2、双踪示波器(模拟/数字)3、连接线若干四、实验原理滤波法及数字锁相环法位同步提取实验原理见通信原理综合实验指导书P129-P134;帧同步提取实验原理见通信原理综合实验指导书P141。

五、实验过程及结果分析(一)熟悉实验箱(二)滤波法位同步带通滤波器幅频特性测量1、连线及相关设置(1)关电,连线。

(2)开电,设置主控,选择【信号源】→【输出波形】。

设置输出波形为正弦波,调节相应旋钮,使其输出频率为200Khz,峰峰值3V。

(3)此时系统初始状态为:输入信号为频率200KHz、幅度为3V 的正弦波。

2、实验操作及波形观测分别观测13号模块的“滤波法位同步输入”和“BPF-Out”,改变信号源的频率,测量“BPF-Out”的幅度填入下表,并绘制幅频特性曲线。

(三)滤波法位同步恢复观测1、连线及相关设置(1)关电,连线。

(2)开电,设置主控菜单,选择【主菜单】→【通信原理】→【滤波法及数字锁相环位同步法提取】。

将13号模块S2拨上。

将S4拨为1000.(3)此时系统初始状态为:输入PN为256K。

实验八位同步信号提取实验一、实验目的1.掌握用数字锁相环提取位同步信号的原理及其对信息代码的要求。

2.掌握位同步器的同步建立时间、同步保持时间、位同步信号同步抖动等概念。

二、实验内容1.观察数字锁相环的失锁状态和锁定状态。

2.观察数字锁相环锁定状态下位同步信号的相位抖动现象及相位抖动大小与固有频差的关系。

3.观察数字锁相环位同步器的同步保持时间与固有频差之间的关系。

三、实验器材1.信号源模块2.同步信号提取模块3.20M双踪示波器一台4.频率计(选用)一台四、实验原理1.电路分析位同步也称为位定时恢复或码元同步。

在任何形式的数字通信系统中,位同步都是必不可少的,无论数字基带传输系统还是数字频带传输系统,无论相干解调还是非相干解调,都必须完成位同步信号的提取,即从接收信号中设法恢复出与发端频率相同的码元时钟信号,保证解调时在最佳时刻进行抽样判决,以消除噪声干扰所导致的解调接收信号的失真,使接收端能以较低的错误概率恢复出被传输的数字信息。

因此,位同步信号的稳定性直接影响到整个数字通信系统的工作性能。

位同步的实现方法分为外同步法和自同步法两类。

由于目前的数字通信系统广泛采用自同步法来实现位同步,故在此仅对位同步中的自同步法进行介绍。

采用自同步法实现位同步首先会涉及两个问题:(1)如果数字基带信号中确实含有位同步信息,即信号功率谱中含有位同步离散谱,就可以直接用基本锁相环提取出位同步信号,供抽样判决使用;(2)如果数字基带信号功率谱中并不含有位定时离散谱,怎样才能获得位同步信号。

数字基带信号本身是否含有位同步信息与其码型有密切关系。

应强调的是,无论数字基带信号的码型如何,数字已调波本身一般不含有位同步信息,因为已调波的载波频率通常要比基带码元速率高得多,位同步频率分量不会落在数字已调波频带之内,通常都是从判决前的基带解调信号中提取位同步信息。

二进制基带信号中的位同步离散谱分量是否存在,取决于二进制基带矩形脉冲信号的占空比。

实验五位同步信号提取实验一、实验目的1.掌握用数字环提取位同步信号的原理及对信息代码的要求。

2.掌握位同步器的同步建立时间、同步保持时间、位同步信号同步抖动等概念。

二、实验内容1.观察数字环的失锁状态、锁定状态。

2.观察数字环锁定状态下位同步信号的相位抖动现象及相位抖动大小与固有频差的关系。

3.观察数字环位同步器的同步保持时间与固有频差之间的关系。

三、实验器材1.信号源模块2.同步信号提取模块3.20M双踪示波器一台4.频率计(选用)一台四、实验步骤1.将信号源模块、同步信号提取模块小心地固定在主机箱中,确保电源接触良好。

2.插上电源线,打开主机箱右侧的交流开关,再分别按下两个模块中的开关POWER1、POWER2,对应的发光二极管LED001、LED002、D500、D501发光,按一下信号源模块的复位键,两个模块均开始工作。

3.将信号源模块的位同步信号的频率设置为15.625KHz(通过拨码开关SW101、SW102进行设置),将信号源模块输出的NRZ码设置为1、0交替码(通过拨码开关SW103、SW104、SW105进行设置)。

4.将同步信号提取模块的拨码开关SW501的第一位拨上,即将数字锁相环的本振频率设置为15.625KHz,然后将信号源模块输出的NRZ码从信号输入点“NRZ-IN”输入,按一下同步信号模块上的“复位”键,使单片机开始工作,以信号源产生的位同步信号“BS”为内触发源,用示波器双踪同时观察信号输出点“位同步输出”的信号与信号源中的“BS”信号。

5.特别注意的是,本模块只能提取NRZ码的位同步信号,而且当信号源模块中的位同步信号的频率偏离同步信号提取模块设置的数字锁相环的本振频率过远时,将无法正确提取输入信号的位同步信号。

本实验中数字锁相环共有15.625KHz、10KHz、8KHz、4KHz四种本振频率可供选择,分别对应拨码开关SW501的1、2、3、4位,实验时请注意正确选择。

1 滤波法对于不归零的随机二进制序列,不能直接从其中滤出位同步信号。

但是,若对该信号进行某种变换,例如,变成归零脉冲后,则该序列中就有f=1/T的位同步信号分量,经一个窄带滤波器,可滤出此信号分量,再将它通过一移相器调整相位后,就可以形成位同步脉冲。

这种方法的方框图如图1-1所示。

它的特点是先形成含有位同步信息的信号,再用滤波器将其滤出。

下面,介绍几种具体的实现方法。

窄带法同步提取法是其中的一种。

图1-1 滤波法原理图图1-1原理图中的波形变换,在实际应用中亦可以是一微分、整流电路,微分、整流后的基带信号波形如图1-2所示。

这里,整流输出的波形与图1-1中波形变换电路的输出波形有些区别,但这个波形同样包含有同步信号分量。

图1-2 基带信号微分、整流波形图1-3 频带受限二相PSK信号的位同步信号提取另一种常用的波形变换方法是对带限信号进行包络检波。

在某些数字微波中继通信系统中,经常在中频上用对频带受限的二相移相信号进行包络检波的方法来提取位同步信号。

频带受限的二相PSK信号波形如图1-3(a)所示。

因频带受限,在相邻码元的相位变换点附近会产生幅度的平滑“陷落”。

经包络检波后,可得图1-3(b)所示的波形。

可以看出,它是一直流和图1-3(c)所示的波形相减而组成的,因此包络检波后的波形中包含有如图1-3(c)所示的波形,而这个波形中已含有位同步信号分量。

因此,将它经滤波器后就可提取出位同步信号。

2 锁相法位同步锁相法的基本原理和载波同步的类似。

在接收端利用鉴相器比较接收码元和本地产生的位同步信号的相位,若两者相位不一致(超前或滞后),鉴相器就产生误差信号去调整位同步信号的相位,直到获得准确的位同步信号为止。

前面讨论的滤波法原理中,窄带滤波器可以是简单的单调谐回路或晶体滤波器,也可以是锁相环路。

我们把采用锁相环来提取位同步信号的方法称为锁相法。

下面介绍在数字通信中常采用的数字锁相法提取位同步信号的原理。

课题二、超前滞后型数字锁相环提取位同步信号的EDA实现

一、课题任务与要求

1.掌握数字锁相环的基本原理;

2.设计数字锁相环的基本模型;

3.根据模型进行程序设计;

4.根据设计的程序进行仿真验证,须达到以下指标:可从任意给定的NRZ 随机序列中提取位同步信号,可以防止相位抖动,并缩短相位调整时间。

二、数字锁相环的建模思想

参考第11章11.5节内容。

三、具体设计步骤

1、超前滞后型数字锁相环基本框图

位同步脉冲

2、数字锁相抗干扰性能的改善

3、缩短相位调整时间

四、功能仿真与验证。

实验十八位同步提取实验一、实验目的1、掌握用滤波法提取位同步信号的原理及其对信息代码的要求。

2、掌握用数字锁相环提取位同步信号的原理及其对信息代码的要求。

3、掌握位同步器的同步建立时间、同步保持时间、位同步信号同步抖动等概念。

二、实验内容1、观察滤波法提取位同步信号各观测点波形。

2、观察数字锁相环的失锁状态和锁定状态。

3、观察数字锁相环锁定状态下位同步信号的相位抖动现象及相位抖动大小与固有频差的关系。

4、观察数字锁相环位同步器的同步保持时间与固有频差之间的关系。

三、实验器材1、信号源模块一块2、⑥号模块一块3、⑦号模块一块4、20M双踪示波器一台5、频率计(选用)一台四、实验原理位同步锁相法的基本原理和载波同步的类似。

在接收端利用鉴频器比较接收码元和本地产生的位同步信号的相位,若两者相位不一致(超前或滞后),鉴相器就产生误差信号去调整位同步信号的相位,直至获得准确的位同步信号为止。

前面讨论的滤波法原理图中,窄带滤波器可以是简单的单调谐回路或晶体滤波器,可以是锁相环路。

我们把采用锁相环来提取位同步信号的方法称为锁相法。

下面介绍在数字通信中常采用的数字锁相环法提取位同步信号的原理。

数字锁相环(DPLL)是一种相位反馈控制系统。

它根据输入信号与本地估算时钟之间的相位误差对本地估算时钟的相位进行连续不断的反馈调节,从而达到使本地估算时钟相位跟踪输入信号相位的目的。

DPLL 通常有三个组成模块:数字鉴相器(DPD)、数字环路滤波器(DLF)、数控振荡器(DCO)。

根据各个模块组态的不同, DPLL 可以被划分出许多不同的类型。

根据设计的要求,本实验系统采用超前滞后型数字锁相环(LL-DPLL)作为解决方案,图18-3是其实现结构。

在LL- DPLL中,DLF 用双向计数逻辑和比较逻辑实现,DCO 采用加扣脉冲式数控振荡器。

这样设计出来的DPLL具有结构简洁明快,参数调节方便,工作稳定可靠的优点。

六、实验步骤1、锁相环法位同步提取(1)将信号源模块上S5拨为“1010”,拨动拨码开关S1、S2、S3,使“NRZ”输出的24位NRZ码设置为01110010 10101010 10101010。

数字锁相位同步提取的VHDL 实现詹鹏 郭勇 赖武刚 蔡顺燕(成都理工大学 四川 成都 610059)摘要:本文设计了一种在数字通信系统中的数字锁相位同步提取方案,详细介绍了本设计的位同步提取原理及其各个组成功能模块的VHDL 语言实现,并在Quartus II 开发平台上仿真验证通过。

本设计采用VHDL 语言编程且在FPGA 芯片上实现,具有可移植性好、体积小、低功耗、可靠性高、方便维护和升级等优点,增强了系统的可靠性和稳定性。

经验证该位同步提取设计方案能够快速的提取位同步时钟,稳定性好。

关键词:位同步;FPGA;VHDL;锁相环;数字通信分类号:TP311,TN919 文献标识码:BImplementation of Digital phase-locked Bit Synchronous extract based on VHDLZHAN Peng GUO Yong LAI Wu –gang Cai Shun-yan( Chengdu University Of Technology Si Chuan Cheng Du 610059)Abstract :This article has designed one kind of digital phase-locked bit synchronous extraction project in the digital communication system, introduced bit synchronous extraction principles and VHDL language realization of each composition function module in detail, and have passed the simulating in the development platform -Quartus II. This design is achieved in a FPGA chip using VHDL language to program. It has the merits of good transplant 、small size 、low-power consumption 、high reliability 、facilitate to maintain and upgrade, and so on… enhanced the reliability and stability of digital communication system. This design can complete bit synchronous clock extraction rapidly and good stability after confirmation.Key words: Bit Synchronous ;FPGA ;VHDL ;Phase-locked loop ;Digital Communication1.引言在数字通信系统中,发送端按照一个确定的时钟逐个传送码元。