锁相环及载波同步

- 格式:ppt

- 大小:970.50 KB

- 文档页数:45

同步技术一、同步技术的定义:同步技术即调整通信网中的各种信号使之协同工作的技术。

诸信号协同工作是通信网正常传输信息的基础。

二、同步技术的分类:按照同步的功能来分,同步可以分为载波同步、位同步(码元同步)、群同步(帧同步)和网同步(通信网中用)等四种。

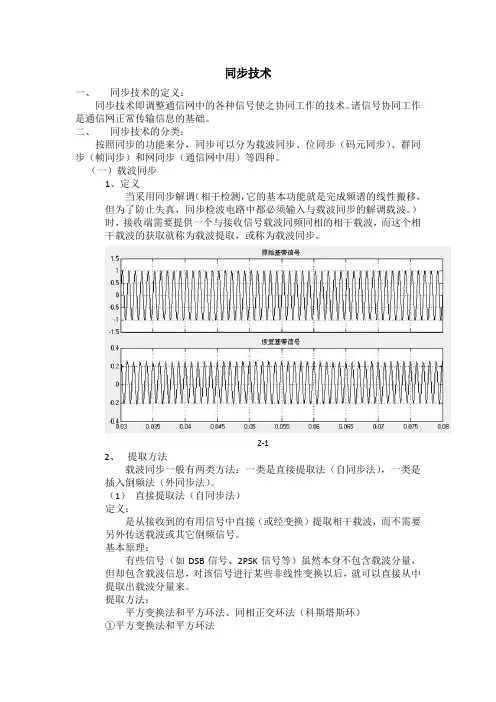

(一)载波同步1、定义当采用同步解调(相干检测,它的基本功能就是完成频谱的线性搬移,但为了防止失真,同步检波电路中都必须输入与载波同步的解调载波。

)时,接收端需要提供一个与接收信号载波同频同相的相干载波,而这个相干载波的获取就称为载波提取,或称为载波同步。

2-12、提取方法载波同步一般有两类方法:一类是直接提取法(自同步法),一类是插入倒频法(外同步法)。

(1)直接提取法(自同步法)定义:是从接收到的有用信号中直接(或经变换)提取相干载波,而不需要另外传送载波或其它倒频信号。

基本原理:有些信号(如DSB信号、2PSK信号等)虽然本身不包含载波分量,但却包含载波信息,对该信号进行某些非线性变换以后,就可以直接从中提取出载波分量来。

提取方法:平方变换法和平方环法、同相正交环法(科斯塔斯环)①平方变换法和平方环法图2-2平方变换法提取载波图2-2即为平方变换法提取载波,为了改善性能,可以在平方变换法大的基础上,把窄带滤波器用锁相环替代,构成如图2-3所示的方框图,这就是平方环法提取载波。

图2-3平方环法提取载波由于锁相环具有良好的跟踪、窄带滤波性能,因此平方环法比一般的平方变换法具有更好的性能,因而得到广泛的应用。

②同相正交环法(科斯塔斯环)图2-4同相正交环法提取载波同相正交环法(科斯塔斯环)是利用锁相环提取载波的另一种常用方法,由于加到上下两个相乘器的本地信号分别为压控振荡器的输出信号和它的正交信号,因此常称这种环路为同相正交环,有时也被称为科斯塔斯环(Costas)环。

如图2-4所示。

(2)插入倒频法(外同步法)定义:是在发端发送信息码元的同时,再发送一个(或多个)包含载波信息的倒频信号,并且要求这个倒频信号不随传播的信息变换,在接收端根据倒频信号提取载波。

锁相环的基本原理锁相环基本原理及其应用锁相环的基本原理锁相环基本原理及其应用锁相环及其应用所谓锁相环路,实际是指自动相位控制电路(APC),它是利用两个电信号的相位误差,通过环路自身调整作用,实现频率准确跟踪的系统,称该系统为锁相环路,简称环路,通常用PLL表示。

锁相环路是由鉴相器(简称PD)、环路滤波器(简称LPF或LF)和压控振荡器(简称VCO)三个部件组成闭合系统。

这是一个基本环路,其各种形式均由它变化而来PLL概念设环路输入信号v= Viomimsin(ωit+φi)环路输出信号v= Vosin(ωot+φo)——其中ωo=ωr+△ωo通过相位反馈控制,最终使相位保持同步,实现了受控频率准确跟踪基准信号频率的自动控制系统称为锁相环路。

PLL构成由鉴相器(PD)环路滤波器(LPF)压控振荡器(VCO)组成的环路。

PLL原理从捕捉过程→锁定A.捕捉过程(是失锁的)a. b.φi┈φi均是随时间变化的,经相位比较产生误差相位φe=φi-φo,也是变化的。

φe(t)由鉴相器产生误差电压v(t)=f(φde)完成相位误差—电压的变换作用。

v(t)为交流电压。

dc.v(t)经环路滤波,滤除高频分量和干扰噪声得到纯净控制电压,由VCO产生d控制角频差△ω0,使ω0随ωi变化。

B.锁定(即相位稳定)a. b.一旦锁定φe(t)=φe∞(很小常数)v(t)= V(直流电压)ddω0≡ωi输出频率恒等于输入频率(无角频差,同时控制角频差为最大△ω0max, 即ω0=ωr+△ω0max。

ωr为VCO固有振荡角频率。

)锁相基本组成和基本方程(时域)各基本组成部件鉴相器(PD)数学模式v(t)=AsinφdDe(t)相位模式环路滤波器(LPF) 数学模式v(t)=A(P) v(t)cFd相位模式压控振荡器(VCO)数学模式相位模式环路模型相位模式:指锁相环(PLL)输入相位和输出相位的反馈调节关系。

相位模型:把鉴相器,环路滤波器和压控振荡器三个部件的相位模型依次级联起来就构成锁相相位模型。

锁相环工作原理锁相环路是一种反馈电路,锁相环的英文全称是Phase-Locked Loop,简称PLL。

其作用是使得电路上的时钟和某一外部时钟的相位同步。

因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。

锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

在数据采集系统中,锁相环是一种非常有用的同步技术,因为通过锁相环,可以使得不同的数据采集板卡共享同一个采样时钟。

因此,所有板卡上各自的本地80MHz和20MHz时基的相位都是同步的,从而采样时钟也是同步的。

因为每块板卡的采样时钟都是同步的,所以都能严格地在同一时刻进行数据采集。

锁相环路是一个相位反馈自动控制系统。

它由以下三个基本部件组成:鉴相器(PD)、环路滤波器(LPF)和压控振荡器(VCO)。

锁相环的工作原理:1. 压控振荡器的输出经过采集并分频;2. 和基准信号同时输入鉴相器;3. 鉴相器通过比较上述两个信号的频率差,然后输出一个直流脉冲电压;4. 控制VCO,使它的频率改变;5. 这样经过一个很短的时间,VCO 的输出就会稳定于某一期望值。

锁相环可用来实现输出和输入两个信号之间的相位同步。

当没有基准(参考)输入信号时,环路滤波器的输出为零(或为某一固定值)。

这时,压控振荡器按其固有频率fv进行自由振荡。

当有频率为fR的参考信号输入时,uR 和uv同时加到鉴相器进行鉴相。

如果fR和fv相差不大,鉴相器对uR和uv进行鉴相的结果,输出一个与uR和uv的相位差成正比的误差电压ud,再经过环路滤波器滤去ud中的高频成分,输出一个控制电压uc,uc将使压控振荡器的频率fv(和相位)发生变化,朝着参考输入信号的频率靠拢,最后使fv= fR,环路锁定。

环路一旦进入锁定状态后,压控振荡器的输出信号与环路的输入信号(参考信号)之间只有一个固定的稳态相位差,而没有频差存在。

实验八数字锁相环与位同步一、实验目的掌握数字锁相环工作原理以及触发式数字锁相环的快速捕获原理。

掌握用数字环提取位同步信号的原理及对信息代码的要求。

掌握位同步器的同步建立时间、同步保持时间、位同步信号同步抖动等概念。

二、实验原理可用窄带带通滤波器,锁相环来提取位同步信号。

实验一中用模数混合锁相环(电荷泵锁相环)提取位同步信号,它要求输入信号是一个准周期数字信号。

实验三中的模拟环也可以提取位同步信号,它要求输入准周期正弦信号。

本实验使用数字锁相环提取位同步信号,它不要求输入信号一定是周期信号或准周期信号,其工作频率低于模数环和模拟环。

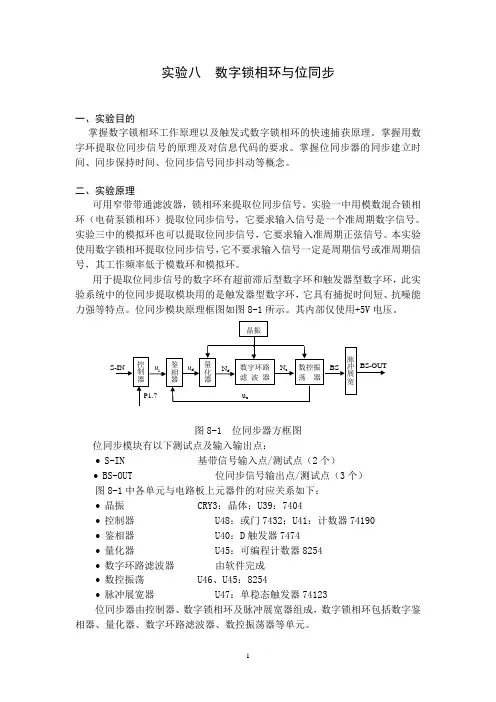

用于提取位同步信号的数字环有超前滞后型数字环和触发器型数字环,此实验系统中的位同步提取模块用的是触发器型数字环,它具有捕捉时间短、抗噪能力强等特点。

位同步模块原理框图如图8-1所示。

其内部仅使用+5V电压。

图8-1 位同步器方框图位同步模块有以下测试点及输入输出点:∙ S-IN 基带信号输入点/测试点(2个)∙ BS-OUT 位同步信号输出点/测试点(3个)图8-1中各单元与电路板上元器件的对应关系如下:∙晶振CRY3:晶体;U39:7404∙控制器U48:或门7432;U41:计数器74190∙鉴相器U40:D触发器7474∙量化器U45:可编程计数器8254∙数字环路滤波器由软件完成∙数控振荡U46、U45:8254∙脉冲展宽器U47:单稳态触发器74123位同步器由控制器、数字锁相环及脉冲展宽器组成,数字锁相环包括数字鉴相器、量化器、数字环路滤波器、数控振荡器等单元。

下面介绍位同步器的工作原理。

数字锁相环是一个单片机系统,主要器件是单片机89C51及可编程计数器8254。

环路中使用了两片8254,共六个计数器,分别表示为8254A 0、8254A 1、8254A 2、8254B 0、8254B 1、8254B 2。

它们分别工作在M 0、M 1、M 2三种工作模式。

实验三:模拟锁相环与载波同步一、实验目的1.模拟锁相环工作原理以及环路锁定状态、失锁状态、同步带、捕捉带等基本概念。

2.掌握用平方法从2DPSK信号中提取相干载波的原理及模拟锁相环的设计方法。

3.了解相干载波相位模糊现象产生的原因。

二、实验内容1. 观察模拟锁相环的锁定状态、失锁状态及捕捉过程。

2. 观察环路的捕捉带和同步带。

3. 用平方环法从2DPSK信号中提取载波同步信号,观察相位模糊现象。

三、实验步骤本实验使用数字信源单元、数字调制单元和载波同步单元。

1.熟悉载波同步单元的工作原理。

接好电源线,打开实验箱电源开关。

2.检查要用到的数字信源单元和数字调制单元是否工作正常(用示波器观察信源NRZ-OUT(AK)和调制2DPSK信号有无,两者逻辑关系正确与否)。

3. 用示波器观察载波同步模块锁相环的锁定状态、失锁状态,测量环路的同步带、捕捉带。

环路锁定时ud为直流、环路输入信号频率等于反馈信号频率(此锁相环中即等于VCO信号频率)。

环路失锁时ud为差拍电压,环路输入信号频率与反馈信号频率不相等。

本环路输入信号频率等于2DPSK载频的两倍,即等于调制单元CAR信号频率的两倍。

环路锁定时VCO信号频率等于CAR-OUT信号频率的两倍。

所以环路锁定时调制单元的CAR和载波同步单元的CAR-OUT频率完全相等。

根据上述特点可判断环路的工作状态,具体实验步骤如下:(1)观察锁定状态与失锁状态打开电源后用示波器观察ud ,若ud为直流,则调节载波同步模块上的可变电容C34,ud随C34减小而减小,随C34增大而增大(为什么?请思考),这说明环路处于锁定状态。

用示波器同时观察调制单元的CAR和载波同步单元的CAR-OUT,可以看到两个信号频率相等。

若有频率计则可分别测量CAR和CAR-OUT频率。

在锁定状态下,向某一方向变化C34,可使ud由直流变为交流,CAR和CAR-OUT频率不再相等,环路由锁定状态变为失锁。

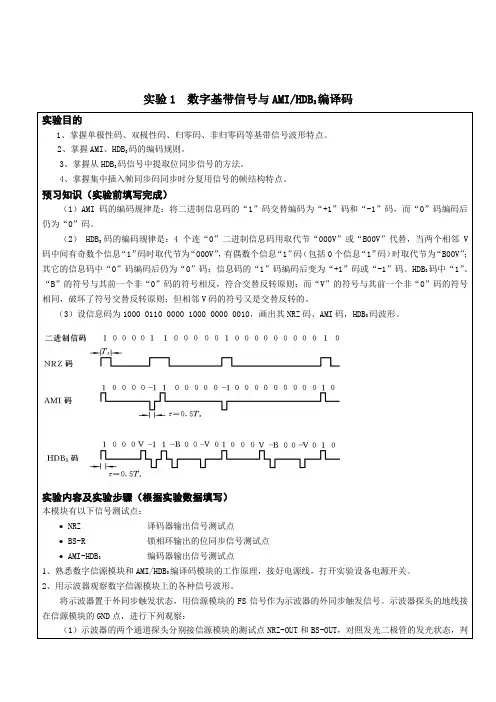

实验1 数字基带信号与AMI/HDB3编译码

实验内容及实验步骤(根据实验数据填写)

本模块有以下信号测试点:

∙ NRZ 译码器输出信号测试点

∙ BS-R 锁相环输出的位同步信号测试点

∙ AMI-HDB3 编码器输出信号测试点

1、熟悉数字信源模块和AMI/HDB3编译码模块的工作原理,接好电源线,打开实验设备电源开关。

2、用示波器观察数字信源模块上的各种信号波形。

将示波器置于外同步触发状态,用信源模块的FS信号作为示波器的外同步触发信号。

示波器探头的地线接在信源模块的GND点,进行下列观察:

实验1 数字基带信号与AMI/HDB3编译码

实验2 数字调制

实验2 数字调制

2DPSK相干解调波形示意图

实验4 数字解调与眼图

实验5数字锁相环与位同步

实验9 PCM时分复用通话与抽样定理

实验9 PCM时分复用通话与抽样定理** 阴影表示频谱混叠。

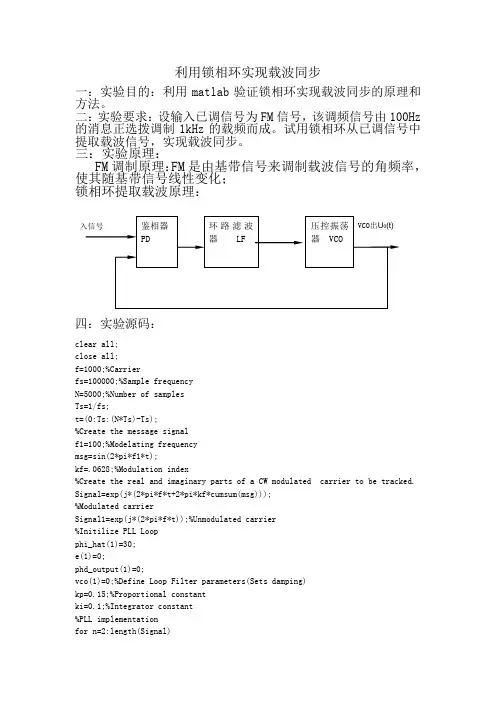

利用锁相环实现载波同步一:实验目的:利用matlab 验证锁相环实现载波同步的原理和方法。

二:实验要求:设输入已调信号为FM 信号,该调频信号由100Hz 的消息正选拨调制1kHz 的载频而成。

试用锁相环从已调信号中提取载波信号,实现载波同步。

三:实验原理:FM 调制原理:FM 是由基带信号来调制载波信号的角频率,使其随基带信号线性变化; 锁相环提取载波原理:四:实验源码:clear all; close all;f=1000;%Carrierfs=100000;%Sample frequency N=5000;%Number of samples Ts=1/fs;t=(0:Ts:(N*Ts)-Ts);%Create the message signal f1=100;%Modelating frequency msg=sin(2*pi*f1*t);kf=.0628;%Modulation index%Create the real and imaginary parts of a CW modulated carrier to be tracked. Signal=exp(j*(2*pi*f*t+2*pi*kf*cumsum(msg))); %Modulated carrierSignal1=exp(j*(2*pi*f*t));%Unmodulated carrier %Initilize PLL Loop phi_hat(1)=30; e(1)=0;phd_output(1)=0;vco(1)=0;%Define Loop Filter parameters(Sets damping) kp=0.15;%Proportional constant ki=0.1;%Integrator constant %PLL implementation for n=2:length(Signal)环路滤波器 LF 入信号 VCO 出U 0(t) 鉴相器 PD 压控振荡器 VCOvco(n)=conj(exp(j*(2*pi*n*f/fs+phi_hat(n-1))));%%Compute VCOphd_output(n)=imag(Signal(n)*vco(n));%Complex multiply VCOxSignal inpute(n)=e(n-1)+(kp+ki)*phd_output(n)-ki*phd_output(n-1);%Filter integratorphi_hat(n)=phi_hat(n-1)+e(n);%Update VCOend;%Plot waveformsstartplot=1;endplot=1000;figure(1);subplot(3,2,1);plot(t(startplot:endplot),msg(startplot:endplot));title('消息信号(频率100Hz)');%xlable(‘Time(seconds)’);ylabel('幅度');grid;figure(1);subplot(3,2,2);plot(t(startplot:endplot),real(Signal(startplot:endplot)));title('FM已调信号(用100Hz的消息信号调制1KHz的载波)');%xlable(‘Time(seconds)’);ylabel('幅度');grid;figure(1)subplot(3,2,3);plot(t(startplot:endplot),e(startplot:endplot));title('环路虑波器的输出');ylabel('幅度');grid;subplot(3,2,4);plot(t(startplot:endplot),real(vco(startplot:endplot)));title('压控振荡器的输出');xlabel('Time(seconds)');ylabel('幅度');grid;subplot(3,2,5);plot(t(startplot:endplot),phd_output(startplot:endplot));title('鉴相器的输出');xlabel('Time(seconds)');ylabel('幅度');grid;subplot(3,2,6);plot(t(startplot:endplot),real(Signal1(startplot:endplot)));title('载波(频率1kHz)');xlabel('Time (seconds )'); ylabel('幅度'); grid;五:实验结果及分析:消息信号是一个单音频信号见subplot(3,2,1),由它来调制载波得已调信号见 subplot(3,2,2),锁相环从已调信号中提取载波信号, 见subplot(3,2,5)是与载波同频同相的本地载波。

实验三十四数字锁相环提取同步信号实验一、实验目的1.学习数字通信中位同步恢复的重要性;2.位同步恢复的主要技术指标;3.了解数字通信位同步恢复的各种方法;4.设计一个数字锁相环提取同步信号电路;5.了解数字锁相环提取同步信号的优缺点;6.用CPLD/FPGA进行位同步信号提取实验。

二、实验仪器与设备1.THEXZ-2型实验箱、数字锁相环提取同步信号实验模块;2.20MHz双踪示波器、万用表。

三、实验原理1.位同步的重要性数字通信中,除了有载波同步的问题外,还有位同步的问题。

因为信息是一串相继的信号码元的序列,解调时常需知道每个码元的起止时刻。

因此,接收端必须产生一个用作抽样判决的定时脉冲序列,它和接收码元的终止时刻应对齐。

我们把在接收端产生与接收码元的重复频率和相位一致的定时脉冲序列的过程称为码元同步或位同步,而称这个定时脉冲序列为码元同步脉冲或位同步脉冲。

要使数字通信设备正常工作,离不开正确的位同步信号。

如果位同步脉冲发生严重抖动或缺位,则使数字通信产生误码;严重时使通信造成中断。

影响位同步恢复的主要原因:①输入位同步电路的信号质量;②信号的编码方式:码元中存在长连“0”或长连“1”。

在实际通信系统中为了节省传输频带和减小对邻近频道的干扰,一般采用限带传输。

也就是将调制信号在基带中进行滚降处理或在中频将已调信号进行中频滤波器成形。

这样的信号经过传输和解调器解调,如QPSK系统则输出是I、O二路模拟信号,由于其形状的原因,因此称为眼图。

位同步取样位置对眼图的开启位置影响很大。

2.位同步的主要技术指标:1)静态相差在相干解调系统中,接收到的信号眼图是由调制器成型滤波器的衰降系统决定的。

为了充分利用接收到的信号能量,通常把位同步的抽样脉冲相位调到眼图最大开启位置。

在这个位置进行判决认为是最佳,称静态相差为零。

相反位同步的抽样脉冲相位偏离了眼图的最大开启位置,就会造成误码或接收机门限特性下降。

通常很多位同步提取电路都存在着一个固定静态相差。

基于 FLL 与 PLL级联的高动态载波跟踪技术高动态给载波的跟踪带来了很大的困难, 本文研究采用锁频环( FLL)和锁相环( PLL) 相结合的方法来实现载波跟踪。

对常用的叉积自动频率跟踪环(CPAFC) 提出了改进, 改进后的鉴频算法具有更宽的鉴频范围和更小的估计误差。

通过 MATLAB 对整体环路进行了仿真, 结果表明该环路可实现在低信噪比、多普勒频移为300kH z、频率一次变化率为 30 kHz/s 下实现载波的跟踪。

引言载波的同步分为载波的捕获和跟踪, 捕获通常采用FFT 来实现载波频率粗捕, 载波的跟踪通常采用锁相环( PL L) 来实现, PLL 在低动态时, 具有较高的跟踪精度和较好的抗噪性能。

但是在高动态环境下由于多普勒效应使接收信号产生的频偏可能会达到几百千赫兹, 频率变化率会达到几千赫兹/秒甚至几十千赫兹/ 秒。

这时为了满足高动态的要求, PLL 必须具有较宽的带宽,这意味着抗噪性能和跟踪精度降低。

此时采用锁相环很难满足系统要求, 可取的方案是采用锁频环( FLL) 。

故在高动态接收机中, 采用 FLL 来跟踪载波的频率而不是相位, FLL 具有较好的动态性能, 但是跟踪精度比PLL低, 二者存在一定的矛盾所以在高动态和低信噪比下, 采用 FLL 和 PLL 相结合来实现载波的跟踪, 用FLL进行载波频率的跟踪, 在频率跟踪之后采用 PLL来进行相位补偿。

FLL 通常采用叉积自动频率跟踪环( CPAFC). 但是这种鉴频算法得到的频差估计值受输入信号的幅度的影响是非线性的、估计误差大。

本文在此基础上进行了改进, 改进后的算法线性鉴频范围比前者宽, 估计误差小。

采用此改进的自动频率跟踪环和锁相环来实现载波的跟 踪, 最后用Matlab 对整体环路进行了仿真。

1 系统的结构整体的环路结构如图 1 所示。

输入信号与数控振荡器混频后, 产生的信号首先要进行多采样抽取, 因为输入信号的采样频率高达数十兆, 如此高的频率给后续的数据处理增加了负担, 因此在混频后要进行 D 倍的频率抽取使频率降低到信号波特率相近的水平。

基于锁频环与锁相环相结合的载波跟踪技术许志鹏;崔琛;余剑【摘要】针对锁频环与锁相环各自在载波跟踪方面的优点与不足,设计了一种基于Costas环的锁频环与锁相环相结合的载波跟踪环路.基于锁频环与锁相环各自锁定时残余频差与残余相差都接近于0的原因,提出了mc、mpe两个阈值,当阈值满足设定的条件时,载波跟踪环路自适应地选择相应的工作状态.仿真结果表明,在阈值达到设定的条件时环路能够正确地实现工作状态的转换,在多普勒频移为固定值以及阶跃函数时能进行准确的跟踪,达到了设计目的.【期刊名称】《电讯技术》【年(卷),期】2012(052)004【总页数】4页(P558-561)【关键词】相干接收机;载波跟踪;锁频环;锁相环【作者】许志鹏;崔琛;余剑【作者单位】电子工程学院信息系,合肥230037;电子工程学院信息系,合肥230037;电子工程学院信息系,合肥230037【正文语种】中文【中图分类】TN973.3相干接收机中,恢复出与载波同频同相的相干载波是接收机系统设计的关键技术之一。

载波跟踪环路通常采用锁频环(FLL)和锁相环(PLL)来实现。

锁相环在低动态时具有较高精度和较好的抗噪性能,但是在较大多普勒频偏条件下锁相环必须增加环路带宽才能对载频进行跟踪,而这也意味着更多噪声的进入,必然减低跟踪精度;而锁频环虽然直接跟踪载波频率,具有较好的动态性能,但是跟踪的精度不如锁相环。

目前文献对锁相环的设计讨论较多,对锁相环和锁频环的结合应用讨论较少。

文献[1]虽然也采取了锁相环与锁频环联合跟踪载波的方式,但是并没有对环路工作状态切换条件作深入细致的讨论,且多普勒频移为固定值以及阶跃函数的情况没有进行仿真。

基于此,针对锁相环与锁频环各自的优缺点,为了实现对载波的精确跟踪,设计了一种锁相环与锁频环相结合的载波跟踪架构,并提出一种使用阈值md 和mpe的判断方法:环路工作过程中不断检测频差大小,当多普勒频移大于设定值时采用锁频环进行频率跟踪;反之锁相环进行相位补偿,实现对载波相位的精确跟踪。