同步二十进制计数器1共30页文档

- 格式:ppt

- 大小:4.00 MB

- 文档页数:30

同步计数器及应用为了提高计数器的工作频率、缩短传输延迟时间,希望计数器状态转换时所有需要翻转的触发器同时翻转,于是同步计数器便应运而生。

在同步计数器内部,各个触发器都受同一时钟脉冲——输入计数脉冲的控制,因此,它们状态更新是同时进行的,故被称为“同步计数器”。

同步计数器既可以用T'触发器组成,也可以用T触发器组成。

在使用T'触发器时,由时钟信号的有无控制触发器是否应翻转。

而在使用T触发器时,是否应当翻转由输入端T的状态决定。

因为T触发器只有一个输入端T,当T-l时,为计数状态;当丁-0时,保持状态不变,通常使用JK触发器构成T触发器。

1.同步二进制减法计数器根据二进制减法计数转换规律,最低位触发器FFo与加法计数器中FFo相同,每来一个计数脉冲翻转一次,应有Jo=Ko =1。

其他触发器的翻转条件是所有低位触发器的Q端全为O,应有Ji一Ki一Qo、J2一Kz一Qi Qo。

由三个JK触发器构成的T触发器构成的三位二进制同步减法计数器如图5. 16电路所示。

图中各触发器均由同一个CP时钟脉冲拉制,因此三个触发器的翻转就由其输入信号的状态决定。

从状态图可知随CP脉冲的递增,触发器的输出Q2 QiQo是递减的,且经过八个CP脉冲完成一个循环过程。

从图5.17(b)所示时序图可知:Qo端输出矩形信号的周期是输入CP信号的周期的两倍,所以Qo端输出信号的频率是输入CP信号频率的1/2,对应Q.端输出信号的频率是输入CP信号频率的114,因此N进制计数器同时也是一个N分频器,所谓分频就是降低频率,N分频器输出信号频率是其输入信号频率的N分之一。

2.集成同步计数器74LS161 74LS161是同步四位二进制加法集成计数器,管脚排列如图5.18所示,逻辑功能如表5.7所示。

集成同步四位二进制加法计数器74LS161具有以下功能:复位端CR =o时,输出Q3 Q2 QiQo全为零,与CP无关,实现异步清零功能(又称复位功能)。

同步二进制计数器计数规律

哎呀呀,我是个小学生,这“同步二进制计数器计数规律”对我来说可太难懂啦!

老师在课堂上讲这个的时候,我感觉自己就像掉进了一个数字的大迷宫里。

什么是同步二进制计数器呀?它的计数规律又是啥?我瞪大眼睛,竖起耳朵,努力想要搞清楚。

我就想呀,这同步二进制计数器是不是就像我们排队跑步,一个接一个,有自己的顺序,不能乱?可这数字的队伍可比我们跑步复杂多啦!

老师说,同步二进制计数器的计数规律是按照二进制的规则来的。

二进制?那不是只有0 和1 嘛。

这就好像我们的开关,开就是1,关就是0 。

可在计数器里,它们可不是简单的开关,而是有着神奇的规律。

我看了看同桌,他也是一脸迷茫。

我忍不住问他:“你懂了吗?”他摇摇头说:“我感觉自己的脑袋都要变成浆糊啦!”可不是嘛,这也太难了!

再看看前面的学霸,人家好像听得津津有味。

我心里那个羡慕呀,我啥时候能像他一样厉害呢?

老师举了个例子,说就像上楼梯,每一步都有特定的数字变化。

我在心里想:这上楼梯谁不会呀,可这数字的楼梯怎么就这么难爬呢?

后来老师又详细地讲了讲,我好像有点明白了。

原来同步二进制计数器的计数规律就是从0 开始,一个一个地往上加,每次加1 ,数字的变化就按照二进制的规则来。

哎呀,我算是搞懂了一些,可还是觉得有点晕乎。

这知识就像一座大山,我才刚刚开始往上爬呢!不过我可不会轻易放弃,我一定要把它弄明白!

我觉得呀,学习这些难的知识就像一场冒险,虽然有时候会迷路,会遇到困难,但是只要坚持,总会找到出路,看到美丽的风景!。

新疆大学课程设计报告所属院系:电气工程学院专业:电气工程课程名称:电子技术B课程设计设计题目:20进制加法计数器电路的设计班级:电气10-4班学生姓名:克依斯尔.卡合曼学生学号:20102101454指导老师: 王红琳努尔买买提完成日期:2014.01.13 —2014.01.2020进制加法计数器电路的设计1.设计目的(1)了解EDA技术的概念、发展及应用。

(2)掌握VHDL语言的基础知识,熟悉在数字电路系统设计中VHDL程序设计。

(3)学习MAX+PLUSⅡ软件的应用方法。

(4)应用EDA技术的设计方法完成(采用原理图和文本法两种方法实现),并在MAX+PLUSⅡ软件上仿真。

(5)需在实验室搭建电路验证并请认真按格式完成课程设计报告。

2.设计内容maxplus2MAX+PLUSII把这些设计转自动换成最终所需的格式。

其设计速度非常快。

对于一般几千门的电路设计,使用MAX+PLUSII,从设计输入到器件编程完毕,用户拿到设计好的逻辑电路,大约只需几小时。

设计处理一般在数分钟内完成。

特别是在原理图输入等方面,Maxplus2被公认为是最易使用,人机界面最友善的PLD开发软件,特别适合初学者使用。

EDA (Electronic Design Automation)EDA技术就是依靠功能强大的电子计算机,在EDA 工具软件平台上,对以硬件描述语言HDL为系统逻辑描述手段完成的设计文件,自动地完成逻辑编译、化简、分割、综合、优化、仿真,直至下载到可编程逻辑器件CPLD/FPGA或专用集成电路ASIC芯片中,实现既定的电子电路设计功能。

2.2 电路的分析(1)创建电路文本图:(3)20进制计数器的原理图:(4)原理图输出波形图:可见当LD信号为“1”是不管CLK信号是什么都不工作。

只要LD为“0”是才能正常工作。

文本原理图其功能表如下:输入输出MR P3 P2 P1 P0 Q3 Q2 Q1 Q01 ×××××××0 0 0 0× d c b a d c b a0 0×××××加计数0 110 1 1 ××××减计数实验接线图:(5)结束语利用MAXPLUS2仿真软件完成了20进制加法计数器原理图及波形仿真,仿真结果与预期相符,实现了20进制的加法。

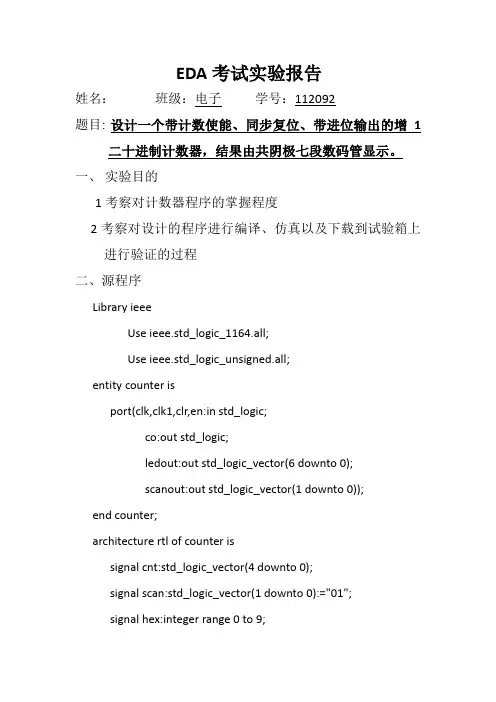

EDA考试实验报告姓名:班级:电子学号:112092题目:设计一个带计数使能、同步复位、带进位输出的增1二十进制计数器,结果由共阴极七段数码管显示。

一、实验目的1考察对计数器程序的掌握程度2考察对设计的程序进行编译、仿真以及下载到试验箱上进行验证的过程二、源程序Library ieeeUseieee.std_logic_1164.all;Useieee.std_logic_unsigned.all;entity counter isport(clk,clk1,clr,en:in std_logic;co:outstd_logic;ledout:outstd_logic_vector(6 downto 0);scanout:outstd_logic_vector(1 downto 0));end counter;architecturertl of counter issignalcnt:std_logic_vector(4 downto 0);signalscan:std_logic_vector(1 downto 0):="01";signalhex:integer range 0 to 9;signalgewei,shiwei:integer range 0 to 9; beginprocess(clk)beginif(clk'event and clk='1')thenifclr='1' thencnt<=(others=>'0');elsif en='1' thenifcnt="10011" thencnt<="00000";co<='1';elsecnt<=cnt+'1';co<='0';end if;end if;end if;end process;process(cnt)begincasecnt iswhen"00000"=>gewei<=0;shiwei<=0;when"00001"=>gewei<=1;shiwei<=0;when"00010"=>gewei<=2;shiwei<=0;when"00011"=>gewei<=3;shiwei<=0;when"00100"=>gewei<=4;shiwei<=0;when"00101"=>gewei<=5;shiwei<=0;when"00110"=>gewei<=6;shiwei<=0;when"00111"=>gewei<=7;shiwei<=0;when"01000"=>gewei<=8;shiwei<=0;when"01001"=>gewei<=9;shiwei<=0;when"01010"=>gewei<=0;shiwei<=1;when"01011"=>gewei<=1;shiwei<=1;when"01100"=>gewei<=2;shiwei<=1;when"01101"=>gewei<=3;shiwei<=1;when"01110"=>gewei<=4;shiwei<=1;when"01111"=>gewei<=5;shiwei<=1;when"10000"=>gewei<=6;shiwei<=1;when"10001"=>gewei<=7;shiwei<=1;when"10010"=>gewei<=8;shiwei<=1;when others=>gewei<=9;shiwei<=1;end case;end process;process(clk1)beginif(clk1'event and clk1='1')thenif(scan=”00” or scan=”11”)thenscan=”01”;elsescan<=not scan;end if;end if;end process;hex<=gewei when scan ="01" else shiwei;with hex selectledout<="0111111" when 0,"0000110" when 1,"1011011" when 2,"1001111" when 3,"1100110" when 4,"1101101" when 5,"1111101" when 6,"0000111" when 7,"1111111" when 8,"1101111" when others;scanout<=scan;endrtl;三、实验结果及分析仿真结果管脚配置实验分析:。