数字集成电路设计之数字系统设计自动化

- 格式:pdf

- 大小:949.96 KB

- 文档页数:116

现代数字系统的设计方法专业:电力电子与电力传动学号:212012*********姓名:刘滔摘要随着微电子技术和计算机技术的不断发展,在涉及通信、国防、航天、工业自动化、仪器仪表等领域的电子系统设计工作中,EDA技术的含量正以惊人的速度上升,它已成为当今电子技术发展的前沿之一。

现代社会电子产品更新换代的速度越来越快,传统的自下而上(Bottom-Up)的设计方法越来越适应不了这种挑战。

随着可编程逻辑器件集成规模的迅速扩大,自身功能的不断完善,以及计算机辅助设计技术的不断发展,在现代电子系统设计领域,EDA(Electronic Design Automation)技术便引起了人们的极大关注。

设计者的工作仅限于利用软件的方式来完成对系统硬件功能的描述。

相应的FPGA/CPLD器件,在EDA工具的帮助下,就可以得到最后的设计结果。

本文首先阐述了EDA技术的基本概念、发展过程和基本特征,最后着重分析EDA技术在两个不同层次上的工作流程,即电路级设计和系统级设计,引入了一种自顶向下的高层次电子设计方法。

关键词:设计方法电子系统设计EDA一、现代数字系统设计的概述EDA(Electronic Design Automation)工程是现代电子信息工程领域中一门发展迅速的新技术。

EDA的定义有广义和狭义之分,广义定义EDA包括半导体工艺设计自动化、可编程器件设计自动化、电子系统设计自动化、印制电路板设计自动化、仿真与测试故障诊断自动化等。

狭义定义的EDA就是电子设计自动化。

EDA技术主要有四个方面:1、可编程逻辑器件,即应用EDA技术完成电子系统设计的载体;2、硬件描述语言(VHDL 或者 Verilog)。

它用来描述系统的结构和功能,是EDA的主要表达手段;3、配套的软件工具。

它用来完成电子系统的智能化设计;4、实验开发系统。

在整个EDA设计电子系统的过程中,实验开发系统是实现可编程器件下载和验证的工具,现代EDA技术是20世纪90年代初从计算机辅助设计、辅助制造和辅助测试等工程概念发展而来的。

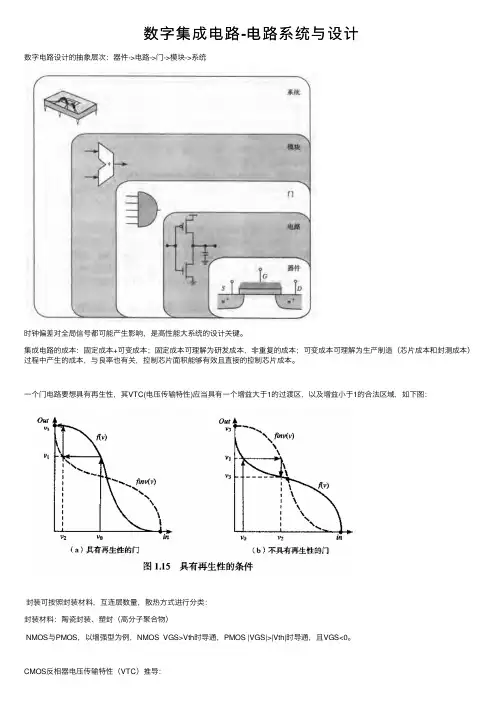

数字集成电路-电路系统与设计数字电路设计的抽象层次:器件->电路->门->模块->系统时钟偏差对全局信号都可能产⽣影响,是⾼性能⼤系统的设计关键。

集成电路的成本:固定成本+可变成本;固定成本可理解为研发成本,⾮重复的成本;可变成本可理解为⽣产制造(芯⽚成本和封测成本)过程中产⽣的成本,与良率也有关,控制芯⽚⾯积能够有效且直接的控制芯⽚成本。

⼀个门电路要想具有再⽣性,其VTC(电压传输特性)应当具有⼀个增益⼤于1的过渡区,以及增益⼩于1的合法区域,如下图:封装可按照封装材料,互连层数量,散热⽅式进⾏分类:封装材料:陶瓷封装、塑封(⾼分⼦聚合物)NMOS与PMOS,以增强型为例,NMOS VGS>Vth时导通,PMOS |VGS|>|Vth|时导通,且VGS<0。

CMOS反相器电压传输特性(VTC)推导:上式为CMOS上下管需要遵守的规则。

结合上式得到,下图为CMOS中上官PMOS部分不同栅极输⼊电压下,下管NMOS电流与输出电压的关系为了使NMOS和PMOS的传输特性能够符合上式DC成⽴,需要根据⼆者的V-I曲线找到交叉点,使其满⾜DC平衡找到上图中的DC平衡交叉点,并提取绘制得到CMOS的电压传输特性如下图,可以看出CMOS的电压传输特性具有再⽣性其中res表⽰呈电阻特性PMOS和NMOS的电流⽅向问题:源極的源是指載流⼦的起點;漏極的漏是指載流⼦的終點。

載流⼦從源極出發,穿過溝道,到達漏極,從外部看,載流⼦最終從漏極漏出去了。

顯然,NMOS和PMOS的載流⼦是不同的,因此導致了令⼈困惑的電流⽅向問題。

盯住載流⼦即可,別被電流⽅向迷惑。

可以簡單地認為,柵極和襯底間的電壓超過閾值後,漏極和源極就接通了,⽽電流⼤⼩則是由柵漏源三極間的電壓決定。

因為MOS是對稱結構,所以源極和漏極無區別且可互換。

關於D和S,也就是漏和源,其實是從⼯藝⾓度觀察的結果。

在MOS中,有兩種載流⼦,⼀種是電⼦,另⼀種是空⽳,標記為N和P。

数字集成电路电路系统与设计

数字集成电路是指将若干个数字电路组合在一起,形成一个完整

的电路系统的过程。

数字集成电路充分利用了数字电子技术的优势,

将不同的数字电路模块集成至一个芯片上,从而大大提高了电路系统

的性能和可靠性。

数字集成电路的设计需要遵循特定的规范和标准,包括电路功能

的设计、电路参数的计算和选取,以及电路布局和制造等方面。

同时,数字集成电路的设计需要充分考虑电路系统的稳定性、抗干扰能力、

低功耗、高可靠性等特点,以满足不同应用场景的需求。

数字集成电路常常应用于各种高精度、高复杂度数字系统中,包

括计算机、通信系统、音视频处理、自动化控制等领域。

在数字集成

电路的设计和制造中,还需要根据具体应用场景选择不同的设计方案

和制造工艺,以获得最优性能和可靠性。

数字集成电路设计一、引言数字集成电路设计是一个广泛且深入的领域,它涉及到多种基本元素和复杂系统的设计。

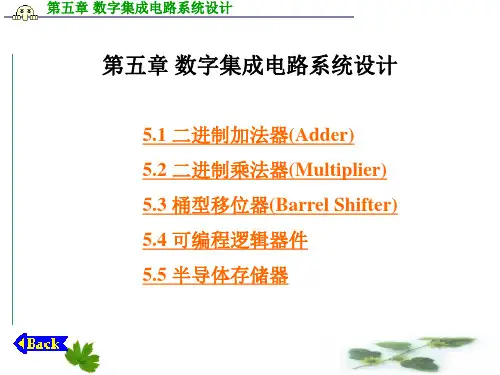

本文将深入探讨数字集成电路设计的主要方面,包括逻辑门设计、触发器设计、寄存器设计、计数器设计、移位器设计、比较器设计、译码器设计、编码器设计、存储器设计和数字系统集成。

二、逻辑门设计逻辑门是数字电路的基本组成单元,用于实现逻辑运算。

常见的逻辑门包括与门、或门、非门、与非门和或非门等。

在设计逻辑门时,需要考虑门的输入和输出电压阈值,以确保其正常工作和避免误操作。

三、触发器设计触发器是数字电路中用于存储二进制数的元件。

它有两个稳定状态,可以存储一位二进制数。

常见的触发器包括RS触发器、D触发器和JK触发器等。

在设计触发器时,需要考虑其工作原理和特性,以确保其正常工作和实现预期的功能。

四、寄存器设计寄存器是数字电路中用于存储多位二进制数的元件。

它由多个触发器组成,可以存储一组二进制数。

常见的寄存器包括移位寄存器和同步寄存器等。

在设计寄存器时,需要考虑其结构和时序特性,以确保其正常工作和实现预期的功能。

五、计数器设计计数器是数字电路中用于对事件进行计数的元件。

它可以对输入信号的脉冲个数进行计数,并输出计数值。

常见的计数器包括二进制计数器和十进制计数器等。

在设计计数器时,需要考虑其工作原理和特性,以确保其正常工作和实现预期的功能。

六、移位器设计移位器是数字电路中用于对二进制数进行移位的元件。

它可以对输入信号进行位移操作,并输出移位后的结果。

常见的移位器包括循环移位器和算术移位器等。

在设计移位器时,需要考虑其工作原理和特性,以确保其正常工作和实现预期的功能。

七、比较器设计比较器是数字电路中用于比较两个二进制数的元件。

它可以比较两个数的值,并输出比较结果。

常见的比较器包括并行比较器和串行比较器等。

在设计比较器时,需要考虑其工作原理和特性,以确保其正常工作和实现预期的功能。

八、译码器设计译码器是数字电路中用于将二进制数转换为另一种形式的元件。

数字集成电路是现代电子产品中不可或缺的一部分,它们广泛应用于计算机、手机、汽车、医疗设备等领域。

数字集成电路通过在芯片上集成大量的数字电子元件,实现了电子系统的高度集成和高速运算。

本文将从电路、系统与设计三个方面探讨数字集成电路的相关内容。

一、数字集成电路的电路结构数字集成电路的电路结构主要包括逻辑门、寄存器、计数器等基本元件。

其中,逻辑门是数字集成电路中最基本的构建元件,包括与门、或门、非门等,通过逻辑门的组合可以实现各种复杂的逻辑功能。

寄存器是用于存储数据的元件,通常由触发器构成;而计数器则可以实现计数和计时功能。

这些基本的电路结构构成了数字集成电路的基础,为实现各种数字系统提供了必要的支持。

二、数字集成电路与数字系统数字集成电路是数字系统的核心组成部分,数字系统是以数字信号为处理对象的系统。

数字系统通常包括输入输出接口、控制单元、运算器、存储器等部分,数字集成电路在其中充当着处理和控制信号的角色。

数字系统的设计需要充分考虑数字集成电路的特性,包括时序和逻辑的正确性、面积和功耗的优化等方面。

数字集成电路的发展也推动了数字系统的不断完善和创新,使得数字系统在各个领域得到了广泛的应用。

三、数字集成电路的设计方法数字集成电路的设计过程通常包括需求分析、总体设计、逻辑设计、电路设计、物理设计等阶段。

需求分析阶段需要充分了解数字系统的功能需求,并将其转化为具体的电路规格。

总体设计阶段需要根据需求分析的结果确定电路的整体结构和功能分配。

逻辑设计阶段是将总体设计转化为逻辑电路图,其中需要考虑逻辑函数、时序关系、并行性等问题。

电路设计阶段是将逻辑电路图转化为电路级电路图,包括门电路的选择和优化等。

物理设计阶段则是将电路级电路图转化为实际的版图设计,考虑布线、功耗、散热等问题。

在每个设计阶段都需要充分考虑电路的性能、面积、功耗等指标,以实现设计的最优化。

结语数字集成电路作为现代电子系统的关键组成部分,对于数字系统的功能和性能起着至关重要的作用。

数字集成电路设计课程设计一、课程设计的背景随着信息技术的快速发展,数字集成电路已成为数字系统设计的基础。

数字集成电路的设计是数字电路设计中的重要内容,其设计水平直接影响了整个数字系统设计的性能和可靠性。

为了培养学生的数字系统设计能力,提高他们的综合技能,数字集成电路设计课程必须设置课程设计环节,让学生通过自主设计电路和实现电路的过程,来了解数字系统设计和数字集成电路的实际运用。

二、课程设计的目标本课程设计主要旨在让学生了解数字集成电路和数字系统设计方面的知识,并培养他们的创新能力和实践操作能力,使其能够熟练地使用EDA工具来设计数字集成电路。

具体目标如下:1.掌握数字系统设计的基本方法和流程;2.熟悉EDA工具的使用;3.实践基本的数字集成电路设计;4.培养创新思维和实践操作能力。

三、课程设计的任务本课程设计分为两个任务,分别是:任务一:基于FPGA实现数字电路设计在这个任务中,学生需要使用FPGA实现一个简单的数字电路设计,具体步骤如下:1.学习FPGA芯片的软件开发环境,并了解开发工具的基本使用方法。

2.根据实际需求,设计一个数字电路电路图,并使用EDA工具进行仿真验证。

3.将设计好的电路烧录到FPGA芯片中,并通过实验验证电路的可行性和正确性。

4.编写实验报告,记录设计过程、结果和分析等内容。

通过这个任务的完成,学生可以深入了解数字电路设计的流程和方法,同时掌握基本的EDA工具使用方法,提高了实践操作能力。

任务二:基于Verilog语言设计数字集成电路这个任务是在前一个任务的基础上,进一步实践和提高数字集成电路设计的能力。

具体步骤如下:1.学生需要掌握Verilog语言的基本语法和使用方法。

2.选定一个实际需要的数字电路任务,并进行详细的设计和仿真验证。

3.将设计好的Verilog代码综合成网表文件,并使用EDA工具进行布局和布线。

4.将布线后的电路设计烧录到FPGA芯片中,并进行实验验证。

verilog hdl数字集成电路设计与原理 数字集成电路是现代电子技术中的重要组成部分,其设计与原理对于电子工程师来说至关重要。

本文将以Verilog HDL为工具,介绍数字集成电路的设计与原理。

一、数字集成电路的概述 数字集成电路是由稳定的电气或电子器件组成的,能够执行数字逻辑操作的电路。

它们以二进制表示,通过与、或、非等逻辑门实现简单或复杂的数字逻辑功能。

数字集成电路的设计与原理是研究数字逻辑电路的基础,是实现数字系统的关键。

二、Verilog HDL的介绍 Verilog HDL是硬件描述语言(Hardware Description Language )的一种,广泛应用于数字电路设计领域。

它不仅可以用于描述数字电路的结构和功能,还可以用于验证和仿真电路的行为。

Verilog HDL 为数字集成电路设计与原理提供了一种高效的工具和方法。

三、数字集成电路的设计步骤 1. 确定需求:在进行数字集成电路的设计之前,首先要明确电路的需求和功能。

例如,设计一个加法器电路,需要明确输入和输出的位数,以及所需的运算规则。

2. 设计逻辑功能:根据电路的需求和功能,使用Verilog HDL描述电路的逻辑功能。

例如,使用逻辑门和寄存器等基本组件,以及运算、比较和控制逻辑来实现增加和溢出处理。

3. 进行仿真:使用Verilog HDL工具进行电路的仿真,验证设计的正确性。

通过使用测试输入数据,观察输出是否符合预期结果。

如果有错误或问题,需要进行调试和修改。

4. 进行综合:将Verilog HDL代码综合为门级电路。

综合工具会将Verilog HDL描述的逻辑电路转化为实际的门级电路,包括各种逻辑门、寄存器和其他组件。

5. 进行布局布线:将综合后的电路进行物理设计,包括电路的布局和布线。

布局布线工具将综合后的门级电路映射到实际器件上,并进行连线等工作,以满足电路的时序和功耗要求。

6. 进行验证:验证设计的正确性和性能。

IC,这些微小但强大的芯片,是我们电子设备的无名英雄,从我们口袋里的光滑智能无线终端,到我们桌子上的强大的截肢者,甚至我们车上最先进的汽车系统。

当它到数字集成电路时,全部是创建顶尖的系统,来传递心跳的性能,而吸电就像一个花哨的鸡尾酒,永远,永远,投球在可靠性上。

这些电路是数据处理、信号处理和控制系统的摇滚巨星,使得我们技术精湛的世界开始运转。

但是,在所有的滑翔和魅力背后,工作上有大量的脑力。

设计数字集成电路就像开始一个令人惊叹的冒险,任务包括设定舞台有规格,通过模型化将人物带入生命,在模拟中通过脚步化,通过合成来伤害它们的存在,最后通过彻底的验证确保一切的平稳航行。

就像是数字交响乐的策划者,进行电路,系统和设计技术的和谐混合,在区块上创建最高效和可靠的集成电路。

这是一个疯狂的旅程,但有人必须做到这一点!设计数字集成电路需要使用不同的工具和方法来开发和改进数字系统。

首先要弄清楚数字系统需要做什么以及它需要多好的表现我们用维利洛格和VHDL等特殊语言创建模型并测试数字系统。

接下来,我们把模型变成逻辑门列表,我们努力确保设计符合所有要求。

我们用半导体制造来制造实际的电路。

这涉及到根据设计创建布局和建造电路。

数字集成电路领域是一个不断发展和动态的研究领域,其特点是设计方法、技术和应用方面不断取得进展。

随着数字系统继续在各种电子装置和系统中发挥重要作用,对数字集成电路设计专业人才的需求日益增加。

对这一领域感兴趣的个人必须在数字电路、系统和设计原则方面奠定坚实的基础,并随时了解数字集成电路技术的最新发展。

只要具备必要的知识和技能,就能够有助于创造创新的数字集成电路,推动技术进步,提高电子系统的性能。

浅谈对数字集成电路设计原理与使用之我见【摘要】数字集成电路是现代电子领域中不可或缺的组成部分,其设计原理和方法至关重要。

本文将从数字集成电路设计的基本原理、常见问题及解决方案、关键技术等方面展开探讨,探讨数字集成电路在通信、计算机等领域的应用,以及其未来发展趋势。

数字集成电路设计的重要性不言而喻,它推动了现代科技的发展,并在各个领域发挥着关键作用。

个人认为,数字集成电路设计原理与使用的学习和掌握对于电子工程师至关重要,只有深入理解其原理,并不断更新技术,才能在激烈的市场竞争中立于不败之地。

通过本文的学习,读者将更加深入了解数字集成电路设计的重要性以及其对现代科技发展的推动作用。

【关键词】数字集成电路,设计原理,现代电子领域,重要性,基本原理,常见问题,解决方案,关键技术,通信,计算机,应用,发展趋势,科技发展,个人看法。

1. 引言1.1 数字集成电路概述数字集成电路是现代电子技术领域中至关重要的一部分,它是在单个芯片上集成了数百甚至数千个电子器件的电路。

数字集成电路可以实现各种逻辑功能,如与门、或门、非门等,从而构建出各种复杂的数字系统。

数字集成电路的发展可以追溯到20世纪60年代,随着科技的不断进步,数字集成电路在各个领域的应用也越来越广泛。

数字集成电路的设计涉及到很多方面的知识,包括逻辑设计、电路设计、信号处理等。

设计师需要根据具体的应用场景来选择合适的器件和电路结构,以实现最佳的性能。

数字集成电路设计中的常见问题包括功耗、速度、面积等方面的优化,设计师需要通过各种方法和技术来解决这些问题。

数字集成电路在现代通信、计算机等领域扮演着至关重要的角色。

它们是各种数字系统的基础,为我们的日常生活和工作提供了便利。

随着科技的不断发展,数字集成电路的设计也在不断进步,未来数字集成电路的应用领域将会更加广泛,性能也会得到进一步提升。

1.2 设计原理和方法数字集成电路的设计原理和方法是数字电子技术领域的重要基础,它涉及到从设计概念到最终产品实现的一系列过程。

数字系统设计自动化第二版边计年数字系统设计自动化作为现代工程技术领域的重要组成部分,一直以来都备受关注。

《数字系统设计自动化》第二版边计年为该领域的重要著作之一,本文将对该书的主要内容进行分析和总结,以期为读者提供更全面、系统的了解。

一、作者介绍1.1 作者背景边计年,美国电子工程师协会(IEEE)和计算机协会(ACM)会士,曾就职于斯坦福大学计算机系,师从计算机设计自动化领域的著名专家约翰·斯密斯博士,是该领域的资深研究者和教育者。

1.2 作者成就边计年在数字系统设计自动化领域取得了丰硕的成果,先后在国际学术期刊和会议上发表了大量高水平的学术论文,被广泛引用和应用。

其著作《数字系统设计自动化》第一版在全球范围内得到了极高的评价和认可,为该领域的发展做出了积极的贡献。

1.3 作者影响边计年的学术成就和教育影响广泛,深受同行和学生的尊重和赞誉。

他曾担任过多个国际学术组织和研究机构的重要职务,对数字系统设计自动化领域的发展产生了重要影响。

二、书籍内容2.1 书籍概述《数字系统设计自动化》第二版旨在系统地介绍数字系统设计自动化的基本原理、关键技术和最新进展,涵盖了该领域的核心知识和前沿研究成果,具有很高的权威性和学术性。

2.2 主要内容该书主要包括以下几个方面的内容:(1)数字系统设计基础:介绍数字系统设计的基本概念、方法和流程,包括数字信号处理、数字电路设计、逻辑综合等内容。

(2)数字系统建模与验证:介绍数字系统建模与验证的理论和方法,包括硬件描述语言(HDL)、高级综合(HLS)、模拟验证、形式验证等内容。

(3)数字逻辑综合与优化:介绍数字逻辑综合与优化的理论和方法,包括逻辑综合算法、布尔函数简化、逻辑优化技术等内容。

(4)集成电路布图设计:介绍集成电路布图设计的理论和方法,包括物理综合、布图布线、功耗优化、时序分析等内容。

(5)自动化设计工具与流程:介绍数字系统设计自动化工具和流程,包括EDA工具的分类与应用、自动化设计流程的规划与管理等内容。

数字集成电路——电路、系统与设计目录第一部分基本单元第1章引论1.1 历史回顾1.2 数字集成电路设计中的问题1.3 数字设计的质量评价1.4 小结1.5 进一步探讨第2章制造工艺2.1 引言2.2 CMOS集成电路的制造2.3 设计规则——设计者和工艺工程师之间的桥梁2.4 集成电路封装2.5 综述:工艺技术的发展趋势2.6 小结2.7 进一步探讨设计方法插入说明A——IC版图第3章器件3.1 引言3.2 二极管3.3 MOS(FET)晶体管3.4 关于工艺偏差3.5 综述:工艺尺寸缩小3.6 小结3.7 进一步探讨设计方法插入说明B——电路模拟第4章导线4.1 引言4.2 简介4.3 互连参数——电容、电阻和电感4.4 导线模型4.5 导线的SPICE模型4.6 小结4.7 进一步探讨第二部分电路设计第5章CMOS反相器5.1 引言5.2 静态CMOS反相器——直观综述5.3 CMOS反相器稳定性的评估——静态特性5.4 CMOS反相器的性能——动态特性5.5 功耗、能量和能量延时5.6 综述:工艺尺寸缩小及其对反相器衡量指标的影响5.7 小结本文由整理提供5.8 进一步探讨第6章CMOS组合逻辑门的设计6.1 引言6.2 静态CMOS设计6.3 动态CMOS设计6.4 设计综述6.5 小结6.6 进一步探讨设计方法插入说明C——如何模拟复杂的逻辑电路设计方法插入说明D——复合门的版图技术第7章时序逻辑电路设计7.1 引言7.2 静态锁存器和寄存器7.3 动态锁存器和寄存器7.4 其他寄存器类型7.5 流水线:优化时序电路的一种方法7.6 非双稳时序电路7.7 综述:时钟策略的选择7.8 小结7.9 进一步探讨第三部分系统设计第8章数字IC的实现策略8.1 引言8.2 从定制到半定制以及结构化阵列的设计方法8.3 定制电路设计8.4 以单元为基础的设计方法8.5 以阵列为基础的实现方法8.6 综述:未来的实现平台8.7 小结8.8 进一步探讨设计方法插入说明E——逻辑单元和时序单元的特性描述设计方法插入说明F——设计综合第9章互连问题9.1 引言9.2 电容寄生效应9.3 电阻寄生效应9.4 电感寄生效应9.5 高级互连技术9.6 综述:片上网络9.7 小结9.8 进一步探讨第10章数字电路中的时序问题10.1 引言10.2 数字系统的时序分类本文由整理提供10.3 同步设计——一个深入的考察10.4 自定时电路设计10.5 同步器和判断器10.6 采用锁相环进行时钟综合和同步10.7 综述:未来方向和展望10.8 小结10.9 进一步探讨设计方法插入说明G——设计验证第11章设计运算功能块11.1 引言11.2 数字处理器结构中的数据通路11.3 加法器11.4 乘法器11.5 移位器11.6 其他运算器11.7 数据通路结构中对功耗和速度的综合考虑11.8 综述:设计中的综合考虑11.9 小结11.10进一步探讨第12章存储器和阵列结构设计12.1 引言12.2 存储器内核12.3 存储器外围电路12.4 存储器的可靠性及成品率12.5 存储器中的功耗12.6 存储器设计的实例研究12.7 综述:半导体存储器的发展趋势与进展12.8 小结12.9 进一步探讨设计方法插入说明H——制造电路的验证和测试本文由整理提供。

第九数字系统设计自动化章数字系统设计自动化9.1 数字系统设计流程概述数字化及其设计自动化;基于设计自动化的设计流程、单元库;EDA技术的发展趋势9.2 硬件描述语言VHDL语言;Verilog HDL语言9.3 设计分析与模拟9.4 自动综合与设计验证自动综合;设计验证9.5 系统封装系统封装第九§9.1 数字系统设计流程概述章v/Vt模拟信号§9.1.1 数字系统及其设计自动化一、数字系统的概念1、自然界物理量:模拟量和数字量(Analog vs.Digital )v/Vt数字信号2、采用数字信号的优势z只有高、低两种电平分别用‘1’‘0’表示;z易于传输信息:抗干扰能力强等;z易于处理信息:有一定的“逻辑思维”能力;z集成度高,通用性强。

数字逻辑电路(数字电路):用来处理数字信号的电子线路。

各种功能是通过逻辑运算和逻辑判断来实现的。

数字逻辑在电子设备或电子系统中的应用3、EDA技术发展的三个阶段:1)早期电子CAD阶段20世纪70年代EDA技术发展初期。

用计算机、二维图形编辑与分析的CAD工具,完成布图布线等高度重复性的繁杂工作。

2)计算机辅助工程CAE阶段20世纪80年代,出现了低密度和,相应的EDA开发工具主要解决电路设计没有完成之前的功能检测等问题。

80年代后期,EDA工具已经可以进行初级的设计描述,综合、优化和设计结果验证。

3) 电子设计自动化EDA阶段20世纪90年代,可编程逻辑器件迅速发展,出现功能强大的全线EDA工具.具有较强抽象描述能力的硬件描述语言(HDL)及高性能综合工具的使用,使过去单功能电子产品开发转向系统级电子产品开发(SOC)。

`开始实现“概念驱动工程”的梦想§9.1.2 基于设计自动化的设计流程基本思想:自顶向下(top-down)的设计方法模拟验证工具:SPICE设计语言:VHDL、Verilog优点:⑴方便了从系统级划分和管理整个项目;⑵简化了设计队伍的管理;⑶减少了不必要的重复;⑷提高了设计的一次成功率。

芯片制造与封装测试物理设计与版图验证逻辑设计与验证寄存器传输级设计与验证功能设计与功能验证NN系统设计与验证产品需求基于设计自动化的设计流程N深亚微米设计流程布局布线逻辑设计行为设计系统功能定义行为仿真与性能评估布局规划Y功能测试图案生成结构仿真与性能评估Y时序分析N后仿真与性能评估测试生成芯片制造YN§9.1.3 单元库单元库信息:z物理版图信息行为模型:高层次描述VHDL/Verilog语言模型时间模型:时序性能,时序模型测试手段电路草图单元标识连线仿真模型§9.1.4 EDA技术的发展趋势摩尔定律(Moore’s Law):每过18个月, IC中晶体管的集成度增加一倍z SOC对EDA软件提出了系统级的仿真能力的要求;z深亚微米设计成功的关键:如何减少互连延迟;z复杂性和集成度的增加对数据管理提出了高要求;z如何减少上市时间(Time-to-Market);z设计的第三维度:低功耗。

第九§9.2 硬件描述语言章§9.2.1 VHDL语言一、什么是VHDL?VHDL--V HSIC HDL超高速集成电路硬件描述语言V—V HSIC (Very High Speed Integrated Circuit) H—H ardwareD—D escriptionL—L anguage二、VHDL的历史z80年代初由美国国防部在实施超高速集成电路(VHSIC)项目时开发的。

z1987年由IEEE 协会批准为IEEE 工业标准,称为IEEE1076-1987。

z各EDA公司相继推出支持VHDL的设计环境。

z1993年被更新为93 标准,即IEEE1076-1993。

进一步提高抽象描述层次,扩展系统描述能力。

三、VHDL的作用1、VHDL打破软、硬件的界限传统的数字系统设计分为:硬件设计(硬件设计人员)软件设计(软件设计人员)VHDL是电子系统设计者和EDA工具之间的界面。

2、VHDL与C、C++的比较:C、C++ 代替汇编等语言VHDL 代替原理图、逻辑状态图等四、VHDL电路设计主要描述数字系统的结构、行为、功能和接口VHDL将一个设计(元件、电路、系统)分为:外部(可视部分:端口)内部(不可视部分:内部功能,算法)外部与内部示意图:器件或子系统ENTITYARCHITECTUREPORTS PROCESS PROCESSPORTS实体(Entity)结构体(Architecture)配置(Configuration)库(Library)、程序包(Package)VHDL 程序基本结构五、VHDL 语言描述模型库、程序包配置(Configuration )实体(Entity )结构体(Architecture )进程/并行结构1)实体(说明)实体(说明):定义系统的输入输出端口语法:ENTITY <entity_name> ISGeneric DeclarationsPort DeclarationsEND <entity_name>; (1076-1987 version)END ENTITY<entity_name> ; ( 1076-1993 version)结构体结构体说明结构体功能描述常数说明数据类型说明信号说明例化元件说明子程序说明块语句BLOCK进程语句PROCESS信号赋值语句子程序调用语句元件例化语句实体与结构体的关系:设计实体结构体1结构体2结构体3结构体n。

一个设计实体可有多个结构体,代表实体的多种实现方式。

2)结构体的语法:ARCHITECTURE结构体名称OF实体名称IS [说明语句]内部信号、常数、数据类型、子程序(函数、过程)、元件等的说明;BEGIN[并行处理(功能描述)语句];END[ARCHITECTURE]结构体名称;注:同一实体的结构体不能同名。

定义语句中的常数、信号不能与实体中的端口同名。

3)配置设计实体结构体1结构体2结构体3结构体n。

一个设计实体的多种实现方式配置:从某个实体的多种结构体描述方式中选择特定的一个。

4)简单配置的语法:CONFIGURATE配置名OF实体名IS FOR选配结构体名END FOR;END配置名;六、数据类型和运算符三种数据对象:常量(Constant)、变量(Variable)信号(Signal)z标准数据类型:整数、实数、位、位矢量、布尔量、字符、字符串、时间、错误等级、自然数、正整数z用户自定义数据类型:枚举类型、整数类型、实数、符点数、数组、存取类型、文件类型、记录、时间z运算符1)逻辑运算符:NOT、AND、OR、NAND、NOR、XOR 2)关系运算符:=、/=、<、<=、>、> =3)算术运算符:+、-、*、/、mod、rem、+(单)、-(单)abs 4)并置运算符:&提问什么是重载运算符?七、基本描述语言z 顺序语句:1)IF 语句2)CASE 语句3)L00P 语句5)REPORT 语句6)RETURN 语句7)NULL 语句z 并法语句:1)Process 进程语句2)并发信号代入语句3)条件信号代入语句4)选择信号代入语句5)Block 语句视频讲解1视频讲解2§9.2.2 Verilog HDL语言什么是Verilog HDL?•Verilog HDL(Hardware Discription Language)一种硬件描述语言,用于从算法级、门级到开关级的多种抽象设计层次的数字系统建模。

Verilog HDL的发展历史1989CADENCE公司购买Verilog版权1983’s Verilog-XL诞生1990Verilog HDL公开发表模拟和数字都适用Verilog2001标准公开发表2001VerilogHDLIEEE1995标准公开发表1995Verilog HDL的发展历史●最初是于1983年由Gateway Design Automation公司(后被Cadence收购)为其模拟器产品开发的硬件建模语言●1990年,Cadence公司成立OVI(Open Verilog International)组织来负责推广Verilog●1995年,IEEE制定了Verilog HDL标准,即IEEE Std 1364 -1995§9.2 硬件描述语言Verilog与VHDL的区别两者的区别:z VHDL侧重于系统级描述,从而更多的为系统级设计人员所采用z Verilog侧重于电路级描述,从而更多的为电路级设计人员所采用一般的Verilog HDL系统设计包括①系统描述设计模块②系统测试模块Ve§9.2 硬件描述语言一、Verilog HDL的描述设计模块1、Verilog基本描述单位:模块①端口信息:模块的输入输出信号。

②逻辑功能:描述模块的输入输出信号的关系。

module是层次化设计的基本构件逻辑描述放在module内部语言的主要特点—模块端口(module ports)•注意模块的名称DFF,端口列表及说明•模块通过端口与外部通信端口在模块名字后的括号中列出端口可以说明为input, output及inout§9.2 硬件描述语言§9.2 硬件描述语言2、Verilog HDL的描述方式在模块中,可以采用下述方式描述一个设计:①数据流描述方式②行为描述方式③结构描述方式④以上方式的混合①数据流描述方式使用连续赋值语句:assign [delay] 赋值线网对象=表达式;半加器的例子module HalfAdder(A, B, Sum, Carry);input A, B;output Sum, Carry;assign Sum=A^B;assign Carry=A&B;endmodule②行为描述方式使用过程语句描述:initial语句:只执行一次always语句:重复执行一个模块内可包含任意多个initial 和always 语句,它们相互并行执行,即,它们的执行顺序与其在模块中的顺序无关always语句:重复执行半加器的例子:module HalfAdder(A, B, Sum, Carry);input A, B;output Sum, Carry;always@(A or B)beginSum=A^B;Carry=A&B;endendmodulemodule muxtwo(out, a, b, sel); input a, b, sel;output out; reg out;always @( sel or a or b)if (! sel) out = a;else out = b;endmodule③结构化描述方式●用Verilog直接描述逻辑图●可使用(1)内置门(基本单元):not, and, or…(2)开关级:nmos, cmos, tran…(3)用户自定义的结构(4)模块实例:其它module单元module twomux(out, a, b, sl); input a, b, sl;output out;not u1 (nsl, sl);and u2 (sela, a, nsl);and u3 (selb, b, sl);or u4 (out, sela, selb); endmoduleVerilog内置门(多输入门)•内置门提供基本的逻辑功能,这些逻辑功能是预定义的(多输入门、多输出门、三态门、MOS开关)多输入门:and,nand,or,nor,xor,xnor格式:门类型实例名(<输出端口>, <控制端口>,<输入端口>) nand nand1(Y, A, B);//2输入与非门xor xor1(Y,A,B,C); //3输入或非门Verilog内置门(多输出门)•内置门提供基本的逻辑功能,这些逻辑功能是预定义(多输入门、多输出门、三态门、MOS开关)多输出门:一个输入,多个输出buf:缓冲器not:反相器如:buf buf1(Out[0],Out[1],Out[2],In);not not2(Out,In);Verilog内置门(三态门)三态门:bufif0, bufif1, notif0, notif1如:bufif0 BF1(Dout,Ctrl,Din);// 当Ctrl=1时,Dout=Din,Ctrl=0时,Dout=z基本单元名称功能bufif1 条件缓冲器,逻辑1 使能bufif0 条件缓冲器,逻辑0 使能notif1 条件反相器,逻辑1 使能notif0 条件反相器,逻辑1 使能带条件的基本单元(续)•条件基本单元有三个端口:输出、数据输入、使能输入Verilog内置门(MOS开关)•内置门提供基本的逻辑功能,这些逻辑功能是预定义的(多输入门、多输出门、三态门、MOS开关)MOS开关:控制数据流动的开关:nmos, cmos, pmos格式:xmos实例名(out, in,<控制端>)例:nmos N1(Out, In, Ctrl);cmos CMOS2(Out, In, NCtrl, PCtrl);module bus_xcvr( bus_a, bus_b, en_a_b, en_b_a);inout bus_a, bus_b;input en_a_b, en_b_a;bufif1 b1 (bus_b, bus_a, en_a_b); bufif1 b2 (bus_a, bus_b, en_b_a);// Structural module logicendmodule。