VHDL程序设计题.pptx

- 格式:pptx

- 大小:117.77 KB

- 文档页数:18

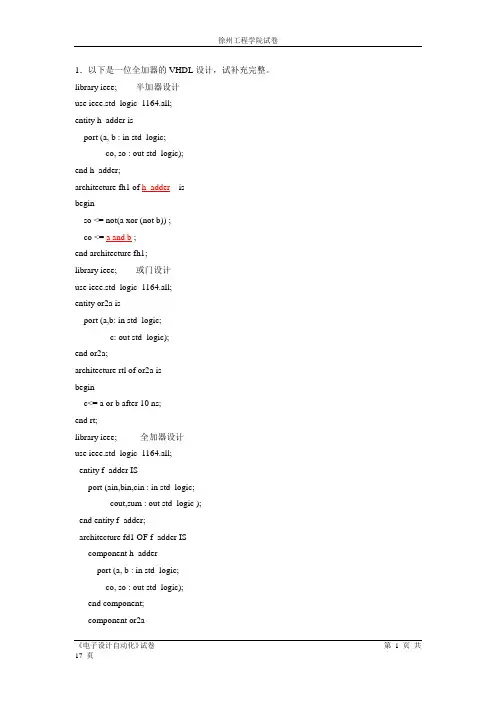

1.以下是一位全加器的VHDL设计,试补充完整。

library ieee; --半加器设计use ieee.std_logic_1164.all;entity h_adder isport (a, b : in std_logic;co, so : out std_logic);end h_adder;architecture fh1 of h_adder isbeginso <= not(a xor (not b)) ;co <= a and b ;end architecture fh1;library ieee; --或门设计use ieee.std_logic_1164.all;entity or2a isport (a,b: in std_logic;c: out std_logic);end or2a;architecture rtl of or2a isbeginc<= a or b after 10 ns;end rt;library ieee; --全加器设计use ieee.std_logic_1164.all;entity f_adder ISport (ain,bin,cin : in std_logic;cout,sum : out std_logic );end entity f_adder;architecture fd1 OF f_adder IScomponent h_adderport (a, b : in std_logic;co, so : out std_logic);end component;component or2aport (a,b: in std_logic;c: out std_logic);end component;signal d, e, f : std_logic;beginu1 : h_adder port map(a=>ain, b=>bin, co=>d, so=>e);u2 : h_adder port map (a=>e, b=>cin, co=>f, so=>sum);u3 : or2a port map (a=>d, b=>f, c=>cout);end architecture fd1;2.以下是含有使能端且具有同步清零的加减计数器的VHDL设计,试补充完整。

VHDL 程序设计题VHDL程序设计题四、编程题(共50分)1、请补全以下二选一VHDL程序(本题10分)En tity mux isport(dO,d1,sel:in bit;q:out BIT ); (2)end mux;architecture conn ect of MUX is (4)sig nal tmpl, TMP2 ,tmp3:bit; (6)begincale:blockbegintmp1<=d0 and sel;tmp2<=d1 and (not sel)tmp3<= tmpl and tmp2;q <= tmp3; (8)end block cale;end CONNECT : (10)2、编写一个2输入与门的VHDL程序,请写出库、程序包、实体、构造体相关语句,将端口定义为标准逻辑型数据结构(本题10分)LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL; ( 2)ENTITY nand2 ISPORT (a,b:IN STD_LOGIC; (4)y:OUT STD_LOGIC); (6)END nan d2;ARCHITECTURE nan d2_1 OF nand2 IS (8)BEGINy <= a NAND b;--与y <=NOT( a AND b);等价 (10) END nan d2_1;3、根据下表填写完成一个3-8线译码器的VHDL程序(16分)LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY decoder_3_to_8 ISPORT (a,b,c,g1,g2a,g2b:IN STD_LOGIC;(2)y:OUT STD_L0GIC_VECT0R(7 DOWNTO 0)):END decoder_3_to_8;ARCHITECTURE rtl OF decoder_3_to_8 ISSIGNAL in data:STD_LOGIC_VECTOR (2 DOWNTO 0);(4)BEGINin data <= c & b & a;(6)PROCESS (in data,g1,g2a,g2b)BEGINIF (g1 = '1' AND g2a = 'O' AND g2b = 'O' ) THEN(8)CASE in data ISWHEN "000"=> y <= "11111110";WHEN "001" => y <= "11111101";WHEN "010" => y <= "11111011";(10)WHEN "011" => y <= "11110111";WHEN "100" => y <= "11101111";WHEN "101" => y <= "11011111";WHEN "110" => y <= "10111111";(12)WHEN "111" => y <= "01111111";WHEN OTHERS=> y <= "XXXXXXXX"; END CASE;ELSEy <= "11111111";END IF;END PROCESS;(16)END rtl;4、三态门电原理图如右图所示,真值表如左图所示,请完成其VHDL程序构造体部分。

![[计算机软件及应用]第4章VHDL设计实例PPT课件](https://uimg.taocdn.com/0dcd63c0a2161479161128c0.webp)

VHDL程序填空题(一) 在下面横线上填上合适的VHDL关键词,完成2选1多路选择器的设计。

LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;1 MUX21 ISPORT(SEL:IN STD_LOGIC;A,B:IN STD_LOGIC;Q: OUT STD_LOGIC );END MUX21;2 BHV OF MUX21 ISBEGINQ<=A WHEN SEL=’1’ EL SE B;END BHV;(二) 在下面横线上填上合适的语句,完成BCD-7段LED显示译码器的设计。

LIBRARY IEEE ;USE IEEE.STD_LOGIC_1164.ALL;ENTITY BCD_7SEG ISPORT( BCD_LED : IN STD_LOGIC_VECTOR(3 DOWNTO 0);LEDSEG : OUT STD_LOGIC_VECTOR(6 DOWNTO 0));END BCD_7SEG;ARCHITECTURE BEHAVIOR OF BCD_7SEG ISBEGINPROCESS(BCD_LED)3IF BCD_LED="0000" THEN LEDSEG<="0111111";ELSIF BCD_LED="0001" THEN LEDSEG<="0000110";ELSIF BCD_LED="0010" THEN LEDSEG<= 4 ;ELSIF BCD_LED="0011" THEN LEDSEG<="1001111";ELSIF BCD_LED="0100" THEN LEDSEG<="1100110";ELSIF BCD_LED="0101" THEN LEDSEG<="1101101";ELSIF BCD_LED="0110" THEN LEDSEG<="1111101";ELSIF BCD_LED="0111" THEN LEDSEG<="0000111";ELSIF BCD_LED="1000" THEN LEDSEG<="1111111";ELSIF BCD_LED="1001" THENLEDSEG<="1101111";ELSE LEDSEG<= 5 ;END IF;END PROCESS;END BEHAVIOR;(三) 在下面横线上填上合适的语句,完成数据选择器的设计。

VHDL程序填空题(一) 在下面横线上填上合适的VHDL关键词,完成2选1多路选择器的设计。

LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;1 MUX21 ISPORT(SEL:IN STD_LOGIC;A,B:IN STD_LOGIC;Q: OUT STD_LOGIC );END MUX21;2 BHV OF MUX21 ISBEGINQ<=A WHEN SEL=’1’ ELSE B;END BHV;(二) 在下面横线上填上合适的语句,完成BCD-7段LED显示译码器的设计。

LIBRARY IEEE ;USE IEEE.STD_LOGIC_1164.ALL;ENTITY BCD_7SEG ISPORT( BCD_LED : IN STD_LOGIC_VECTOR(3 DOWNTO 0);LEDSEG : OUT STD_LOGIC_VECTOR(6 DOWNTO 0));END BCD_7SEG;ARCHITECTURE BEHA VIOR OF BCD_7SEG ISBEGINPROCESS(BCD_LED)3IF BCD_LED="0000" THEN LEDSEG<="0111111";ELSIF BCD_LED="0001" THEN LEDSEG<="0000110";ELSIF BCD_LED="0010" THEN LEDSEG<= 4 ;ELSIF BCD_LED="0011" THEN LEDSEG<="1001111";ELSIF BCD_LED="0100" THEN LEDSEG<="1100110";ELSIF BCD_LED="0101" THEN LEDSEG<="1101101";ELSIF BCD_LED="0110" THEN LEDSEG<="1111101";ELSIF BCD_LED="0111" THEN LEDSEG<="0000111";ELSIF BCD_LED="1000" THEN LEDSEG<="1111111";ELSIF BCD_LED="1001" THEN LEDSEG<="1101111";ELSE LEDSEG<= 5 ;END IF;END PROCESS;END BEHA VIOR;(三) 在下面横线上填上合适的语句,完成数据选择器的设计。