有限状态机及其扩展

- 格式:ppt

- 大小:991.00 KB

- 文档页数:46

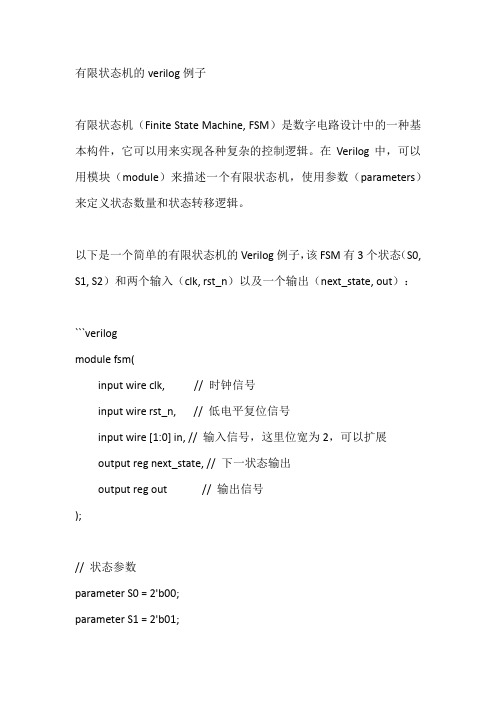

有限状态机的verilog例子有限状态机(Finite State Machine, FSM)是数字电路设计中的一种基本构件,它可以用来实现各种复杂的控制逻辑。

在Verilog中,可以用模块(module)来描述一个有限状态机,使用参数(parameters)来定义状态数量和状态转移逻辑。

以下是一个简单的有限状态机的Verilog例子,该FSM有3个状态(S0, S1, S2)和两个输入(clk, rst_n)以及一个输出(next_state, out):```verilogmodule fsm(input wire clk, // 时钟信号input wire rst_n, // 低电平复位信号input wire [1:0] in, // 输入信号,这里位宽为2,可以扩展output reg next_state, // 下一状态输出output reg out // 输出信号);// 状态参数parameter S0 = 2'b00;parameter S1 = 2'b01;parameter S2 = 2'b10;// 状态寄存器reg [1:0] state;// 状态转移逻辑always @(posedge clk or negedge rst_n) beginif (!rst_n) begin// 当处于复位状态时,状态寄存器和输出都初始化为0state <= S0;out <= 1'b0;end else begin// 根据当前状态和输入信号,更新下一状态和输出case (state)S0: beginnext_state <= S1;out <= 1'b1;endS1: beginnext_state <= S2;out <= 1'b0;endS2: beginnext_state <= S0;out <= 1'b1;enddefault: beginnext_state <= S0;out <= 1'b0;endendcaseendendendmodule```在这个例子中:- `clk` 是时钟信号。

有限状态机原理

有限状态机(Finite State Machine, FSM)是一种计算模型,用于描述系统或算法的行为。

它由一组有限个状态、一组可能的输入信号和一组定义状态转换规则的状态转换函数组成。

在任意时刻,FSM都处于一个特定的状态,等待输入信号触发状态转换。

有限状态机具有以下基本特点:

1. 状态:有限状态机有一组预定义的状态,每个状态表示系统或算法的一种行为或状态。

2. 输入信号:系统或算法接收一组可能的输入信号,每个输入信号可能触发状态的转换或执行某种操作。

3. 状态转换:有限状态机通过状态转换函数定义可能的状态转换规则,以及在特定输入信号下从一个状态转换到另一个状态的动作或操作。

4. 动作:状态转换可以伴随着执行特定的动作或操作,用于改变系统的状态或执行一些其他的操作。

有限状态机应用广泛,可以用于描述各种系统的行为,如计算机中的指令执行、网络通信协议、自动控制系统等。

它可以帮助开发者理清系统的行为逻辑,简化复杂系统的设计和实现。

有限状态机还可以通过组合、嵌套等方式进行组合和扩展,以应对更加复杂的问题。

状态机分类

状态机是一种计算模型,它将计算过程看作状态的转换。

根据状态机的特性和实现方式的不同,我们可以将状态机分为以下几类:

1. 有限状态自动机(FSM)

有限状态自动机是最简单的状态机,它包含一组状态和一组转移条件。

在任何时候,状态机只能处于其中一个状态,而转移条件定义了从一个状态到另一个状态的转换。

有限状态自动机通常用于解决识别问题,例如正则表达式匹配。

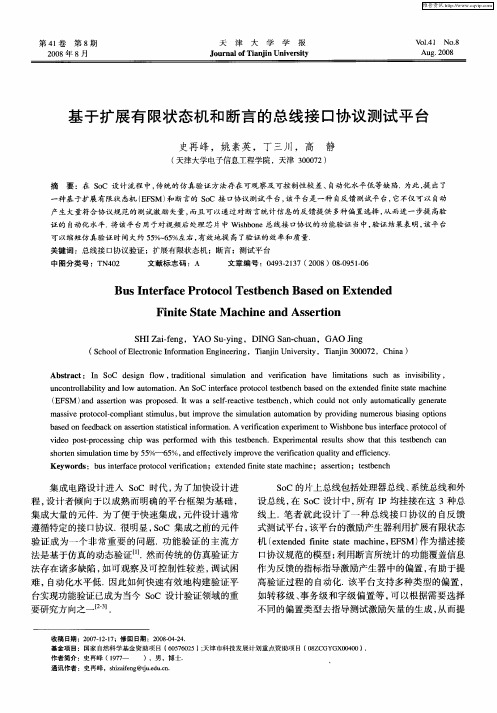

2. 基于事件的状态机(EFSM)

基于事件的状态机扩展了有限状态自动机的转移条件,使其能够对事件做出响应。

事件可以是内部事件,例如超时或计数器溢出,也可以是外部事件,例如输入或输出。

基于事件的状态机通常用于实现协议或通信模型。

3. 层次状态机(HSM)

层次状态机是一种分层的状态机,它将状态和转移条件分组成层。

每一层都有自己的状态和转移条件,而底层状态机可以控制上层状态机的转换。

层次状态机通常用于处理复杂的控制流程,例如嵌入式系统或游戏引擎。

4. 反应式状态机(RSM)

反应式状态机是一种特殊的状态机,它可以对外部事件做出反应并改变其内部状态。

反应式状态机还可以将其状态和行为分成可

重用的模块,从而使状态机模型更加模块化和可扩展。

反应式状态机通常用于实现基于事件的系统和应用程序。

总之,状态机是一种强大的计算模型,可用于建模和实现各种计算问题。

通过了解不同类型的状态机,我们可以选择最适合特定问题的状态机实现方式。