EDA数字钟

- 格式:doc

- 大小:860.00 KB

- 文档页数:19

实验报告实验四多功能数字钟设计一、实验目的1、学习复杂数字电路系统的设计。

2、设计一个多功能数字钟。

二、实验要求1.数字显示当前的小时、分钟;2.可以预置为12小时计时显示和24小时计时显示;3.一个调节键,用于调节目标数位的数字。

对调节的内容敏感,如调节分钟或秒时,保持按下时自动计数,否则以脉冲计数;4.一个功能键,用于切换不同状态:计时、调时、调分、调秒、调小时制式。

三、实验仪器PC机、Quartus II软件、EDA实验箱四、实验原理1.系统需要两个六十进制计数器用于分钟和秒的计时,为方便译码采用60进制计数器(1)秒计时实验程序如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;USE IEEE.STD_LOGIC_ARITH.ALL;entity second ISport(clk1,rst1:in std_logic;cout1:out std_logic;cq0:out std_logic_vector(3 downto 0);cq1:out std_logic_vector(3 downto 0));END second;ARCHITECTURE behave of second isSIGNAL d: std_logic_vector(3 downto 0);SIGNAL g: std_logic_vector(3 downto 0);BEGINprocess(clk1,rst1,d,g)BEGINif (rst1 ='1') thend <="0000";g <="0000";elsif(clk1'EVENT and clk1='1')thenif(d=9 and g=5)thencout1<='1';elsecout1<='0';end if;if(d=9)thend<="0000";if(g=5)theng<="0000";elseg<=g+1;end if;elsed<=d+1;end if;end if;end process;cq0<=d;cq1<=g;end behave;clk1是时钟信号,rst1是复位信号, cout1作为下一模块分钟设计的时钟信号,cq0,cq1输出信号最后接在动态译管码芯片上。

摘要数字时钟,就是以数字显示取代模拟表盘的钟表,在显示上它用数字反应此时的时间,它还能同时显示时,分,秒,且能够对时,分,秒准确进行校时。

数字时钟是一种用数字电路技术实现时、分、秒计时的装置。

与机械式时钟相比具有更高的准确性和直观性,且无机械装置,具有更长的使用寿命,已得到广泛的使用。

数字钟从原理上讲是一种典型的数字电路,一般是由振荡器、分频器、计数器、显示器等几部分组成。

其中包括了组合逻辑电路和时序电路。

数字钟的设计方法有许多种,例如:可用中小规模集成电路组成电子钟;也可以利用专用的电子钟芯片配以显示电路及其所需要的外围电路组成电子钟;还可以利用单片机来实现电子钟等等。

本设计采用EDA技术,以硬件描述语言Verilog HDL为系统逻辑描述手段设计文件,在QUARTUS II工具软件环境下,采用自顶向下的设计方法,由各个基本模块共同构建了一个基于FPGA的数字钟。

数字时钟以其体积小、重量轻、抗干扰能力强、对环境要求高、高精确性、容易开发等特性,在工业控制系统、智能化器仪表、办公自动化等诸多领域取得了极为广泛的应用,诸如定时自动报警、按时自动打铃、时间程序自动控制、定时广播、自动启闭路灯、定时开关烘箱、通断动力设备、甚至各种定时电气的自动启用等。

关键词:EDA、QuartusII、Verilog HDL、FPGA芯片、数字时钟等AbstractDigital clock is with digital display to replace analog dial watch, in the show it with digital reaction at this time, it can display at the same time, minutes and seconds, and can pair, minutes and seconds precise timing.Digital clock is a digital circuit technology to achieve time, minutes and seconds of the device. Compared with the mechanical clock has higher accuracy and intuitive, and no mechanical device, has a longer life, has been widely used. Digital clock from the principle of speaking is a typical digital circuit, generally by the oscillator, frequency divider, counter, display and other parts of the composition. The combination logic circuit and the sequential circuit are included in the circuit. Digital clock design, there are many methods. For example: available small scale integrated circuit composition electronic clock; can also use special chip electronic clock with to display circuit and its peripheral circuit composed of electronic clock; can also be used to achieve single-chip electronic clock and so on.This design using EDA technology, the Hardware Description Language Verilog HDL logic system description method of design documents, in the Quartus II software environment by top-down design method, by all the basic modules work together to build a based on FPGA digital clock.Digital clock with the volume small, light weight, strong anti-interference ability, on the environment requirements high, high precision, ease of development, and so on, in the fields of industrial control system, intelligent of instrumentation, office automation, made extremely widely used, such as timing automatic alarm, timely automatic bell, a time program automatic control, regular radio, automatic opening and closing lights, oven timer switch, on-off power equipment, and even a variety of timing electric automatically enabled.Keywords: EDA, QuartusII, Verilog HDL,FPGA chip, Digital clock, etc.摘要 (1)第一章绪论 (4)1.1选题意义与研究现状 (4)1.2国内外研究及趋势 (4)第二章EDA技术 (6)2.1 EDA技术简介 (6)2.2 EDA技术特点 (6)2.3 EDA技术的发展历程 (6)第三章 QuartusⅡ,FPGA的简介 (9)3.1 Quartus II简介 (9)3.2 FPGA简介 (9)3.3 FPGA系统设计流程 (11)3.4本设计所用黑金开发板AX301简介 (12)第四章数字时钟总体设计方案 (14)4.2 数字钟的工作原理 (14)第五章数字时钟的具体设计 (15)5.1 本设计的顶层图 (15)5.2 时钟控制模块 (15)5.2.1信号定义 (15)5.2.2分频模块 (16)5.2.3走时模块 (16)5.3显示模块 (20)第六章程序的验证与修改 (25)6.1程序导入 (25)6.2开发板演示 (25)第七章总结与展望 (27)7.1论文总结 (27)7.2后续展望 (27)致谢 ................................................................................................................... 错误!未定义书签。

eda课程设计数字钟实验一、课程目标知识目标:1. 学生能够理解数字时钟的基本原理,掌握EDA工具的使用方法,并能够运用Verilog HDL语言描述数字时钟的基本功能。

2. 学生能够掌握数字时钟设计中涉及的计数器、分频器等基本模块的工作原理和设计方法。

3. 学生了解数字时钟系统的层次化设计方法,并能够根据设计需求进行模块划分。

技能目标:1. 学生能够运用所学知识,使用EDA工具设计并实现一个简单的数字时钟,培养动手实践能力。

2. 学生能够通过分析问题、解决问题,培养逻辑思维能力和团队协作能力。

情感态度价值观目标:1. 学生通过实际操作,体验数字电路设计的乐趣,激发对电子信息技术学习的兴趣。

2. 学生在课程学习过程中,培养严谨的科学态度和良好的工程意识,提高对电子产品质量的追求。

3. 学生通过团队合作,培养沟通协作能力,增强团队意识和集体荣誉感。

课程性质:本课程为电子设计自动化(EDA)的实践课程,结合数字电路设计原理,让学生通过实际操作,掌握数字时钟的设计与实现。

学生特点:学生已经具备一定的电子信息技术基础,对数字电路有一定的了解,具备基本的编程能力。

教学要求:注重理论与实践相结合,强调学生的动手实践能力,鼓励学生独立思考和团队协作,培养解决实际问题的能力。

通过本课程的学习,使学生能够将所学知识应用于实际工程项目中,提高学生的综合素质。

二、教学内容本课程教学内容主要包括以下三个方面:1. 数字时钟原理及设计方法- 理解数字时钟的基本原理,包括计时原理、分频原理等。

- 学习数字时钟的模块化设计方法,掌握计数器、分频器等基本模块的设计与实现。

关联教材章节:第五章《数字时钟的设计与应用》2. EDA工具及Verilog HDL语言- 学习EDA工具的使用方法,如Quartus II等。

- 掌握Verilog HDL语言的基本语法和编程技巧,能够使用Verilog描述数字电路。

关联教材章节:第四章《EDA工具与Verilog HDL编程》3. 数字时钟设计与实现- 学习数字时钟的整体设计流程,包括模块划分、代码编写、仿真验证等。

eda课程设计数字钟设计一、课程目标知识目标:1. 学生能理解EDA(电子设计自动化)的基本概念,掌握数字钟的基本原理和设计流程。

2. 学生能描述数字钟的各个模块功能,如计时、显示、调整等,并理解它们之间的协同工作方式。

3. 学生掌握Verilog等硬件描述语言的基本语法,能够利用EDA工具进行基本的数字电路设计和仿真。

技能目标:1. 学生能够运用所学知识,使用EDA工具设计简单的数字时钟电路,并进行功能仿真。

2. 学生通过小组合作,培养团队协作能力和问题解决能力,提高工程实践和项目管理的初步技能。

3. 学生能够运用批判性思维分析设计过程中的问题,提出优化方案,并对设计方案进行改进。

情感态度价值观目标:1. 学生通过数字钟的设计实践,培养对电子工程领域的兴趣和探究精神,激发创新意识和创造潜能。

2. 学生在学习过程中,形成严谨的科学态度和良好的工程意识,认识到技术对日常生活的影响。

3. 学生在小组合作中,学会相互尊重和沟通,培养积极向上的团队精神,增强集体荣誉感。

课程性质分析:本课程为实践性较强的电子设计课程,要求学生将理论知识与实际操作相结合,通过动手实践,深化对电子设计自动化原理的理解。

学生特点分析:针对高中年级学生,已有一定的电子基础和逻辑思维能力,对新鲜事物充满好奇心,具备自主学习的能力。

教学要求:课程要求教师通过引导和启发,帮助学生将抽象的理论具体化,通过项目式的教学方法,使学生能够将所学知识应用于实际问题的解决中。

二、教学内容本课程教学内容围绕数字钟设计的全过程,分为以下三个部分:1. 理论知识学习:- 电子设计自动化(EDA)基本概念与原理;- 数字时钟的组成、工作原理及各模块功能;- Verilog硬件描述语言的基本语法及使用方法;- 相关电子元器件的特性和应用。

2. 实践操作部分:- 使用EDA工具(如ModelSim、Quartus等)进行基本操作;- 设计数字钟的各个模块,并进行功能仿真;- 对设计过程中出现的问题进行分析,提出优化方案;- 完成数字钟整体设计与调试。

eda数字电子钟课程设计一、课程目标知识目标:1. 让学生理解数字电子时钟的基本原理,掌握EDA技术及其在数字电子时钟中的应用。

2. 使学生掌握数字电子时钟的设计流程,包括硬件设计、软件编程及系统调试。

3. 让学生掌握时钟信号的产生、计数、显示等模块的工作原理和电路设计。

技能目标:1. 培养学生运用EDA工具(如Protel、Multisim等)进行电路设计与仿真测试的能力。

2. 培养学生具备编程和调试数字电子时钟程序的基本技能,提高实际动手操作能力。

3. 培养学生团队协作、沟通表达、问题分析和解决的能力。

情感态度价值观目标:1. 培养学生对电子工程学科的兴趣,激发学生学习热情,形成积极的学习态度。

2. 培养学生具有创新意识和实践精神,鼓励学生勇于尝试,不断优化设计方案。

3. 培养学生关注社会发展,了解电子产品在生活中的应用,提高社会责任感和使命感。

分析课程性质、学生特点和教学要求,本课程目标将分解为以下具体学习成果:1. 学生能够独立完成数字电子时钟的电路设计和程序编写。

2. 学生能够运用EDA工具进行电路仿真测试,分析并解决设计中出现的问题。

3. 学生能够以团队形式进行项目汇报,展示设计成果,接受提问并给予解答。

4. 学生通过课程学习,提升对电子工程的兴趣,树立正确的价值观和人生观。

二、教学内容根据课程目标,本章节教学内容主要包括以下三个方面:1. 数字电子时钟原理及EDA技术概述- 时钟信号的产生与计数原理- 数字电子时钟的组成与工作原理- EDA技术简介及其在数字电子时钟设计中的应用2. 数字电子时钟设计与实现- 硬件设计:时钟信号电路、计数器电路、显示电路等- 软件编程:基于单片机的程序编写,实现时钟功能- 系统调试:电路测试、程序调试及优化3. 教学实践与项目汇报- 实践操作:运用EDA工具进行电路设计与仿真测试- 项目实施:分组进行数字电子时钟设计,培养学生的团队协作能力- 项目汇报:展示设计成果,锻炼学生的沟通表达和问题分析解决能力教学内容安排和进度如下:1. 第一周:数字电子时钟原理及EDA技术概述2. 第二周:硬件设计与软件编程基础3. 第三周:系统调试与优化4. 第四周:实践操作与项目实施5. 第五周:项目汇报与评价教学内容与教材章节关联如下:1. 《电子技术基础》第三章:数字电路基础2. 《单片机原理与应用》第四章:单片机程序设计3. 《EDA技术及应用》第二章:EDA工具使用与电路设计实例三、教学方法针对本章节内容,采用以下多样化的教学方法,以激发学生的学习兴趣和主动性:1. 讲授法:用于对基本原理和概念进行系统讲解,如数字电子时钟的工作原理、EDA技术概述等。

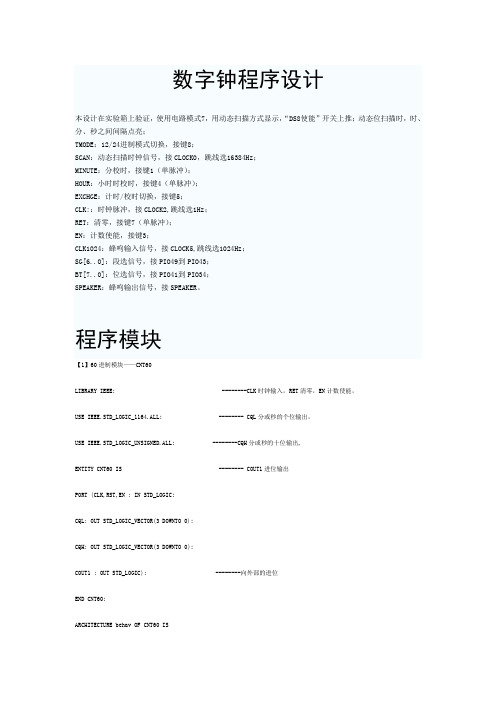

数字钟程序设计本设计在实验箱上验证,使用电路模式7,用动态扫描方式显示,“DS8使能”开关上推;动态位扫描时,时、分、秒之间间隔点亮;TMODE:12/24进制模式切换,接键8;SCAN:动态扫描时钟信号,接CLOCK0,跳线选16384Hz;MINUTE:分校时,接键1(单脉冲);HOUR:小时时校时,接键4(单脉冲);EXCHGE:计时/校时切换,接键5;CLK::时钟脉冲,接CLOCK2,跳线选1Hz;RET:清零,接键7(单脉冲);EN:计数使能,接键3;CLK1024:蜂鸣输入信号,接CLOCK5,跳线选1024Hz;SG[6..0]:段选信号,接PIO49到PIO43;BT[7..0]:位选信号,接PIO41到PIO34;SPEAKER:蜂鸣输出信号,接SPEAKER。

程序模块【1】60进制模块——CNT60LIBRARY IEEE; --------CLK时钟输入,RET清零,EN计数使能,USE IEEE.STD_LOGIC_1164.ALL; -------- CQL分或秒的个位输出,USE IEEE.STD_LOGIC_UNSIGNED.ALL; --------CQH分或秒的十位输出,ENTITY CNT60 IS -------- COUT1进位输出PORT (CLK,RST,EN : IN STD_LOGIC;CQL: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);CQH: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);COUT1 : OUT STD_LOGIC); --------向外部的进位END CNT60;ARCHITECTURE behav OF CNT60 ISSIGNAL CQI0: STD_LOGIC_VECTOR (3 DOWNTO 0);SIGNAL CQI1: STD_LOGIC_VECTOR (3 DOWNTO 0);SIGNAL COUT0 : STD_LOGIC; ------低位向高位的进位BEGINPROCESS(CLK,RST,EN) -------十进制BEGINIF RST='1' THEN CQI0 <=(OTHERS =>'0');ELSIF CLK'EVENT AND CLK='1' THENIF EN ='1' THENIF CQI0 <9 THEN CQI0 <=CQI0+1;ELSE CQI0 <=(OTHERS=>'0');END IF;END IF;IF CQI0 = 9 THEN COUT0 <= '1';ELSE COUT0<='0';END IF;END IF;END PROCESS;CQL<=CQI0;PROCESS(COUT0,RST) ------六进制BEGINIF RST='1' THEN CQI1 <=(OTHERS =>'0');ELSIF COUT0'EVENT AND COUT0='1' THENIF CQI1<5 THEN CQI1<=CQI1+1;ELSE CQI1<=(OTHERS=>'0');END IF;IF CQI1=5 AND CQI0=9 THEN COUT1<='1';ELSE COUT1<='0';END IF;END IF;END PROCESS;CQH<=CQI1;END behav;【2】24|12进制模块——CNT24LIBRARY IEEE; ---------CLK输入分的进位信号,RET清零,EN计数使能, USE IEEE.STD_LOGIC_1164.ALL; ----------MODE为12和24进制的切换,USE IEEE.STD_LOGIC_UNSIGNED.ALL; --------- CQL小时的个位输出,CQH小时的十位输出ENTITY CNT24 ISPORT (CLK,RST,EN,MODE: IN STD_LOGIC;CQL: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);CQH: OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END CNT24;ARCHITECTURE behav OF CNT24 ISSIGNAL CQI0: STD_LOGIC_VECTOR (3 DOWNTO 0);SIGNAL CQI1: STD_LOGIC_VECTOR (3 DOWNTO 0);SIGNAL CQI2: STD_LOGIC_VECTOR (3 DOWNTO 0);SIGNAL CQI3: STD_LOGIC_VECTOR (3 DOWNTO 0);BEGINP1: PROCESS(CLK,RST,EN) --------24进制模式 BEGINIF RST='1' THENCQI0 <=(OTHERS =>'0');CQI1 <=(OTHERS =>'0');ELSIF CLK'EVENT AND CLK='1' THENIF EN ='1' THENIF CQI1<2 THENIF CQI0<9 THENCQI0<=CQI0+1;ELSE CQI0<=(OTHERS=>'0');CQI1<=CQI1+1;END IF;ELSIF CQI0<3 THENCQI0<=CQI0+1;ELSE CQI0<=(OTHERS=>'0');CQI1<=(OTHERS=>'0'); END IF;END IF;END IF;END PROCESS P1;P2: PROCESS(CLK,RST,EN) ------12进制模式BEGINIF RST='1' THENCQI2 <=(OTHERS =>'0');CQI3 <=(OTHERS =>'0');ELSIF CLK'EVENT AND CLK='1' THENIF EN ='1' THENIF CQI3<1 THENIF CQI2<9 THENCQI2<=CQI2+1;ELSE CQI2<=(OTHERS=>'0');CQI3<=CQI3+1;END IF;ELSIF CQI2<2 THENCQI2<=CQI2+1;ELSE CQI2<="0001";CQI3<=(OTHERS=>'0');END IF;END IF;END IF;END PROCESS P2;P3: PROCESS(MODE) ------MODE=’1’为24进制,MODE=’0’为12进制 BEGINCASE MODE ISWHEN '1'=> CQL<=CQI0;CQH<=CQI1;WHEN '0'=> CQL<=CQI2;CQH<=CQI3;WHEN OTHERS=>NULL;END CASE;END PROCESS P3;END behav;【3】控制逻辑模块——CONTROLLIBRARY IEEE; -------EXCHGE校时与计时模式控制,USE IEEE.STD_LOGIC_1164.ALL; -------MINUTE手动分校时USE IEEE.STD_LOGIC_UNSIGNED.ALL; -------HOUR手动时校时ENTITY CONTROL IS -------CY0,CY1分别接受秒和分的进位信号PORT (MINUTE,HOUR,EXCHGE,CY0,CY1: IN STD_LOGIC; ------CLK0,CLK1分别控制分和小时的时钟脉冲CLK0: OUT STD_LOGIC;CLK1: OUT STD_LOGIC);END CONTROL;ARCHITECTURE behav OF CONTROL ISSIGNAL A0: STD_LOGIC;SIGNAL A1: STD_LOGIC;BEGINP1: PROCESS(EXCHGE,MINUTE,HOUR)BEGINIF EXCHGE='1' THENA0<=MINUTE;A1<=HOUR;END IF;END PROCESS P1;P2: PROCESS(EXCHGE,CY0,CY1) -------EXCHGE=’1’校时模式,EXCHGE=’0’为计时模式 BEGINIF EXCHGE='1' THENCLK0<=A0;CLK1<=A1;ELSE CLK0<=CY0;CLK1<=CY1;END IF;END PROCESS P2;END ARCHITECTURE behav;【4】动态扫描模块——SCAN_LEDLIBRARY IEEE; -------SCAN动态扫描时钟信号USE IEEE.STD_LOGIC_1164.ALL; -------DIN接受时、分、秒数据USE IEEE.STD_LOGIC_UNSIGNED.ALL; -------SG输出段选信号ENTITY SCAN_LED IS -------BT输出位选信号PORT(SCAN : IN STD_LOGIC;DIN:IN STD_LOGIC_VECTOR(23 DOWNTO 0);SG:OUT STD_LOGIC_VECTOR(6 DOWNTO 0);BT:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END;ARCHITECTURE one OF SCAN_LED ISSIGNAL CNT6:STD_LOGIC_VECTOR(2 DOWNTO 0);SIGNAL D:STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINP1:PROCESS(SCAN)BEGINIF SCAN'EVENT AND SCAN='1' THENIF CNT6<5 THENCNT6<=CNT6+1;ELSE CNT6<="000";END IF;END IF;END PROCESS P1;P2:PROCESS(CNT6) --------位选BEGINCASE CNT6 ISWHEN"000"=> BT <="00000001"; --------时、分、秒之间隔一个数码管显示 WHEN"001"=> BT <="00000010";WHEN"010"=> BT <="00001000";WHEN"011"=> BT <="00010000";WHEN"100"=> BT <="01000000";WHEN"101"=> BT <="10000000";WHEN OTHERS => NULL;END CASE;END PROCESS P2;P4: PROCESS(CNT6)BEGINCASE CNT6 ISWHEN"000"=> D <=DIN(3 DOWNTO 0);WHEN"001"=> D <=DIN(7 DOWNTO 4);WHEN"010"=> D <=DIN(11 DOWNTO 8);WHEN"011"=> D <=DIN(15 DOWNTO 12);WHEN"100"=> D <=DIN(19 DOWNTO 16);WHEN"101"=> D <=DIN(23 DOWNTO 20);WHEN OTHERS=>NULL;END CASE;END PROCESS P4;P3:PROCESS(D) -------段选BEGINCASE D ISWHEN "0000" =>SG<="0111111";WHEN "0001" =>SG<="0000110";WHEN "0010" =>SG<="1011011";WHEN "0011" =>SG<="1001111";WHEN "0100" =>SG<="1100110";WHEN "0101"=>SG<="1101101";WHEN "0110" =>SG<="1111101";WHEN "0111" =>SG<="0000111";WHEN "1000" =>SG<="1111111";WHEN "1001" =>SG<="1101111";WHEN OTHERS=>NULL;END CASE;END PROCESS P3;END ARCHITECTURE one;【5】整点报时模块——ALARMLIBRARY IEEE; ------ML输入分个位,MH输入分十位USE IEEE.STD_LOGIC_1164.ALL; ------SL输入秒个位,SH输入秒十位USE IEEE.STD_LOGIC_UNSIGNED.ALL; ------CLK输入1024Hz时钟脉冲ENTITY ALARM IS ------SPEAKER输出报时信号PORT (ML: IN STD_LOGIC_VECTOR(3 DOWNTO 0);MH: IN STD_LOGIC_VECTOR(3 DOWNTO 0);SL: IN STD_LOGIC_VECTOR(3 DOWNTO 0);SH: IN STD_LOGIC_VECTOR(3 DOWNTO 0);CLK: IN STD_LOGIC;SPEAKER: OUT STD_LOGIC);END ALARM;ARCHITECTURE behav OF ALARM ISSIGNAL DIV2CLK: STD_LOGIC;BEGINPROCESS(CLK)BEGIN ----------实验箱的可用时钟有限,1024Hz作高音信号 IF CLK'EVENT AND CLK='1' THEN -----------1024Hz时钟脉冲2分频,产生蜂鸣低音信号 DIV2CLK<=NOT DIV2CLK;END IF;END PROCESS;PROCESS(MH,ML,SH,SL)BEGINIF MH=5 AND ML=9 THENIF SH=5 THENIF (SL=1 OR SL=3 OR SL=5 OR SL=7) THEN -------51、53、55、57秒输出低音信号SPEAKER<=DIV2CLK;ELSIF (SL=9) THEN --------59秒输出高音信号SPEAKER<=CLK;ELSE SPEAKER<='0';END IF;ELSE SPEAKER<='0';END IF;ELSE SPEAKER<='0';END IF;END PROCESS;END ARCHITECTURE behav;【6】顶层实体——CLOCKLIBRARY IEEE; ------CLK接1Hz时钟脉冲,USE IEEE.STD_LOGIC_1164.ALL; ------ RET接清零键,EN接计数使能键,ENTITY CLOCK IS ------SCAN接CLK0时钟扫描信号PORT(CLK,EN,RST,SCAN,TMODE,EXCHGE:IN STD_LOGIC; ------TMODE12|24进制切换HOUR,MINUTE,CLK1024:IN STD_LOGIC; -------EXCHGE计时|校时模式控制SPEAKER: OUT STD_LOGIC; -------HOUR手动时校时SG:OUT STD_LOGIC_VECTOR(6 DOWNTO 0); -------MINUTE手动分校时BT:OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); ------CLK1024接1024Hz时钟脉冲END ENTITY; -------SG输出段选信号ARCHITECTURE STRUC OF CLOCK IS -------BT输出位选信号COMPONENT CNT60 ------SPEAKER接蜂鸣器PORT (CLK,RST,EN : IN STD_LOGIC;CQL: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);CQH: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);COUT1 : OUT STD_LOGIC);END COMPONENT;COMPONENT CNT24PORT (CLK,RST,EN,MODE: IN STD_LOGIC;CQL: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);CQH: OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END COMPONENT;COMPONENT CONTROLPORT (MINUTE,HOUR,EXCHGE,CY0,CY1: IN STD_LOGIC;CLK0: OUT STD_LOGIC;CLK1: OUT STD_LOGIC);END COMPONENT;COMPONENT SCAN_LEDPORT(SCAN : IN STD_LOGIC;DIN:IN STD_LOGIC_VECTOR(23 DOWNTO 0);SG:OUT STD_LOGIC_VECTOR(6 DOWNTO 0);BT:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END COMPONENT;COMPONENT ALARM ISPORT (ML: IN STD_LOGIC_VECTOR(3 DOWNTO 0);MH: IN STD_LOGIC_VECTOR(3 DOWNTO 0);SL: IN STD_LOGIC_VECTOR(3 DOWNTO 0);SH: IN STD_LOGIC_VECTOR(3 DOWNTO 0);CLK: IN STD_LOGIC;SPEAKER: OUT STD_LOGIC);END COMPONENT;SIGNAL D :STD_LOGIC_VECTOR(23 DOWNTO 0);SIGNAL M0,M1,M2,M3 :STD_LOGIC;SIGNAL M4,M5,M6,M7 :STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINu1: CNT60 PORT MAP(CLK=>CLK,RST=>RST,EN=>EN,COUT1=>M0,CQH=>D(7 DOWNTO 4),CQL=>D(3 DOWNTO 0));u2: CNT60 PORT MAP(CLK=>M2,RST=>RST,EN=>EN,COUT1=>M1,CQH=>D(15 DOWNTO 12),CQL=>D(11 DOWNTO 8)); u3: CNT24 PORT MAP(CLK=>M3,RST=>RST,EN=>EN,MODE=>TMODE,CQH=>D(23 DOWNTO 20),CQL=>D(19 DOWNTO 16)); u4: CONTROL PORT MAP(EXCHGE=>EXCHGE,HOUR=>HOUR,MINUTE=>MINUTE,CLK0=>M2,CLK1=>M3,CY0=>M0,CY1=>M1);u5: SCAN_LED PORT MAP(SCAN=>SCAN,SG=>SG,BT=>BT,DIN(3 DOWNTO 0)=>D(3 DOWNTO 0),DIN(7 DOWNTO 4)=>D(7 DOWNTO 4),DIN(11 DOWNTO 8)=>D(11 DOWNTO 8),DIN(15 DOWNTO 12)=>D(15 DOWNTO 12),DIN(19 DOWNTO 16)=>D(19 DOWNTO 16),DIN(23 DOWNTO 20)=>D(23 DOWNTO 20));U6: ALARM PORT MAP(ML=>M6,MH=>M7,SL=>M4,SH=>M5,CLK=>CLK1024, SPEAKER=>SPEAKER);END STRUC;。

电子设计自动化(EDA)—数字时钟LED数码管显示二、实验内容和实验目的1. 6个数码管动态扫描显示驱动2. 按键模式选择(时\分\秒)与闹钟(时\分)调整控制,3. 用硬件描述语言(或混合原理图)设计时、分、秒计数器模块、闹钟模块、按键控制状态机模块、动态扫描显示驱动模块、顶层模块。

要求使用实验箱左下角的6个动态数码管(DS6 A~DS1A)显示时、分、秒;要求模式按键和调整按键信号都取自经过防抖处理后的按键跳线插孔。

实验目的: 1)学会看硬件原理图, 2)掌握FPGA硬件开发的基本技能3)培养EDA综合分析、综合设计的能力三、实验步骤、实现方法(或设计思想)及实验结果主要设备: 1)PC机, 2)硬件实验箱, 3)Quartus II软件开发平台。

1.打开Quartus II , 连接实验箱上的相关硬件资源, 如下图1所示。

2.建立新文件, 选择文本类型或原理图类型。

3. 编写程序。

4.编译5. 仿真, 加载程序到芯片, 观察硬件输出结果(数码管显示)6.结果正确则完成。

若结果不正确, 则修改程序, 再编译, 直到正确。

模24计数器模块LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;ENTITY count24 ISPORT(clk,en:IN STD_LOGIC;cout:OUT STD_LOGIC;hh,hl:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END count24;ARCHITECTURE arc OF count24 ISSIGNAL a,b:STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINPROCESS(clk,en)BEGINhh<=a;hl<=b;IF(clk'EVENT AND clk='1') THENIF(en='1') THENIF(a="0010" AND b="0011") THENa<="0000";b<="0000";ELSE IF(b="1001") THENa<=a+'1';b<="0000";ELSE b<=b+'1';END IF;END IF;IF(a="0010" AND b="0010") THENcout<='1';ELSE cout<='0';END IF;END IF;END IF;END PROCESS;END arc;模60计数器模块LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;ENTITY count60 ISPORT(clk,en:IN STD_LOGIC;cout:OUT STD_LOGIC;hh,hl:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END count60;ARCHITECTURE arc OF count60 ISSIGNAL a,b:STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL sout:STD_LOGIC;BEGINPROCESS(clk)BEGINhh<=a; hl<=b;IF(clk'EVENT AND clk='1') THENIF(en='1') THENIF(a="0101" AND b="1001") THENa<="0000";b<="0000";ELSE IF(b="1001") THENa<=a+'1';b<="0000";ELSE b<=b+'1';END IF;END IF;END IF;END IF;END PROCESS;sout<='1' WHEN a="0101" AND b="1001" ELSE '0';cout<=sout AND en;END arc;4-7显示译码模块LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY segment4to7 ISPORT(s:IN STD_LOGIC_VECTOR(3 DOWNTO 0);a,b,c,d,e,f,g:OUT STD_LOGIC);END segment4to7;ARCHITECTURE arc OF segment4to7 IS SIGNAL y:STD_LOGIC_VECTOR(6 DOWNTO 0); BEGINa<= y(6);b<= y(5);c<= y(4);d<= y(3);e<= y(2); f<= y(1);g<= y(0);PROCESS(s)BEGINCASE s ISWHEN "0000"=>y<="1111110"; WHEN "0001"=>y<="0110000"; WHEN "0010"=>y<="1101101"; WHEN "0011"=>y<="1111001"; WHEN "0100"=>y<="0110011"; WHEN "0101"=>y<="1011011"; WHEN "0110"=>y<="1011111"; WHEN "0111"=>y<="1110000"; WHEN "1000"=>y<="1111111"; WHEN "1001"=>y<="1111011"; WHEN OTHERS=>y<="0000000"; END CASE;END PROCESS;END arc;带闹钟控制模块LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY mode_adjust_with_alarm ISPORT (adjust,mode,clk1hz: IN STD_LOGIC;clkh,enh,clkm,enm,clks,enha: OUT STD_LOGIC;clkh_a,clkm_a:OUT STD_LOGIC;mode_ss: OUT STD_LOGIC_VECTOR(2 DOWNTO 0));END mode_adjust_with_alarm;ARCHITECTURE arc OF mode_adjust_with_alarm ISTYPE mystate IS (s0,s1,s2,s3,s4,s5);SIGNAL c_state,next_state: mystate;BEGINPROCESS (c_state)BEGINCASE c_state ISWHEN s0=> next_state <= s1; clkh<=clk1hz; clkm<=clk1hz; clks<=clk1hz;enh<='0'; enm<='0'; enha<='0'; clkh_a<= '0'; clkm_a<= '0'; mode_ss <="000";WHEN s1=> next_state <= s2; clkh<=adjust; clkm<= '0'; clks<='0';enh<='1'; enm<='0';enha<='0'; clkh_a<= '0';clkm_a<= '0'; mode_ss <="001";WHEN s2=> next_state <= s3; clkh<= '0'; clkm<=adjust; clks <= '0';enh<='0';enm<='1';enha<='0'; clkh_a<= '0'; clkm_a<= '0'; mode_ss <="010";WHEN s3=> next_state <= s4; clkh<= '0'; clkm<= '0'; clks<=adjust;enh<='0'; enm<='0';enha<='0'; clkh_a<= '0'; clkm_a<= '0'; mode_ss <="011";WHEN s4=> next_state <= s5; clkh<= clk1hz; clkm<= clk1hz; clks<=clk1hz;enh<='0';enm<='0';enha<='1'; clkh_a<=adjust; clkm_a<= '0'; mode_ss <="100";WHEN s5=> next_state <= s0; clkh<= clk1hz; clkm<= clk1hz; clks<=clk1hz;enh<='0'; enm<='0'; enha<='0'; clkh_a<= '0'; clkm_a<=adjust; mode_ss <="101";END CASE;END PROCESS;PROCESS (mode)BEGINIF (mode'EVENT AND mode='1') THENc_state<=next_state ;END IF;END PROCESS;END arc;扫描模块LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY scan ISPORT(clk256hz:IN STD_LOGIC;ss:OUT STD_LOGIC_VECTOR(2 DOWNTO 0));END scan;ARCHITECTURE arc OF scan ISTYPE mystate IS (s0, s1,s2,s3,s4,s5);SIGNAL c_state,next_state: mystate;BEGINPROCESS ( c_state )BEGINCASE c_state ISWHEN s0=> next_state <=s1; ss<="010";WHEN s1=> next_state <=s2; ss<="011";WHEN s2=> next_state <=s3; ss<="100";WHEN s3=> next_state <=s4; ss<="101";WHEN s4=> next_state <=s5; ss<="110";WHEN s5=> next_state <=s0; ss<="111";END CASE;END PROCESS;PROCESS (clk256hz)BEGINIF (clk256hz'EVENT AND clk256hz='1') THENc_state<=next_state ;END IF;END PROCESS;END arc;复用模块LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY mux ISPORT(hh,hl,mh,ml,sh,sl,hha,hla,mha,mla:IN STD_LOGIC_VECTOR(3 DOWNTO 0);ss,mode_ss:IN STD_LOGIC_VECTOR(2 DOWNTO 0);y:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);alarm:OUT STD_LOGIC);END mux;ARCHITECTURE arc OF mux ISSIGNAL a,hhtmp,hltmp,mhtmp,mltmp,shtmp,sltmp:STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINPROCESS(mode_ss)BEGINCASE mode_ss ISWHEN "000"=>hhtmp<=hh; hltmp<=hl; mhtmp<=mh; mltmp<=ml; shtmp<=sh; sltmp<=sl;WHEN "001"=>hhtmp<=hh; hltmp<=hl; mhtmp<=mh; mltmp<=ml; shtmp<=sh; sltmp<=sl;WHEN "010"=>hhtmp<=hh; hltmp<=hl; mhtmp<=mh; mltmp<=ml; shtmp<=sh; sltmp<=sl;WHEN "011"=>hhtmp<=hh; hltmp<=hl; mhtmp<=mh; mltmp<=ml; shtmp<=sh; sltmp<=sl;WHEN "100"=> hhtmp<=hha; hltmp<=hla; mhtmp<=mha; mltmp<=mla; shtmp<=sh; sltmp<=sl;WHEN "101"=> hhtmp<=hha; hltmp<=hla; mhtmp<=mha; mltmp<=mla; shtmp<=sh; sltmp<=sl;WHEN OTHERS=>hhtmp<="0000";hltmp<="0000";mhtmp<="0000";mltmp<="0000";shtmp<="0000";sltmp<="0000"; END CASE;END PROCESS;PROCESS(ss)BEGINCASE ss ISWHEN "010"=> a <=hhtmp;WHEN "011"=> a <=hltmp;WHEN "100"=> a <=mhtmp;WHEN "101"=> a <=mltmp;WHEN "110"=> a <=shtmp;WHEN "111"=> a <=sltmp;WHEN OTHERS => a <="0000";END CASE;y<=a;END PROCESS;alarm<='1' WHEN ((hh=hha)AND(hl=hla)AND(mh=mha)AND(ml=mla)) ELSE '0';END arc;闪烁模块LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY blink_control ISPORT(ss,mode_ss:IN STD_LOGIC_VECTOR(2 DOWNTO 0);blink_en:OUT STD_LOGIC);END blink_control;ARCHITECTURE arc OF blink_control ISBEGINPROCESS (ss,mode_ss)BEGINIF(ss="010" AND mode_ss="001") THEN blink_en<='1';ELSIF(ss="011" AND mode_ss="001") THEN blink_en<='1';ELSIF(ss="100" AND mode_ss="010") THEN blink_en<='1';ELSIF(ss="101" AND mode_ss="010") THEN blink_en<='1';ELSIF(ss="110" AND mode_ss="011") THEN blink_en<='1';ELSIF(ss="111" AND mode_ss="011") THEN blink_en<='1';ELSIF(ss="010" AND mode_ss="100") THEN blink_en<='1';ELSIF(ss="011" AND mode_ss="100") THEN blink_en<='1';ELSIF(ss="100" AND mode_ss="101") THEN blink_en<='1';ELSIF(ss="101" AND mode_ss="101") THEN blink_en<='1';ELSE blink_en<='0';END IF;END PROCESS;END arc;Top文件LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY design3 ISPORT (mode,adjust,clk1hz,clk2hz,clk256hz,clk1khz:IN STD_LOGIC;alarm,a,b,c,d,e,f,g:OUT STD_LOGIC;ss:OUT STD_LOGIC_VECTOR(2 DOWNTO 0));END design3;ARCHITECTURE arc OF design3 ISCOMPONENT mode_adjust_with_alarm PORT (adjust,mode,clk1hz: IN STD_LOGIC;clkh,enh,clkm,enm,clks,enha: OUT STD_LOGIC;clkh_a,clkm_a:OUT STD_LOGIC;mode_ss: OUT STD_LOGIC_VECTOR(2 DOWNTO 0));END COMPONENT;COMPONENT scan PORT (clk256hz:IN STD_LOGIC;ss:OUT STD_LOGIC_VECTOR(2 DOWNTO 0));END COMPONENT;COMPONENT segment4to7 PORT (s: IN STD_LOGIC_VECTOR(3 DOWNTO 0);a,b,c,d,e,f,g: OUT STD_LOGIC);END COMPONENT;COMPONENT mux PORT(hh,hl,mh,ml,sh,sl,hha,hla,mha,mla:IN STD_LOGIC_VECTOR(3 DOWNTO 0);ss,mode_ss:IN STD_LOGIC_VECTOR(2 DOWNTO 0);y:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);alarm:OUT STD_LOGIC);END COMPONENT;COMPONENT blink_control PORT(ss,mode_ss:IN STD_LOGIC_VECTOR(2 DOWNTO 0);blink_en:OUT STD_LOGIC);END COMPONENT;COMPONENT count24 PORT (clk,en:IN STD_LOGIC;cout:OUT STD_LOGIC;hh,hl:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END COMPONENT;COMPONENT count60 PORT (clk ,en:IN STD_LOGIC;cout:OUT STD_LOGIC;hh,hl:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END COMPONENT;SIGNALclkh,enh,clkm,enm,clks,clkh_a,clkm_a,coutm,couts,coutm_en,couts_en,cout,vcc,coutma_en,coutma,alarm1,bli nk_en,blink_tmp,enha: STD_LOGIC;SIGNAL mode_ss,ss1:STD_LOGIC_VECTOR(2 DOWNTO 0);SIGNAL hh,hl,mh,ml,sh,sl,hha,hla,mha,mla,y,i:STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINvcc<='1';coutm_en <= enh OR coutm;couts_en <= enm OR couts;coutma_en<= enha OR coutma;blink_tmp<=blink_en and clk2hz;i(3)<=y(3) OR blink_tmp;i(2)<=y(2) OR blink_tmp;i(1)<=y(1) OR blink_tmp;i(0)<=y(0) OR blink_tmp;ss<=ss1;alarm<=alarm1 AND clk1khz;u1:mode_adjust_with_alarmPORT MAP( adjust,mode,clk1hz,clkh,enh,clkm,enm,clks,enha,clkh_a,clkm_a,mode_ss);u2:count24 PORT MAP(clkh,coutm_en,cout,hh,hl);u3:count60 PORT MAP(clkm,couts_en,coutm,mh,ml);u4:count60 PORT MAP(clks,vcc,couts,sh,sl);u5:count24 PORT MAP(clkh_a,coutma_en,cout,hha,hla);u6:count60 PORT MAP(clkm_a,vcc,coutma,mha,mla);u7:mux PORT MAP(hh,hl,mh,ml,sh,sl,hha,hla,mha,mla,ss1,mode_ss,y,alarm1);u8:scan PORT MAP(clk256hz,ss1);u9:blink_control PORT MAP(ss1,mode_ss,blink_en);u10:segment4to7 PORT MAP(i,a,b,c,d,e,f,g);END arc;实验结果:数字钟包括正常的时分秒计时, 实验箱左下角的6个动态数码管(DS6 A~DS1A)显示时、分、秒。

eda课程设计 数字钟。

一、课程目标知识目标:1. 让学生理解数字时钟的基本原理,掌握数字时钟电路的设计方法。

2. 使学生掌握EDA工具的使用,学会利用工具进行电路设计、仿真和调试。

3. 帮助学生了解数字时钟中各个模块的功能和相互关系。

技能目标:1. 培养学生运用EDA工具进行数字电路设计的能力。

2. 培养学生分析问题、解决问题的能力,能够根据实际需求设计简单的数字时钟电路。

3. 提高学生的动手实践能力,学会使用相关仪器设备进行电路调试。

情感态度价值观目标:1. 激发学生对电子设计的兴趣,培养创新意识和探索精神。

2. 培养学生良好的团队协作精神,学会与他人共同解决问题。

3. 培养学生严谨的科学态度和勤奋刻苦的学习精神。

课程性质:本课程为实践性课程,旨在通过数字时钟电路设计,提高学生的电子设计能力。

学生特点:学生具备一定的电子基础知识,对EDA工具感兴趣,但动手实践能力有待提高。

教学要求:注重理论与实践相结合,充分调动学生的积极性,引导学生主动参与教学活动,提高学生的实践能力。

教学过程中,注重培养学生的团队合作精神和创新能力,为学生的未来发展奠定基础。

通过本课程的学习,使学生能够具备独立设计、制作和调试数字时钟电路的能力。

二、教学内容根据课程目标,本章节教学内容主要包括以下几部分:1. 数字时钟原理:讲解数字时钟的基本原理,分析数字时钟的各个模块功能,如秒脉冲发生器、计数器、显示驱动等。

2. EDA工具使用:介绍EDA工具的基本操作,如原理图绘制、电路仿真、PCB设计等,使学生掌握使用EDA工具进行数字电路设计的方法。

3. 数字时钟电路设计:根据实际需求,制定数字时钟设计方案,包括选择合适的元器件、绘制原理图、编写程序等。

4. 电路仿真与调试:指导学生利用EDA工具进行电路仿真,分析电路性能,优化设计方案;并进行实际电路搭建与调试,培养学生的动手实践能力。

教学大纲安排如下:1. 第一周:数字时钟原理学习,熟悉各个模块功能。

EDA课程设计报告一·设计任务使用硬件描述语言,在CPLD/FPGA上实现一个多功能数字钟。

二·设计要求除按键、LED、扬声器、时钟信号外,整个数字钟的功能要求在一块芯片上实现。

a)具有时,分,秒,计数显示功能,以24小时循环计时;b)具有时间清零功能;c)具有小时、分钟和秒钟调整功能(个位和十位分开调或合起来调)。

d)具有闹钟功能,能预设闹钟时间,精确到秒。

整个数字钟只设一个时钟输入端口,所需不同频率信号在内部分频实现。

(LED扫描频率设为50Hz以上)。

三·设计方案设计采用模块方式,分别为分频模块:产生1Hz的脉冲作为秒的输入,和产生1kHz的脉冲作为数码管显示的动态扫描。

计时模块:秒模块,分模块,时模块。

闹钟模块,显示模块,控制模块。

四·模块端口设置1. 分频模块输入:clkin : 本实验输入为50MHz晶振输出:clk : 为显示模块及始终调节提供1KHz脉冲clkt: 为计数器模块提供1Hz脉冲2. 计时模块m 是模式按键,当m=0 时,进入计时模式,在计时模式下可以进行时间调整。

num3,num4 产生加速调整时间,当其值为1 时,可以快速调整时间,该调整时间的频率由clk 提供。

counta,count1 是手动调节时间。

Turn 接按键,可以改变当前调节的是小时还是分钟,长按turn 键还可以使秒钟信号清零。

sec1,min1,hour1 输出的是计时的秒,分,时。

3.闹钟模块原理:num1,num2 产生加速调整时间,当其值为1 时,可以快速调整时间,该调整时间的频率由clk 提供。

countb,count2 是手动调节闹钟时间。

amin,ahour 是输出的闹钟的分钟和小时4. 控制模块m 是模式按键,当m=0 时,指当前输出的是计时功能;当m=1 时,指当前调整的是闹钟时间;当m=2 时,指当前调整的是计时时间;当m=3 时,此时turn 按键可用于跑表的暂停与开始。

eda数字钟课程设计一、课程目标知识目标:1. 让学生掌握EDA技术的基本概念,理解数字钟的原理和设计流程。

2. 学会使用Verilog HDL语言编写简单的数字电路程序,实现数字钟的基本功能。

3. 了解数字钟各模块的功能和相互关系,如分频器、计数器、秒/分/时显示等。

技能目标:1. 培养学生运用所学知识,自主设计并实现简单数字电路的能力。

2. 提高学生动手实践能力,学会使用FPGA/CPLD等开发工具进行数字电路的调试和验证。

3. 培养学生团队协作和沟通能力,能在小组合作中发挥各自优势,共同完成项目任务。

情感态度价值观目标:1. 激发学生对电子设计自动化技术的兴趣,培养其创新意识和探索精神。

2. 培养学生严谨、细致、负责的工作态度,注重实践操作的规范性和安全性。

3. 增强学生的自信心,使其在项目实践中体验到成功的喜悦,培养克服困难的勇气。

课程性质:本课程为电子信息类专业的实践课程,旨在培养学生的实际操作能力和创新能力。

学生特点:学生已经掌握了数字电路和Verilog HDL语言的基本知识,具有一定的编程和实践能力。

教学要求:结合学生特点,注重理论与实践相结合,以项目为导向,引导学生自主探究和合作学习。

通过课程学习,使学生能够独立完成数字钟的设计与实现,提高其综合运用所学知识解决实际问题的能力。

教学过程中,注重分解课程目标为具体的学习成果,以便进行教学设计和评估。

二、教学内容1. 数字钟原理及设计流程:介绍数字钟的基本工作原理,包括时钟信号产生、分频、计数、显示等模块的功能和设计方法。

教材章节:第三章“数字电路设计基础”,第5节“数字时钟设计”2. Verilog HDL语言基础:回顾Verilog HDL的基本语法和结构,强调模块化设计,掌握基本逻辑门、时序逻辑的描述方法。

教材章节:第二章“硬件描述语言Verilog HDL”,第1-4节3. 数字钟各模块设计:- 分频器设计:学习如何实现时钟信号的分频,得到所需的计数脉冲。

设计报告课程名称在系统编程技术任课教师周泽华老师设计题目数字钟班级11电子信息工程(1)班姓名童亚强学号1105011025日期2013/12/29摘要:20世纪90年代,国际上电子和计算机技术较为先进的国家,一直在积极探索新的电子电路设计方法,并在设计方法、工具等方面进行了彻底的变革,取得了巨大成功。

在电子技术设计领域,可编程逻辑器件(如CPLD、FPGA)的应用,已得到广泛的普及,这些器件为数字系统的设计带来了极大的灵活性。

这些器件可以通过软件编程而对其硬件结构和工作方式进行重构,从而使得硬件的设计可以如同软件设计那样方便快捷。

这一切极大地改变了传统的数字系统设计方法、设计过程和设计观念,促进了EDA技术的迅速发展。

EDA技术就是以计算机为工具,设计者在EDA软件平台上,用硬件描述语言VHDL完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。

EDA技术的出现,极大地提高了电路设计的效率和可操作性,减轻了设计者的劳动强度。

EDA技术在电子系统设计领域越来越普及,本设计主要利用VHDL语言在EDA平台上设计一个电子数字钟,它的计时周期为24小时,显示满刻度为24时59分59秒,另外还具有校时功能和闹钟功能。

总的程序由几个各具不同功能的单元模块程序拼接而成,其中包括分频程序模块、时分秒计数和设置程序模块、比较器程序模块、三输入数据选择器程序模块、译码显示程序模块和拼接程序模块。

并且使用QUARTUS II9.0软件进行电路波形仿真,下载到EDA实验箱进行验证。

关键词:数字钟 EDA VHDL语言一、设计目的1、熟练地运用数字系统的设计方法进行数字系统设计;2、能进行较复杂的数字系统设计;3、按要求设计一个数字钟。

二、设计内容1、要求显示秒、分、时,显示格式如下:图2.1 显示格式2、可清零、可调时,具有整点报时功能。

三、设计原理1、数字钟的基本工作原理:数字钟以其显示时间的直观性、走时准确性作为一种计时工具,数字钟的基本组成部分离不开计数器,在控制逻辑电路的控制下完成预定的各项功能。

数字钟的基本原理方框图如下:1)时钟计数:完成时、分、秒的正确计时并且显示所计的数字;对秒、分——60进制计数,即从0到59循环计数,时钟——24进制计数,即从0到23循环计数,并且在数码管上显示数值。

2)时间设置:手动调节分钟、小时,可以对所设计的时钟任意调时间,这样使数字钟真正具有使用功能。

我们可以通过实验板上的键7和键4进行任意的调整,因为我们用的时钟信号均是1HZ的,所以每LED灯变化一次就来一个脉冲,即计数一次。

3)清零功能:reset为复位键,低电平时实现清零功能,高电平时正常计数。

可以根据我们自己任意时间的复位。

4)蜂鸣器在整点时有报时信号产生,蜂鸣器报警。

产生“滴答.滴答”的报警声音。

2、数字钟设计的电路原理图3、VHDL 设计注:详细的VHDL文件见附录四、设计仪器、设备PC机一台、GW48—PKnow教学实验系统一台、下载电缆一根(已接好)library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity DigitalClock isport(clk,en,rst : in std_logic;ADJEN : in std_logic;AlarmEn : in std_logic;alarmADJ : in std_logic;ADJ : in std_logic_vector(3 downto 0);sound : out std_logic;hour_unit : out std_logic_vector(3 downto 0);hour_decade : out std_logic_vector(3 downto 0);min_unit : out std_logic_vector(3 downto 0);min_decade : out std_logic_vector(3 downto 0);sec_unit : out std_logic_vector(3 downto 0);sec_decade : out std_logic_vector(3 downto 0);dote1 : out std_logic_vector(3 downto 0);dote2 : out std_logic_vector(3 downto 0));end ;architecture bhv of DigitalClock iscomponent hourport(rst,carry,en : in std_logic;ADJclk,ADJEN : in std_logic;ADJ : in std_logic_vector(3 downto 0);decade,unit : out std_logic_vector(3 downto 0));end component;component minport(rst,carry,en : in std_logic;ADJclk,ADJEN : in std_logic;ADJ : in std_logic_vector(3 downto 0);carryout : out std_logic;decade,unit : out std_logic_vector(3 downto 0));end component;component secport(rst,clk,en : in std_logic;ADJEN : in std_logic;carryout : out std_logic;decade,unit : out std_logic_vector(3 downto 0));end component;component alarmport(clk,en,ADJclk : in std_logic;alarmADJ : in std_logic;AlarmEn : in std_logic;ADJ : in std_logic_vector(3 downto 0);hour_unit : in std_logic_vector(3 downto 0);hour_decade : in std_logic_vector(3 downto 0);min_unit : in std_logic_vector(3 downto 0);min_decade : in std_logic_vector(3 downto 0);ADJhour_unit : out std_logic_vector(3 downto 0);ADJhour_decade : out std_logic_vector(3 downto 0);ADJmin_unit : out std_logic_vector(3 downto 0);ADJmin_decade : out std_logic_vector(3 downto 0);sound : out std_logic);end component;component PrescalClkport(clkin : in std_logic;clkout_1Hz : out std_logic;clkout_4Hz : out std_logic);end component;signal carry1,carry2,clk_1Hz,clk_4Hz : std_logic;signal hour1,hour2,min1,min2 ,ADJhour1,ADJhour2,ADJmin1,ADJmin2 : std_logic_vector(3 downto 0);beginU1 : hour port map(rst=>rst,ADJclk=>clk_4Hz,en=>en,carry=>carry1,ADJEN=>ADJEN,ADJ=>ADJ,decade=>hour1,unit=>hour2);U2 : min port map(rst=>rst,ADJclk=>clk_4Hz,en=>en,carry=>carry2,carryout=>carry1,ADJEN=>ADJEN,ADJ=>ADJ,decade=>min1,unit= >min2);U3 : sec port map(rst=>rst,clk=>clk_1Hz,en=>en,carryout=>carry2,decade=>sec_decade,unit=>sec_unit,ADJEN=>ADJEN);U4 : alarm port map(clk=>clk_1Hz,en=>en,ADJclk=>clk_4Hz,alarmADJ=>alarmADJ,AlarmEn=>AlarmEn,ADJ=>ADJ, hour_unit=>hour2,hour_decade=>hour1,min_unit=>min2,min_decade=>min1,ADJhour_decade=>ADJhour1,ADJhour_unit=>ADJhour2,ADJmin_decade=>ADJmin1,ADJmin_unit=>ADJmin2 , sound=>sound);U5 : PrescalClk port map(clkin=>clk,clkout_1Hz=>clk_1Hz,clkout_4Hz=>clk_4Hz);process(hour1,hour2,min1,min2,alarmADJ,ADJhour1,ADJhour2,ADJmin1,ADJmin2)beginif(alarmADJ='0') thenhour_decade<=hour1;hour_unit<=hour2;min_decade<=min1;min_unit<=min2;elsehour_decade<=ADJhour1;hour_unit<=ADJhour2;min_decade<=ADJmin1;min_unit<=ADJmin2;end if;dote1<="1010";dote2<="1010";end process;end;五、设计步骤1、用VHDL程序设计步骤1:为本项设计建立文件夹任何一项设计都是一项工程,都必须首先为此工程建立一个放置与此工程相关的所有的文件夹,在此文件夹被EDA 软件默认为工作库。