微机原理第5章存储器系统

- 格式:ppt

- 大小:1.48 MB

- 文档页数:85

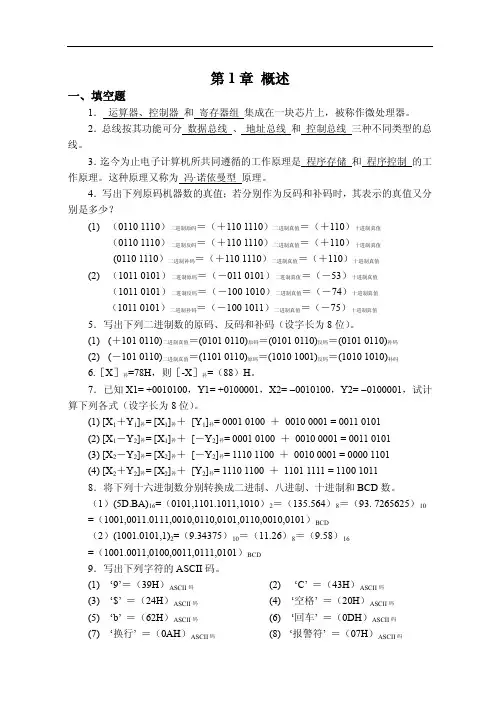

微机原理与接口技术复习题(本)第1章概论1. 什么是程序和指令?2. 洪。

诺依曼计算机的核心原理是什么?3. 存储程序的概念是什么?4. CPU由那三部分组成?主机由那几部分组成?5. CPU对内存有那两种操作?6. 325.625D=- B= H234D= BCD7. 已知X=-1110011B,试求[X]原、[X]反、[X]补。

8. 已知X=-1110111B ,Y=+1011010B,求[X+Y]补。

9. 已知X=-1101001B ,Y=-1010110B 计算X-Y。

第2章微型计算机基础1. 微处理器内部由那三部分组成?2. 控制器有那些功能?3. 8086由那两部分组成?其功能是什么?4. 熟悉8088最小模式下的主要引脚功能。

5. 指令队列有什么功能?6. 8088的8个通用寄存器是什么?4个段寄存器是什么?两个控制寄存器是什么?7. 什么是逻辑地址和物理地址,有什么关系什么?8. 4个段寄存器中那一个段寄存器用户程序不用设置。

9. 什么是总线?10. 总线周期中,什么情况下要插入TW等待周期?11. 8088CPU中标志寄存器包含那些标志位什么?第3 章、第4章8088指令系统与汇编语言程序设计1. 什么是寻址方式? 8088CPU有那些寻址方式?2. 试说明MOV SI ,[BX ] 与LEA SI , [BX]两条指令的区别。

3. 设DS=212AH ,CS=0200H ,IP=1200H, BX=0500H , DATA=40H,[217A0H]=2300H, [217E0H]=0400H ,[217E2H]=9000H ,试确定下列指令的转移地址:(1) JMP BX(2) JMP WORD PTR [BX](3) JMP DWORD PTR [BX]4. 设SP=2300H ,AX=50ABH ,BX=1234H ,执行PUSH AX 后SP=?在执行PUSH BX ,POP AX后SP=?,AX=?,BX=?.5. 已知AL=7BH ,BL=38H ,试问执行ADD AL ,BL 后的6个状态标志是什么?6. 试判断下列程序执行后AX中的内容是什么。

习题五一. 思考题⒈半导体存储器主要分为哪几类?简述它们的用途和区别。

答:按照存取方式分,半导体存储器主要分为随机存取存储器RAM(包括静态RAM和动态RAM)和只读存储器ROM(包括掩膜只读存储器,可编程只读存储器,可擦除只读存储器和电可擦除只读存储器)。

RAM在程序执行过程中,能够通过指令随机地对其中每个存储单元进行读\写操作。

一般来说,RAM中存储的信息在断电后会丢失,是一种易失性存储器;但目前也有一些RAM 芯片,由于内部带有电池,断电后信息不会丢失,具有非易失性。

RAM的用途主要是用来存放原始数据,中间结果或程序,与CPU或外部设备交换信息。

而ROM在微机系统运行过程中,只能对其进行读操作,不能随机地进行写操作。

断电后ROM中的信息不会消失,具有非易失性。

ROM通常用来存放相对固定不变的程序、汉字字型库、字符及图形符号等。

根据制造工艺的不同,随机读写存储器RAM主要有双极型和MOS型两类。

双极型存储器具有存取速度快、集成度较低、功耗较大、成本较高等特点,适用于对速度要求较高的高速缓冲存储器;MOS型存储器具有集成度高、功耗低、价格便宜等特点,适用于内存储器。

⒉存储芯片结构由哪几部分组成?简述各部分的主要功能。

答:存储芯片通常由存储体、地址寄存器、地址译码器、数据寄存器、读\写驱动电路及控制电路等部分组成。

存储体是存储器芯片的核心,它由多个基本存储单元组成,每个基本存储单元可存储一位二进制信息,具有0和1两种状态。

每个存储单元有一个唯一的地址,供CPU访问。

地址寄存器用来存放CPU访问的存储单元地址,该地址经地址译码器译码后选中芯片内某个指定的存储单元。

通常在微机中,访问地址由地址锁存器提供,存储单元地址由地址锁存器输出后,经地址总线送到存储器芯片内直接进行译码。

地址译码器的作用就是用来接收CPU送来的地址信号并对它进行存储芯片内部的“译码”,选择与此地址相对应的存储单元,以便对该单元进行读\写操作。

第二章 8086 体系结构与80x86CPU1.8086CPU 由哪两部份构成?它们的主要功能是什么?答:8086CPU 由两部份组成:指令执行部件<EU,Execution Unit>和总线接口部件<BIU,Bus Interface Unit>。

指令执行部件〔EU 主要由算术逻辑运算单元<ALU>、标志寄存器F R、通用寄存器组和E U 控制器等4个部件组成,其主要功能是执行指令。

总线接口部件<BIU>主要由地址加法器、专用寄存器组、指令队列和总线控制电路等4个部件组成,其主要功能是形成访问存储器的物理地址、访问存储器并取指令暂存到指令队列中等待执行,访问存储器或者I/O 端口读取操作数参加E U 运算或者存放运算结果等。

2.8086CPU 预取指令队列有什么好处? 8086CPU 内部的并行操作体现在哪里?答: 8086CPU 的预取指令队列由6个字节组成,按照8086CPU 的设计要求, 指令执行部件〔EU 在执行指令时,不是直接通过访问存储器取指令,而是从指令队列中取得指令代码,并分析执行它。

从速度上看,该指令队列是在C PU 内部,EU 从指令队列中获得指令的速度会远远超过直接从内存中读取指令。

8086CPU 内部的并行操作体现在指令执行的同时,待执行的指令也同时从内存中读取,并送到指令队列。

5.简述8086 系统中物理地址的形成过程。

8086 系统中的物理地址最多有多少个?逻辑地址呢?答: 8086 系统中的物理地址是由20 根地址总线形成的。

8086 系统采用分段并附以地址偏移量办法形成20 位的物理地址。

采用分段结构的存储器中,任何一个逻辑地址都由段基址和偏移地址两部份构成,都是16 位二进制数。

通过一个20 位的地址加法器将这两个地址相加形成物理地址。

具体做法是16 位的段基址左移4位<相当于在段基址最低位后添4个"0">,然后与偏移地址相加获得物理地址。

单⽚微机原理系统设计与应⽤课后部分习题答案第⼆章 MCS-51单⽚机硬件结构2-5. 8051单⽚机堆栈可以设置在什么地⽅?如何实现?答:8051单⽚机堆栈可以设置在内部RAM中。

当系统复位时,堆栈指针地址为07H,只要改变堆栈指针SP的值,使其为内部RAM中地址量,就可以灵活的将堆栈设置在内部RAM中。

2-16. 8051单⽚机内部数据存储器可以分为⼏个不同的区域?各有什么特点?2-21.复位后,CPU内部RAM各单元内容是否被清除?CPU使⽤的是哪⼀组⼯作寄存器?它们的地址是什么?如何选择确定和改变当前⼯作寄存器组?答:复位并不清除CPU内部RAM单元中内容,掉电会清除内部RAM 中内容。

复位以后因为PSW=00H,所以选择⼯作寄存器0区,所占地址空间为00H-07H。

⼯作寄存器组可以查询PSW中的RS1(PSW.4)和RS0(PSW.3)来确定,改变当前RS1和RS0的值即可改变当前⼯作寄存器组。

2-22.指出复位后⼯作寄存器组R0-R7的物理地址,若希望快速保护当前⼯作寄存器组,应采取什么措施?答:复位⼯作寄存器组R0-R7的物理地址为00H-07H。

如希望快速保护当前⼯作寄存器组,可以通过改变PSW中RS1(PSW.4)和RS0(PSW.3)的当前值来完成。

第三章 MCS-51指令系统3-6.设系统晶振为12MHz,阅读下列程序,分析其功能,并⼈⼯汇编成机器代码。

答:因为AJMP指令必须有PC指针地址,所以本题解题时设程序开始地址为1000H。

本程序完成功能是使P1.0⼝输出⽅波:T=2*((3*250+2+2)*10+1+2+2)=15090us=15.09ms翻译成机器语⾔的难点在于AJMP⼀句,根据AJMP指令代码可知,该指令为2个字节,⾼8为字节构成为“A10A9A800001”,低8位字节构成为“A7-A0”。

⼜有设置了程序起始地址为1000H,很容易可以写出各指令的地址,AJMP的绝对转移⽬标地址为1002H,A10=0、A9=0、A8=0,所以机器代码为“01 02”,⽬标地址在2区,因为A15-A11为“00010”。

习 题 五一. 思考题二. 综合题⒈ 已知一个SRAM 芯片的容量为16KB×4,该芯片的地址线为多少条数据线为多少条 答:芯片容量为142B ,所以该芯片的地址线为14条,数据线为4条。

⒉ 巳知一个DRAM 芯片外部引脚信号中有4条数据线,7条地址线,计算其存储容量。

答:7421284⨯=⨯位。

3.某存储芯片上有1024个存储单元,每个存储单元可存放4位二进制数值,则该存储芯片的存储容量是多少字节。

答:512B 。

4. 某 RAM 芯片的存储容量为 1024×8 位,该芯片的外部引脚最少应有几条其中几条地址线几条数据线若已知某 RAM 芯片引脚中有 13 条地址线,8 条数据线,那么该芯片的存储容量是多少答:该芯片外部引脚最少应有18条;其中10条地址线,8条数据线。

芯片的存储容量是32KB 。

5. 在部分译码电路中,若CPU 的地址线A 15、A 14和A 13未参加译码,则存储单元的重复地址有多少个。

答:328=个。

6. 假设选用一片6264芯片和一片2764芯片构成内存储系统。

采用线选法控制片选端,至少需要多少条片选地址线若采用部分译码法控制片选端,至少需要多少条片选地址线采用全部译码法控制片选端,则需要多少条的片选地址线答:用线选法控制片选端,至少需要2条片选地址线;若采用部分译码法控制片选端,至少需要1条片选地址线;采用全部译码法控制片选端,则需要1条的片选地址线。

7.设某微型机的内存RAM 区的容量为128KB ,若用 2164 芯片构成这样的存储器,需多少片 2164至少需多少根地址线其中多少根用于片内寻址多少根用于片选译码答:需16片 2164;至少需8根地址线;其中7根用于片内寻址;1根用于片选译码。

8. 设有一个存储器系统,由2个8KB 的6264SRAM 芯片构成。

其中1#芯片的地址范围为0A6000H~0A7FFFH ,2#芯片的地址范围为0AA000H~0ABFFFH ,下图画出了74LS138译码器、存储器与8088CPU 的连接图,但只画出了连线图的一部分,请将电路连接图补充完整。

5.10用16K X1位的DRAM 芯片组成64K X8位存储器,要求:(1) 画出该存储器的组成逻辑框图。

(2) 设存储器读/写周期为0.5卩SQPU在1 yS内至多要访问一次。

试问采用哪种刷新方式比较合理?两次刷新的最大时间间隔是多少?对全部存储单元刷新一遍所需的实际刷新时间是多少?(1)组建存储器共需DRAM 芯片数N= (64K*8 ) / (16K*1 ) =4*8 (片)。

每8片组成16K X8位的存储区,A13~A0作为片内地址,用A15、A14经2:4译码器产生片选信号:,逻辑框图如下(图有误:应该每组8片,每片数据线为1根)(2)设16K X8位存储芯片的阵列结构为128行X128列,刷新周期为2ms。

因为刷新每行需0.5 yS,则两次(行)刷新的最大时间间隔应小于:心遊“55(呵128为保证在每个1yS内都留出0.5 yS给CPU访问内存,因此该DRAM适合采用分散式或异步式刷新方式,而不能采用集中式刷新方式。

若采用分散刷新方式,则每个存储器读/写周期可视为1 yS,前0.5yS用于读写,后0.5 yS用于刷新。

相当于每1 yS刷新一行,刷完一遍需要128X 1 yS= 128 yS,满足刷新周期小于2ms的要求;若采用异步刷新方式,则应保证两次刷新的时间间隔小于15.5 y S如每隔14个读写周期刷新一行,相当于每15 yS刷新一行,刷完一遍需要128 x 15yS= 1920 y S,满足刷新周期小于2ms的要求;需要补充的知识:刷新周期:从上一次对整个存储器刷新结束到下一次对整个存储器全部刷新一遍为止的时间间隔。

刷新周期通常可以是2ms,4ms或8ms。

DRAM 一般是按行刷新,常用的刷新方式包括:集中式:正常读/写操作与刷新操作分开进行,刷新集中完成。

特点:存在一段停止读/写操作的死时间,适用于高速存储器。

(DRAM 共行,刷新周期为Q = 以为读写时间,tr = 0.5以为刷新时间,tc = 1 yS 为存储周期)异步式:前两种方式的结合, 每隔一段时间刷新一次, 只需保证在刷新周期内对整个存储器刷新一遍。